# PERFORMANCE EVALUATION AND CONTROL OF AN MMC ACTIVE RECTIFIER WITH HALF-BRIDGE AND FULL-BRIDGE SUBMODULES FOR HVDC APPLICATIONS

by

## Ayoub Julius Mbogela

Submitted in partial fulfilment of the requirements for the degree

Master of Engineering (Electrical Engineering)

in the

Department of Electrical, Electronic and Computer Engineering Faculty of Engineering, Built Environment and Information Technology

UNIVERSITY OF PRETORIA

July 2021

#### **SUMMARY**

# PERFORMANCE EVALUATION AND CONTROL OF AN MMC ACTIVE RECTIFIER WITH HALF-BRIDGE AND FULL-BRIDGE SUBMODULES FOR HVDC APPLICATIONS

by

## Ayoub Julius Mbogela

Supervisor: Prof. M.N. Gitau

Department: Electrical, Electronic and Computer Engineering

University: University of Pretoria

Degree: Master of Engineering (Electrical Engineering)

Keywords: active rectifier, full bridge submodule, half bridge submodule, high

voltage direct current converter, modular multilevel converter, modular multilevel rectifier, power electronic transformer, smart

transformer, solid state transformer.

The modular multilevel active rectifier was designed and evaluated, whereby the half bridge and the full bridge DC-DC converters as its submodules for the high voltage direct current transmission were compared. It was found that, by taking advantage of the unipolar modulation scheme in the full bridge converter, the switching losses in the two converters are equal when they are both operated in the linear modulation region. Furthermore, operating the full bridge converter in the overmodulation region does not give it a pronounced advantage over the half bridge converter. The conduction losses in the full bridge converter are two times higher than those in the half bridge converter, due to double the number of semiconductor devices. However, using the half bridge converter in the high voltage direct current modular multilevel converter requires an expensive DC-side breaker, while use of the full bridge converter eliminates the need for such a breaker due to the

intrinsic DC-side fault current blocking capability. The clear choice between the two requires industry cost data.

A design methodology for the submodule capacitor average voltage loop controllers for phase-shifted carrier modulated modular multilevel converters was carried out from first principles. The methodology enables design of such controllers to be carried out in a step by step and straightforward manner without resorting to simulation or guesswork.

A simple but effective submodule capacitor sizing method was proposed. The resulting submodule capacitor size was shown to be smaller than those resulting from other sizing methods proposed in the literature while achieving the submodule capacitor voltage ripple specifications.

A robust DC bus voltage controller design for modular multilevel rectifiers was presented, whereby a design method for multilevel voltage source converters with DC link capacitors was adopted for modular multilevel rectifiers. Since the modular multilevel converters for HVDC application are designed without the DC-link capacitor to mitigate the effects of a possible DC-side fault current, the submodule capacitors in the modular multilevel converter acted as an equivalent DC link capacitor to accomplish the design.

## LIST OF ABBREVIATIONS

AC alternating current

CB circuit breaker

CCSC circulating current suppression controller

CSC current source converter

DC direct current

EMF electromotive force

FACTS flexible alternating current transmission system

FB full bridge

FID fault isolation device

FREEDM future renewable electric energy delivery and management

HB half bridge

KCL Kirchhoff's current law

KVL Kirchhoff's voltage law

LFT line frequency transformer

MMC modular multilevel converter

PET power electronic transformer

PWM pulse-width modulation

SiC silicon carbide

SM submodule

STATCOM static synchronous compensator

SST solid state transformer

ST smart transformer

THD total harmonic distortion

VSC voltage source converter

WBG wide band gap

## TABLE OF CONTENTS

| CHAP' | TER 1 INTRODUCTION                                                        | 1 |

|-------|---------------------------------------------------------------------------|---|

| 1.1   | PROBLEM STATEMENT                                                         | 1 |

|       | 1.1.1 Context of the problem                                              | 1 |

|       | 1.1.2 Research gap                                                        | 2 |

| 1.2   | RESEARCH OBJECTIVE AND QUESTIONS                                          | 3 |

| 1.3   | APPROACH                                                                  | 4 |

| 1.4   | RESEARCH GOALS                                                            | 5 |

| 1.5   | RESEARCH CONTRIBUTION                                                     | 5 |

| 1.6   | RESEARCH OUTPUTS                                                          | 6 |

| 1.7   | OVERVIEW OF STUDY                                                         | 6 |

| CHAP' | TER 2 LITERATURE STUDY                                                    | 9 |

| 2.1   | CHAPTER OBJECTIVES                                                        | 9 |

| 2.2   | THE MODULAR MULTILEVEL CONVERTER                                          | 9 |

| 2.3   | THE MMC MODULATION AND CONTROL                                            | 1 |

|       | 2.3.1 Modulation of the HB-MMC                                            | 2 |

|       | 2.3.2 Modulation of the FB-MMC                                            | 3 |

|       | 2.3.3 Submodule capacitor balancing control                               | 5 |

|       | 2.3.3.1 Individual SM capacitor voltage balancing loop                    | 7 |

|       | 2.3.3.2 Arm voltage balancing loop                                        | 7 |

|       | 2.3.3.3 Leg average voltage balancing (averaging) loop                    | 7 |

|       | 2.3.4 Circulating Current Suppression Controller (CCSC)                   | 8 |

| 2.4   | THE MMC IN HVDC SYSTEMS AND THE HVDC PROTECTION                           |   |

|       | OVERVIEW                                                                  | 9 |

|       | 2.4.1 The Power Electronic Transformer and its role in HVDC protection 1  | 9 |

|       | 2.4.2 Overview of the HB and the FB converters as submodules for HVDC-PET | - |

|       | MMC2                                                                      | 3 |

|       | 2.4.3 The | e feasibility of the Power Electronic Transformer for fault isolati | ion in an |

|-------|-----------|---------------------------------------------------------------------|-----------|

|       | HV        | DC system                                                           | 24        |

| 2.5   | СНАРТЕ    | R SUMMARY                                                           | 30        |

| CHAP  | TER 3     | MODELING OF THE MODULAR MULTILEVEL CONV                             | ERTER     |

|       |           |                                                                     | 32        |

| 3.1   | СНАРТЕ    | R OBJECTIVES                                                        | 32        |

| 3.2   | BASIC O   | PERATION OF THE MMC                                                 | 32        |

| 3.3   | CURREN    | T CONTROL MODEL                                                     | 36        |

| 3.4   | DC BUS    | VOLTAGE CONTROL MODEL                                               | 39        |

| 3.5   | SUBMOI    | DULE CAPACITOR VOLTAGE BALANCING CONTROL M                          | ODELS     |

|       | 40        |                                                                     |           |

| 3.6   | СНАРТЕ    | R SUMMARY                                                           | 49        |

| CHAP' | ΓER 4     | ANALYSIS OF THE MODULAR MULTILEVEL CONVE                            | ERTER     |

|       |           | WITH HALF-BRIDGE AND FULL-BRIDGE SUBMODU                            | LES 50    |

| 4.1   | СНАРТЕ    | R OBJECTIVES                                                        | 50        |

| 4.2   | INTROD    | UCTION                                                              | 50        |

| 4.3   | DEVICE    | RATINGS                                                             | 51        |

| 4.4   | POWER     | LOSSES COMPARISONS BETWEEN HB-MMC AND FB-MI                         | MC 52     |

|       | 4.4.1 Ser | niconductor switch and antiparallel diode conduction losses         | 53        |

|       | 4.4.2 Ser | niconductor switching losses                                        | 54        |

|       | 4.4.3 Arı | n inductor I <sup>2</sup> R losses                                  | 55        |

| 4.5   | СНАРТЕ    | R SUMMARY                                                           | 56        |

| CHAP' | TER 5     | DESIGN OF THE MODULAR MULTILEVEL CONVERS                            | ΓER 57    |

| 5.1   | СНАРТЕ    | R OBJECTIVES                                                        | 57        |

| 5.2   | INTROD    | UCTION                                                              | 57        |

| 5.3   | SUBMOI    | OULE CAPACITOR SIZING                                               | 57        |

| 5.4   | ARM INI   | DUCTOR SIZING                                                       | 66        |

| 5.5   | СНАРТЕ    | R SUMMARY                                                           | 67        |

| CHAP  | TER 6     | CONTROL OF THE MODULAR MULTILEVEL CONVE                             | ERTER     |

|       |           |                                                                     | 69        |

| 6.1   | СНАРТЕ    | R OBJECTIVES                                                        | 69        |

| 6.2   | CLIDDEN   | T CONTROL LED                                                       | 70        |

| 6.3 D  | C BUS VOLTAC    | GE CONTROLLER                         | 75      |

|--------|-----------------|---------------------------------------|---------|

| 6.4 L  | EG AVERAGE V    | VOLTAGE CONTROLLERS                   | 79      |

| 6.5 C  | RCULATING C     | CURRENT SUPPRESSION CONTROLLER        | 84      |

| 6.6 C  | HAPTER SUMM     | MARY                                  | 85      |

| СНАРТЕ | R 7 SIMUL       | LATION RESULTS AND DISCUSSION         | 86      |

| 7.1 C  | HAPTER OBJEC    | CTIVES                                | 86      |

| 7.2 IN | TRODUCTION      | V                                     | 86      |

| 7.3 H  | B-MMC VERSU     | US FB-MMC                             | 87      |

| 7.     | 3.1 AC-side qua | antities                              | 87      |

| 7.     | 3.2 Arm quantit | ties                                  | 87      |

| 7.     | 3.3 DC-side qua | antities                              | 92      |

| 7.4 L  | NEARLY MOD      | OULATED FB-MMC VERSUS OVERMODULATED   | FB-     |

| M      | MC              |                                       | 94      |

| 7.5 PC | OWER LOSSES     | S AND NUMBER OF SEMICONDUCTOR DEVICES | 99      |

| 7.6 C  | HAPTER SUMM     | MARY                                  | 102     |

| СНАРТЕ | R 8 CONCI       | LUSION                                | 103     |

| REFERE | NCES            |                                       | 105     |

| ADDEND | UM A MODE       | LING OF LEG AVERAGE VOLTAGE CONTROL   | L LOOPS |

|        | FOR A           | NY NUMBER OF SUBMODULES               | 115     |

| ADDEND | UM B CALCU      | ULATION OF ANALYTICAL VALUES          | 117     |

| B.1 L  | NEARLY MOD      | DULATED MODULAR MULTILEVEL CONVERTE   | R 117   |

| B.2 O  | VERMODULAT      | TED MODULAR MULTILEVEL CONVERTER      | 118     |

## 1.1 PROBLEM STATEMENT

## 1.1.1 Context of the problem

For transmitting electrical power over long distances, the high voltage direct current (HVDC) lines have been shown to be more efficient than the high voltage alternating current (HVAC) lines for distances of above 500-800 km for overhead lines and for distances of above 50 km for underground cables [1]. The modern HVDC transmission lines are based on voltage source converters (VSCs) since they allow power flow reversal without reversing the terminal voltage polarity, unlike the current source converters (CSVs) [2]. However, the VSC-HVDC systems are vulnerable to DC-side fault currents for two major reasons. First, the lines usually do not have any current filters which would otherwise attenuate the fault current [3]. Second, the antiparallel diodes in the semiconductor switches in the VSCs give a free pathway to the DC-side fault current [4].

The proposed solutions to the DC-side fault current are either to have DC circuit breakers on the lines, similar to those used in the AC lines but designed to specifically cater for the DC line requirements [5], or to develop VSCs capable of blocking the DC-side fault current [6]. Due to the nature of the DC transmission, the DC circuit breakers tend to be expensive and bulky which limits the economic viability of the HVDC lines and tend to not meet the space and weight requirements of areas such as offshore windfarms [7].

The VSCs for HVDC applications can be roughly put into two categories: those that are based on the half bridge (HB) converter and those that are based on the full bridge (FB)

converter. The HB-based converters are claimed to be more efficient (hence more economically viable) since they have fewer semiconductor devices, but they lack the intrinsic capability to block the DC-side fault current. On the other hand, the FB-based VSCs have the inherent ability to block the DC-side fault current but are claimed to be less efficient due to their higher count of semiconductor devices. However, their intrinsic capabilities to block the DC-side fault current promise elimination of the bulky DC breakers from the HVDC lines [8], [9].

In most studies the evaluation of the modular multilevel converter (MMC) for various applications is done using an inverter. Although the MMC rectifier and inverter share a lot in terms of current control, the DC bus voltage control and evaluation in the rectifier has been side-lined for the most part. MMC evaluation in rectifier mode helps to identify issues that are peculiar to the MMC rectifier.

## 1.1.2 Research gap

The comparison between the HB and the FB converters as SMs of the MMC for use in HVDC networks is unclear. The comparison must consider not only the difference in efficiency but also all the advantages and disadvantages that each converter brings at a system level. Also, an approach to efficiency comparison needs to be carried out beyond the comparison based on the number of semiconductor switches per submodule only, considering factors such as the switching frequency.

The controller design methodology for SM capacitor voltage balancing in phase-shifted carrier modulated MMCs is not elaborate, whereby design of parameters of such controllers depends on simulation or the parameters are quoted to remain the same as suggested by the original literature that proposed the control structure. For optimal control, the SM capacitor voltage balancing loops must be mathematically modelled so that controllers can be designed to compensate the models accordingly.

SM capacitors play a significant role in the cost and physical size of the MMC. The SM capacitors must be optimally designed to keep the cost and size down.

MMC performance evaluation is usually carried out using an inverter. Although the MMC rectifier shares the current control with the MMC inverter, the DC bus voltage control is unique to the rectifier. Evaluation of the MMC in rectifier mode unmasks research opportunities that are unique to the rectifier mode.

## 1.2 RESEARCH OBJECTIVE AND QUESTIONS

The first objective of this research is to establish the better candidate between the HB and the FB for the HVDC transmission. The comparisons done in the literature do not fully consider all the features of the FB SM. Where the features of the FB SM are considered, they are not put into context to verify if they help the FB SM outperform the HB SM. Apart from DC-side fault blocking capability, the extra features of the FB SM are its ability to be operated at half the switching frequency as that of the HB SM but produce an output waveform of the same effective switching frequency and its ability to be operated in the overmodulation region. The areas of comparison are efficiency, DC-side fault current blocking capability, and the implied cost. Since temporary faults lead only to temporary power outages, converters with fault ride-through capabilities should be able to mitigate them. On the other hand, blocking a permanent DC-side fault may need more than just control-based fault ride-through capabilities.

The second objective is to develop an elaborate controller design methodology for SM capacitor voltage balancing. The main power controller design and modulation for the MMC are straightforward. However, the controller design for the SM capacitor voltage balancing in phase-shifted modulated MMCs is not elaborate, as the controllers are often obtained through intensive simulation or produced without an explanation of how they were obtained.

The third objective aims to achieve a SM capacitor design methodology that results in an optimum capacitor size. SM capacitors contribute significantly to the cost and size of the

converter station. The existing SM capacitor sizing methods in literature, however, do not result into similar capacitor values and are usually an overdesign.

The fourth objective is to evaluate the performance of the MMC in a rectifier mode. The MMC rectifier is usually side-lined in the literature. Evaluation of the MMC performance in rectifier mode unveils the research areas that are unique to the MMC rectifier.

The research questions to be answered are:

- Which is the more suitable DC-DC converter, between the HB and the FB, for use as

a SM in HVDC systems MMCs, based on DC-side fault handling capability,

efficiency, and cost?

- Can an elaborate and step by step controller design methodology for MMC SM capacitor voltage balancing be established?

- To reduce size and cost of the MMC stations, can an optimum SM capacitor size be achieved?

- Are there research areas unique to the MMC rectifier that are overlooked in the literature?

## 1.3 APPROACH

The HB-SM and the FB-SM will be compared through analysis and simulations. Expected results will be shown through analysis, which will be confirmed by computer simulations of an MMC rectifier using PSIM software.

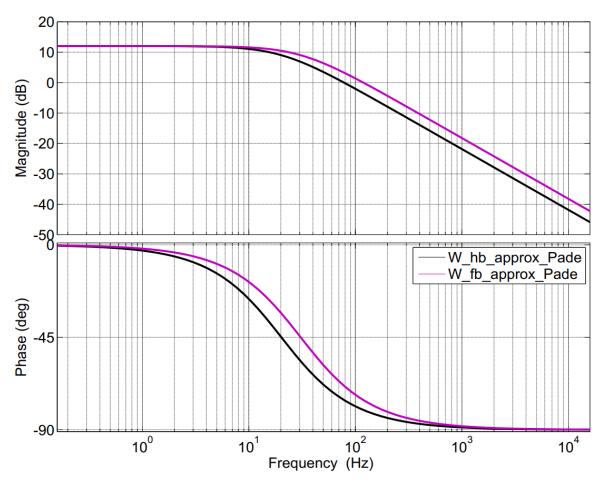

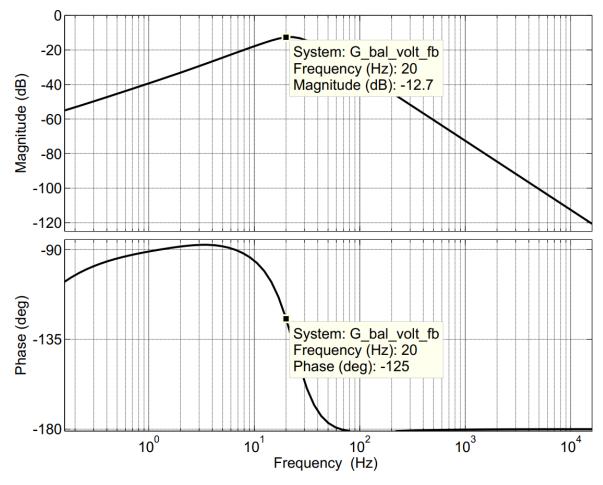

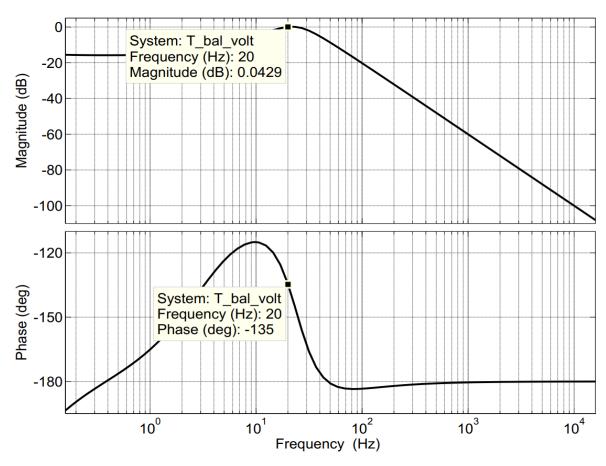

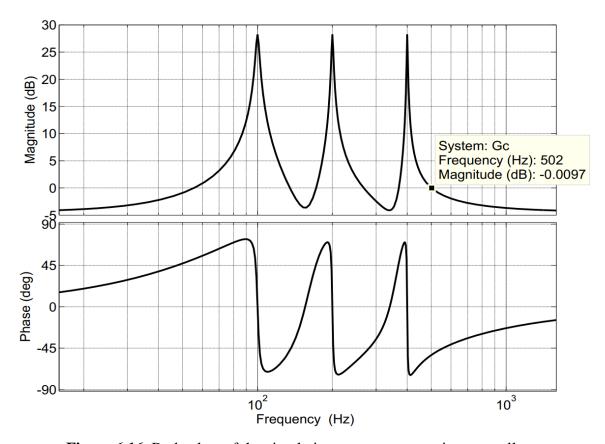

A mathematical model for SM capacitor voltage balancing control loops, specifically the average voltage balancing loop, will be derived from first principles, and the resulting Bode plots for a specified system extracted. Controllers will be designed based on these Bode plots and their effectiveness verified through simulation of an MMC rectifier using PSIM software.

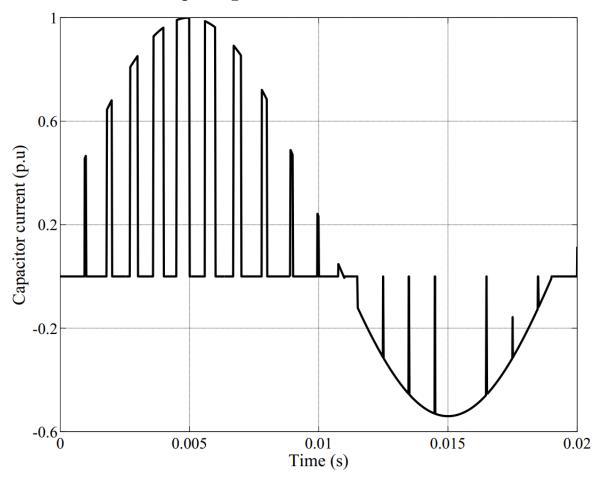

A SM capacitor design method will be derived through analysis and the resulting SM capacitor size compared to the SM capacitor sizes out of existing sizing methods, for the same operating conditions. The effectiveness of the resulting capacitor size will be verified through simulation of an MMC rectifier using PSIM software, whereby the resulting SM capacitor ripple voltage must be within a specified value.

By analyzing the simulation results, especially the characteristics of the resulting DC bus voltage of the MMC rectifier, research areas that are specific to the MMC rectifier will be identified.

## 1.4 RESEARCH GOALS

This research aims at a conclusive comparison of the HB-SM and FB-SM for use in the HVDC MMCs; an elaborate controller design methodology for the SM capacitor voltage control loops for phase-shifted carrier MMCs; an optimum SM capacitor sizing method; and to unveil research areas that are specific to the MMC rectifier.

## 1.5 RESEARCH CONTRIBUTION

- Detailed evaluation the HB and the FB converters for use in MMCs in HVDC systems based on efficiency, DC-side fault current blocking capability, and cost.

- An elaborate controller design methodology for SM capacitor voltage balancing.

- A simple and straightforward SM capacitor sizing method that results to minimized SM capacitors.

- Identification of research areas specific to the MMC rectifier and a robust MMC rectifier DC bus voltage control method. The research issues identified will be explored in future work.

#### 1.6 RESEARCH OUTPUTS

A.J. Mbogela and M.N. Gitau, "Control and performance evaluation of the active MMC rectifier with half bridge and full bridge submodules for HVDC application", IET Power Electronics, in preparation, July 2021.

A.J. Mbogela and M.N. Gitau, "An optimal submodule capacitor sizing method for modular multilevel converters for HVDC application", *IEEE Transactions on Power Electronics*, under review, July 2021.

## 1.7 OVERVIEW OF STUDY

In Chapter 2 a literature study was performed. It was found that the comparison between the half bridge and the full bridge DC-DC converters as candidates for the HVDC-MMC is not clear. There are areas where the half bridge converter has clear advantages over the full bridge converter, and vice versa, as well as some overlapping areas, such as switching losses and component ratings, which need a thorough comparison. It was also found that the controller design for the submodule capacitor voltage balancing loops of phase-shifted carrier modulated MMCs is not well elaborated in the literature, and that the design of such controllers depends on simulation and guesswork combined with fine tuning.

In Chapter 3 the modeling of the MMC was carried out. The model describing the basic operation of the converter was first considered, then the current control, the DC bus voltage control, and the SM capacitor average voltage control (leg average voltage control) models were presented. The leg average voltage control model is part of the contribution of this dissertation.

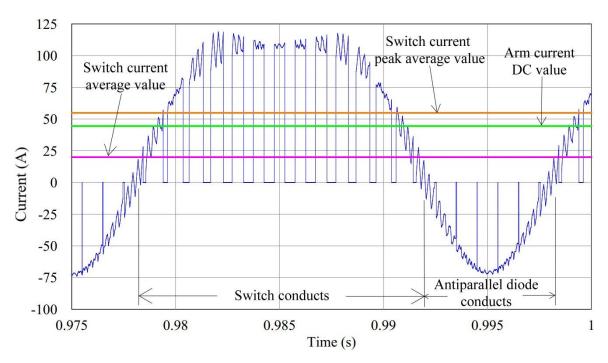

In Chapter 4 the analysis of the modular multilevel converter with half bridge or full bridge submodules was carried out. The device ratings and the loss analyses were carried out. As expected, it was found that the conduction losses in the FB-MMC are twice as much as those in the HB-MMC. The switching losses, however, were found to be equal. The ohmic losses

in the arm inductors were also found to be equal. In the overmodulation region the FB-MMC processed even higher conduction and ohmic losses while the switching losses could not be predicted.

In Chapter 5 the design of the modular multilevel converter is carried out. The SM capacitor and the arm inductor were sized. A new capacitor sizing method that results into a smaller capacitor size than other methods in the literature was proposed.

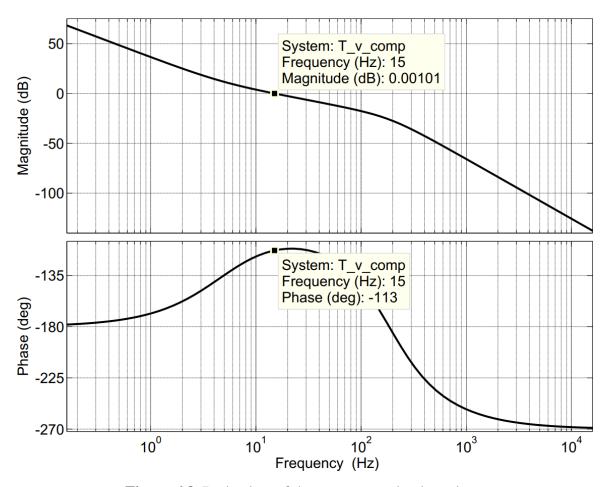

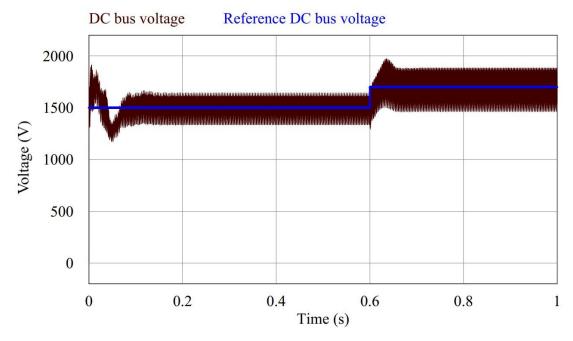

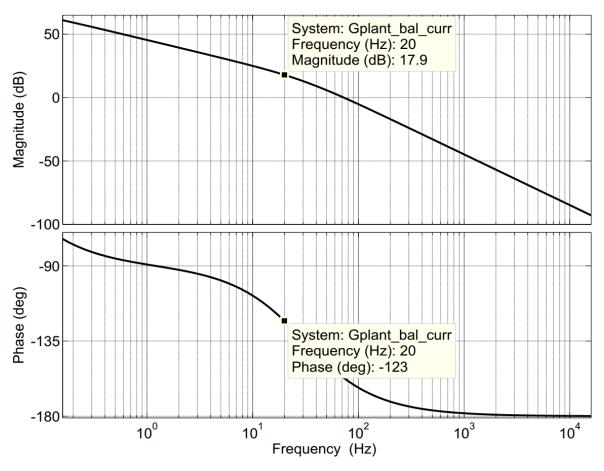

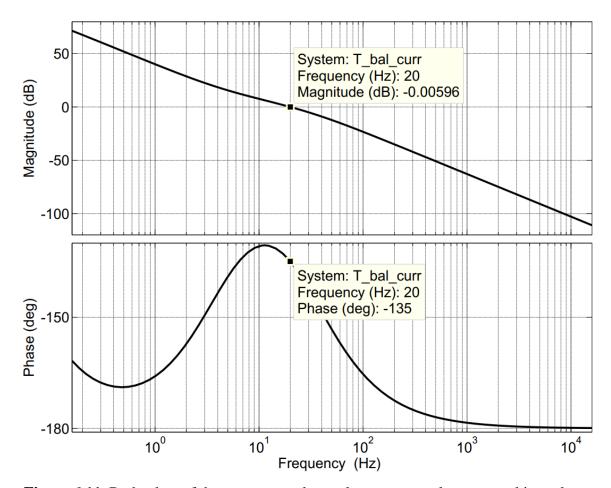

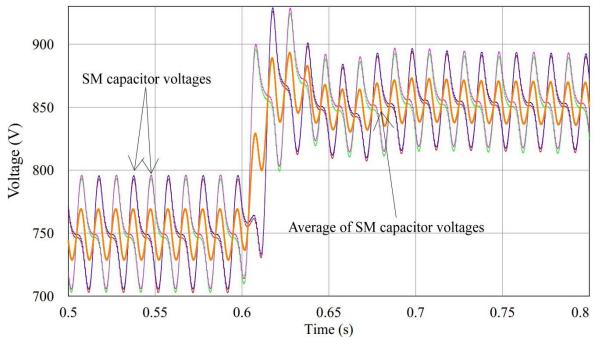

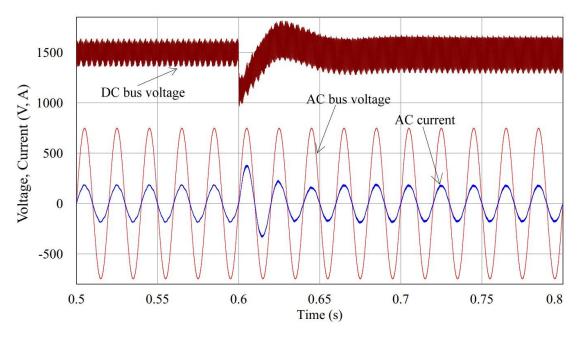

In Chapter 6 the control of the MMC was designed. Simulation was used to verify the adapted DC bus control model and the SM capacitor average voltage control model developed in Chapter 3. The robustness of the models and controllers were tested by applying step changes of around 13%.

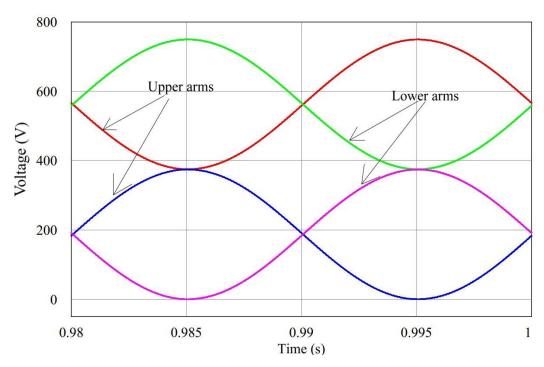

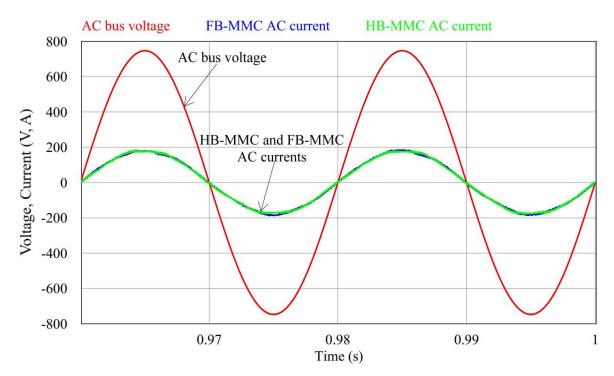

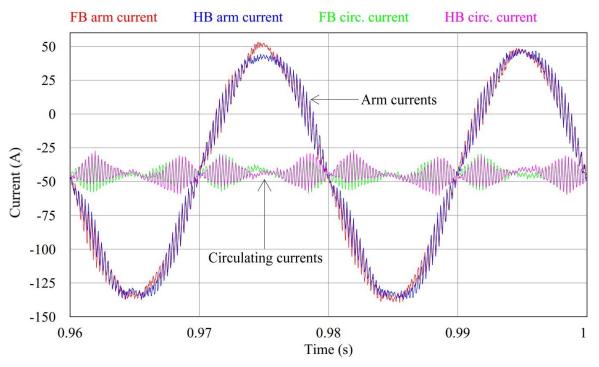

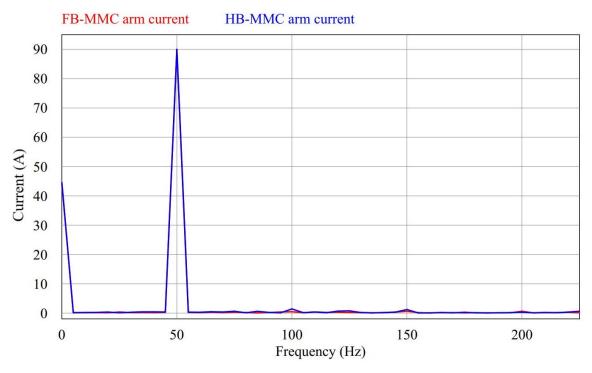

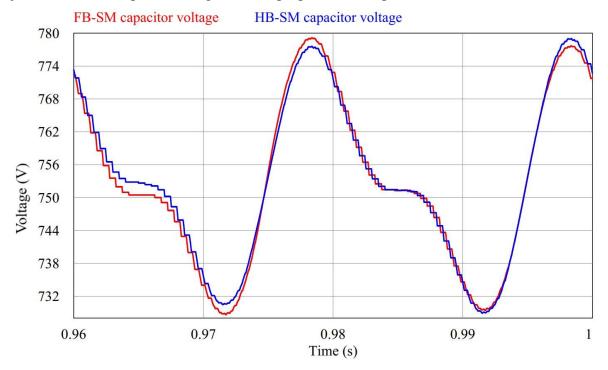

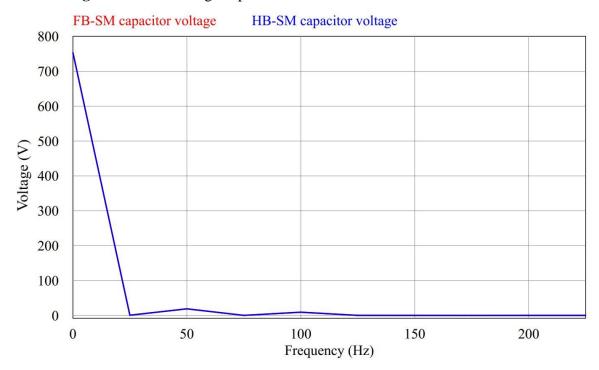

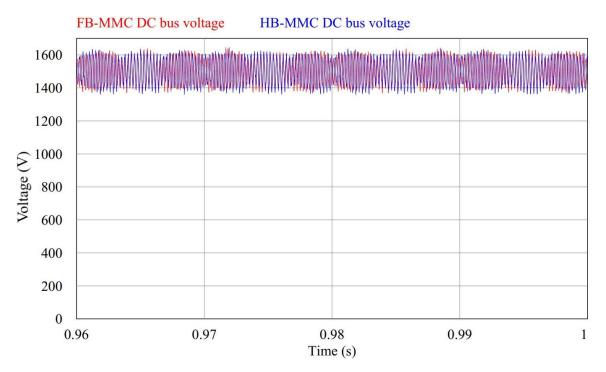

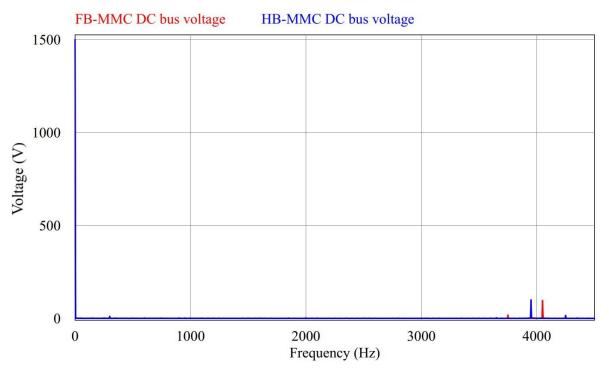

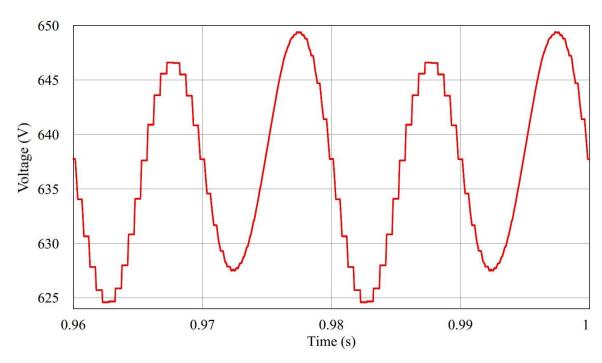

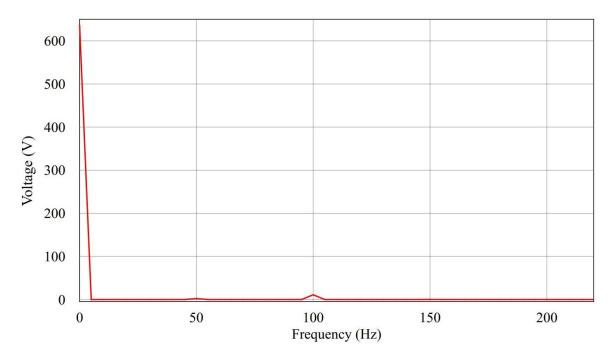

In Chapter 7 the simulation results were presented. It was found that the HB-MMC and the FB-MMC had minimal differences in the simulated quantities. Although the FB-MMC was operated at half the switching frequency as that of the HB-MMC, the DC bus voltage ripple was at the same frequency as that of the HB-MMC. The SM capacitor voltage ripple, out of the proposed SM capacitor design method, was found to meet the SM capacitor voltage ripple specifications, hence justifying the design method. The conduction losses in the FB-MMC were found to be twice those in the HB-MMC, while the switching losses were found to be equal. In the overmodulation region the FB-MMC processed even higher conduction losses but lower switching losses. Overall, it processed 1.2 times higher losses in the overmodulation region than in the linear modulation region. It was also found that the switches (as well as the diodes) in a SM, for a given power flow direction, do not carry the same amount of current. Also, if a switch carries more current in a given power flow direction, the antiparallel diode carries more current in the other power flow direction (rectifier versus inverter). On average, however, the amounts of current carried by the devices agree with the analysis in Chapter 4, which is the reason the power losses also agree with the analysis. It was demonstrated that although the FB-MMC processes higher losses than the HB-MMC, it has the advantage of the ability to block the DC-side fault current. It was also demonstrated that operating the FB-MMC in the overmodulation region does not

favour it against the HB-MMC. It was further demonstrated that the HB and the FB SMs could be used together in an HVDC-MMC, whereby the FB SMs are used only in the final rectifier stage of the PET, the stage that interfaces the DC bus, while the rest of the stages are constructed using the HB-MMC (the PET may be used to interconnect AC and DC systems. When that happens, there would be at least two rectification stages. The first rectification stage is rectifying the AC voltage before it goes through an inverter then through a high frequency transformer. Then it goes through rectification again to interface the DC bus. All other stages can be built with HB SMs, but the last stage that interfaces the HVDC line must have protection against DC-side faults). That way both the superior efficiency the HB SMs and the fault blocking capability of the FB SMs are harnessed. It was also demonstrated that the DC bus voltage ripple needs to be incorporated in sizing of the SM capacitor, which may require the switching frequency harmonic analysis of the MMC rectifier to find out how the DC bus voltage ripple is related to the SM capacitor size.

In Chapter 8 some concluding remarks were drawn.

## 2.1 CHAPTER OBJECTIVES

This chapter intends to provide background knowledge on the MMC, its modulation and control, the application of the MMC in the HVDC systems in form of a power electronic transformer (PET), an overview comparison between the half bridge (HB) and the full bridge (FB) converters as submodules for the HVDC-MMC, and an overview of the HVDC protection.

## 2.2 THE MODULAR MULTILEVEL CONVERTER

Multilevel converters show good output wave quality, less common mode noise, and high efficiency [10], [11]. With the modular architecture, multilevel converters excel at high voltage and high power applications, whereby higher voltage and higher power units are constructed from lower voltage and lower power submodules [12]. A converter of such architecture is called a modular multilevel converter (MMC). MMCs operate at relatively low switching frequencies and bear relatively high copper efficiency. They are also easy to construct and are easily scalable due to their modularity [8], [13].

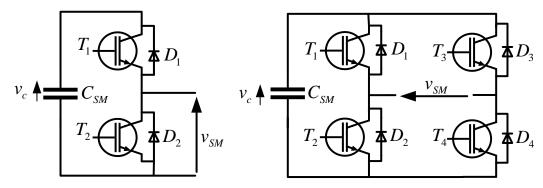

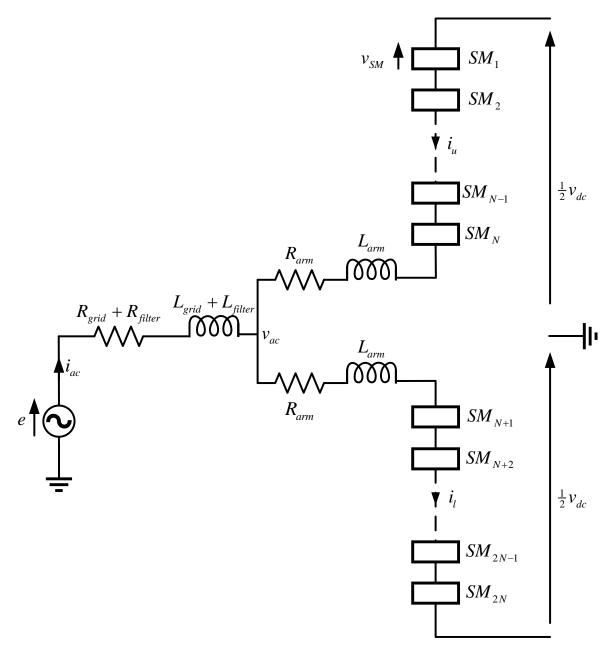

The MMC can be either single phase or multiphase, usually three phases. The MMC is made up of phase legs. In turn, each phase leg is made up of two arms: the *upper* arm and the *lower* arm. Each arm is made up of several submodules [12]. A submodule is a converter in its own right and it can be a two-level or a multilevel converter [14]. The basic submodules are the half bridge and the full bridge converters, illustrated in Figure 2.1. A single leg of an MMC is shown in Figure 2.2 (it can also be interpreted as a single phase MMC). A multiphase

MMC is constructed by connecting an appropriate number of such legs in parallel on the DC side.  $L_{grid}$  is the sum of the estimated grid equivalent inductance and the isolation transformer leakage inductance.  $L_{filter}$  is connected to minimize the arm inductance value, which should overall reduce the total inductance used in the converter design [15].

**Figure 2.1.** The half-bridge (left) and the full-bridge (right) submodules.

Figure 2.2. A leg of an MMC.

## 2.3 THE MMC MODULATION AND CONTROL

Generally, the modulation aims to achieve one or more of these objectives, depending on the application: to minimize the harmonic distortion of the output waveform; to minimize the switching losses, the cooling system, and the filter sizes; to maximize the input voltage

utilization; to attain voltage balance among the floating (SM) capacitors; and equal sharing of power and power losses among SMs [16].

Generally, the modulation schemes are classified according to how the switching pulses are obtained: pulse width modulation (PWM) e.g. space vector modulation (SVM) and selective harmonic elimination (SHE), pseudo-modulation e.g. square wave or staircase modulation, and closed loop control methods with implicit modulator e.g. hysteresis current control and finite-states model-predictive control (FS-MPC) [16]. The PWM schemes are further categorized into fundamental frequency (50 Hz or 60 Hz) switching modulations such as SHE and nearest level modulation (NLM); low frequency (< 2 kHz) switching schemes such as the sampled averaged modulation (SAM) and SVM; and high frequency (> 2 kHz) switching schemes such as level-shifted carrier (LSC) modulation and phase-shifted carrier (PSC) modulation [17].

For multilevel converters, PSC and different variations of LSC [18] are used, especially at high frequencies where they result into natural SM capacitor voltage balance. When they are used at low frequencies to minimize switching losses, the main control loop must be used in conjunction with a dedicated SM capacitor voltage balancing control loop [19].

## 2.3.1 Modulation of the HB-MMC

Among the various modulation schemes, PSC is the most suitable for MMC with fewer levels because it is easier to implement in a microcontroller, and the phase shift required between the contiguous carriers must not be highly accurate for a low number of SMs [20], [21]. PSC also results in an even loss distribution among the SMs [21], [22]. For an MMC with N SMs per arm, N carriers per arm are needed and are shifted from each other by  $2\pi/N$  rad, which is done to eliminate the high frequency harmonic component in the arm current [23].

In PSC, the top arm and lower arm SM carriers are shifted from each other by  $\pi/N$  rad if N is even and by 0 if N is odd [24]. This allows for independent modulation of the upper and

the lower arm SMs and is referred to as the 2N + 1 scheme, as it results to 2N + 1 AC-side voltage levels. Furthermore, in this scheme the inserted number of SMs in the leg is not constant [25]. Its counterpart is the N+1 scheme, which is achieved by modulating the upper and the lower arms in a complimentary manner, i.e., the upper and lower arm carriers are shifted from each other by  $\pi$  rad [24]. The 2N + 1 scheme results into a lower total harmonic distortion (THD) of the AC-side voltage, owing to its higher number of levels which also means that the voltage steps are smaller [26]. It however results into higher SM capacitor voltage imbalances [25], which consequently leads to higher arm voltage imbalances, and in turn lead to higher circulating currents and SM capacitor voltage ripple. Furthermore, the eliminated harmonics from the AC-side voltage appear on the DC side [24]. The N+1 scheme ensures that a constant number of SMs is inserted across the leg, resulting to more balanced SM capacitor voltages, hence lower SM capacitor voltage ripple and circulating currents [25]. It however leads to a relatively higher AC-side voltage THD, as its number of levels is almost half of that of the 2N + 1 scheme [24], [26]. With the N + 1scheme, the AC-side voltage has an effective switching frequency of  $N \times f_{sw}$  while with the 2N + 1 scheme the effective switching frequency is  $2N \times f_{sw}$ , which has an influence on the size of the AC-side filter — if a filter is installed at all [22], [26]. In a leg, the modulation signals for the lower and for the upper arms are shifted from each other by  $\pi$  rad. This applies to both the 2N + 1 and the N + 1 schemes.

## 2.3.2 Modulation of the FB-MMC

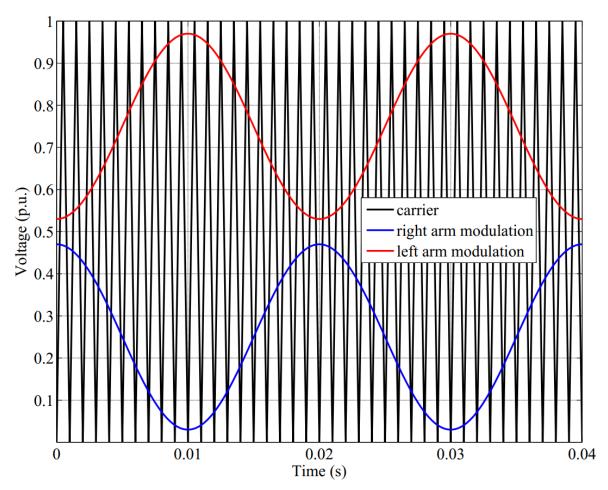

There are mainly two ways the FB-SM can be modulated. Although they both depend on a unipolar switching scheme, they have different performances.

The first method effectively utilizes only three switches during normal operation, while all switches come into play during blocking state [27]. During normal operation switches  $T_1$  and  $T_4$  are gated so that a positive capacitor voltage is inserted. To bypass the capacitor voltage, either switches  $T_1$  and  $T_3$  or  $T_2$  and  $T_4$  are turned on simultaneously (see Figure 2.1). To balance off voltage and current stress among switches, the bypassing may alternately utilize upper and bottom switches on a cycle-by-cycle basis. Even then, switches  $T_2$  and  $T_3$

would be operated only half the time switches  $T_1$  and  $T_4$  would be. In fact, if bypassing were to utilize only the bottom switches, switch  $T_3$  and its antiparallel diode would be idle all the time during normal operation of the MMC converter. Thus, this scheme has a poor utilization of semiconductor devices. In addition, the semiconductor devices operate at the same frequency as those in a HB do. The only advantage it brings over the HB-SM is that it can block a DC-side fault current.

The second scheme requires two different modulating signals for the left and right arms [28], as in Fig 2.3. This scheme automatically balances the voltage and current stress among the semiconductor devices and effectively doubles the switching frequency. This means that the switching frequency in the HB-SM for the same effective switching frequency. This should significantly reduce the switching losses.

**Figure 2.3.** A unipolar switching scheme for independent modulation of the left and the right arms of the FB-SM. The top signal modulates the left arm while the bottom signal modulates the right arm.

## 2.3.3 Submodule capacitor balancing control

Apart from the main power control achieved through the current and the DC bus voltage controllers, SM capacitor voltage balancing control is necessary for the working of the MMC. If the modulation scheme or the conditions of operation do not guarantee self-balancing of the SM capacitor voltages an auxiliary control loop must be added to the main control loop to balance the SM capacitor voltages.

The two common SM capacitor voltage balancing methods are the capacitor voltage sorting [12], [29], which is especially used in converters with a high number of SMs, and the

classical, decentralized closed loop control, which adjusts each SM modulation signal accordingly [30 - 32]. The classical closed loop control is used only with the PSC modulation scheme, and has better controllability if the switching frequency is high enough [17]. Although the sorting method is suited for high number of SMs, the computational burden associated with the sorting process increases with an increasing number of SMs, calling for more efficient sorting algorithms [33]. On the other hand, the decentralized closed loop control method does not have an elaborate method in the literature of determining the controller gains, as the associated transfer functions have not been derived. The pioneering literature on the decentralized closed loop control method admits to the difficulties of establishing these constants and promises to address it in a separate publication [30], which to the date of publication of this dissertation, to the best knowledge of the author, such a publication does not exist yet. The constants have been quoted to remain the same in some studies, regardless of the varying operating conditions, while other studies claim to have obtained them through simulations [22], [34].

The classical SM capacitor voltage balancing control aims to achieve the following objectives, as originally described and illustrated in [31] and [32]:

- (i) Individual SM capacitor voltage balancing, whereby each SM capacitor voltage follows the reference voltage given by  $V_{dc}/N$ .

- (ii) *Arm voltage balancing*, whereby the average voltages across the two arms in the leg are forced to follow each other so that there is minimal discrepancy between them.

- (iii) Leg average voltage balancing (averaging), whereby the average voltage across the leg is forced to equal the DC bus voltage.

The control aims at reducing the circulating current, especially the second order harmonic, which is the most significant among all the harmonics. The other harmonics are small and can be ignored, depending on the application.

The circulating current can be thought to result from any one or more of the following: an imbalance between the average voltages across the two arms in a leg; an imbalance between any two legs; an imbalance between a leg and the DC bus [35].

The various control loops that may be used in combination to achieve capacitor voltage balancing and to suppress the circulating current are described and illustrated below.

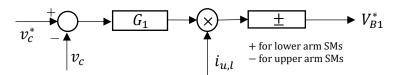

## 2.3.3.1 Individual SM capacitor voltage balancing loop

Figure 2.4. Individual SM capacitor voltage balancing. Adapted from [31], © 2011 IEEE.

In Figure 2.4,  $v_c^*$  is the reference voltage given by  $V_{dc}/N$ ,  $v_c$  is the sensed capacitor voltage of the SM in question,  $G_1$  is the controller,  $i_{u,l}$  is the arm current (upper arm current for upper SMs and lower arm current for lower arm SMs), and  $V_{B1}^*$  is the reference control voltage generated by this loop that goes into the modulation of the particular SM capacitor voltage.

## 2.3.3.2 Arm voltage balancing loop

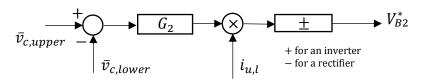

Figure 2.5. Arm voltage balancing. Adapted from [31], © 2011 IEEE.

As explained previously, this controller (see Figure 2.5) forces the average of the lower SM capacitor voltages to follow the average of the upper SM capacitor voltages, so that the voltages across the two arms in a leg are balanced. Thus,  $\bar{v}_{C,upper}$  is the average of the upper SM capacitor voltages while  $\bar{v}_{C,lower}$  is the average of the lower SM capacitor voltages.

## 2.3.3.3 Leg average voltage balancing (averaging) loop

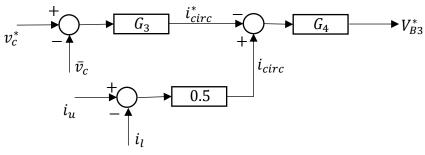

Figure 2.6. Average voltage balancing. Adapted from [31], © 2011 IEEE.

The outer voltage loop sets a reference for the inner loop to follow. In this controller (see Figure 2.6)  $\bar{v}_C$  is the average of all SM capacitor voltages in the leg,  $i_u$  and  $i_l$  are the upper and lower arm currents, respectively. The outer loop shares the reference  $v_c^*$  with the individual voltage balancing loop of Figure 2.4, since the required average of all the SM capacitor voltages in the leg equals the required voltage for a single SM capacitor.

## 2.3.4 Circulating Current Suppression Controller (CCSC)

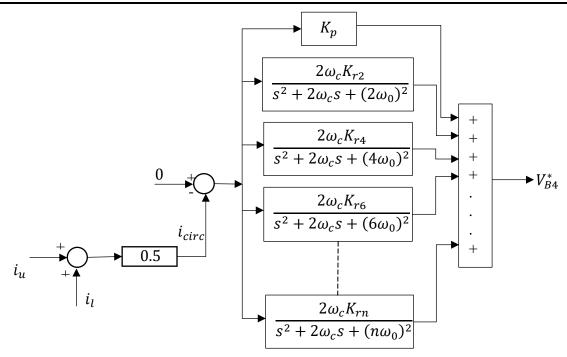

Ideally, the leg average voltage controller should regulate the circulating current such that the power processing frequencies (DC and the fundamental frequency) are amplified while the harmonics are suppressed. Nevertheless, for suppression of the harmonics, a dedicated separate controller can be implemented for better results. Such a controller is a Quasi Proportional Resonant (QPR) controller, illustrated in Figure 2.7. It is preferred in application over the proportional resonant (PR) controller for better digital realization and noise rejection. The QPR controller allows targeting specific frequencies, with a bandwidth  $\omega_c$  around such a frequency. The narrow bandwidth allows only those frequencies of interest to be controlled. Such frequencies, whose components are to be suppressed, are the harmonics  $\omega_0$ ,  $2\omega_0$ ,  $4\omega_0$ ,  $6\omega_0$ , ...,  $n\omega_0$ . The harmonics beyond the  $n^{th}$  order are considered insignificant. The reference to this controller is set to 0 [36].

**Figure 2.7.** Circulating Current Suppression Controller (CCSC). Adapted from [36], © 2012 IEEE.

## 2.4 THE MMC IN HVDC SYSTEMS AND THE HVDC PROTECTION OVERVIEW

Before addressing the challenge of HVDC protection and how the MMC architecture fits in, it is important to address the concept of the PET and how it utilizes the MMC architecture.

## 2.4.1 The Power Electronic Transformer and its role in HVDC protection

The main reason the alternating current (AC) power transmission and distribution system has been widely adopted compared to the direct current (DC) counterpart is the voltage transformation ease and convenience brought about by the line frequency transformer (LFT) used in the AC systems [37]. In the LFT, the output voltage directly follows the input voltage and the input current directly follows the output current. With this behaviour, a fault that occurs on either side of the transformer directly affects the other side [38], [39]. Adoption of the DC transmission system would require AC-DC, DC-DC and DC-AC converters that can handle high voltage levels in order to reduce copper losses in the long-distance transmission conductors. For many years, however, the semiconductor technology for such

high voltages has been immature. With the maturing of the semiconductor technology, DC transmission systems, known as the HVDC systems, are slowly replacing AC counterparts for long-distance transmission. Even better, the so called multiterminal HVDC systems bring about flexibility by interconnecting asynchronous AC systems and DC systems of different voltage levels. The distance above which the HVDC transmission systems are more economical than their AC counterparts is above 500-800 km for overhead lines and about 50 km for marine cables [1].

The major challenge in HVDC systems is the DC-side fault detection and isolation. Since a DC voltage signal does not have a zero-crossing, circuit breakers would need to operate at high voltages, which is uneconomical [6]. Research is ongoing to design and manufacture economical circuit breakers to use in HVDC systems. The other alternative is to use transformerless MMCs with fault blocking capability SMs. However, such converters do not galvanically isolate the input and the output sides, which would make other systems connected to the converter, such as the battery energy storage system (BESS), vulnerable [40].

The LFT equivalent for the DC systems is essentially a galvanically isolated DC-DC converter, called the power electronic transformer (PET), also called the solid-state transformer (SST) or simply the smart transformer (ST). It is constituted of several stages, including rectification, inversion, and galvanic isolation. The voltage transformation through switching action and the galvanic isolation prevent direct communication of the input and the output side voltage and current signals [41]. If there is a fault on the output side, the transformer simply reduces the output voltage, with the effect that the input side voltage is maintained and can service other lines [37]. Instead of transforming voltage at the line frequency, the PET does so in the medium frequency range, which reduces the physical footprint and the magnetic material requirement [42], [43]. Using the wide bandgap (WBG) semiconductor devices, General Electric (GE) has been reported to develop a PET prototype that is only 30% in weight of the equally rated LFT, with the volume being 50% of the equivalent dry-type LFT [44]. The size reduction that was achieved is in line with what has

been reported in the literature [45]. The limiting factor for the switching frequency of the PET are the switching losses.

The PET has its weaknesses and strengths against the LFT. When the PET was conceptualized, it would not even be prototyped at relevant power and voltage levels mostly because of the cost, especially that of the semiconductors required for its construction. The limited topologies available with which to design the PET also did not allow scaling up of power and voltage as these topologies subjected semiconductors to relatively higher voltage and current stress levels, [46], [47]; something modern topologies such as multilevel converters can fairly mitigate [10], [48]. But the same cannot be said of the cost of the PET today since the cost of semiconductors has dropped significantly. By the generally accepted Moore's law, the price of semiconductors is expected to continue decreasing with time, pushing the price of PET even further down. Also, once the PET is widely accepted, its cost will be expected to go further down due to the mass-manufacturing effect [42]. Furthermore, the construction cost of the PET is competitive because of the operation at relatively higher frequencies, which in turn demands smaller volume of magnetic materials.

Generally, due to the relatively more complex nature of the PET, it is viewed as far less reliable than the LFT. But the architecture of the PET has a significant implication on the reliability of the PET. If it is constructed based on the modular multilevel converters, the PET will have redundant switching states that would allow bypassing failed submodules. The failed submodules can be reported by the PET for maintenance since measurements and sensing are part of the normal operation of the PET. The measurements can also be used to predict the probability of failure of the components. This information can be used to plan interventions before the failure happens. All this significantly improves the reliability of the PET [37].

In terms of efficiency, the PET, which for a long time has been based on the silicon (Si) semiconductors, has been reported to bear a lower efficiency than that of the LFT [45], [47]. However, with the introduction of WBG devices, the PET stands to achieve efficiencies comfortably above 98% as the WBG device technology continues to improve [44], [49].

Non-linear loads inject a significant amount of current harmonics into the transformer. This has a significant effect on the efficiency of the LFT since the primary side current traces the secondary side current. If the LFT is replaced by the PET, the effect of the non-linear loads on the efficiency of the transformer would be minimal since the input side current does not reflect the output side current. In terms of power quality and protection, this means that the primary side is isolated from the secondary side [50], [51].

Since PETs adjust voltage through switching, their transformation ratio is continuously variable within a given range, unlike in the LFTs whereby this ratio is fixed by the transformer windings. This means that the PETs do not require any mechanical tap-changers, unlike the LFTs. The tap-changing functionality is instantaneously achieved through switching [42], [46], [47].

Apart from voltage transformation, the PET helps to improve the general system power quality. An example is the handling of non-linear loads as alluded to above. Furthermore, since the PET is integrated with active rectifiers, it helps to improve the system's power factor. Also, the PET handles unbalanced loads better than the LFT, in the same way it handles distortions and non-linear loads [51].

Thus, the PET has an edge over the LFT in terms of weight and volume, with its efficiency closely matching that of the LFT, especially if the newer more efficient and more capable semiconductor devices known as the WBG semiconductor devices are considered [44], [49], [52]. However, although a conclusive research on the cost comparison of the PET and LFT has not been published yet, projections do favour the LFT when the comparison is based on isolated units, that is, the PET and the LFT compared without considering the impact of each at a system level [52]. If the projections are based on a system-level comparison, it is well understood that the PET would eliminate the need of many expensive components/functions such as reactive power support (e.g. flexible AC transmission system (FACTS) devices such as the static synchronous compensator (STATCOM) and the static volt-ampere reactive compensator (SVC), to mention a few) [42]. The reason is that the modern PET is based on voltage source converters (VSC), let alone the fact that it is actively controlled, as all other

systems based on power electronics usually are. VSCs enable grid power reversal without reversing the voltage polarity [2], which greatly enhances the controllability of the grid [53]. Equally important, the PET stands to eliminate the bulky and expensive DC-side circuit breaker (CB), if the PET is enabled with the DC-side blocking capability [4], [54]. All this would give the PET a pronounced advantage over the LFT.

If the PET uses the MMC architecture, it has the potential to incorporate distributed sources such as solar and wind electricity generators. This is because its high power-density makes it able to accommodate many inputs in a confined space. Its flexible control makes the PET able to manage distributed sources, distributed storage units, and AC-DC interconnections. Due to its bidirectional power supply, the PET enables energy exchange between the grid and the storage units [39], [55], [56]. This is an advantage of the PET over the LFT.

There is a substantial literature on the adoption of the PET in low and medium voltages, especially in the smart grid area. The future renewable electric energy delivery and management (FREEDM) system, developed by a consortium of universities in the US, is being developed to use the PET together with fault isolation devices (FIDs) in the distribution system [57]. However, FIDs are conceptual devices in research and development. The FID prototypes that have been tested have been shown to be power inefficient hence uneconomical. Also, they cannot be extended to high voltage use as their voltage and current handling capabilities are limited [58].

## 2.4.2 Overview of the HB and the FB converters as submodules for HVDC-PET-MMC

The DC-side fault isolation and blocking in HVDC systems is an important research topic. The MMC submodules with fault-blocking capability such as the FB and its family have for a long time been deemed lossier than the conventionally used HB-SM [9]. However, new literature on the subject suggest that the FB may not be that less power efficient compared to the HB, especially if one considers that FB devices are operated at half the switching frequency in the HB counterpart for the same effective switching frequency (due to the

unipolar switching scheme), and are subject to lower blocking voltages if the converter is operated in the overmodulation region [59], [60]. This reduces the switching losses in the FB semiconductor devices as these losses are directly proportional to the device switching frequency and the blocking voltage [61]. Also, SMs capable of inserting a negative voltage like the FB-SM have been reported to reduce the SM capacitor ripple [59], [62], driving down the arm circulating currents which drives the system losses further down. Also, the DC-side fault blocking capability of the FB promises elimination of the expensive and bulky DC-CB [4]. All these premises call for a thorough comparison between the HB-based SMs and their FB-based counterparts. In the meantime, new research has been published proposing a control method that enables HB-based MMCs to ride through DC-side faults much like FB-based MMCs, eliminating the need to block the converter during a DC-side temporary fault [54]. However, the nature of the HB-SM does not allow it to block DC-side permanent fault currents. Nevertheless, it has raised the competitiveness of the HB-SM, making the comparison more interesting and probably much more important than before.

# 2.4.3 The feasibility of the Power Electronic Transformer for fault isolation in an HVDC system

Although the focus of this research is not exactly on protection, one of the required important features of the HVDC transmission line is the ability to protect the system against the DC-side fault currents. Thus, a short overview of the methods proposed/developed for this purpose would be helpful to paint a picture of the state-of-the-art HVDC protection and the influence of the PET and the choice of SM on protection.

The voltage source converter HVDC (VSC-HVDC) systems are, by design, vulnerable to faults [3]. This is because, unlike the line-commutated converter HVDC (LCC-HVDC) counterpart, they do not have any DC inductors to limit a fault current. This means that some faults in VSC-HVDC would not be necessarily perceived as faults in LCC-HVDC. Due to low line inductance the current rises rapidly and the maximum it can rise to is only 2 p.u., due to converter limitations [3], [38], [57], [63]. Another important difference between LCC and VSC is that in VSC the diodes antiparallel to the switches keep feeding the fault current

even after the switches are blocked [4]. The speed at which the fault current rises and the maximum to which it can get imposes a demand for fast fault detection and location methods, and fast-acting circuit breakers. Another requirement is due to the reason that a DC current does not have a zero-crossing. This requires the circuit breaker to be able to dissipate all the energy it absorbs during breaking [64]. Put another way, the circuit breaker must be able to drive the current to zero before breaking. AC breakers meet none of these requirements. They also shut down the entire system, even for single line to ground faults in which the system could continue operating on one pole using the ground as the return path [3].

Some of the VSC-HVDC fault detection and location methods are briefly described below:

- a) Current differential protection: A selective protection method where current is measured at both ends of a line using relays [65]. The relays communicate data to each other. They then calculate the current difference between the two ends. If the difference exceeds a given threshold for a set amount of time, a fault is registered. However, it needs a communication link and data processing, which in turn brings about transmission and processing delays, as well as reliability concerns since its reliability depends on the reliability of the telecommunication infrastructure [66].

- b) Cable directional protection: An alternative to the current differential protection where only the direction of the fault current is communicated to the other relay. The trip commands are based on the comparison of the directions. Since only the sign of the current is communicated, the method is more robust. It, however, suffers from the same drawbacks as the current differential [67].

- c) Overcurrent and Undervoltage: Since faults are characterized by overcurrent and undervoltage, either of the two can be used to detect a fault. Only local measurements are used, eliminating the need for a communication link. This method cannot distinguish between faults internal and external to the converter, thus, it lacks selectivity. However, techniques exist that can relate local measurements to the distance of the fault [68 70], although the accuracy of the model affects their precision [6].

d) Travelling-wave-based techniques: These methods analyze the current and voltage wavefronts propagating from the fault location to the line-ends, according to the travelling wave theory on transmission lines. Since the waves travel at speeds close to that of light, these techniques are fast although several successive wavefronts must be measured in order to draw a conclusion on the presence of a fault. Their shortcoming comes when the transmission lines cover a long distance as the wave magnitudes significantly deteriorate [71].

- e) Voltage and current derivatives: Similar to the overcurrent/undervoltage method but derivatives of current and voltage are used rather than the magnitudes. This renders them faster. But they are affected by the line distance and the line/converter impedance. The latter affects the selectivity of this method. In particular, methods based on voltage/current derivatives may fail to distinguish between internal and external faults [71 73].

- f) Wavelet transform: A signal processing technique based on time-scale (not time or frequency domain but simultaneously both) is applied to the travelling wave signals [4], [74]. It works by detecting abrupt changes such as the transients associated with a fault current, and it can discriminate between fault signal-components and non-fault transients. However, it must be combined with other fault-detection methods for accurate results.

- g) Hand-shaking method: This method is used to ensure selectivity in multiterminal HVDC (MT-HVDC) systems. Each station converter constantly monitors current in all branches emanating from it. When a fault-level current is recorded, the converter opens a breaker on the line with the highest current away from the converter [4]. This means some lines without a fault will be opened. Even though the healthy lines are reconnected after a reclose process, the momentary isolation of healthy lines is a significant drawback of this method. Furthermore, the method assumes that fast DC switches are available. The DC switches cannot break the fault current, only can isolate the faulty lines after all the AC breakers associated with the converter trip [3]. It is, however, worthy noting that DC switches are more economical than DC breakers [75]. Furthermore, the method is slow and does not satisfy the reliability requirements [76].

h) Converter arm currents: This method aims at protecting the converter. It measures the arm currents of the station modular multilevel converter (MMC) and blocks the converter if the value exceeds a threshold value. However, it cannot locate the fault [6].

- i) Inductive fault current limiters: Inductors are connected at the station terminals to increase the fault impedance, which slows down the rate of rising of the fault current hence giving time for slow breakers to act. However, the inductors add to the cost, weight and power losses [6].

- j) Artificial-Intelligence-based methods: These methods depend on algorithms that are trained with massive fault data so that they can take appropriate action in the future. However, they need enormous data for the fault scenarios used in training to be comprehensive. They are also complex to develop and have to be adapted to different converter architectures such as two-level, three-level, etc. [4], [76].

Some of the technologies and methods used to block faults and isolate faulty lines are briefly described below:

1) HVDC system protection with AC devices: Instead of breakers acting on the DC side, they act on the AC side of the grid. AC protection devices are less expensive than DC counterparts, they have a shorter lead time, their technology is more mature, and they are more familiar. However, they take longer to interrupt a fault due to their mechanical restrictions. They also tend to shut down the entire converter system, even for ground faults, which could be easily isolated. They are also inconvenient in multiterminal HVDC systems [3], [77], [78].

Protection can be achieved by using a combination of AC circuit breakers and fast action DC switches in a method known as "handshaking" as described above.

Fuses could be used to protect the multiterminal HVDC systems, but they cannot tell apart between temporary and permanent faults – all faults are considered permanent. They are only used as the last resort when other protection schemes fail [3].

- 2) HVDC system protection with DC devices: DC protection devices act faster than their AC counterparts and can isolate the faulted sections without closing the entire system.

- a) DC circuit breaker equipment: Double-ended DC transmission systems use the ability of a thyristor to quickly cut off current to block the DC-side fault current. If the same process is used in multiterminal HVDC systems, however, it would require the entire multiterminal HVDC system to disconnect. Use of AC-side breakers would not be effective to protect the converters as these breakers are not fast enough. Thus, a high-voltage DC circuit breaker needs to be installed on the DC side, if the converters do not have the DC-side fault current blocking capability. Such DC breakers would significantly reduce the recovery time and shutting down the entire multiterminal HVDC system would not be necessary [3]. Since DC current does not have a natural zero-crossing, it should be forced to zero before a circuit breaker can act. Other issues that may arise before the current goes to zero, such as the arc time and overvoltage, should also be considered. Nevertheless, there are two main technologies for DC breakers: superposition oscillation current method and current transfer method.

The superposition oscillation current method utilizes the negative resistance characteristic of the arc to create an artificial zero of the oscillating current. However, the negative resistance characteristic becomes less obvious as the amplitude of the oscillating current increases, placing a limit on the circuit breaker's current capacity. Thus, it is not guaranteed that the breaker will counter the fault.

Current transfer method counters the fault current by discharging a capacitor in a direction such as to drive down the fault current. This method can break the DC-side fault current with a shorter break time compared to the superposition oscillation current method, but it is more complex, which makes it less reliable [79].

CHAPTER 2 LITERATURE STUDY

b) IGBT circuit breakers: These utilize the blocking capability of the solid-state device. They can block only the DC-side faults, not faults on the converter side. They are used together with fast action DC switches, which are used to isolate the faulted line after the IGBT blocks the fault. This strategy is more effective than the AC devices but also more expensive [3], with the cost close to half the total cost of the converter station [7].

- c) Converter embedded devices: These are installed inside the voltage source converters to detect and isolate DC-side faults. They eliminate the use of additional devices, which reduces the converter footprint. However, a converter redesign is required [80].

- 3) Converters with fault blocking capability: Some converters have the capability to insert either a positive or negative voltage into the circuit. They are referred to as bipolar converters. For example, the FB converter inserts a negative voltage when all its four semiconductor switches are blocked [6]. The path of the current is such that the converter inserts a negative voltage. If a station MMC converter is based on a bipolar converter, it has the capability to block a DC fault by inserting a negative voltage. This voltage acts against the fault and eventually drives it to zero. If two such converters at the ends of a faulted line insert negative voltages and isolate the line through IGBT blocking, then the need for a DC breaker is eliminated. This has been asserted in the literature [4]. It is claimed that the reason the FB-SM and its derivatives are dismissed for use in HVDC systems is the increased semiconductor device count, increased power losses, and initial investment cost, compared to the widely accepted half bridge HB-SM [6 - 9], [81-85]. But it has been realized that this justification is not necessarily objective. For example, the FB-SM needs to operate at only half the effective switching frequency due to the nature of the unipolar switching scheme used [60]. This drives down switching losses.

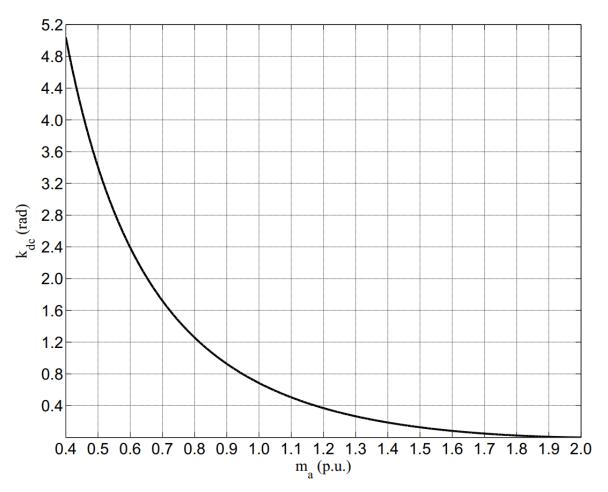

Furthermore, insertion of a negative voltage allows overmodulation, which means that the peak of the AC-side voltage gets higher than half of the DC-side voltage. One of the advantages of this kind of operation is the reduction or even elimination of circulating energy between the upper and lower arms, as well as SM capacitor voltage ripple reduction [59], [62]. Conversely, it can be viewed as a way to operate the converter at a lower DC bus

CHAPTER 2 LITERATURE STUDY

voltage either deliberately or as an optimal method in case of fluctuating energy systems such as wind power generator systems [86]. Deliberately operating the converter at low DC bus voltages through overmodulation implies lower SM capacitor voltages, which in turn implies lower blocking voltages for semiconductor devices. The advantages are the smaller-sized SM capacitors and semiconductor devices and reduced switching losses [60].

Although these observations do not arrive at a generalized conclusion that FB-based MMCs are competitive against or better than the HB-based MMCs, they call for an objective comparison between the two SMs as potential candidates for the HVDC-MMC.

### 2.5 CHAPTER SUMMARY

In this chapter an overview of the modular multilevel converter, the power electronic transformer, and high voltage DC transmission line protection was provided.

In Section 2.2 the topology and the basic operation of the modular multilevel converter was explored.

In Section 2.3 the modulation and control of the modular multilevel converter was explored. The modulation of the half-bridge and the full-bridge submodules was reviewed. It was seen that the control involved the main power as well as the submodule capacitor voltage balancing. However, it was found that there is not yet an elaborate method to calculate the control gains/constants for the submodule capacitor voltage balancing control loops if the classic control method is used, as opposed to the sorting method.

In section 2.4 the power electronic transformer and its feasibility to replace the line frequency transformer in the transmission lines was explored. It was found that although the power electronic transformer may not outperform the line frequency transformer when the two are compared as standalone units, it may do so if the system-level advantages it brings are considered. Such advantages are the grid stability and reduction or elimination of some of the grid components or functions that are used together with the line frequency transformer e.g. static synchronous compensators. The power electronic transformer also has

CHAPTER 2 LITERATURE STUDY

a smaller size and weight compared to the line frequency transformer, which may be critical requirements for some installations such as offshore wind farms. A conclusive comparison between the power electronic transformer and the line frequency transformer would be a good research problem.

It was also found that the half-bridge submodule has been deemed better than the full-bridge submodule for use in the high voltage DC modular multilevel converter but some of the converter-level and system-level advantages the full-bridge submodule offers have been overlooked. It has been concluded that if the comparison must be a fair one, all those advantages must be considered. Such advantages are the ability of the full-bridge submodule to operate at half the switching frequency of the half-bridge for the same effective switching frequency which reduces switching losses, the ability of the full-bridge to operate in the overmodulation region which reduces the components size and reduces submodule capacitor ripple, and the ability of the full-bridge to block a DC-side fault which eliminates the need for the expensive and bulky DC circuit breaker.

## CHAPTER 3 MODELING OF THE MODULAR MULTILEVEL CONVERTER

### 3.1 CHAPTER OBJECTIVES

In this chapter the modeling of the MMC is carried out, starting with the basic operation of the converter, then the models pertaining to different control objectives of the MMC. The modeling lays the foundation for the analysis, design, and control of the MMC, to be carried out in subsequent chapters.

### 3.2 BASIC OPERATION OF THE MMC

With reference to Figure 2.2, the KVL equations of the MMC can be written as follows:

$$-\frac{1}{2}v_{dc}(t) + \sum_{i=1}^{N} v_{c_{mod},i}(t) + L_{arm} \frac{di_{u}(t)}{dt} + R_{arm}i_{u}(t) + v_{ac}(t) = 0,$$

(3.1)

$$-\frac{1}{2}v_{dc}(t) + \sum_{j=N+1}^{2N} v_{c_{mod},j}(t) + L_{arm}\frac{di_l(t)}{dt} + R_{arm}i_l(t) - v_{ac}(t) = 0,$$

(3.2)

whereby  $v_{c_{mod},j}$  is the modulated SM capacitor voltage corresponding to the  $j^{th}$  SM and it appears on the AC side of the SM, i.e., across the terminals with the voltage  $v_{SM}$  in Figure 2.1 and Figure 2.2. KCL gives

$$i_{ac}(t) = i_l(t) - i_u(t).$$

(3.3)

The circulating current is that which circulates among a leg and the DC bus and does not appear on the AC side. It is defined as

$$i_{circ}(t) = \frac{i_l(t) + i_u(t)}{2}.$$

(3.4)

The third KVL equation is obtained as

$$-v_{dc}(t) + \sum_{j=1}^{2N} v_{c_{mod},j}(t) + 2R_{arm}i_{circ}(t) + 2L_{arm}\frac{di_{circ}(t)}{dt} = 0.$$

(3.5)

If  $\sum_{j=1}^{N} v_{c_{mod},j}$  is named  $v_u$ ,  $\sum_{j=N+1}^{2N} v_{c_{mod},j}$  is named  $v_l$ , and  $\sum_{j=1}^{2N} v_{c_{mod},j}$  is named  $v_{leg}$ , (3.1) becomes (3.6), (3.2) becomes (3.7), and (3.5) becomes (3.8).

$$-\frac{1}{2}v_{dc}(t) + v_u + L_{arm}\frac{di_u(t)}{dt} + R_{arm}i_u(t) + v_{ac}(t) = 0,$$

(3.6)

$$-\frac{1}{2}v_{dc}(t) + v_l + L_{arm}\frac{di_l(t)}{dt} + R_{arm}i_l(t) - v_{ac}(t) = 0.$$

(3.7)

$$-v_{dc}(t) + v_{leg} + 2R_{arm}i_{circ}(t) + 2L_{arm}\frac{di_{circ}(t)}{dt} = 0.$$

(3.8)

Accordingly,

$$v_{leg}(t) = v_l(t) + v_u(t)$$

$$= v_{dc}(t) - R_{arm} (i_l(t) + i_u(t)) - L_{arm} \frac{d}{dt} (i_l(t) + i_u(t))$$

$$= v_{dc}(t) - 2R_{arm} i_{circ}(t) - 2L_{arm} \frac{d}{dt} i_{circ}(t).$$

(3.9)

In a balanced three phase MMC the DC bus current divides equally among the three legs. The circulating current consists of this DC component and the even harmonics of the fundamental component [87], i.e.,

$$i_{circ}(t) = \frac{1}{3}i_{dc}(t) + \sum_{n=2}^{\infty} I_n \sin(n\omega t + \theta_n),$$

$$n = 2, 4, 6, ...$$

(3.10)

In (3.10),  $\theta_n$  is the phase angle between the harmonic and the reference signal  $v_{ac}$ . Using (3.3) and (3.4) to solve for  $i_l$  and for  $i_u$  gives

$$i_l(t) = i_{circ}(t) + \frac{1}{2}i_{ac}(t)$$

(3.11)

and

$$i_u(t) = i_{circ}(t) - \frac{1}{2}i_{ac}(t)$$

(3.12)

Substituting (3.10) in (3.11) and in (3.12) gives

$$i_{l}(t) = \frac{1}{3}i_{dc}(t) + \frac{1}{2}i_{ac}(t) + \sum_{n=2}^{\infty} I_{n}\sin(n\omega t + \theta_{n})$$

(3.13)

and

$$i_u(t) = \frac{1}{3}i_{dc}(t) - \frac{1}{2}i_{ac}(t) + \sum_{n=2}^{\infty} I_n \sin(n\omega t + \theta_n),$$

(3.14)

respectively, again with n = 2, 4, 6, ...

Subtracting (3.6) from (3.7) gives (3.15).

$$v_{l}(t) - v_{u}(t) + R_{arm}(i_{l}(t) - i_{u}(t)) + L_{arm}\frac{d}{dt}(i_{l}(t) - i_{u}(t)) - 2v_{ac}(t) = 0$$

$$\Rightarrow \frac{v_{l}(t) - v_{u}(t)}{2} + \frac{1}{2}R_{arm}i_{ac}(t) + \frac{1}{2}L_{arm}\frac{d}{dt}i_{ac}(t) - v_{ac}(t) = 0$$

$$\Rightarrow v_{refl}(t) + \frac{1}{2}R_{arm}i_{ac}(t) + \frac{1}{2}L_{arm}\frac{d}{dt}i_{ac}(t) - v_{ac}(t) = 0$$

(3.15)

whereby

$$v_{refl}(t) = \frac{v_l(t) - v_u(t)}{2}$$

(3.16)

and is known as the internal EMF of the converter or the reflected DC bus voltage, and it is essentially the inverted DC bus voltage. Thus, the internal AC voltage of the converter can be conceptualized as a result of the switching matrix acting on the DC bus voltage. If the switching function is represented by  $\psi$ , then

$$v_{refl,k}(t) = \psi_k(t)V_{dc}, \quad k \in \{a, b, c\}$$

(3.17)

whereby k represents the phase of the signal. Ideally  $\psi$  is a pure sinusoid. In practice it is a combination of a pure sinusoid and harmonics. In an MMC the harmonics are exacerbated by limited number of levels and significant size of voltage steps. The higher the number of levels and the smaller the steps the closer the switching function and the resulting internal

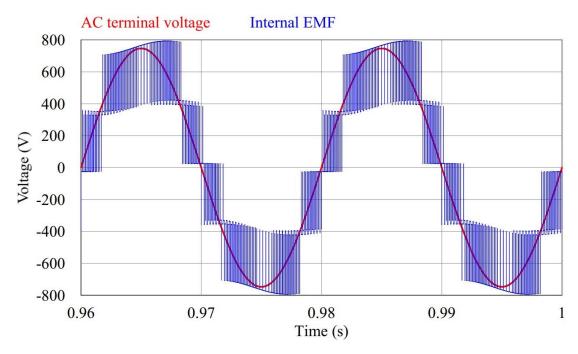

EMF are to pure sinusoids. From a perspective of an MMC inverter,  $v_{refl}$  is filtered by the arm inductors to give a much smoother voltage  $v_{ac}$  at the AC terminals, as is evident from (3.15). The simulated  $v_{ac}$  and  $v_{refl}$  are shown in Figure 3.1.

The average of  $v_{leg}$  is controlled to closely match the DC bus voltage average  $V_{dc}$ , with the small difference between  $v_{leg}$  and  $v_{dc}$  appearing across the arm inductor, as expressed by (3.9). Thus, if the AC variations in  $v_{leg}$  are ignored,  $v_{leg}(t) = V_{leg}$ . Ideally, the voltages  $v_{refl}$  and  $V_{leg}$  are related by [88]

$$v_{refl}(t) = \frac{1}{2} m_a V_{leg} \sin \omega t \tag{3.18}$$

whereby  $m_a$  is the modulation index defined as

$$m_a = \frac{2V_{ac}}{V_{dc}} \tag{3.19}$$

Equation (3.9) can be rewritten as

$$V_{leg} = v_l(t) + v_u(t) (3.20)$$

Solving (3.16) and (3.20) for  $v_l$  and  $v_u$  then substituting (3.18) gives

$$v_l(t) = \frac{1}{2}(1 + m_a \sin \omega t)V_{leg}$$

(3.21)

and

$$v_u(t) = \frac{1}{2} (1 - m_a \sin \omega t) V_{leg}.$$

(3.22)

The functions  $(1 + m_a \sin \omega t)/2$  and  $(1 - m_a \sin \omega t)/2$  are equivalent to the SM quantities waveform duty ratio functions, for the lower and the upper arm SMs, respectively. Examples of such quantities are the SM output voltage and the SM capacitor current. This is implied from the analysis carried out in the literature, whereby these functions are used as modulation functions to synthesize capacitor voltages from the arm currents [89], as well as synthesize the SM AC-side voltage from its DC-side voltage [90]. The averages of these functions are 0.5, implying the average waveform duty of MMC quantities is 0.5.

**Figure 3.1.** Simulated AC terminal voltage and the internal EMF.

### 3.3 CURRENT CONTROL MODEL

The voltage  $v_{ac}$  is given by

$$v_{ac}(t) = e(t) - \left(R_{grid} + R_{filter}\right)i_{ac}(t) - \left(L_{grid} + L_{filter}\right)\frac{d}{dt}i_{ac}(t), \tag{3.23}$$

so that (3.15) becomes

$$e(t) = v_{refl}(t) + \left(\frac{1}{2}R_{arm} + R_{grid} + R_{filter}\right)i_{ac}(t) + \left(\frac{1}{2}L_{arm} + L_{grid} + L_{filter}\right)\frac{d}{dt}i_{ac}(t).$$

$$(3.24)$$

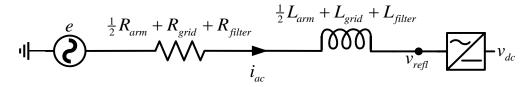

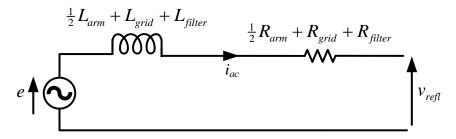

Figure 3.2 illustrates (3.24), with the rectification stage also shown for the sake of converter completeness.

**Figure 3.2.** Equivalent of the AC-side and arm inductances, with their parasitic resistances. Adapted from [91], © 2015 IEEE.

Department of Electrical, Electronic and Computer Engineering University of Pretoria

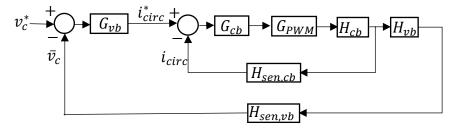

The converter current control model to be used for the controller design is then illustrated in Figure 3.3. The model does apply to other VSCs other than the MMC [21], [92], [93].

**Figure 3.3.** Current control model of a voltage source converter.

To simplify the controller design, vector control can be opted for. In this control scheme the circuit variables in the abc stationary-frame are transformed to the dq synchronous-frame. The dq frame is formed by two axes: the direct and the quadrature, which are  $90^{\circ}$  apart with the quadrature axis leading. The active power can be processed on either of the axes, with the reactive power being processed on the other axis. In the subsequent analysis, for simplicity, the subscript ac is dropped from  $i_{ac}$  and refl is dropped from  $v_{refl}$ .

A three-phase system can be transformed into an equivalent two-phase system as follows

$$v_{\alpha}(t) + jv_{\beta}(t) = \frac{2}{3}K\left(v_{\alpha}(t) + v_{b}(t)e^{j\frac{2\pi}{3}} + v_{c}(t)e^{j\frac{4\pi}{3}}\right)$$

(3.25)

with K being the scaling constant according to the type of transformation adopted, as indicated in Table 1 [93].

**Table 3.1.** Three-phase to two-phase transformation constants.

| Type of transformation | Value of K   |

|------------------------|--------------|

| Amplitude invariant    | 1            |

| RMS-value invariant    | $1/\sqrt{2}$ |

| Power invariant        | $\sqrt{3/2}$ |

For the amplitude invariant transformation,

$$\begin{bmatrix} v_{\alpha} \\ v_{\beta} \end{bmatrix} = \begin{bmatrix} \frac{2}{3} & -\frac{1}{3} & -\frac{1}{3} \\ 0 & \frac{1}{\sqrt{3}} & -\frac{1}{\sqrt{3}} \end{bmatrix} \begin{bmatrix} v_{a} \\ v_{b} \\ v_{c} \end{bmatrix}.$$

(3.26)

The signals  $v_{\alpha}$  and  $v_{\beta}$  are still AC. They are further transformed into a synchronous reference frame so that the resulting signals are DC. If  $\theta$  is the instantaneous angle between the direct-axis and the  $\alpha$ -axis, then the dq signals are obtained as follows

$$\begin{bmatrix} v_d \\ v_q \end{bmatrix} = \begin{bmatrix} \cos \theta & \sin \theta \\ \sin \theta & -\cos \theta \end{bmatrix} \begin{bmatrix} v_\alpha \\ v_\beta \end{bmatrix}. \tag{3.27}$$

Voltages across inductors transform to

$$v_{L,d}(t) = L \frac{di_d(t)}{dt} + L\omega i_q(t),$$

$$v_{L,q}(t) = L \frac{di_q(t)}{dt} - L\omega i_d(t),$$

(3.28)

whereby  $i_d$  and  $i_q$  are the dq components of the AC current and  $L = L_{grid} + L_{filter} + 0.5L_{arm}$  is the equivalent inductance. As seen in (3.28), the inductor voltages bring about the coupling of the direct and quadrature axes. A system controller for a closed loop must be designed such that the two axes are decoupled if the two axes must not interfere with each other.

KVL around Figure 3.3 gives

$$e(t) = L\frac{di(t)}{dt} + i(t)R + v(t)$$

(3.29)

Transformation of (3.29) into the dq frame gives

$$e_d(t) = L \frac{di_d(t)}{dt} + L\omega i_q(t) + i_d(t)R + v_d(t)$$

$$e_q(t) = L \frac{di_q(t)}{dt} - L\omega i_d(t) + i_q(t)R + v_q(t)$$

(3.30)

Choosing the q-axis as the power axis,  $e_d$  is zero while  $e_q$  is the amplitude of e. For a unity power factor condition, the controller reference of  $i_d$  is set to zero so that the system active power is given by

$$P = \frac{3}{2}E_q I_q \tag{3.31}$$

while the reactive power is zero. To decouple the two axes, the following decoupling equations are used [93]:

$$v_d(t) = -v'_d(t) + e_d(t) - \omega L i_q(t),$$

$$v_q(t) = -v'_q(t) + e_q(t) + \omega L i_d(t),$$

(3.32)

so that (3.30) becomes

$$v'_d(t) = L \frac{di_d(t)}{dt} + i_d(t)R,$$

$$v'_q(t) = L \frac{di_q(t)}{dt} + i_q(t)R.$$

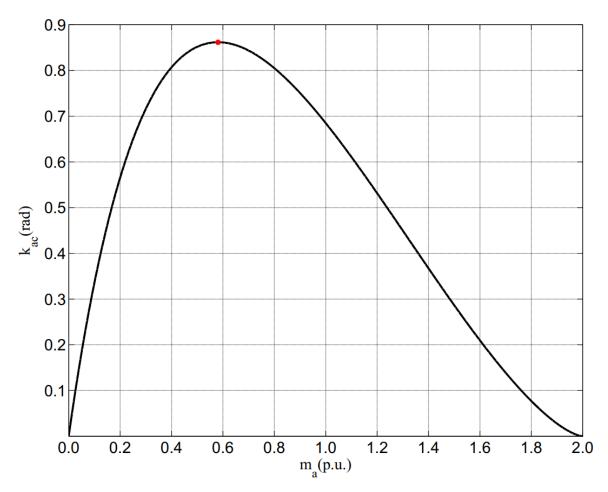

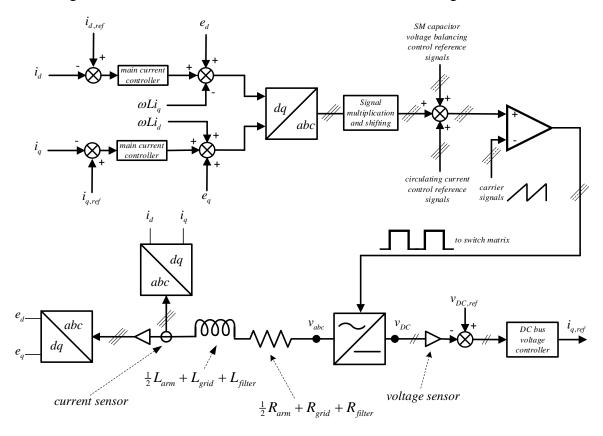

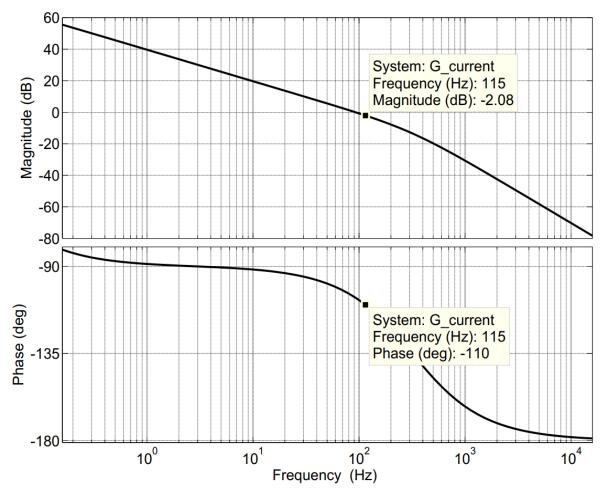

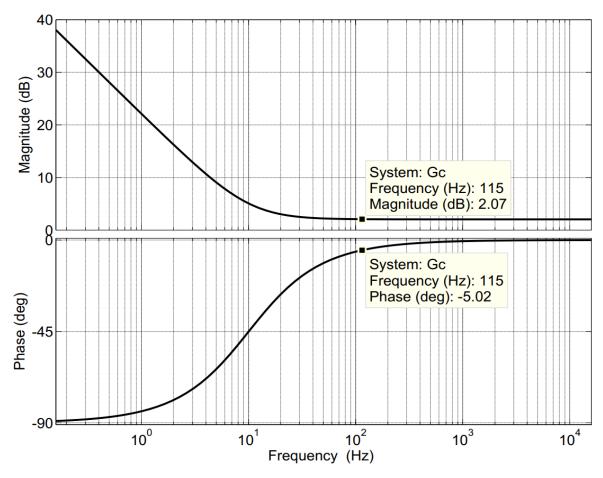

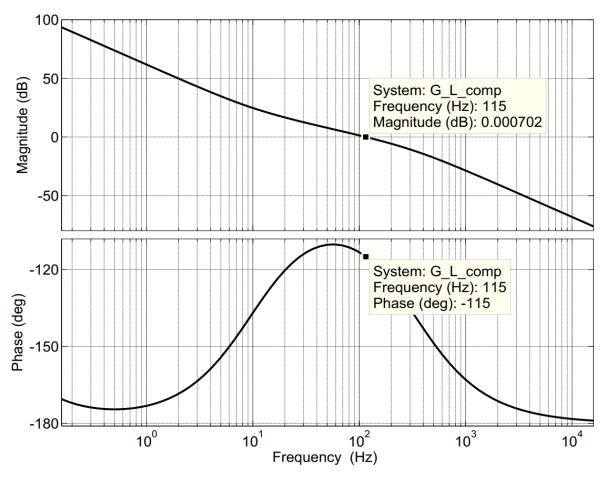

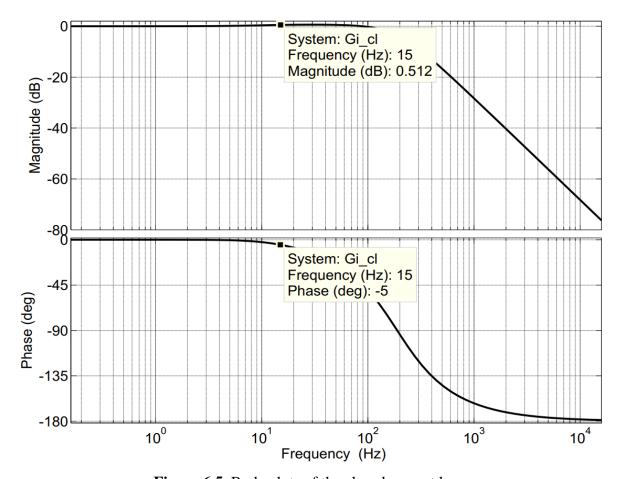

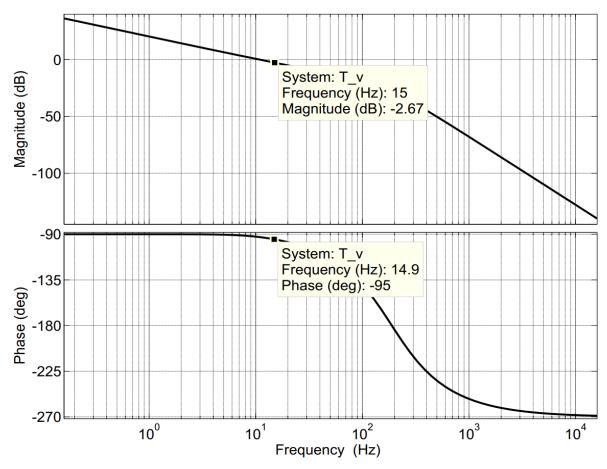

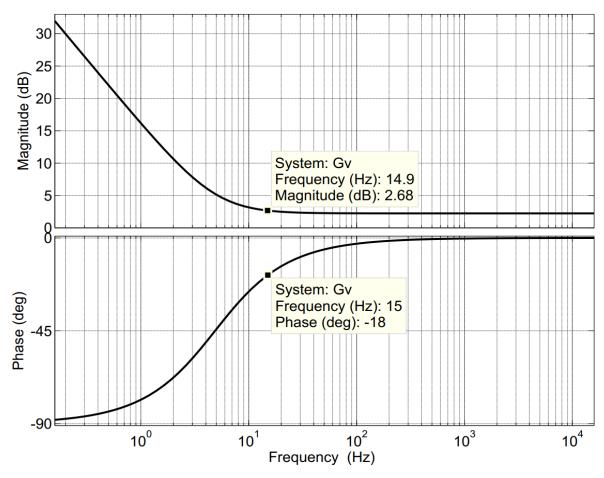

(3.33)