# DIFFERENTIAL CURRENT SENSOR LINEARISATION IN LOW-VOLTAGE CMOS

by

#### Neil Naudé

Submitted in partial fulfilment of the requirements for the degree Master of Engineering (Electronic Engineering)

in the

Department of Electrical, Electronic and Computer Engineering Faculty of Engineering, Built Environment and Information Technology

#### UNIVERSITY OF PRETORIA

January 2017

#### **SUMMARY**

#### DIFFERENTIAL CURRENT SENSOR LINEARISATION IN LOW-VOLTAGE CMOS

by

#### Neil Naudé

| Supervisor: | Prof S. Sinha                                                        |  |

|-------------|----------------------------------------------------------------------|--|

| Department: | Electrical, Electronic and Computer Engineering                      |  |

| University: | University of Pretoria                                               |  |

| Degree:     | Master of Engineering (Electronic Engineering)                       |  |

| Keywords:   | Low-voltage, CMOS, monolithic current sensor, SenseFET,              |  |

|             | linearisation, folded cascode, DC-DC converter, bias current         |  |

|             | equalisation, wireless sensor networks, CMOS process characteristics |  |

The viability of low cost, distributed, and autonomous wireless sensor networks is determined by the affordability of the integration and operation of each sensor node. Self-sufficient nodes which harvest energy from the local environment decrease operating and maintenance costs over extended periods of time. This affordability can be achieved by increasing the power usage efficiency of designs implemented in an older and cheaper CMOS process. This circumvents the use of a more compact technology node which trades increased efficiency for cost. The efficiency of power conversion is determined by topology, component quality, control scheme, and internal measurement accuracy.

This research focuses on improving internal measurement during the power conversion process, in order to reduce conversion loss from the internal control error. A current sensing integrated circuit was proposed which is insensitive to dominant process characteristics which degrade the performance of other sensing solutions. In particular, the detrimental effect of channel length modulation is compensated for. This compensation is achieved by decoupling the sensor biasing and differential steering pair from being influenced by the external current being measured. Widely used solutions were studied and analysed in the context of implementation in a low cost and low-voltage CMOS process. Key process characteristics which negatively influenced these solutions were identified and formed the basis of developing an improved integrated current sensor. Current research in the literature

is tightly focused on improved accuracy without the constraints of process costs, low operating voltage (800mV - 1.2 V), and prevalent second order effects of device operation.

A study of the literature on CMOS-based integrated current sensing demonstrates a common goal towards improving sensor accuracy by developing either new topologies or augmenting known topologies. New and augmented topologies focus on novel analogue networks which aim to improve the linearity of CMOS based current sensing. The colloquially named SenseFET circuit is a foundation for many variations of integrated current sensor. This integrated circuit generates an estimate of the current flowing into a DC-DC boost-buck converter by sampling the current sourced into the converters inductor. The low maximum operating voltage of the chosen CMOS process restricts the application of typical published solutions. The sensitivity of other solutions to second order effects limits application as well. The proposed solution is based on such a sampling topology with a focus on achieving linearity in a process with pronounced channel-length modulation effects as well as a relatively low operating voltage. The goal of the improved design is to test if linearity can be improved by developing a circuit which is robust towards second-order process effects.

Discreet and integrated boost-buck converters were studied and analysed to form the basis of further sensor developments. An integrated non-inverting converter topology suitable for single rail operation was identified and designed as the system environment for which an integrated sensor would be developed. This would allow for comparison of sensor designs in a known environment, both in simulation and in prototyping of the integrated system. The proposed integrated current sensor was developed analytically before being simulated both mathematically and at transistor gate level. This iterative process was applied to a known design as a performance baseline and to demonstrate the improvements achieved.

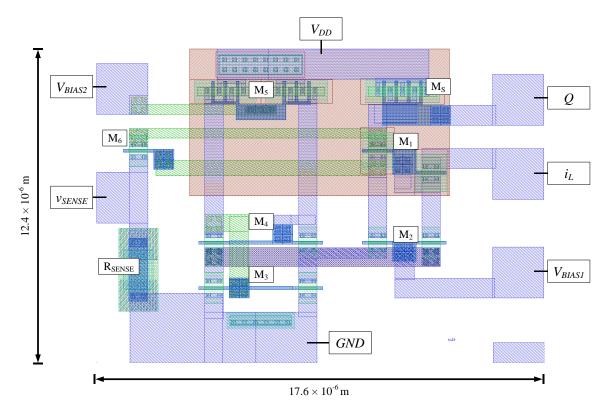

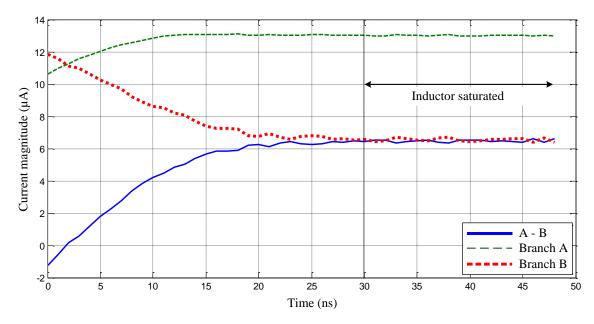

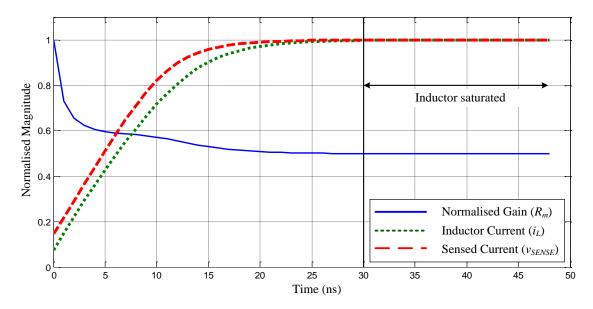

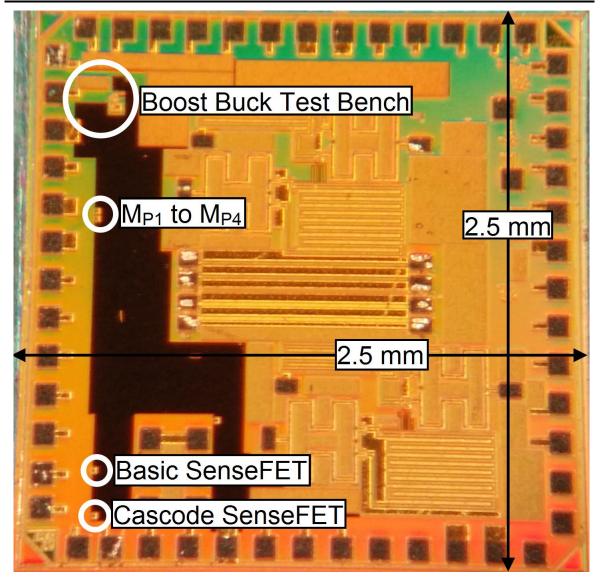

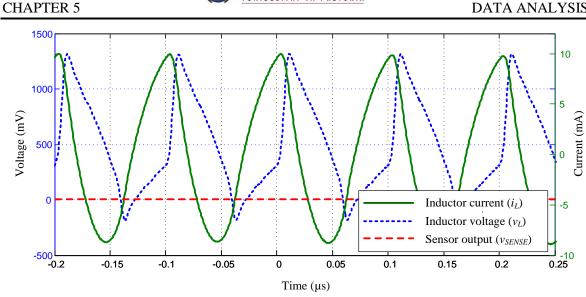

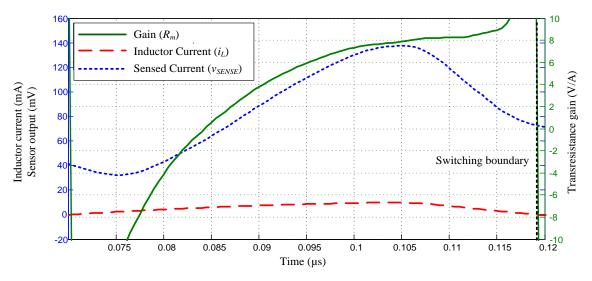

A prototype integrated circuit and test boost-buck converter were implemented in a 130 nm BiCMOS process to test and verify the sensor design against simulated results. Integrated circuits implemented include a reference and improved current sensor, boost-buck converter without closed loop control, and a boost-buck converter using current feed-forward control. The total proposed sensor area is  $12 \ \mu m \times 17 \ \mu m$ . The improved sensor performed well when operated over a more constrained range than what was designed for. Measured linearity compared favourably with simulation, with the exception of linearity at switching cycle boundaries. The improved sensor operates from 800mV to 1.2 V and has a transresistance gain of 5 V/A on both the charge and discharge portions of the power conversion cycle. The

designed gain was 2 V/A. Inductor current inversion at the conversion cycle boundaries resulted in unexpected but explicable behaviour.

#### ACKNOWLEDGEMENTS

I would like to thank the Eskom Tertiary Education Support (TESP) programme for its financial sponsorship in the preliminary stages of this study. Through the work done for the TESP, I was able to lay the foundations of this study and work that followed.

The MOSIS Educational Programme (MEP) was instrumental in facilitating this work. The MEP's sponsorship of the chip prototyping allowed my ideas and work to be tested. Prototyping through the MEP enabled practical outcomes from the study, adding credibility to my work for which I am thankful.

Professor Saurabh Sinha has been a source of guidance and knowledge throughout the majority of my academic career. His support and drive has been a positive influence throughout the course of this work, motivating me to continue working despite the challenges of balancing my professional career, personal life, and academic activities. I am not only grateful for his involvement and patience, but motivated to keep improving and diversifying my engineering, professional, and academic skills.

Dr Melissa Adendorff not only provided her excellent proofreading and editing skills, but offered a wealth of knowledge and advice that I relied on to successfully complete this dissertation. Her continual support and criticism were indispensable, allowing me to approach aspects of this work with insight and understanding. As my partner, her support was invaluable and I only have the greatest appreciation for her efforts.

I would also like to thank my family for their patience and support from the start and throughout this work.

Finally, I would like to thank the following individuals and organisations for their time and resources:

Dr Mladen Božanić for his advice and assistance at the start of this study,

Dr Tinus Stander and the staff of the Carl and Emily Fuchs Institute of Microelectronics (CEFIM) at the University of Pretoria, for allowing me to use their facilities.

My employer and colleagues at GEW Technologies (Pty) Ltd, for their support and laboratory resources.

#### LIST OF ABBREVIATIONS

| BiCMOS | Bipolar CMOS                            |

|--------|-----------------------------------------|

| СМС    | Current mode control                    |

| CMOS   | Complementary metal oxide semiconductor |

| DC     | Direct current                          |

| DRC    | Design rule check                       |

| DMM    | Digital multi-meter                     |

| DUT    | Device under test                       |

| ESR    | Effective series resistance             |

| FET    | Field effect transistor                 |

| IC     | Integrated circuit                      |

| KCL    | Kirchhoff's current law                 |

| LDO    | Low drop out                            |

| LVS    | Layout versus schematic                 |

| MEP    | MOSIS education program                 |

| MDO    | Mixed domain oscilloscope               |

| MPW    | Multi-project wafer                     |

| NDA    | Non-disclosure agreement                |

| OPAMP  | Operational amplifier                   |

| PA     | Power amplifier                         |

| PCB    | Printed circuit board                   |

| PSU    | Power supply unit                       |

| PVT    | Process, voltage, and temperature       |

| PWM    | Pulse-width modulation                  |

| QFN    | Quad flat no-lead                       |

| RF     | Radio frequency                         |

| SCE    | Short channel effects                   |

| SMD   | Surface mount device                                |

|-------|-----------------------------------------------------|

| SPICE | Simulation program with integrated circuit emphasis |

| TE    | Test equipment                                      |

| VMC   | Voltage mode control                                |

| WSN   | Wireless sensor network                             |

# **TABLE OF CONTENTS**

| C | НАРТ | ER  | 1 INTRODUCTION                                | 1 |

|---|------|-----|-----------------------------------------------|---|

|   | 1.1  | CH  | APTER OVERVIEW                                | 1 |

|   | 1.2  | BA  | CKGROUND OF THE RESEARCH                      | 1 |

|   | 1.3  | HY  | POTHESIS AND RESEARCH PROBLEMS                | 3 |

|   | 1.4  | JUS | STIFICATION FOR THE RESEARCH                  | 4 |

|   | 1.5  | RES | SEARCH METHODOLOGY                            | 5 |

|   | 1.6  | DEI | LIMITATIONS AND ASSUMPTIONS                   | 8 |

|   | 1.7  | CO  | NTRIBUTION                                    | 9 |

|   | 1.8  | PUI | BLICATIONS FROM THIS RESEARCH                 | 9 |

|   | 1.9  | OU  | TLINE OF THE DISSERTATION                     | 9 |

|   | 1.10 | С   | CONCLUSION 1                                  | 0 |

| С | НАРТ | ER  | 2 LITERATURE STUDY 1                          | 1 |

|   | 2.1  | CH  | APTER OVERVIEW                                | 1 |

|   | 2.2  | DIS | TRIBUTED SENSOR NETWORKS1                     | 1 |

|   | 2.3  | ENI | ERGY HARVESTING1                              | 2 |

|   | 2.4  | DC  | -DC CONVERTER FUNDAMENTALS1                   | 3 |

|   | 2.4  | .1  | Continuous mode1                              | 5 |

|   | 2.4  | .2  | Discontinuous mode 1                          | 6 |

|   | 2.5  | DC  | -DC CONVERTER FEEDBACK CONTROL 1              | 7 |

|   | 2.6  | СМ  | OS CONVERTER DESIGNS                          | 9 |

|   | 2.6  | .1  | Inverting and non-inverting DC-DC converters  | 9 |

|   | 2.6  | .2  | Alternative CMOS converter control topologies | 0 |

|   | 2.6  | .3  | Integrated CMC converters                     | 0 |

|   | 2.7  | СМ  | OS BASED CURRENT SENSING                      | 2 |

|   | 2.7  | .1  | General current sensing techniques            | 2 |

|   | 2.7  | .2  | Integrated current sensing – The SenseFET     | 4 |

| 2.7  | 7.3 Improved SenseFETs                                  |          |

|------|---------------------------------------------------------|----------|

| 2.8  | TECHNOLOGY SHORTCOMINGS                                 | 27       |

| 2.3  | 3.1 Channel length modulation                           |          |

| 2.3  | 3.2 Velocity saturation                                 |          |

| 2.3  | 3.3 Low-voltage limitations                             |          |

| 2.3  | 3.4 Other device limitations                            |          |

| 2.9  | CMOS CASCODE TECHNIQUES                                 |          |

| 2.10 | RESEARCH CONTRIBUTION                                   |          |

| 2.11 | CONCLUSION                                              |          |

| CHAP | TER 3 METHODOLOGY                                       |          |

| 3.1  | CHAPTER OVERVIEW                                        |          |

| 3.2  | RESEARCH METHODOLOGY OVERVIEW                           |          |

| 3.3  | RATIONALE                                               |          |

| 3.4  | PROBLEM DEFINITION AND LITERATURE STUDY                 |          |

| 3.5  | TECHNOLOGY                                              |          |

| 3.6  | ANALYSIS, MATHEMATICAL MODELLING, AND CHARACTER         | SISATION |

|      |                                                         |          |

| 3.0  | 5.1 Analysis                                            |          |

| 3.0  | 5.2 Mathematical modelling and computational evaluation |          |

| 3.0  | 5.3 Device characterisation                             |          |

| 3.7  | SCHEMATIC SIMULATION                                    |          |

| 3.7  | 7.1 Constraints from simulation and experiment design   |          |

| 3.8  | EXPERIMENTAL DESIGN                                     |          |

| 3.9  | LAYOUT AND LAYOUT VERIFICATION                          |          |

| 3.9  | P.1 Layout considerations                               |          |

| 3.9  | D.2   Layout versus schematic                           | 46       |

| 3.9  | D.3 Design rule check                                   |          |

| 3.10 | MANUFACTURING                                           |          |

| 3.   | 10.1 Chip fabrication                                   |          |

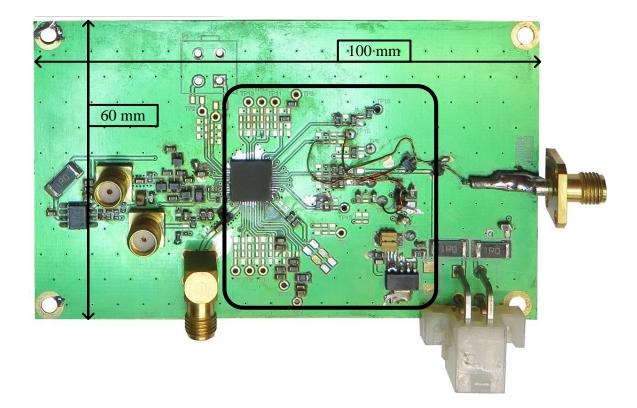

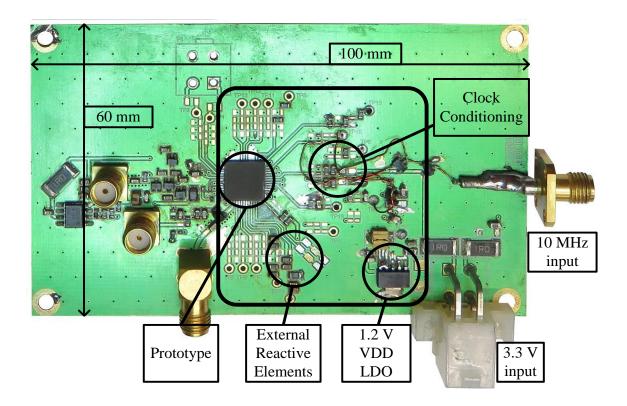

| 3.10.2  | PCB design and fabrication                                             | 47  |

|---------|------------------------------------------------------------------------|-----|

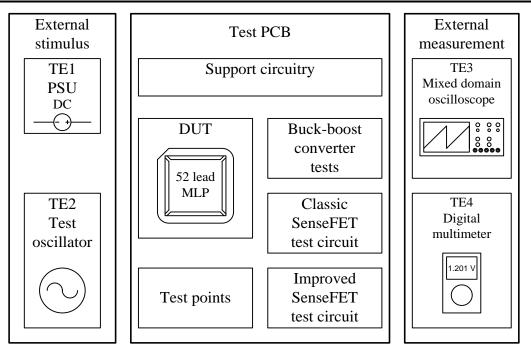

| 3.11 N  | /IEASUREMENT                                                           | 47  |

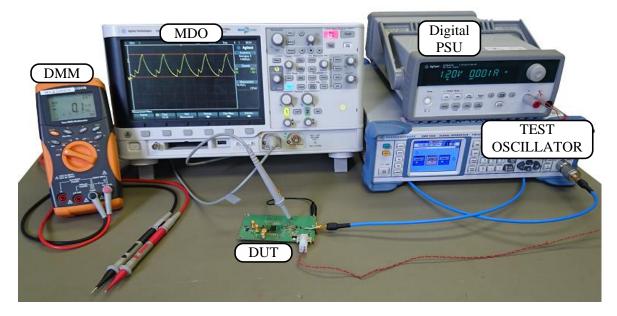

| 3.11.1  | Measurement setup                                                      | 48  |

| 3.11.2  | Test setup 1: SenseFET characterisation                                | 50  |

| 3.11.3  | Test setup 2: Buck-boost converter                                     | 52  |

| 3.11.4  | Data analysis                                                          | 52  |

| 3.12 T  | TECHNICAL SOFTWARE                                                     | 53  |

| 3.13 C  | CONCLUSION                                                             | 54  |

| CHAPTER | 4 DESIGN AND FABRICATION                                               | 56  |

| 4.1 CH  | APTER OVERVIEW                                                         | 56  |

| 4.2 PR  | OCESS CHARACTERISATION                                                 | 56  |

| 4.2.1   | Process characterisation overview                                      | 56  |

| 4.2.2   | Deriving channel length modulation parameters from process characteris | tic |

| curves  |                                                                        | 57  |

| 4.3 RE  | FERENCE SENSEFET                                                       | 60  |

| 4.3.1   | Overview                                                               | 60  |

| 4.3.2   | Design concepts                                                        | 61  |

| 4.3.3   | Implementation                                                         | 62  |

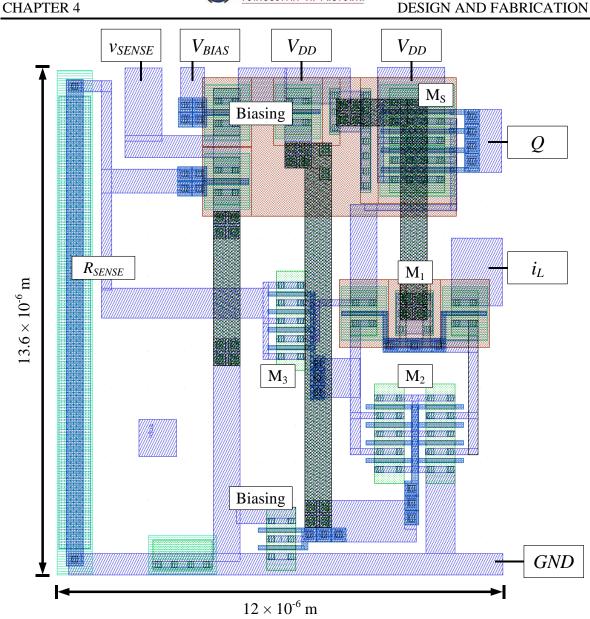

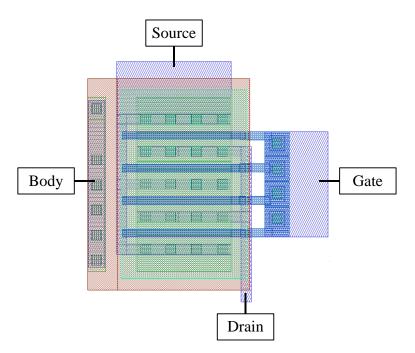

| 4.3.4   | Layout                                                                 | 65  |

| 4.3.5   | Simulated performance                                                  | 68  |

| 4.4 CA  | SCODED SENSEFET                                                        | 71  |

| 4.4.1   | Overview                                                               | 71  |

| 4.4.2   | Design Concepts                                                        | 72  |

| 4.4.3   | Implementation                                                         | 77  |

| 4.4.4   | Layout                                                                 | 79  |

| 4.4.5   | Simulated performance                                                  | 80  |

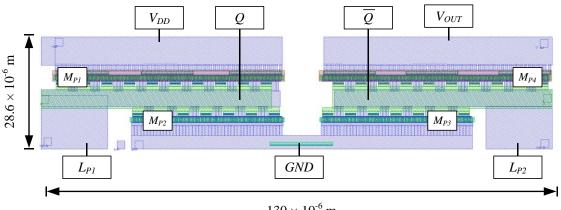

| 4.5 FA  | BRICATION                                                              | 82  |

| 4.5.1   | Overview                                                               | 82  |

| 4.5.2   | Fabrication preparation                                                | 83  |

| 4.5  | 5.3         | Fabricated integrated circuit                   |  |

|------|-------------|-------------------------------------------------|--|

| 4.6  | ME          | ASUREMENT SETUP                                 |  |

| 4.6  | 5.1         | Overview                                        |  |

| 4.6  | 5.2         | Additional integrated circuitry for measurement |  |

| 4.6  | 5.3         | Additional external circuitry for measurement   |  |

| 4.6  | 5.4         | Printed circuit board                           |  |

| 4.6  | 5.5         | Laboratory setup                                |  |

| 4.7  | CO          | NCLUSION                                        |  |

| CHAP | ГER         | 5 DATA ANALYSIS                                 |  |

| 5.1  | СН          | APTER OVERVIEW                                  |  |

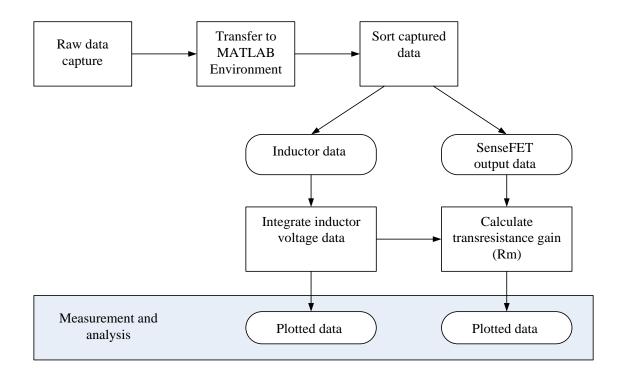

| 5.2  | DA          | TA COLLECTION                                   |  |

| 5.3  | DA          | TA PROCESSING                                   |  |

| 5.4  | TES         | ST 1 MEASUREMENT DATA                           |  |

| 5.4  | <b>I</b> .1 | Reference SenseFET                              |  |

| 5.4  | 1.2         | Cascoded SenseFET                               |  |

| 5.5  | TES         | ST 2 MEASUREMENT DATA                           |  |

| 5.6  | PRO         | OCESSED DATA AND OBSERVATIONS                   |  |

| 5.6  | 5.1         | Reference SenseFET                              |  |

| 5.6  | 5.2         | Cascoded SenseFET                               |  |

| 5.7  | SEN         | NSEFET DATA INTERPRETATION AND ANALYSIS         |  |

| 5.7  | 7.1         | Reference SenseFET                              |  |

| 5.7  | 7.2         | Cascoded SenseFET                               |  |

| 5.8  | CO          | NCLUSION                                        |  |

| CHAP | ΓER         | 6 CONCLUSION                                    |  |

| 6.1  | СН          | APTER OVERVIEW                                  |  |

| 6.2  | OV          | ERVIEW OF THE STUDY                             |  |

| 6.2  | 2.1         | Contextualisation                               |  |

| 6.2  | 2.2         | Hypothesis and research problems                |  |

| 6.2.              | 3 Overview of relevant literature                        |     |

|-------------------|----------------------------------------------------------|-----|

| 6.3               | METHODOLOGICAL REFLECTION                                |     |

| 6.3.              | 1 Contextualisation                                      |     |

| 6.3.2             | 2 Analysis, mathematical modelling, and characterisation |     |

| 6.3.              | 3 Methodological limitations                             |     |

| 6.3.4             | 4 Design and prototyping                                 |     |

| 6.3.              | 5 Technical software                                     | 116 |

| 6.3.              | 6 Measurement                                            | 116 |

| 6.4               | RESULTS                                                  |     |

| 6.4.              | 1 Data interpretation and data analysis                  |     |

| 6.4.2             | 2 Discussion                                             |     |

| 6.5               | LIMITATIONS OF THE STUDY                                 | 119 |

| 6.6               | OPPORTUNITIES FOR FUTURE RESEARCH                        |     |

| 6.7               | CONTRIBUTION TO THE BODY OF KNOWLEDGE                    |     |

| REFERI            | ENCES                                                    |     |

| ADDENDUM A MATLAB |                                                          |     |

| ADDEN             | DUM B PCB SCHEMATICS                                     |     |

# CHAPTER 1 INTRODUCTION

#### **1.1 CHAPTER OVERVIEW**

This dissertation investigates integrated circuit (IC) current measuring techniques as a method of improving the efficiency of integrated switched mode power converters. This chapter provides the contextual background and motivation for this investigation, as well as an overview of subsequent research. The presentation of the development of relevant research questions follows, as well as an explanation of the relevance of the research, and the scope of the investigation. This chapter finally presents an overview of the study's methodology and the structure of this dissertation.

#### **1.2 BACKGROUND OF THE RESEARCH**

Autonomous wireless sensor networks (WSN) are able to perform long-term data acquisition of environmental factors in the region in which they are deployed [1]. Sensor nodes that do not require maintenance, and which could be produced inexpensively, allow for the construction of affordable sensor networks. Affordability allows for the detailed characterisation of environments, whether they be industrial, agriculture, or urban in nature.

Sensor networks may be broadly characterised as either structured sensor networks, or as unstructured sensor networks [1]. Each node in the network gathers data within its measurement range, and this data is either stored or transmitted to a data collection point. Structured networks utilise few sensor nodes at selected, or lumped, points in the environment of interest. In such sensor networks, the sensor nodes do not gather data from the entire environment, but from specific planned locations. Unstructured networks utilise a ubiquitous and ad hoc sensor distribution in the environment of interest. This distinction in terms of node distribution drives the functional requirements of each node. The relatively sparse nodal distribution in a structured network, the number of sensor nodes required to provide full coverage of the environment of interest is high, requiring low cost sensors that remain effective. For a sensor node to be effective as an unstructured network element, it needs to be self-sufficient, maintenance free, and inexpensive enough to be replaced instead of repaired. Integrated circuit (IC) technology is suitable for meeting these requirements.

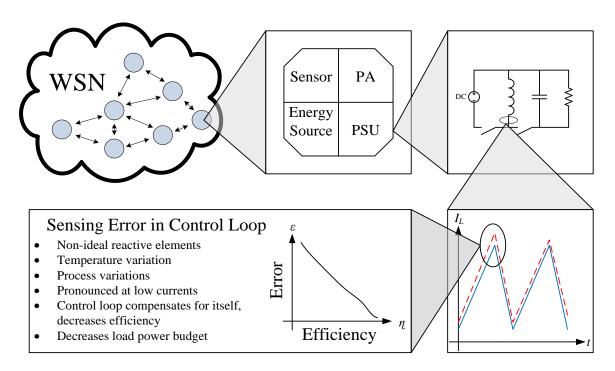

Figure 1.1 depicts an overview of a sensor node's functional requirements in an unstructured network, as well as additional detailed requirements that are part of the focus of this dissertation.

Figure 1.1. Unstructured WSN node requirement breakdown.

The sensor node diagram in Figure 1.1 consists of an energy source, power supply unit (PSU), power amplifier (PA), and the sensor [2]. Each functional unit in the node is powered by the energy source. The PSU converts the energy from the energy harvesting source to a DC power source for the sensor and PA. The sensor sub-system contains the sensing circuitry as well as digitisation and processing, storage, and radio frequency (RF) up-converter. The PA sub-system consists of the amplifier and antenna required to connect wirelessly to the rest of the sensing network. The amount of energy that the energy source can supply and the efficiency of the PSU determines the overall power budget for the entire sensor node. Each of these four sub-systems has operational and design aspects which can be improved on to achieve the core design mandate.

Operational efficiency may be improved by migrating the sensor node design to a more compact integrated process [3]. This is done at a greater expense, threatening the low-cost requirement. An alternative is to improve efficiency in a lower cost process. This dissertation presents this approach as applied to the PSU.

The PSU comprises several aspects which determine the overall efficiency of operation. These aspects may be classified as being influenced either by design or by component and environmental characteristics. Figure 1.1 demonstrates how one such design aspect can be the source of inefficiency. Effective switched mode power conversion relies on internally measuring the flow of energy through the conversion process, and using this information to steer internal control schemes. The accuracy of this measurement is influenced by multiple factors, including process and temperature variations, non-ideal reactive components, and low voltage operation. An inaccurate internal measurement introduces erroneous information into PSU control loop. The processed error leads to control loop inaccuracies.

#### 1.3 HYPOTHESIS AND RESEARCH PROBLEMS

Integrated PSU design and research focuses on three key areas. These are internal measurement, control scheme topology, and improved reactive networks. Reactive networks are off-chip. Effective control schemes are well understood [4], [5], and the analogue subsystems used to implement these schemes make extensive use of operational amplifiers (OPAMP). Similarly, analogue signal processing using OPAMP implementations of the required control transfer functions is well documented [6]. Internal measurement is an area of active research with several techniques being developed for modern CMOS processes [7], [8] and [9]. These techniques are not commonly implemented in low-voltage technologies which are of interest for sensor node implementation. This alludes to a potential area where improvements and adaptations could be made to make a low-voltage implementation feasible.

The implementation and necessary improvement of these internal measurement techniques in a low-voltage process could lead to viable solutions for deploying PSU designs that compete in performance with known designs implemented in a more compact technology node. The performance characteristics of internal current measurement techniques implemented in an available low-voltage 130 nm CMOS process must be determined. The available CMOS process has a low maximum gate-oxide breakdown voltage, and the device's performance is strongly influenced by channel length modulation effects. This dissertation considers low operating voltage and non-negligible second order effects on the linearity of known current sensing techniques. Using the aforementioned rationale and the outcome of analysis and simulation of current techniques in the available CMOS process, the research hypotheses may be stated as follows:

If integrated circuit topologies for measuring current using CMOS devices were improved to be resilient to second order effects and low voltage operation, the linearity of the measurement would improve.

The following key research problems complement the aforementioned hypothesis:

- 1. Determine the extent of the effect of second order effects on the linearity of integrated current sensing circuits.

- 2. How will the non-linearity be modelled using traditional analytical models? How could such models be used to gain additional insight into circuit operation and be used to derive solutions that address non-linearity? How well do these models agree with gate level simulation?

- 3. How robust are the solutions to process, temperature, and voltage (PVT) variations?

- 4. Determine if it possible to significantly improve linearity in comparison to other designs.

A prototype implementing both a reference design as well as an improved design will be used to draw comparison between implementation and theoretical analysis and modelling. Outcomes of this comparison are used to verify or refute the hypothesis. The differences between theoretical and practical implementations are subjected to additional analysis to determine the origin of discrepancies.

#### 1.4 JUSTIFICATION FOR THE RESEARCH

The rationale for improving design efficiency at a specific CMOS technology node is to obtain equivalent power performance from a larger<sup>1</sup> and more cost-effective process than that of a smaller, lower power, and expensive process [3]. The aim of this research is to decrease the cost of production without a significant reduction in power efficiency. If the requirements for implementing an unstructured WSN are considered, then a high efficiency at reduced cost is paramount to the viability of such networks.

Department of Electrical, Electronic and Computer Engineering University of Pretoria

<sup>&</sup>lt;sup>1</sup> The terms "larger" and "smaller" refer to the minimum aspect ratio possible in a CMOS process.

This study focuses on improving the efficiency of the power converter which converts a variable DC input to a fixed DC output. Improving the conversion efficiency allows for an increased power budget from which other systems in the sensor node must draw power. This work therefore focuses on the internal sensing used by DC-DC switched mode converters to monitor the current flowing through the converter.

The techniques presented in this dissertation are justified by the poor transferability of current designs to the target 130 nm process. The relatively low operating voltage (0.8 V to 1.2 V) and prominent second order effects in the 130 nm process are detrimental to the linearity of current designs by reducing the dynamic range of these designs. The reduction in dynamic range introduces an internal measurement error which causes the internal control loop to either under or over compensate during the conversion cycle. The non-linearity renders these designs unsuitable solutions for internal current sensing. This dissertation presents possible techniques which may be used to improve the linearity of these internal current sensor designs by utilising networks which are resistant to process parameters introducing errors.

Finally, this study demonstrates improved linearity, strengthening the justification for using the low cost and low-voltage 130 nm CMOS process as a platform for the development of sensor nodes in a WSN.

#### 1.5 RESEARCH METHODOLOGY

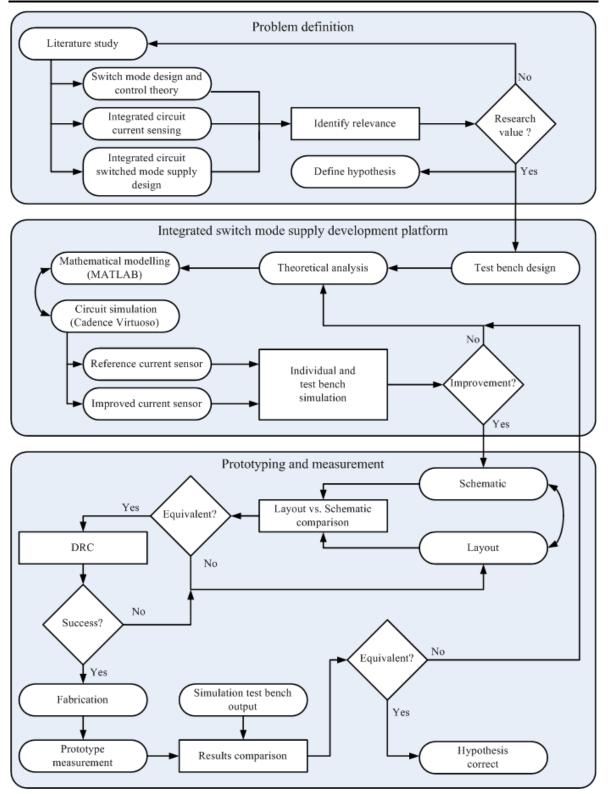

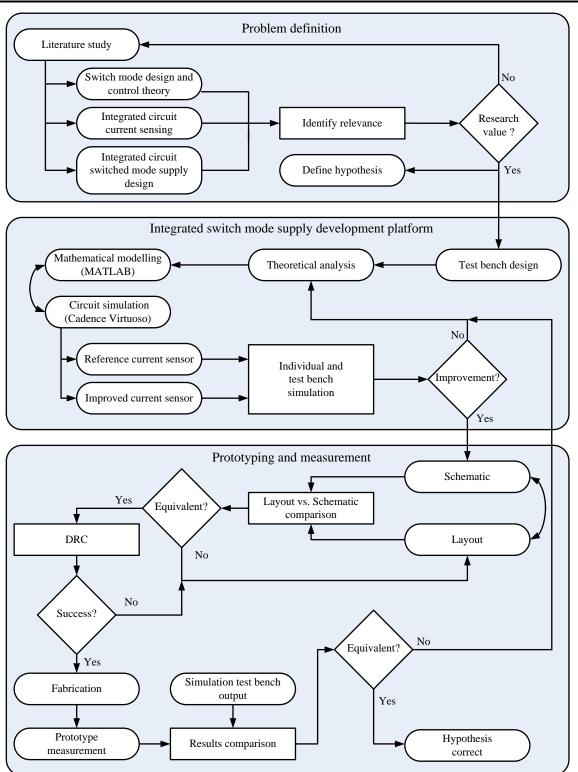

Figure 1.2 diagrammatically demonstrates the methodology used to approach the work in this dissertation. The methodology has three phases, with each phase focusing on a collection of sequential and iterative tasks specific to the goals of the phase.

The first phase comprises the problem definition which is focused on defining and refining the research questions which must be asked. The primary task is a detailed literature study of relevant material to identify the research value. The literature study is an iterative process, starting with a broad investigation into switched mode design principles and their application in the integrated circuit environment. On each iteration of the literature study, the study becomes more focused until the specific research value can be identified in terms of the broader research goals. For this work, the functional components of integrated switched mode supplies are studied to identify which component is a candidate for improvement with the overall goal of improving system performance of the switched mode converter.

The implementation of the internal current sensing circuit in a 130 nm process was identified as viable candidate for improvement. This process was available to students at the University of Pretoria through the MOSIS educational program (MEP). The IBM 8HP BiCMOS process at the 130 nm technology node offers a process which is affordable and operates at low-voltage. The feature size of this process is also in accordance with the trending features size of other work in the literature. These characteristics of the IBM 8HP BiCMOS process make it a suitable candidate to test and develop the concepts in this dissertation.

The second phase is focused on familiarisation with fundamentals and development of techniques which may be used to test the hypothesis. This includes the creation of a baseline, which is developed from designs in the current literature as a performance reference. The design research focus also requires an integrated test bench which is used to stimulate the proposed design and reference. Development is an iterative process alternating between high level mathematical models and low level device simulation.

The designs are developed from analytical models which form the basis for the mathematical models implemented in MATLAB<sup>2</sup>. The outcomes of these models form the basis of the development of the required sensing and test circuits in a 130 nm BiCMOS process through the MOSIS educational program<sup>3</sup>. The circuits are designed and tested using Cadence Virtuoso<sup>4</sup>. Once the development is able to demonstrate an improvement in software simulation, the second phase is complete.

<sup>&</sup>lt;sup>2</sup> MATLAB is supplied by Mathworks (<u>www.mathworks.com</u>), developers of technical computing software for scientists and engineers.

<sup>&</sup>lt;sup>3</sup> More information on scheduled multi-wafer projects from the MOSIS service is provided at (<u>https://www.mosis.com/</u>).

<sup>&</sup>lt;sup>4</sup> *Cadence Virtuoso* is a visualisation and analysis tool for simulating and analysing the performance of analogue, RF, and mixed-signal designs

#### CHAPTER 1

#### INTRODUCTION

Figure 1.2. Outline of research methodology.

The third and final phase focuses on real-world prototyping and testing of the hypothesis. The integrated circuit layout of the designs to be tested is done in Cadence Virtuoso. Cadence Virtuoso is also used to test electrical equivalence between the design schematic and physical

layout. Once the layout satisfied the equivalence requirement a final design rule check (DRC) must be run to verify whether the layout is suitable for manufacture.

The final fabrication is achieved through the MOSIS service. The fabricated IC is mounted to a printed circuit board (PCB) which serves as an interface between the final IC and external circuit components and test equipment. Measurement data are thus captured using a mixed domain oscilloscope. The captured data is processed in MATAB and compared with simulation and analytical outcomes. These comparisons are then used to test whether the hypothesis is correct, and to draw additional conclusions.

#### 1.6 DELIMITATIONS AND ASSUMPTIONS

It is assumed that the circuit behaviour described and the techniques that were developed and applied are transferable to technologies with a similarly low operating voltage and influential channel modulation effects. This should be verifiable through research, comparing process parameters and simulation using alternate process models. Implementation in an alternate process operating at a higher process voltage is not possible using the available resources, and the techniques implemented in such technologies are thus transferred to the available CMOS process to draw comparison. Analytical models are used to show the influence of various process parameters and operational conditions on the developments in this dissertation.

The focus of this study is on the development of an improved integrated current sensor for integrated switched mode power supplies. The design of the test circuits prioritises basic functionality. The integration with off-chip components did not focus on a high level of integration. High quality common components are thus selected to implement external circuit elements.

Prototype hardware in this study is limited to a single iteration over the course of this study. This limitation stems from limited availability of silicon real-estate through the MOSIS education program. Furthermore, the iterative process takes several months.

In practice, a completely integrated sensor node would make use of a power source that harvests energy from its environment, using additional circuitry to condition this energy to comply with the limits of the 130 nm process used. In this study, the external power is provided by a digitally controlled power supply to provide predictable and consistent power

for measurement and evaluation of the prototype. In a similar manner, the switching signal used to drive the switched mode converter test bench is provided by an external signal source.

#### **1.7 CONTRIBUTION**

The primary contribution in this dissertation is the application of techniques used in differential amplifiers and current references to supress the significant influence of non-linear effects on a current sensing circuits operation.

The 130 nm CMOS process used has a relatively low maximum operating voltage of 1.2 V with significant channel length modulation. Relevant designs [10] in the literature make use of CMOS technologies with a higher maximum operating voltage. The higher operating voltage allows for integrated current sensors to be linearised using operational amplifier based designs. These solutions are not easily transferrable to the low-voltage 130 nm CMOS process. This dissertation utilises an alternative approach that introduces a compensating network suppressing the effects of channel length modulation on current sensor operation. This network additionally provides a degree of immunity to external network voltages influencing current sensor biasing.

#### **1.8 PUBLICATIONS FROM THIS RESEARCH**

The work in this dissertation also resulted in an accepted publication for the peer reviewed journal, Microelectronics International [11]. The paper, accepted for publication in August, 2016 is titled: *Linearized differential current sensor in low-voltage CMOS*.

This technical paper focused on the techniques used to linearise the current sensing SenseFET circuit as well as experimental results from the prototype.

#### **1.9 OUTLINE OF THE DISSERTATION**

Chapter 1 provides context and motivation for the work in this dissertation. The research hypothesis is formulated and justified. The research methodology that is applied to test the hypothesis is presented. Delimitations and assumptions are discussed and justified to constrain the scope of this study. Finally, the research contribution is discussed.

Chapter 2 presents a review of the literature relevant to the development of the hypothesis. A summary of techniques and approaches is presented in clarify the void in current

knowledge that the hypothesis is testing. This chapter primarily discusses current sensing techniques developed by other researchers and the technologies in which these techniques were implemented.

Chapter 3 focuses on the applied methodology and tools used to test the hypothesis. Analytical and mathematical models are described in terms of the definition of the predominant research questions in the realm of circuit analysis and design. The application of these models and tools is also described.

Chapter 4 has two areas of focus. Firstly, the chapter discusses the outcomes from the application of the methodology and models in Chapter 3. The models developed are applied and tested in a simulation environment. The first order results are evaluated against model outcomes and used to refine designs. The refinements are discussed and simulation is used to demonstrate differences. The second part of the chapter focuses on the implementation and development of a prototype in the available CMOS process. This area of focus discusses transferring circuit designs in terms of layout, and motivations for layout choices.

Chapter 5 documents the measurement process and evaluation of the prototype performances. It presents a comparison of these results with simulation results, as well as a discussion of the similarity and differences in performance and behaviour between simulation, analytical, and practical domains.

Chapter 6 collates the information from the preceding chapters to draw conclusions and answer the predominant research questions. The result of the hypothesis test is formally stated. This chapter also discusses shortcomings of the test, contributions made to the body of knowledge, successes and failures, and the potential for future research.

#### 1.10 CONCLUSION

This chapter provided an introduction to the work covered in this dissertation. The problem context was described as well as how a research hypothesis was developed. The justification for this research was presented. The research methodology used to test the hypothesis within the constraints of the available resources was described. A summary of the research contribution was provided. The outline of the dissertation provides the reader with an overview of the material covered in each chapter.

# CHAPTER 2 LITERATURE STUDY

#### 2.1 CHAPTER OVERVIEW

This Chapter presents concepts from the literature used to develop and define the research hypothesis. The wider research context is investigated and refined in order to establish a clear focus for subsequent work needed to test this hypothesis. This Chapter also provides an overview of the concepts and mathematical models which the study utilises to formally define the research questions.

Energy harvesting techniques and switched mode DC-DC converter topologies are investigated, alongside control schemes for effective switched mode power supply design. It is necessary to investigate the implementation of these converter topologies in CMOS technology, in order to determine areas of improvement. The process limitations of the available technology are considered. The outcomes of this investigation are used to develop both the test and the development environment used in this work. The hypothesis tested in this research calls for the development of new internal current sensing circuits to be evaluated against solutions from the literature. This Chapter presents an investigation of such current sensing circuits.

#### 2.2 DISTRIBUTED SENSOR NETWORKS

Wireless sensor networks (WSNs) are sensor networks with multiple interconnected nodes. Each node in the network is wireless and interacts with neighbouring nodes through a wireless interface. This connectivity may be used to create a wireless sensor network which is distributed throughout a target environment. WSNs do not typically feature an extensive support infrastructure. The networks are designed to be deployed in inaccessible regions with little or no maintenance support.

WSNs are categorised as either structured or unstructured. Structured networks have a predetermined structure with each node in a planned location. Unstructured networks do not have a planned structure and sensor nodes are distributed randomly throughout an environment [1]. The advantage of structured networks is that they require fewer sensor nodes to be effective, allowing a limited degree of maintenance and supervision. Unstructured networks have too many nodes (thousands to tens of thousands) for supervision

and maintenance actions to be practical. For this reason, unstructured networks need to be autonomous.

A typical wireless sensor node comprises a power source, one or more sensors, memory and processor, and a radio transceiver. Each of these aspects of the sensor node is constrained by the cost and functional requirement for the WSN. These constraints include limited power, communication range, hardware cost effectiveness, limited processing power, and memory.

#### 2.3 ENERGY HARVESTING

Practical WSNs have sensor nodes which do not require maintenance, and this is also applicable to the node's power source. Discrete sensor nodes can have power consumption as low as 0.3 mW [12] but still rely on battery power, limiting the nodes operational life to several years. The low power requirements of integrated devices allow energy harvesting from the environment to be a viable source of renewable power. The typical power usage for an integrated sensor node is between 1  $\mu$ W and 20  $\mu$ W [13] with complex sensors requiring up to 100  $\mu$ W [14]. Sources from which energy can be harvested fall into five general categories, namely motion and vibration (kinetic), thermal gradients, photovoltaic sources, RF energy [15], and electrochemical processes.

Energy harvesting from motion and vibration utilise electrostatic, piezoelectric, or electromagnetic transducers to convert kinetic energy into electric energy [16]. Electrostatic transducers convert the relevant motion between polarised and overlapping terminals of a capacitive device to a stored charge as the potential between terminals changes. The charge generated by the deformation of materials under mechanical stress is used in piezoelectric transducers. Electromagnetic transducers utilise electromagnetic induction which arises from the relative motion of a conductor through an electromagnetic field.

If two lengths of dissimilar conductors are connected, the unconnected terminals will develop an open circuit voltage, if the temperature of each conductor is different. This is known as the Seebeck Effect, and it is used to harvest energy from thermal gradients. Energy may be harvested from light using a transducer incorporating photovoltaic cells. The effectiveness of the photovoltaic cell is strongly dependent on the available incident light.

RF energy harvesting harnesses ambient RF energy in a desired band using an antenna. The primary obstacle to harnessing RF energy is that RF energy attenuates rapidly as it

CHAPTER 2

propagates through the atmosphere and other environmental elements. Obtaining a meaningful amount of energy requires a large collection area, or a localised RF energy source designed specifically to distribute power to a WSN [15].

Energy harvesting is possible in an environment where natural electrochemical processes could be exploited. Such a potential environment is a WSN deployed over and within a living organism. The fluids in such an environment have electrolytic properties, allowing for the construction of a rechargeable battery as the electrolytic fluid is replenished. Such a battery is demonstrated in [17] and develops 1.5 mW at 1.2 V.

#### 2.4 DC-DC CONVERTER FUNDAMENTALS

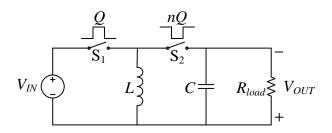

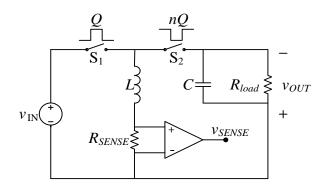

This section presents an overview of DC-DC converter fundamentals, specifically the buckboost topology, which is able to develop an output voltage either larger or smaller than the input [18]. This presentation comprises a description of the operation of this topology, as well as its two modes of operation. Figure 2.1 presents a diagram of a basic inverting buckboost DC-DC converter.

Figure 2.1. Buck-boost voltage converter topology.

The converter shown in Figure 2.1 is classified as an inverting buck-boost converter because the polarity on the output is reversed to that of the input. The converter works on a cyclic basis. Switches  $S_1$  and  $S_2$  alternate being opened and closed with  $S_2$  open while  $S_1$  is closed. During the first phase of each switching cycle, energy is transferred from the source to the inductor *L*. In the second phase of the switching cycle the energy stored in the inductor is transferred to capacitor *C* and  $R_{load}$ .

At the start of a switching cycle  $(t = 0t_T s) Q$  is on and closes S<sub>1</sub>. Therefore, nQ is the logical complement of Q and S<sub>2</sub> is open. In the second part of the switching cycle Q is off and S<sub>1</sub> is open. Similarly, nQ is on and switch S<sub>2</sub> is closed. This creates two distinct circuit behaviours. From time  $t = 0t_T s$  to  $t = Dt_T s$ , S<sub>1</sub> is closed and S<sub>2</sub> is open, allowing power from the DC Department of Electrical, Electronic and Computer Engineering 13 University of Pretoria

**CHAPTER 2**

source to be passed through inductor *L*. From time  $t = Dt_T s$  to  $t = t_T s$ , S<sub>1</sub> is open and S<sub>2</sub> is closed and *L* is connected capacitor *C* and a resistive load *R*<sub>load</sub>. The currents and voltages in the circuit are shown in Figure 2.2.

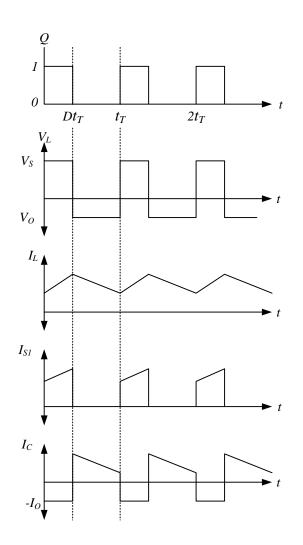

Figure 2.2. Buck-boost converter waveforms.

In Figure 2.2, Q is the switching clock signal which is high for a percentage D of the total switching interval.  $V_L$  is a plot of the voltage over the inductor where  $V_S$  is the source voltage and  $V_O$  is the output voltage.  $I_L$  is a plot of the current flowing through the inductor L. The gradient of the current flow is positive as energy is stored in L and negative as L discharges into the load. The current through  $S_1$  is equivalent to  $I_L$  when L is charging.  $S_1$  does not conduct when L discharges into the load.  $I_C$  is a plot of the current drawn by the load while L charges.

In the on state with  $S_1$  closed the change in inductor current is given by:

$$\frac{di_L}{dt} = \frac{V_{IN}}{L} \tag{2.1}$$

This leads to a total change in current by  $t = Dt_T$  of:

$$\Delta i_{Lon} = \int_{0}^{Dt_{T}} di_{L} = \int_{0}^{Dt_{T}} \frac{V_{IN}}{L} dt = \frac{V_{IN} Dt_{T}}{L}$$

(2.2)

Where *D* is the duty cycle of *Q* and 0 < D < 1.

Similarly, in the off state with S<sub>2</sub> closed:

$$\Delta i_{Loff} = \int_{0}^{(1-D)t_{T}} \frac{V_{OUT}}{L} dt = \frac{V_{OUT}(1-D)t_{T}}{L}$$

(2.3)

#### 2.4.1 Continuous mode

Continuous conduction is defined as the inductor current not being 0 A for any appreciable length of time during the entire switching cycle. By this definition, and assuming a perfect inductor, the total energy entering the inductor for  $t = 0t_T s$  to  $t = Dt_T s$  must be equal to energy transferred out of the inductor for the remainder of the switching cycle. This is expressed as:

$$\Delta i_{Lon} + \Delta i_{Loff} = 0 \tag{2.4}$$

Substituting (2.2) and (2.3) into (2.4) yields:

$$0 = \frac{V_{IN}Dt_T}{L} + \frac{V_{OUT}(1-D)t_T}{L}$$

(2.5)

Solving for *V*<sub>OUT</sub>/*V*<sub>IN</sub> yields:

$$\frac{V_{OUT}}{V_{IN}} = \left(\frac{-D}{1-D}\right) \tag{2.6}$$

(2.6) shows that the conversion ratio is determined only by the duty cycle D. Varying the value of D allows the output to be larger, smaller, or equal to in magnitude to the input. The effect of D is summarised in Table 2.1.  $V_{OUT}$  is expressed as a magnitude because the base buck-boost converter topology is an inverting converter.

| Duty cycle         | Converter output     | <b>Conversion type</b> |

|--------------------|----------------------|------------------------|

| 0 < <i>D</i> < 0.5 | $ V_{OUT}  < V_{IN}$ | Buck                   |

| 0.5 < D < 1        | $ V_{OUT}  > V_{IN}$ | Boost                  |

| <i>D</i> = 0.5     | $ V_{OUT}  = V_{IN}$ | None                   |

**Table 2.1** Effect of duty-cycle on V<sub>OUT</sub>.

Table 2.1 categorises the conversion behaviour as either buck, boost, or none. When 0 < D < 0.5, the converter 'bucks' the input voltage such the output voltage is less than the input. For 0.5 < D < 1, the converter 'boosts' the input voltage such that the output voltage is larger than the input. When D = 0.5, the converter neither bucks nor boosts the input and the output voltage is equal to the input.

#### 2.4.2 Discontinuous mode

Discontinuous conduction is defined as an operating mode where the inductor current is 0 A for an appreciable amount of time in the switching cycle. The derivation of a continuous operation assumes energy is transferred continuously through the entire cycle. The derivation of equations of the discontinuous mode must account for the time in the cycle during which there is no conduction. This maximum inductor current with  $S_2$  closed and  $S_1$  open is given by:

$$0 = \frac{V_{OUT}\delta t_T}{L} + \frac{V_{IN}Dt_T}{L}$$

(2.7)

Where  $\delta$  is the differential time that the inductor current is 0 A. The maximum current in the on state with S<sub>1</sub> closed is given by:

$$I_{L_{MAX}} = \frac{V_{IN}Dt_T}{L}$$

(2.8)

And the load current  $I_{OUT}$  in the off state with S<sub>2</sub> closed is given by:

$$I_{OUT} = \frac{I_{L_{MAX}}}{2}\delta \tag{2.9}$$

Substituting (2.8) and (2.9) into (2.7) allows the output voltage to be expressed as:

$$V_{OUT} = -\frac{V_{IN}D^2 t_T}{2LI_{OUT}}$$

(2.10)

(2.10) shows that in the discontinuous conduction state, the output voltage is a function of the output current. The discontinuous mode is unable to operate effectively in practice unless the effect of variable  $I_{OUT}$  is considered.

#### CHAPTER 2

Two techniques may be used to account for the dependence on  $I_{OUT}$ . The maximum current that can be sourced by the converter can be constrained, allowing for *L* to be chosen such that the converter does not enter the discontinuous mode. Alternatively, a closed loop controller can be used to modulate the value of *D* such that the converter remains in the continuous mode.

To keep the converter in continuous mode, the minimum value for L is given by:

$$L_{MIN} = \frac{(1-D)^2 R_{load}}{2f}$$

(2.11)

Where *f* is the switching frequency of the converter in Hz and  $R_{load}$  is the effective load resistance seen by the converter for a given output voltage  $V_{OUT}$ .

The minimum capacitance required for a desired output voltage ripple,  $V_r$ , is given by:

$$C_{MIN} = \frac{DV_{OUT}}{V_r R_{load} f}$$

(2.12)

Appropriate choice of L and C will yield a converter which does not enter discontinuous conduction operation if second order and parasitic effects are negligible. However, this is not applicable in practice, and the operation of both continuous and discontinuous modes benefit from external control.

#### 2.5 DC-DC CONVERTER FEEDBACK CONTROL

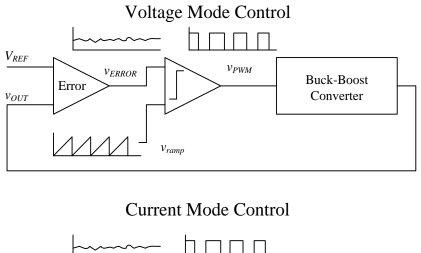

Two popular techniques for feedback control for buck-boost converters may be classified as either current mode control, or voltage mode control [19]. A simplified topology for each is shown in Figure 2.3.

Figure 2.3. Voltage mode control and current mode control topologies.

As in Figure 2.3, voltage mode control (VMC) senses a scaled value of the output voltage which is compared to a reference voltage by an error amplifier. The result,  $v_{ERROR}$ , is compared to a fixed ramp which is modulated through a comparator to create the pulse width modulated (PWM) control signal for the converter. VMC benefits from simple implementation both from a hardware and control theory perspective. VMC also provides excellent load regulation, since variations in loading are quickly compensated for by the error amplifier. Line regulation is hampered by changes in the line voltage needing to propagate to the output before being accounted for in the control loop.

Current mode control (CMC) alleviates the delayed reaction to line changes by incorporating a feed forward network, where the input is sensed and forms part of the control network. The current in the inductor is sensed and used to generate the periodic ramp signal required for PWM. This improves the dynamic response of the converter to changes at its terminals at the cost of additional complexity, both in controller design and hardware implementation. Current mode control is well suited to applications with variable input voltage, such as a sensor node in a WSN which is powered through energy harvesting.

#### 2.6 CMOS CONVERTER DESIGNS

There has been extensive research and development of CMOS DC-DC converters. Researchers focus on alternative converter control topology, application specific improvements, and converter optimisation.

#### 2.6.1 Inverting and non-inverting DC-DC converters

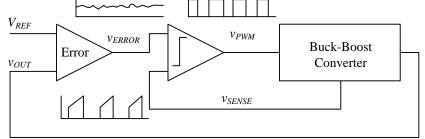

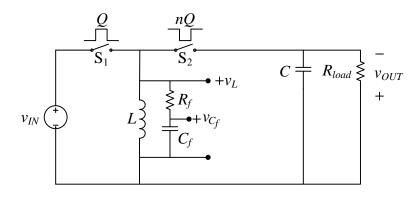

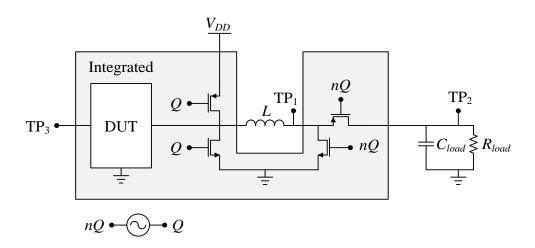

DC-DC converters are classified as either inverting or non-inverting. The output of noninverting DC-DC converters has the same polarity as that of the input relative to the input's ground reference [18]. The output of an inverting DC-DC converter has inverted polarity relative to the input's ground reference. The circuit in Figure 2.1 is an example of an inverting DC-DC converter. The DC-DC converter topology in Figure 2.4 makes use of additional switching to generate a non-inverted output [20].

Figure 2.4. Non-inverting DC-DC converter topology.

This DC-DC converter shown in Figure 2.4 uses two additional switches to effectively reverse the polarity of *L* during the second phase of the conversion cycle.  $S_1$  and  $S_2$  are closed ( $S_3$  and  $S_4$  are open) for the first phase of the conversion, charging *L*.  $S_3$  and  $S_4$  ( $S_1$  and  $S_2$  are open) are closed for the second phase of the conversion. The output voltage of this non-inverting DC-DC converter is given by:

$$\frac{V_{OUT}}{V_{IN}} = \left(\frac{D}{1-D}\right) \tag{2.13}$$

This non-inverting design is frequently used in fully integrated designs where the cost and complexity of additional devices is negligible. The non-inverting configuration also allows for a common ground reference between input and output.

#### 2.6.2 Alternative CMOS converter control topologies

An integrated DC-DC converter will often have a single power source, such as a battery or power reservoir, and must efficiently transform the stored energy to the voltage levels required by several different subsystems. Such a system is presented in [21] where a single inductor boost converter drives four low dropout regulators (LDOs). The buck-boost converter may be integrated with other system elements to improve its overall efficiency. Such a design is presented in [22], where the converter topology is combined with a power amplifier to improve overall efficiency by dynamically adjusting converter output as required by the PA.

In mobile applications, there are stringent requirements of DC-DC converters. Power sources such as batteries have variable output voltage which require the converter to have a wide input and output range with good line and load regulation. The portable, compact, or integrated device being powered has multiple power usage modes varying from low to high. The highly variable load must also be accommodated by the converter. These requirements have driven the development of multimode control schemes which offer efficiency over the wide range of input and output conditions [23]. [24] presents a minimum energy tracking loop which actively monitors the converter load and dynamically adjusts the output voltage of the converter to deliver the minimum amount of power.

Analogue control schemes are prevalent in converter designs, with current mode control being used extensively. Analogue control schemes are susceptible to internal variations which influence the closed loop response of the control network. Digitally controlled DC-DC converters have been developed to counter these variations and to introduce additional multimode operation [25].

#### 2.6.3 Integrated CMC converters

The inherent low-cost per device in IC technology counters any cost factors when implementing CMC. The primary disadvantage of CMC is the additional expense associated with the increased complexity of the CMC. This expense is not a limiting factor for integrated implementations.

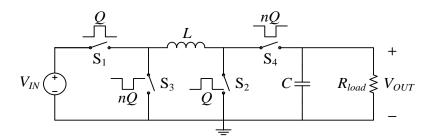

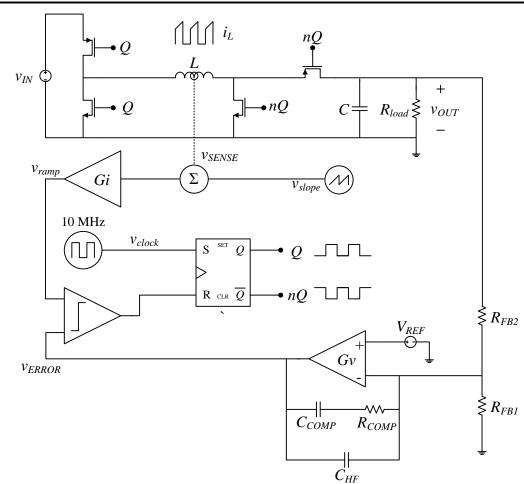

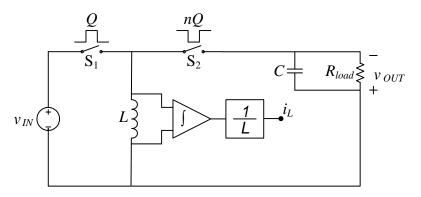

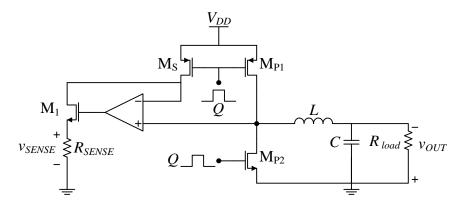

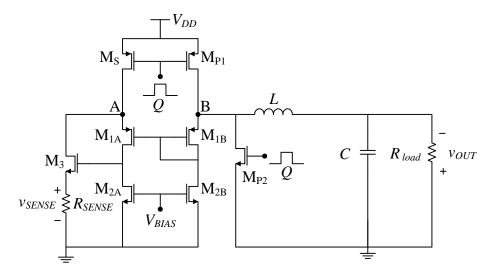

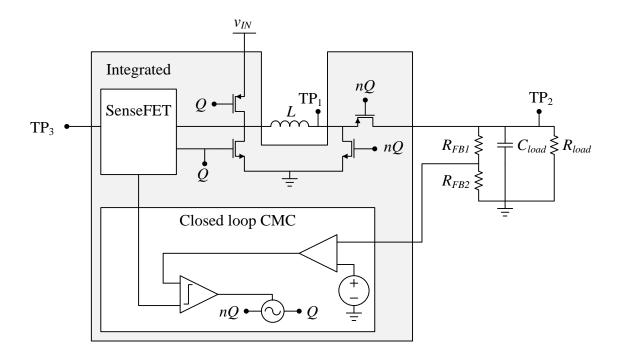

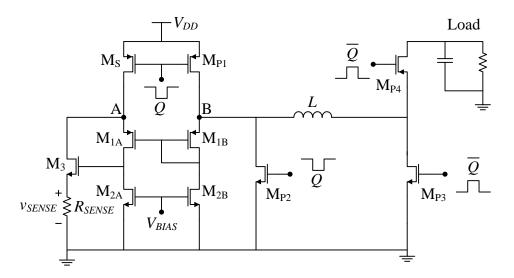

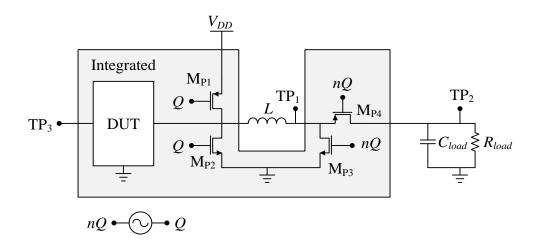

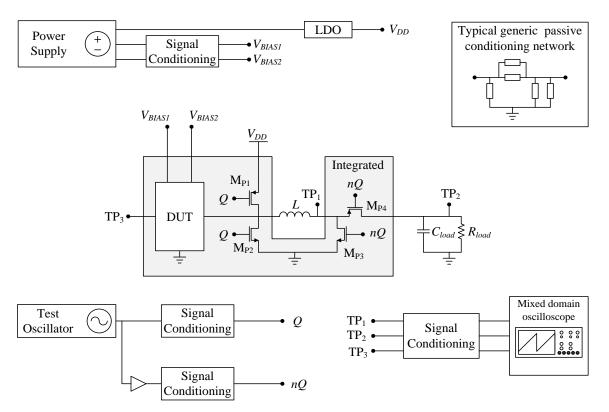

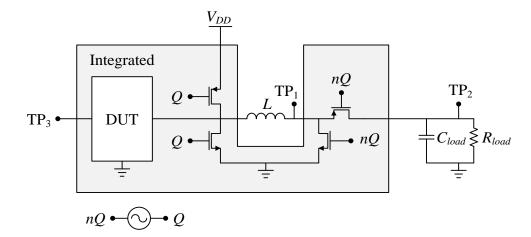

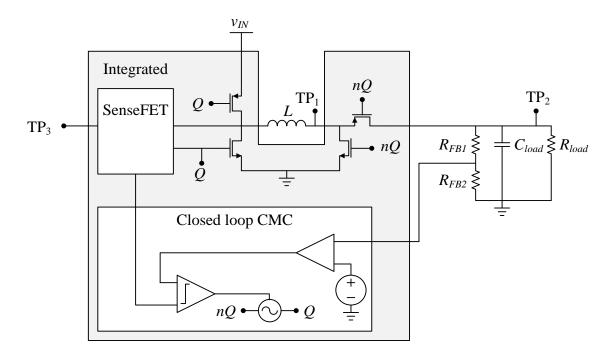

[26], [27], and [20] present typical CMC based DC-DC converters with the control loop implemented with rudimentary analogue circuits and sensors. Figure 2.5 shows a generalised integrated buck-boost converter with analogue CMC control.

**CHAPTER 2**

Figure 2.5. Generalised non-inverting buck-boost converter with analogue current mode control.

The simplified CMC topology of Figure 2.3 has been expanded in Figure 2.5 to show the primary circuits required for an IC implementation. The DC-DC converter by [28] improves on the typical designs by identifying the internal CMOS current sensor, which converts the inductor current to a scaled sensed voltage, as one of the circuits which can be improved to increase overall efficiency. The converter is implemented in a 0.6  $\mu$ m process with a maximum input of 5.2 V.

Chapter 4 demonstrates that these designs – which are effective in their respective technology nodes – become ineffective when scaled down to 130 nm. The techniques used in these implementations need to be updated or changed to maintain functionality.

#### 2.7 CMOS BASED CURRENT SENSING

Current sensing circuits range from simple passive networks to active current sensor sensors. A summary of common sensor types is presented in [29]. The purpose of these circuits is to measure the current in the converters inductor. Current sensing circuits perform either a direct measurement of the current in the inductor or infer the current through indirect measurement of another circuit parameter.

#### 2.7.1 General current sensing techniques

The circuit in Figure 2.6 uses the most rudimentary form of current measurement by placing a resistor  $R_{SENSE}$  in series with the inductor.

Figure 2.6. Rudimentary current sensing network.

The current in the resistor will be the same as that of the inductor and the sense current can be converted to a voltage ( $v_{SENSE}$ ) by applying Ohm's Law to the voltage drop over  $R_{SENSE}$ . The primary disadvantage of this technique is that in each switching cycle power is lost through  $R_{SENSE}$ , which loads the converter and reduces the overall efficiency. To circumvent this power loss, lossless current sensing techniques have been developed.

In integrated switch mode converters, switches  $S_1$  and  $S_2$  in Figure 2.6 are implemented with power transistors. This integration allows the on resistance of the device to be used to replace  $R_{SENSE}$  without introducing additional losses. This technique is inexpensive, but inaccurate, as the device on resistance is susceptible to PVT variations [30].

There are several techniques which infer the inductor current by measuring the voltage across the inductor L with varying degrees of accuracy. The simplest approach is to have a series RC network in shunt with the inductor, as shown in Figure 2.7. If the effective series

resistance (ESR) of the inductor L and the inductance of L are known, then the inductor current can be determined for appropriate values of  $R_f$  and  $C_f$  [31].

Figure 2.7. Voltage filtering network in shunt with converter inductor.

The technique employed by the circuit of Figure 2.7 relies on the designer knowing the characteristics of the inductor used in order to select  $R_f$  and  $C_f$ . Integrated switch mode converters which are not designed for a specific value of L would also need  $R_f$  and  $C_f$  to be selected. Additionally, the accuracy of this technique is susceptible to variation in component values. This limitation is overcome by integrated circuits which measure the inductor value and the inductor effective series resistance (ESR) [9]. A DC-DC converter that is able to measure the value of the power inductor used can adapt the converter control loop to provide accurate control.

Sensorless current sensing techniques, such as those employed by [32], determine the current in the inductor by integrating the differential voltage over the inductor. This technique is shown in figure and directly applies the current voltage relationship for inductors given by:

$$i_L = \frac{1}{L} \int_{t_0}^{t_1} v_L(\tau) d\tau + i_L(t_0)$$

(2.14)

With  $t_0$  to  $t_1$  the period over which the current is being sensed.  $i_L(t_0)$  is the initial current value.

Figure 2.8. Sensorless current sensing circuit.

The application of (2.14) requires, in Figure 2.8, the value of *L* to be known, which is practically cumbersome for integrated circuits, and is also susceptible to variations in the value of *L*.

#### 2.7.2 Integrated current sensing – The SenseFET

In CMOS applications where the switches in the DC-DC converter are implemented with integrated power transistors on the same die as the integrated controller, the SenseFET<sup>5</sup> approach to current sensing offers many advantages [29].

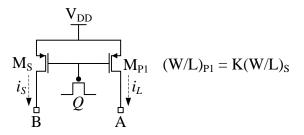

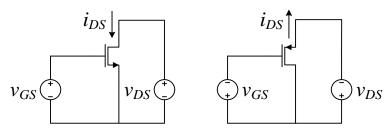

The SenseFET fundamental circuit is shown in Figure 2.9.

Figure 2.9. Fundamental SenseFET circuit.

In Figure 2.9, the aspect ratio of  $M_{P1}$  is chosen to be much larger than that of  $M_{S}$  effectively negating the power consumption of  $M_{S}$ . The gates of  $M_{S}$  and  $M_{P1}$  are driven by the same signal. In a DC-DC converter application, the gates are driven by the converter's internal switching signal.

Department of Electrical, Electronic and Computer Engineering University of Pretoria

<sup>&</sup>lt;sup>5</sup> SenseFET is a concatenation of the word sense and the abbreviation for field effect transistor (FET).

If the voltage at nodes A and B is held constant, and ideal transistors are assumed to be operating in saturation, then the current  $i_S$  is given by:

$$i_{S} = \frac{\dot{k_{p}}}{2} \left( \frac{W}{L} \right)_{S} (v_{GS} - V_{t})^{2} \text{ and } i_{L} = \frac{\dot{k_{p}}}{2} K \left( \frac{W}{L} \right)_{S} (v_{GS} - V_{t})^{2}$$

(2.15)

$$i_S = \frac{i_L}{K} \tag{2.16}$$

The gates of  $M_S$  and  $M_{P1}$  driven by the same signal source and the devices only differ in aspect ratio. This configuration results in  $i_S$  being a scaled version of  $i_L$  by (2.15) and (2.16).

A simple SenseFET implementation is shown in Figure 2.10. The opamp is used to equalise the drain voltages of  $M_S$  and  $M_{P1}$ .

Figure 2.10. Simple SenseFET implemented with idealised components.

The circuit in Figure 2.11 is also commonly used [28]. Transistor pair  $M_1$  and  $M_2$  form a simple differential amplifier.  $M_2$  provides biasing for  $M_1$ . The gates of  $M_{1A}$  and  $M_{1B}$  are connected and  $M_{1B}$  is diode connected.

Figure 2.11. SenseFET implemented with a greatly simplified amplifier.

If all transistors are assumed to be ideal, then on every cycle circuit operation is given by applying Kirchhoff's Current Law (KCL) at nodes A and B:

$$i_{DSM_{P1}} = K i_{DSM_S} \tag{2.17}$$

$$i_L = i_{DSM_{P1}} - i_{DSM_{1B}} \tag{2.18}$$

$$i_{DSM_3} = i_{DSM_S} - i_{DSM_{1A}} \tag{2.19}$$

Since

$$i_L + i_{DSM_{1B}} \tag{2.21}$$

(2.20)

$$\iota_{DSM_S} = \frac{1}{K}$$

(2.21)

$$i_{DSM_3} = \frac{i_L}{K} + \frac{i_{DSM_{1B}}}{K} - i_{DSM_{1A}}$$

(2.22)

$$i_L \gg i_{DSM_{1B}} \tag{2.23}$$

From Ohm's Law

$$v_{SENSE} = R_{SENSE} i_{DSM_3} \tag{2.24}$$

$$v_{SENSE} \approx R_{SENSE} \left( \frac{i_L}{K} - i_{DSM_{1A}} \right)$$

(2.25)

Whereas in Figure 2.9, *K* is the scaling factor applied to the aspect ratio of  $M_{P1}$  in terms of  $M_{S}$ . The derivation of  $v_{SENSE}$  in (2.25) assumes and ideal device with negligible second order effects.  $v_{SENSE}$  is thus only a function of  $i_L$ , with  $R_{SENSE}$ , *K*, and  $i_{DSM1A}$  constants.

(2.17) to (2.25) are derived assuming the current through a transistor from source to drain  $(i_{DS})$  in saturation is given by:

$$i_{DS} = \frac{k'}{2} \left(\frac{W}{L}\right) (v_{GS} - V_t)^2$$

(2.26)

Where:

| k'                         | Process transconductance parameter |

|----------------------------|------------------------------------|

| $\left(\frac{W}{L}\right)$ | Transistor aspect ratio            |

| $v_{GS}$                   | The gate source voltage            |

| V <sub>t</sub>             | Device threshold voltage           |

The inclusion of channel modulation effects to (2.26) results in:

$$i_{DS} = \frac{k'}{2} \left(\frac{W}{L}\right) (v_{GS} - V_t)^2 (1 + \lambda v_{DS})$$

(2.27)

Where  $v_{DS}$  is the drain source voltage and  $\lambda$  is a process parameter representing the effect of channel length modulation in  $i_{DS}$ . This inclusion significantly effects the derivation of  $v_{SENSE}$  in terms of  $i_L$ . The effect of channel length modulation on SenseFET performance is considered in Chapter 4.

# 2.7.3 Improved SenseFETs

Application specific improvements to the standard SenseFET design are prevalent in literature. Improvements address the basic SenseFET circuit topology by increasing measurement bandwidth, increased linearity, low-voltage operation, and to combat process specific parameters. In the concluding section of this Chapter summarises contributions from the literature and contextualises the work in this dissertation.

# 2.8 TECHNOLOGY SHORTCOMINGS

The characteristics of the CMOS process which has been utilised need to be accounted for in the integrated circuit design. The available low-voltage process through the MOSIS program is the IBM 8HP BiCMOS process at the 130 nm technology node. The maximum allowable voltage in this process is below that of technologies used in the literature. This subsection discusses the predominant process and device characteristics which influence the work in this dissertation.

#### 2.8.1 Channel length modulation

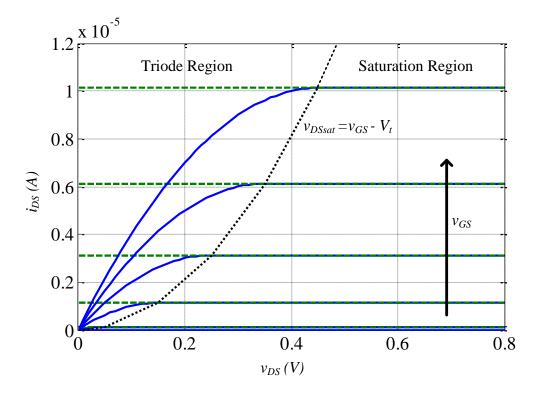

The idealised large-signal model of a field effect transistor (FET) operating in saturation has the drain to source current,  $i_{DS}$ , given by (2.26). Assuming a linear device,  $i_{DS}$  when the transistor is operating in the triode region is given by:

$$i_{DS} = k' \left(\frac{W}{L}\right) \left[ (v_{GS} - V_t) v_{DS} - \frac{1}{2} v_{DS}^2 \right]$$

(2.28)

A plot of  $i_{DS}$ - $v_{DS}$  for the idealised large signal model is shown in Figure 2.12.

Figure 2.12. Idealised *i*<sub>DS</sub>-*v*<sub>DS</sub> characteristic curves.

In Figure 2.12 the value of  $i_{DS}$  in saturation has been extrapolated to illustrate that the  $i_{DS}$ - $v_{DS}$  gradient in saturation is 0. This model also assumes an infinite output resistance. The basis of this assumption is that once  $v_{DS} = v_{DSsat}$  further increases in  $v_{DS}$  has no physical effect on the conduction channel of the FET. The output resistance in saturation is defined by the  $i_{DS}$ - $v_{DS}$  gradient in saturation with constant  $v_{GS}$  or:

$$r_0 = \frac{\Delta v_{DS}}{\Delta i_{DS}} \tag{2.29}$$

Since increasing  $v_{DS}$  beyond  $v_{DSsat}$  in saturation does not affect  $i_{DS}$ ,  $r_0$  must be infinite [33].

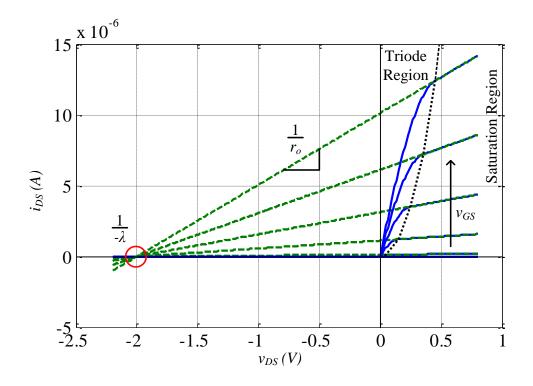

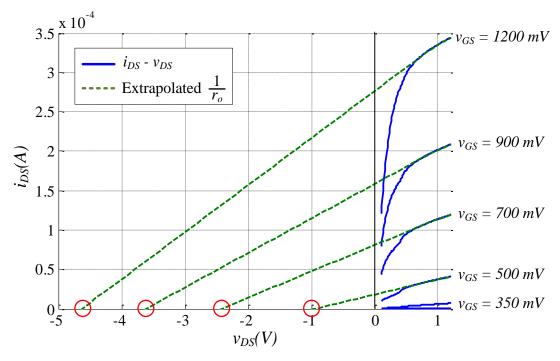

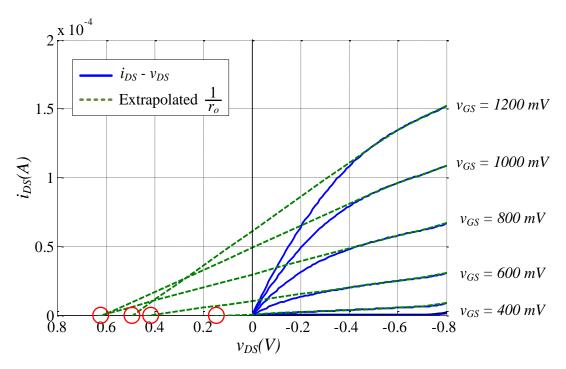

In practice the idealised large signal model is inadequate because an increase in  $v_{DS}$  beyond  $v_{DSsat}$  physically effects the conduction channel in the FET. Increasing  $v_{DS}$  beyond  $v_{DSsat}$  modulates the channel length, causing  $i_{DS}$  to vary with  $v_{DS}$  in saturation. The significance of channel length modulation in a target process should be considered when developing circuit designs. Channel length modulation is modelled by including a weighting factor of  $(1+\lambda v_{DS})$  as in (2.27). Figure 2.13 illustrates the effect of severe channel length modulation on the  $i_{DS}-v_{DS}$  characteristic curves.

Figure 2.13. *i*<sub>DS</sub>-*v*<sub>DS</sub> characteristic curves with channel length modulation incorporated.

In Figure 2.13 the value of  $i_{DS}$  has once again been extrapolated to illustrate effect of channel length modulation, which introduces a finite output resistance  $r_o$ .  $r_o$  may behave dynamically in circuits where  $i_{DS}$  and  $v_{DS}$  fluctuate. The output resistance is defined by:

$$r_{O} = \left[\lambda \frac{k'}{2} \frac{W}{L} (v_{GS} - V_{t})^{2}\right]^{-1}$$

(2.30)

$$r_0 \simeq [\lambda I_{DS}]^{-1} \tag{2.31}$$

$$r_0 \simeq \frac{V_A}{I_{DS}}$$

with  $V_A = \frac{1}{\lambda}$  (2.32)

$V_A$  is a process parameter referred to as the Early voltage.  $I_{DS}$  is the instantaneous DC drain to source current for a fixed  $V_{DS}$  and  $V_{GS}$ . In practice the determination of  $V_A$  is difficult and is usually derived from experimental data [30].

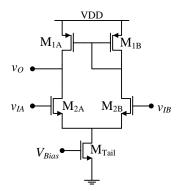

Figure 2.14 illustrates a simple CMOS differential amplifier with active load.

Figure 2.14. Simple CMOS differential amplifier with active load.

The large-signal gain of the differential pair M<sub>2</sub> is given by:

$$A_{M_2} = -g_m(r_{oM_1}||r_{oM_2})$$

(2.33)

Where  $r_o = \frac{V_A}{I_{DS}}$  and

$$g_m = \frac{\dot{k_n}}{2} \left(\frac{W}{L}\right) (v_{GS} - V_t) (1 + \lambda v_{DS})$$

(2.34)

(2.33) and (2.34) are both functions of  $V_A$  with (2.33) being a strong function of  $i_{DS}$ . This dominance manifests as an unbalanced operation of the differential pairs, as variance in  $i_{DS}$  causes the small-signal and large-signal parameters of the transistors to vary with  $i_{DS}$ . The effects of  $V_A$  on circuit performance is discussed further in Chapter 4 of this dissertation.

# 2.8.2 Velocity saturation

The average horizontal electric field in a FET device is  $V_{DS}/L$  [30]. At low field strengths, the relationship between field strength and carrier velocity in the transistor is linear. As field strength increases, either by increasing  $V_{DS}$  or decreasing L, the carrier velocity does not increase, however, rather approaching the scattering-velocity limit.

If the horizontal electric field is small, the drift velocity is given by:

$$v_d(\mathbf{y}) = \mu_n E(\mathbf{y}) \tag{2.35}$$

$$E(y) = \frac{dV}{dy} \tag{2.36}$$

Where E(y) is the horizontal electric field, y is the axis along the length of the device from source to drain, dV is the incremental voltage drop along dy, and  $\mu_n$  is the average electron mobility. (2.35) shows that the  $v_d$  behaves linearly with E(y).

At higher field strengths, this linear relationship is no longer valid and the drift velocity is instead approximated by:

$$v_{dsc} \approx \frac{\mu_n E}{1 + \frac{E}{E_c}}$$

(2.37)

Where  $E_c$  is the critical field value with  $E_c \approx 1.5 \times 10^6$  V/m.

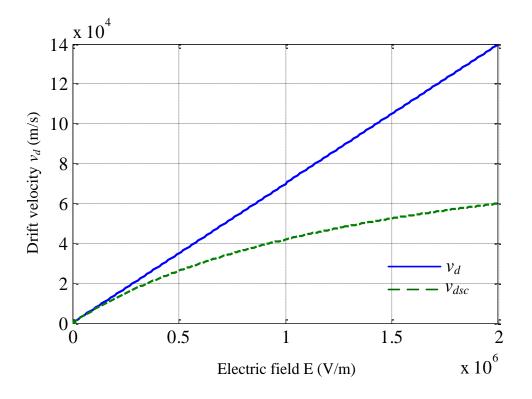

The plot in Figure 2.15 is of (2.35) and (2.37).

Figure 2.15. Electron drift velocity for linear and approximate models.

In Figure 2.15 it can be seen that for low electric field strength ( $E < 2 \times 10^5$ ) the linear approximation of  $v_d$  agrees with  $v_{dsc}$ . At higher field strengths, the linear approximation is no longer accurate. At a field strength of  $E = 1.5 \times 10^6$  V/m, the drift velocity predicted by the linear approximation of (2.35) is nearly double that of the more accurate prediction of (2.37). In a process with a gate length of 130 nm, applying (2.36) show that  $v_{DS} > 200$  mV is enough to generate an electric field larger than the critical field value  $E_c$ .

From [30],  $I_{DS}$  in the triode and saturation regions (assuming fixed  $V_{DS}$ ) is given by:

$$i_{DS} = \frac{k'_n}{2\left(1 + \frac{v_{DS}}{E_c L}\right)} \frac{W}{L} \left[2(v_{GS} - V_t)v_{DS} - v_{DS}^2\right]$$

(2.38)

$$I_{DS} \cong \frac{k'_n}{2\left(1 + \frac{v_{GS} - V_t}{E_c L}\right)} \frac{W}{L} (v_{GS} - V_t)^2$$

(2.39)

With (2.38) applying to the triode region and (2.39) applying to the saturation region.

The overall effect of velocity saturation is that it reduces the expected drain-source current in the device as predicted by (2.27) and (2.28). In devices with short channel lengths this effect becomes more pronounced as the electric field strength increases as channel lengths become shorter.

# 2.8.3 Low-voltage limitations

In low-voltage processes such as the IBM 8HP 130 nm BiCMOS process, analogue circuits must be able to operate with a low voltage supply rail to prevent voltages in the circuit from exceeding the oxide breakdown voltage of each device. This low-voltage limitation restricts available headroom for cascaded designs. Low-voltage processes also have reduced device thresholds voltages ( $V_t$ ) which can increase static power dissipation [34]. Designing for low-voltage requires the application of more complex circuits using folded structures [30] or new design approaches that make use of FETs that operate in the sub-threshold ( $v_{DS} \ll V_t$ ) region [35].

#### 2.8.4 Other device limitations

The process utilised in this study is primarily affected by channel length modulation and low operating voltage. These are not the only short channel effects (SCEs) which degrade the performance of FET devices with sub-micron and deep sub-micron gate lengths. Strong electrical fields in the vicinity of the device gate, and thinner oxide layers as technology scales down has resulted in gate leakage or tunnelling currents becoming significant [30],

[36]. The device design is complicated when scaling down for a lower supply voltage by the non-scaling Si bandgap potential. Thus, device design choices which account for the bandgap potential tend to increase  $V_t$  when it is preferred to have a lower  $V_t$  [36].

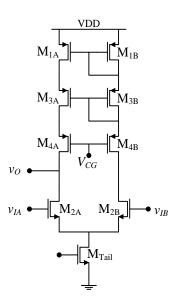

# 2.9 CMOS CASCODE TECHNIQUES

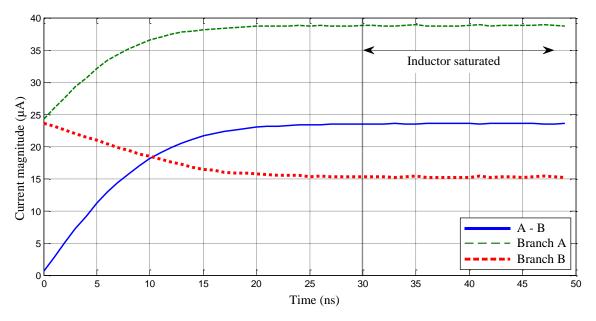

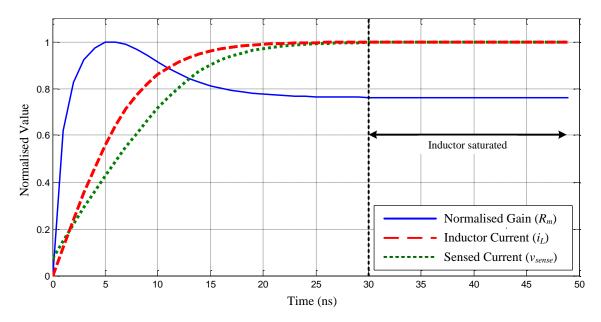

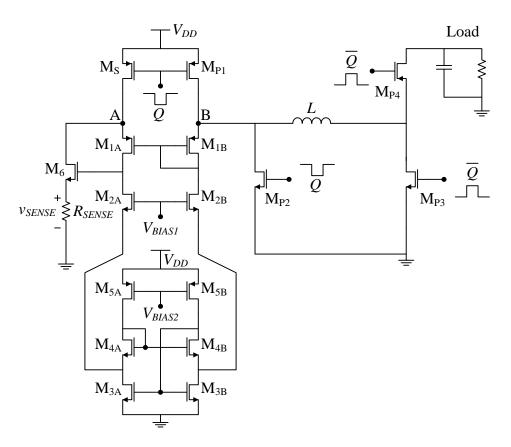

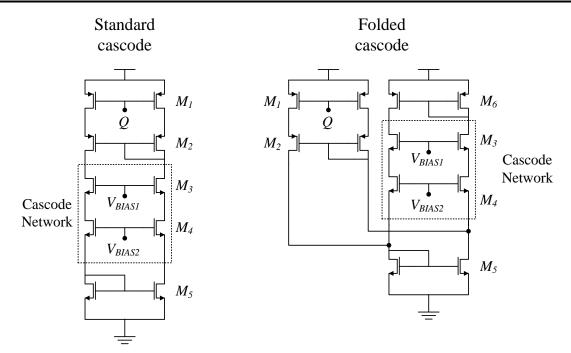

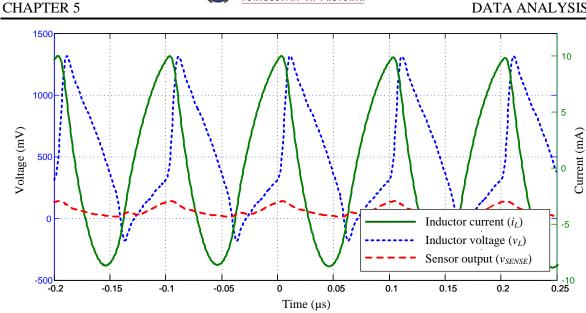

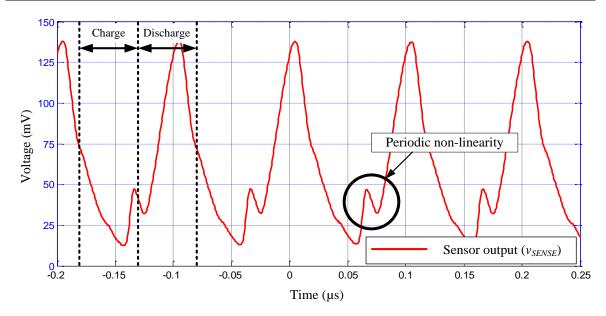

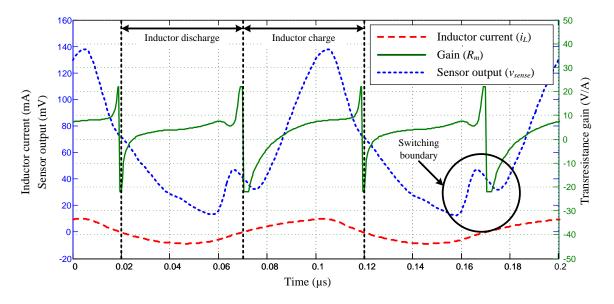

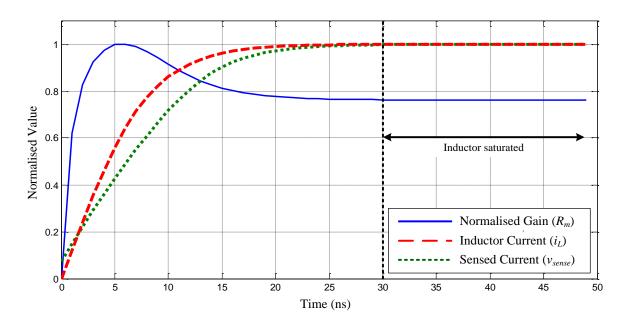

CMOS processes with sub-micron gate lengths are susceptible to significant channel length modulation [34]. (2.30) - (2.32) show that the increased prevalence of channel length modulation decreases the finite output resistance. In analogue amplifier stages, the output resistance,  $g_m r_o$ , is a key parameter in determining the large- and small-signal gain of the amplifier.  $g_m r_o$  Can be increased by using active load cascodes which effectively multiply  $g_m r_o$  [30]. The cascoding technique vertically stacks additional active load devices in an amplifier to increase gain. Figure 2.16 expands the simple differential amplifier of Figure 2.14 to include a cascoded active load.