ORIGINAL RESEARCH

The Institution of Engineering and Technology WILEY

# The effect of temperature variation on the transient response of RF PIN diode limiters for very high frequency applications

Cornelius Johannes Botha

Department of Electrical, Electronic, and Computer Engineering, University of Pretoria, Pretoria, South Africa

Correspondence Cornelius Johannes Botha.

Email: u10690922@tuks.co.za

Funding information National Research Foundation, Grant/Award Number: UID137950

#### Tinus Stander

### Abstract

This work presents the effect of temperature change on the capacitance of silicon PIN diodes and the resulting change in performance of RF limiters at very high frequency (VHF). Device temperatures were varied between -25 °C and 100 °C, with small-signal parameters (including device capacitance) extracted at regular temperature increments and bias voltages from -20 Vdc to +3 Vdc using a multi-bias parameter extraction method. It was found that the junction capacitance of the four PIN diodes under investigation increases with temperature, as expected from carrier lifetime behaviour, while results also confirmed prior observations of an inverse relationship between forward-biased series resistance and temperature. Devices were subsequently tested in two different limiter topologies through high-power transient measurements. It was found that the combination of increased capacitance and decreases the flat leakage of a limiter. It was also concluded that, for VHF, an anti-parallel topology provides the best performance over a wide range of temperatures.

#### **KEYWORDS**

limiters, parameter estimation, p-i-n diodes, semiconductor device models

### 1 | INTRODUCTION

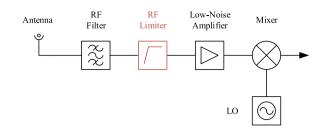

In modern communication systems, a single antenna is often used for both transmitting and receiving signals [1]. In highpower systems, such as very high frequency (VHF) radios used for military, signals can leak from the transmission path into the receiver path [2]. In other applications, such as mobile electronic warfare (EW) systems, a broadband receiver antenna is frequently found in very close proximity to a high-power transmitter antenna that occupies the same frequency spectrum [3]. A simplified superheterodyne communications receiver is shown in Figure 1. An RF limiter is a power attenuation device that is inserted between a source, such as an antenna, and sensitive components at the start of a receiver chain and is designed to prevent high-power signals from passing into the receiver, whilst allowing the receiver to function unprotected in the absence of such signals [2, 4-8]. The limiter has, since its invention in the 1960s, become a key

component in modern receiver protector designs to provide electromagnetic protection to sensitive circuit components at the front-end of a receiver chain [4–6, 9–12].

Military communication and EW systems commonly use the VHF band (30–300 MHz) and are often used by personal and armoured vehicles that are deployed in harsh environments. Systems are exposed to extreme device temperatures during their service in the field. It is, therefore, critically important to understand performance variation due to ambient temperature variation.

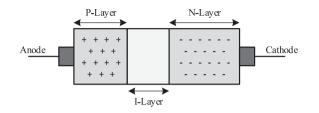

PIN diodes, as depicted conceptually in Figure 2, are generally preferred to other solid-state alternatives such as Schottky diodes for RF limiters because of their power handling capability and slower response times (which ensures that solid-state switching follows the RF envelope rather than rectifying the RF signal). A PIN diode with a thick I-layer has more capacitance and a slower response and longer recovery time than a PIN diode with a thin I-layer but also has greater

1

This is an open access article under the terms of the Creative Commons Attribution-NonCommercial-NoDerivs License, which permits use and distribution in any medium, provided the original work is properly cited, the use is non-commercial and no modifications or adaptations are made.

<sup>© 2024</sup> The Author(s). IET Microwaves, Antennas & Propagation published by John Wiley & Sons Ltd on behalf of The Institution of Engineering and Technology.

FIGURE 1 Simplified communications receiver.

FIGURE 2 PIN diode layout.

power handling capability [13]. Studies that investigated the effect of ambient temperature on PIN diodes focused primarily on the change in diode resistance in the forward-bias state and at frequencies outside the VHF band [7, 8, 14-19], or changes due to self-heating rather than ambient variation [20]. It is, however, known that the spike leakage of a PIN diode limiter can be influenced by the response time of the PIN diode, as more energy can pass through the limiter before it provides sufficient limiting [3, 12]. Spike leakage is dependent on how fast a diode switches between the off and on state. The response time and recovery time of the PIN diode is directly related to the diode's carrier lifetime [1, 5, 11, 21], and the carrier lifetime is in turn influenced by temperature and the capacitance of the I-layer [8, 14, 22]. These effects are compounded in an overall response of higher transient spikes in diodes with thicker I-layers [23].

However, despite these known dependencies, there is no systemic study investigating the effect temperature has on the capacitance of PIN diodes and the resulting impact on a PIN diode limiter's transient performance, specifically for diodes in limiters used in applications that operate in the VHF band.

Recent literature on PIN diode and PIN diode limiters has focused on improved circuit or device design [24–26] (including integration with amplifiers [27, 28], filters [29, 30], or reflectionless balanced networks [31]), improved circuit modelling [32] or modelling by other means such as neural networks [33], the application of novel materials such as diamond [34], improved packaging [35–38], MMIC integration [39, 40], reliability studies [41], and advances in device modelling [42–45]. While the effect of incident power or pulse length [46] on self-heating of the device is often studied [47– 51], as is changes in CW operation due to temperature variation [52–54], changes in transient behaviour due to ambient temperature variation are not. While spike leakage in VHF limiters was studied extensively in ref. [23], the impact of temperature on this leakage was not. This paper aims to address this shortcoming in literature by providing, for the first time, explicit data on capacitance variation over temperature in PIN diodes, as well as studying the effect of temperature variation on the transient response of PIN diode-based limiters.

A brief review of a PIN diode's operation and known temperature dependencies is provided in Section 2. Section 3 outlines this work's methodology to PIN diode modelling, based on experimental measurements under temperature variation and presents the small-signal model variation of the selected PIN diodes at different bias points and temperatures. Section 4 presents the measurement setup and results of the transient operation at different temperatures, with the findings summarised in Section 5.

### 2 | REVIEW OF PIN DIODES AND MODELLING

While both the theory and techniques of PIN diodes and limiters are well-documented, a short overview is presented here for the sake of the later discussions.

### 2.1 | Review of structure and properties

PIN diodes can be considered as a bias-controlled variable resistor at RF and microwave frequencies [1, 6, 10, 55]. The P-layer (Figure 2) is a thin layer with low resistance and is heavily doped with p-type acceptor impurities (or holes), while the N-layer is heavily doped with n-type donor impurities (or electrons). The I-layer, or intrinsic layer, is an undoped layer containing very little impurities and, as a result, has a high resistivity. In commercial diodes, the intrinsic layer is rarely purely undoped but is often lightly doped with n-type impurities [1, 10, 11]. The I-layer can also be lightly doped with gold atoms to substantially reduce the minority carrier lifetime.

However, gold adds to the cost of the diode and increases the minimum resistance of the PIN diode [1].

The electrical characteristics of a PIN diode also depend significantly on the I-layer properties. These include the stored charge (which controls the resistance and capacitance), carrier lifetime (which governs the RF resistance and affects the response time, spike leakage, recovery time, and bandwidth), and power handling (through the thickness of the I-layer). For example, a PIN diode with a thick I-layer is expected to have high power handling capability but is too slow to be used in stand-alone RF limiter applications because of its long response time [7].

### 2.2 | Forward-biased equivalent circuit

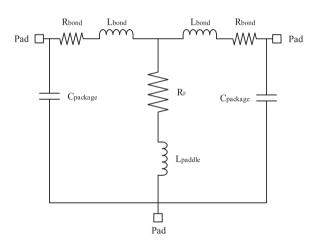

A forward-biased PIN diode behaves as a current-controlled resistor that presents a linear resistance to the flow of RF current through the diode. It is this property that enables a PIN diode to be used as an RF power control element [55]. The equivalent circuit of a forward-biased, shunt-grounded, PIN diode is shown in Figure 3.

The only intrinsic steady-state diode property modelled is the forward-biased resistance,  $R_F$ , which is a function of the forward-biase current,  $I_F$ . The other parameters are the bond wire inductance and resistance, the package capacitances, and the diode grounding inductance,  $L_{paddle}$ . Package reactance have little effect on the diode's performance for frequencies below 1 GHz [7, 55].

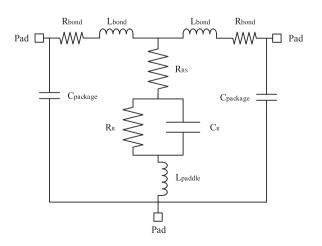

#### 2.3 | Reverse-biased equivalent circuit

The equivalent circuit of a reversed-biased diode in shunt configuration is shown in Figure 4, and consists of the shunt combination of diode capacitance,  $C_R$ , and diode resistance,  $R_R$ , in series with the parasitic inductance,  $L_{paddle}$ , which can also be neglected for frequencies below 1 GHz [7, 55].

$C_R$  and  $R_R$  represent the reactance and net dissipative resistance of the depleted I-layer in the reverse-biased diode, respectively.  $C_R$  includes the junction capacitance,  $C_j$ . Similarly,

FIGURE 3 Forward-biased, shunt-grounded, PIN diode equivalent circuit. Adapted from [56].

**FIGURE 4** Reverse-biased PIN diode equivalent circuit. Adapted from [56].

the parallel resistance, R<sub>R</sub>, is also affected by any series resistance in the semiconductor or diode contacts or package.

### 2.4 | Known thermal effects

Two main parameters of a PIN diode are strongly influenced by temperature, namely the I-layer ambipolar mobility,  $\mu_a(T)$ , and carrier lifetime,  $\tau(T)$  [8, 14, 15]. Ambipolar mobility and carrier lifetime as a function of temperature are given as the following equations:

$$\mu_{\rm a}(T) = \mu_{\rm a}(T_{\rm nom}) \left(\frac{T}{273 + T_{\rm nom}}\right)^{-2.3} (^{\circ}{\rm C}), \qquad (1)$$

and

$$\tau(T) = \tau(T_{\text{nom}}) \left(\frac{T}{273 + T_{\text{nom}}}\right)^{\tau_{\text{coefficient}}} (^{\circ}\text{C}), \qquad (2)$$

where  $\mu a(T)$  is the ambipolar mobility as a function of temperature,  $\tau(T)$  is the carrier lifetime as a function of temperature, T is the temperature in °C,  $T_{nom}$  is the ambient temperature in °C, T is the temperature in °C, and  $\tau_{coefficient}$  is the carrier lifetime temperature coefficient.

Equation (2) shows that the carrier lifetime increases with increasing temperature, as confirmed in refs. [15] and [22], while  $\tau_{\text{coefficient}}$  depends on the diode's surface passivation and I-layer capacitance [16], [19]. Ambipolar mobility in (1) decreases with increasing temperature [15].

Thermal capacitance is defined as the amount of energy required to raise the temperature of the I-layer of the diode by 1°C, in the absence of heat flow from the diode [1, 57]. Thermal capacitance is given by the following equation:

$$C_{\text{Thermal}} = \frac{\rho c_{\theta}}{V} (J/^{\circ}\text{C}), \qquad (3)$$

where  $C_{\text{Thermal}}$  is the thermal capacitance in Joule per Celsius (J/°C),  $c_{\theta}$  is the specific heat property of the diode material in cal/(g °C),  $\rho$  is the density of the diode material in g/cm<sup>3</sup>, and V is the volume of the I and N-layer.

Equation (3) suggests that a diode with a thick I-layer has greater heat capacitance and requires more energy to increase the temperature through self-heating.

Ambient temperature variations are expected to have less of an impact on diodes with thick I-layers, and more of an impact on diodes with a thin I-layer.

### 3 | SMALL-SIGNAL MODELLING AND MODEL VARIATION

To establish the effect of temperature change on device smallsignal capacitance, it must first be extracted from temperaturevaried small-signal S-parameter measurements of the PIN diode. The purpose of this test was to characterise each of the PIN diodes in Table 1 individually by measuring the Sparameter data for each diode at different temperatures and bias voltages over a range of frequencies. Using the Sparameter data and through a parameter extraction process, the equivalent circuit models were determined.

### 3.1 | Measurement approach

The PIN diodes that were used for this study is given in Table 1. Four silicon PIN diodes from Skyworks Inc. were chosen to represent a selection of diodes with small, medium, and large I-layers, in terms of thickness. The PCB was manufactured on 0.5 mm thick Rogers RO4003C and devices fed by a grounded coplanar waveguide. A 30 mm launch distance was added to all the calibration standards and the DUT characterisation circuit to allow any higher-order modes from the connector to microstrip transition to attenuate.

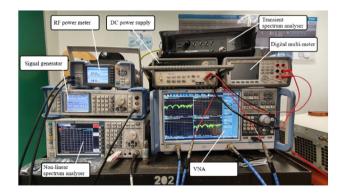

The PIN diodes were soldered to the test fixture as shown in Figure 5. A Rohde & Schwarz ZNB20 vector network analyser was used, with the addition of a bench power supply and a digital multi-metre (Figure 6).

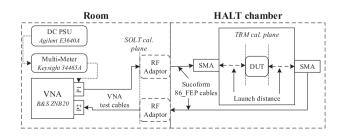

The small-signal measurement used a 5-point measurement average. An Agilent E3640A 20 V/1.5 A DC power supply and Keysight 34,465A digital multi-metre (Figure 6) were used to bias and measure the current through the DUT, respectively. The temperature range of interest (-25 °C to 100 °C) was divided into 25 °C intervals. A highly accelerated life test (HALT) chamber was used to control and vary the temperature

TABLE 1 PIN diode selection.

| Diode<br>name | I-layer<br>thickness<br>(µm) | <b>C</b> <sub>j</sub> (pF) | Max<br>CW (W) | Carrier<br>lifetime,<br>τ, (ns) |

|---------------|------------------------------|----------------------------|---------------|---------------------------------|

| CLA4610       | 4.5                          | 0.32 @<br>-6 V             | 8             | 20                              |

| CLA4608       | 7                            | 0.6 @<br>-38 V             | 5             | 100                             |

| CLA4611       | 12                           | 0.25 @<br>-38 V            | 10            | 300                             |

| CLA4609       | 20                           | 0.6 @<br>-30 V             | 16            | 1100                            |

$FIGURE\ 5 \quad {\rm Test\ fixture\ with\ DUT}.$

to which the test jig was subjected. The measurement setup shown in Figure 7.

The test cables that were connected between the DUT inside the HALT chamber and the VNA on the outside would be subjected to changing temperature and were, therefore, selected for temperature stability. Multiple units of a specific PIN diode were available and were installed into the characterisation (Figure 5) and limiter circuits beforehand, therefore eliminating the need to move a single PIN diode between circuits.

The DC bias voltages were in 5 V steps from -20 V to -10 V, 1 V steps from -10 V to -1 V, and 0.1 V increments from -1 V to +3 V. This was done to achieve greater resolution in bias regions of fast model parameter variation. +3 V was selected as the maximum voltage because of the allowable current draw by the PIN diode through the VNA in the absence of a current-limiting resistor.

A two-tier calibration procedure was used. For the VNA cable calibration, the SOLT calibration standard was chosen, whereas TRM calibration standard was used to de-embed the test fixture. The SOLT calibration establishes a calibration plane at the outside of the HALT chamber where the temperature is constant, and the TRM calibration shifts the calibration plane to the inside of the HALT chamber and handles temperature variations (Figure 7). A two-tier approach was also done to allow large volumes of data to be captured in a reasonable amount of time.

### 3.2 | Circuit model parameter extraction

To investigate the effect of temperature variation on smallsignal junction capacitance, the circuit model in Figure 4 can be fitted to measured reverse-biased small-signal parameters,

FIGURE 6 Measurement equipment.

FIGURE 7 Small-signal measurement setup.

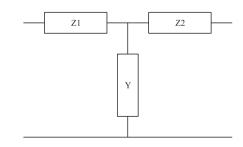

with some package parameters extracted using forward-biased measurements and the model in Figure 3. The equivalent T-circuit for both models can be presented as is shown in Figure 8.

The equivalent circuit neglects the effect of  $C_{package}$ . Parameters  $Z_1$  and  $Z_2$  represent the combined impedance of  $R_{bond}$  and  $L_{bond}$  in the series branch, whereas Y represents the admittance of the shunt branch.  $C_{package}$  is neglected in the frequency range of interest.

The branch impedance and shunt admittance can be calculated from the ABCD parameters of the circuit using (4).

$$\begin{bmatrix} A & B \\ C & D \end{bmatrix} = \begin{bmatrix} (1+YZ_1) & (Z_1+Z_2+YZ_1Z_2) \\ Y & (1+YZ_2) \end{bmatrix}, \quad (4)$$

where the two-port ABCD parameters are calculated from the measured S-parameters.

Both direct-extraction and optimization-based algorithms for parameter extraction [58] must deal with the ill-conditioned nature of the extraction problem, which makes determining a unique equivalent model for a device challenging. This illconditioned behaviour of extraction is prevalent in parasitic elements such as lead or bond inductances, or package capacitances, due to the small effect they have on the measured data. Using a multi-bias approach that combines S-parameter data from multiple bias points into an integrated parameter extraction algorithm has demonstrated to be effective in extracting a distinctive set of model parameters [59]. In this study, the following heuristics are applied in extraction:

- 1. L<sub>padde</sub>, R<sub>bond</sub>, and L<sub>bond</sub> are bias independent.

- 2. At low frequencies, C<sub>R</sub> dominates the imaginary part of the shunt impedance.

- 3. When the PIN diode is forward biased, the junction capacitance in the shunt branch is negligible.

- 1. At high frequencies, the shunt admittance is dominated by the reactance of L<sub>padde</sub>.

- 2. At low frequencies, the shunt impedance is dominated by R<sub>F</sub>.

On the basis of these assumptions, the parameter extraction process started with the forward-biased model. Using the de-embedded S-parameter data, the forward-biased series and shunt branch impedances were calculated according to (4).

FIGURE 8 T-branch equivalent circuit.

The total shunt impedance for a forward-biased PIN diode at 3 V is given by (5), with the best-fit value of  $L_{paddle}$  extracted at the highest bias voltages using (6). The inductance was calculated at frequencies between 4000 and 6000 MHz where the inductive reactance is dominant.

$$Z_{3V} = R_{\rm F} + j\omega L_{\rm paddle} \tag{5}$$

$$L_{\text{paddle}} = \Im m(Z_{3V})/\omega \tag{6}$$

where  $Z_{3V}$  is the complex shunt impedance at 3V ( $\Omega$ ), and  $\omega$  is the angular frequency.

The value of  $L_{paddle}$  was averaged across the three highest bias voltages to obtain a consistent value which was used as a constant to extract the value of reverse-biased parameters.

The total shunt impedance for a reverse-biased PIN diode is given by the following equation:

$$Z_{\rm R} = R_{\rm RS} + R_{\rm R} \left\| \left( \frac{1}{j\omega C_{\rm R}} \right) + j\omega L_{\rm paddle}, \right\|$$

(7)

where  $Z_R$  is the shunt impedance at a given reverse voltage  $(\Omega)$ ,  $R_{RS}$  is the reverse-biased series resistance  $(\Omega)$ ,  $R_R$  is the reverse-biased parallel resistance  $(\Omega)$ ,  $C_R$  is the junction capacitance (pF),  $L_{paddle}$  is the previously calculated paddle inductance, and  $\omega$  is the angular frequency.

Using the branch impedances,  $Z_1$  and  $Z_2$ , the series resistance and inductance were calculated using the following equations:

$$Z_{\rm x} = R_{\rm bond} + j\omega L_{\rm bond},\tag{8}$$

$$R_{\text{bond}} = real(Z_{\text{x}}), \tag{9}$$

$$L_{\text{bond}} = \Im m(Z_{\text{x}})/\omega, \qquad (10)$$

where  $Z_x$  is the complex series branch impedance ( $\Omega$ ), and  $\omega$  is the angular frequency.

### 3.3 | Reverse-biased capacitance versus temperature results

This section presents the capacitance versus temperature results for each diode and provides a comparison amongst the diodes and PIN diode models.

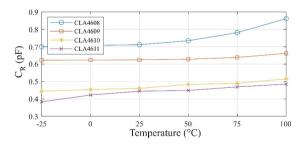

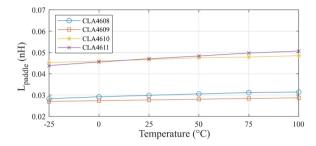

The variation of the capacitance,  $C_R$ , with temperature is shown in Figure 9, and would indicate a gradual increase with temperature. Table 2 summarises the results of Figure 9.

The nominal values of  $C_R$  correspond well with published datasheet values, featuring an irregular relationship between Ilayer thickness and junction capacitance. The data would indicate that the diode with the thickest I-layer, CLA4609, exhibits less capacitance change over temperature than the diodes with a thinner I-layer thickness, as is suggested by (3), except for the CLA4610 diode. It is also interesting to note that, for this device, most of the capacitance increase occurs between 75 °C and 100 °C.

## 3.4 | Reverse-biased resistance versus temperature results

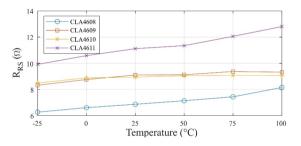

The best-fit series resistance,  $R_{RS}$ , that was extracted at 0 V for various PIN diodes, is shown in Figure 10 and demonstrates a gradual increase in series resistance over increasing temperature.

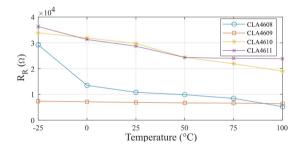

The best-fit parallel resistance,  $R_R$ , extracted at 0 V versus temperature is shown in Figure 11. All the diodes show a sharp decrease in resistance from -25 °C to 100 °C, except for the CLA4609 diode which has a more gradual decline.

### 3.5 | Forward-biased resistance versus temperature results

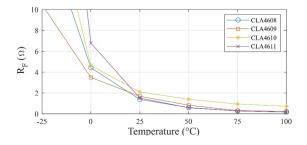

The PIN diodes' forward resistance,  $R_F$ , at around 10 mA versus temperature is given in Figure 12 and would indicate that the diodes studied here have a carrier lifetime coefficient of greater than 2.3. The large variation in forward resistance below 0 °C could be due to inaccurate parameter extraction in a range where  $R_F$  is no longer expected to be a small value.

The change in resistance with temperature was discussed in a study by Caverly [15, 19], where it was shown that the forward-biased resistance of the PIN diode may increase ( $\tau_{\text{coefficient}} < 2.3$ ), decrease ( $\tau_{\text{coefficient}} > 2.3$ ), or remain constant ( $\tau_{\text{coefficient}} = 2.3$ ) over temperature. While the manufacturer of the DUTs included in this study does not provide the required information to calculate the carrier lifetime

FIGURE 9 Capacitance versus temperature comparison at 0 V.

TABLE 2 Summarised change in capacitance per diode at 0 V.

| PIN<br>diode | I-layer<br>thickness<br>(μm) | <i>C</i> <sub><i>R</i></sub> at<br>−25 °C (pF) | <b>C</b> <sub><b>R</b></sub> at 100 °C (pF) | $\frac{\Delta C_R}{125 \ ^{o}C}$ (pF) |

|--------------|------------------------------|------------------------------------------------|---------------------------------------------|---------------------------------------|

| CLA4610      | 4.5                          | 0.4448                                         | 0.5152                                      | 0.0704                                |

| CLA4608      | 7                            | 0.6995                                         | 0.8615                                      | 0.162                                 |

| CLA4611      | 12                           | 0.3834                                         | 0.4856                                      | 0.1022                                |

| CLA4609      | 20                           | 0.6229                                         | 0.662                                       | 0.0391                                |

temperature coefficient, the results shown in Figure 12 would indicate that the diodes studied here have a carrier lifetime temperature coefficient of greater than 2.3. This can further and readily be explained by decreased scattering due to an increase in lattice phonons, increased carrier mobility and decreased bandgap [51].

### 3.6 | Package parasitics versus temperature results

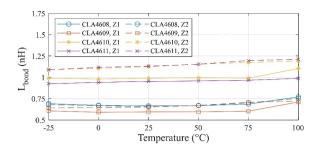

The branch inductance,  $Z_1$  and  $Z_2$  shown in Figure 8, versus temperature for each diode is shown in Figure 13. The results show a slight increase in bond-wire inductance, likely due to minor temperature elongation of the bond wire length.

The diodes' best-fit paddle inductance,  $L_{paddle}$ , extracted at the highest bias voltages using (6) is shown in Figure 14. The results show a negligible increase in inductance with increasing temperature. Differences in inductance between diodes, which were also observed in Figure 13, are likely due to small variations in the amount of solder used during installation.

FIGURE 10 Series resistance versus temperature at 0 V.

FIGURE 11 Parallel resistance versus temperature at 0 V.

FIGURE 12 Forward resistance versus temperature at around 10 mA.

FIGURE 13 Branch inductance versus temperature at 3 V.

FIGURE 14 Paddle inductance versus temperature at 3 V.

### 4 | PIN DIODE LIMITER TRANSIENT CHARACTERISATION

This section presents the measurement setup and transient responses of each limiter topology at different frequencies and temperatures. The small-signal model discussed in Section 3 provides, conceptually, a good baseline for how a diode's capacitance will change with increasing temperature. Although the specific capacitance values may differ between the smallsignal and large signal models, the trends over temperature can reasonably be expected to correspond and are used here to compare transient measurements.

From the discussion in Section 3, it is expected that the change in capacitance,  $C_R$ , and forward resistance,  $R_F$ , due to temperature will affect the transient response of a limiter in terms of the limiter's spike and flat leakage, since the flat leakage is dependent on how small the forward resistance of the diode becomes during its on state, whereas the spike leakage is dependent on the carrier lifetime, which is in turn influenced by temperature and the capacitance of the I-layer [8, 14, 22].

### 4.1 | Circuits under test

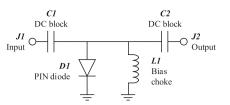

Two PIN diode limiter topologies were chosen to evaluate the effect of temperature variation on PIN-diode limiter response, namely the traditional PIN diode limiter, and the anti-parallel limiter. The traditional PIN diode limiter (Figure 15) is the simplest type of PIN diode-based limiter and is frequently featured in component datasheets.

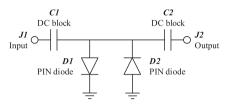

The anti-parallel limiter circuit (Figure 16) does not require a DC bias choke and has been shown to have improved performance compared to the traditional limiter topology [60].

FIGURE 15 Traditional limiter circuit topology.

FIGURE 16 Anti-parallel limiter circuit topology.

The results for the CLA4608 and CLA4609 diodes are presented, as they provide variety in intrinsic layer width (7 vs.  $20 \mu$ m) and carrier lifetime (100 vs. 1100 ns).

### 4.2 | Measurement setup

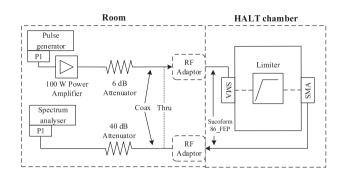

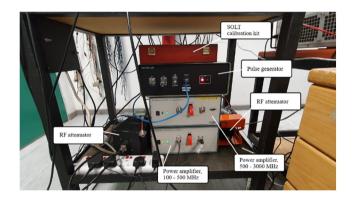

The purpose of this measurement was to measure the spike and flat leakage of the PIN diode limiter through transient analysis at different temperatures. The measurement setup is shown in Figure 17.

A pulse generator (Figure 18) was used to produce pulsed RF signals at 100 and 300 MHz, amplified to 100 W peak signal using a power amplifier. The results at 100 and 300 MHz are presented in Tables 3 and 4 in the following section. The limiter's response was measured using an Anritsu MS2090 A handheld spectrum analyser (Figure 6) configured in the zerospan (time domain) mode.

### 4.3 | Traditional limiter measurement results

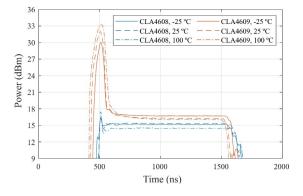

Figure 19 shows the transient response for the traditional limiter using the CLA4608 and CLA4609 PIN diodes at 100 MHz at different temperatures.

For the CLA4608 diode, the results show a 0.7 dB decrease in the flat leakage from -25 °C to 100 °C. For the CLA4609 PIN diode, the limiter's flat leakage decreases with increasing temperature due to a decrease in the series resistance at higher temperatures shown in Figure 12. The results show a decrease in the flat leakage of around 0.6 dB from-25°C to 100°C.

The limiter's change in spike leakage with temperature shows that, at 100 MHz, the magnitude of the spike increases by approximately 1.2 dB from -25 °C to 100 °C for the CLA4608 diode, which, in combination with the decreasing flat leakage, increases the spike leakage. For the CLA4609 diode, the results show a significantly more pronounced (3.1 dB) increase in the spike magnitude, as well as a longer spike

duration, over increasing temperature. These increases can be attributed to the increase in the diode's carrier lifetime, which is influenced by temperature and the increase in capacitance of the I-layer, as was shown in Figure 9.

FIGURE 17 Limiter transient measurement setup.

FIGURE 18 Transient measurement equipment.

# 4.4 | Anti-parallel limiter measurement results

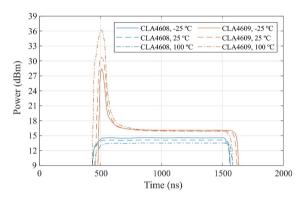

Figure 20 show the transient response of the anti-parallel limiter with the CLA4608 and CLA4609 PIN diodes at 100 MHz for different temperatures.

Like the results in Figure 19, the anti-parallel limiter with the CLA4608 diode also exhibits a decrease in the flat leakage of about 0.6 dB from - 25°C to 100°C, whereas the response for the CLA4609 diode shows that the limiter's flat leakage decreases marginally with increasing temperature, with the results showing a decrease in the flat leakage of around 0.14 dB from -25 °C to 100 °C. An increase in both the magnitude and duration of the spike in the case of the CLA4609 diode is also observed, with the spike magnitude increasing by 6.8 dB from -25 °C to 100 °C.

The CLA4608 diode, with its thinner I-layer, was fast enough to respond to the incident RF pulse and did not present any significant spike leakage.

### 4.5 | Results summary

Table 3 shows a summary of the traditional limiter's performance at 100 and 300 MHz using the two different PIN diodes. The table shows a clear trend of increasing spike leakage and near-constant flat leakage with increasing temperature. The increase in spike leakage is more severe with the larger, CLA4609 PIN diode, at 100 MHz.

A summary of the anti-parallel limiter's performance at 100 and 300 MHz is given in Table 4. As was the case with the CLA4609 diode in the traditional limiter topology, the table

|             | Spike leakage (nJ) |                                                                   | Flat leakage (dBm)                                                                            |                                                                                                                                      |

|-------------|--------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Freq. (MHz) | CLA 4608           | CLA 4609                                                          | CLA 4608                                                                                      | CLA 4609                                                                                                                             |

| 100         | 0.1                | 24.33                                                             | 15.17                                                                                         | 16.7                                                                                                                                 |

|             | 0.12               | 48.24                                                             | 15.33                                                                                         | 16.28                                                                                                                                |

|             | 0.17               | 83.75                                                             | 14.46                                                                                         | 16.1                                                                                                                                 |

| 300         | 0.54               | 0                                                                 | 15.33                                                                                         | 17.96                                                                                                                                |

|             | 0.59               | 0                                                                 | 15.35                                                                                         | 18.07                                                                                                                                |

|             | 0.66               | 0                                                                 | 14.73                                                                                         | 18.36                                                                                                                                |

|             | 100                | Freq. (MHz) CLA 4608   100 0.1   0.12 0.17   300 0.54   0.59 0.59 | Freq. (MHz) CLA 4608 CLA 4609   100 0.1 24.33   0.12 48.24   0.17 83.75   300 0.54 0   0.59 0 | Freq. (MHz) CLA 4608 CLA 4609 CLA 4608   100 0.1 24.33 15.17   0.12 48.24 15.33   0.17 83.75 14.46   300 0.54 0 15.33   0.59 0 15.35 |

**TABLE 3** Traditional limiter PIN diode comparison at 100 and 300 MHz.

|            |             | Spike leakage (nJ) |         | Flat leakage (dBm) |          |

|------------|-------------|--------------------|---------|--------------------|----------|

| Temp. (°C) | Freq. (MHz) | CLA 4608           | CLA4609 | CLA 4608           | CLA 4609 |

| -25        | 100         | 0.01               | 12.93   | 14.55              | 16.1     |

| 25         |             | 0                  | 30.27   | 14.1               | 15.94    |

| 100        |             | 0                  | 97.9    | 13.49              | 15.96    |

| -25        | 300         | 0.18               | 0.76    | 13.98              | 19.04    |

| 25         |             | 0.25               | 0.24    | 13.57              | 18.31    |

| 100        |             | 0.49               | 0.19    | 12.28              | 18.1     |

**TABLE 4** Anti-parallel limiter PIN diode comparison at 100 and 300 MHz.

**FIGURE 19** Traditional limiter's transient response versus temperature with CLA4608 and CLA4609 PIN diodes at 100 MHz.

**FIGURE 20** Anti-parallel limiter's transient response versus temperature with CLA4608 and CLA4609 PIN diodes at 100 MHz.

shows a clear trend of increasing spike leakage with increasing temperature at 100 MHz. This can be attributed to the increase in the diode's carrier lifetime which is influenced by temperature and the increase in capacitance of the I-layer, as was shown in Figure 9. The results further show a small decrease in the flat leakage at both frequencies for both diodes.

### 5 | CONCLUSION

This work presented, for the first time, explicit data on capacitance variation over temperature for silicon PIN diodes and studied the effect of temperature variation on the transient response of PIN diode-based limiters.

It is evident from Figure 9 that a PIN diode's capacitance,  $C_R$ , increases with temperature between -25 °C and 100 °C, mirroring the effect of temperature on capacitance in Schottky photodiodes [61]. The measured data also supports (3), which suggests that temperature variations will have less of an impact on diodes with thick I-layers, and more of an impact on diodes with a thin I-layer. The reverse-biased resistance results showed a gradual increase in series resistance series,  $R_{RS}$ , with temperature, where the parallel resistance,  $R_R$ , showed a sharp decrease in resistance with increasing temperature. It was also found that the forward-bias series resistance,  $R_F$ , decreases

with temperature. It is concluded that the measured diodes have a carrier lifetime temperature coefficient,  $\tau_{coefficient}$ , of greater than 2.3, which is indicative of a negative resistance coefficient.

The transient results showed that the flat leakage decreases with increasing temperature for both the traditional and antiparallel limiter topologies operating at VHF, while the spike leakage increases. The decrease in flat leakage with increasing temperature is due to the decrease in the forward-biased resistance that was shown in Figure 12. The increase in spike leakage with increasing temperature, a novel experimental observation of this work, can be attributed to the increase in the diode's carrier lifetime, which is influenced by temperature and the increase in capacitance of the I-layer. This observation is supported by the small-signal characteristics in Figures 9 and 12, where it is shown that C<sub>R</sub> increases with increasing temperature, while R<sub>F</sub> decreases. It can further be concluded that the increase in spike leakage at higher temperatures correlates with increasing device capacitance as influenced by carrier lifetime.

The increase in spike leakage was found to be more severe with the thicker CLA4609 PIN diode, which showed far greater spike leakage compared to the other diodes at 100 MHz. This can be attributed to the CLA4609 diode's increased carrier lifetime compared to the smaller CLA4608 diode, which is due to its thickness (20  $\mu$ m compared to 7  $\mu$ m). The result agrees with prior studies that found that diodes with a thin I-layer (less junction capacitance) have little spike leakage and that thick I-layer diodes (more junction capacitance) have much more spike leakage [13]. As discussed in Section II, the response time of the PIN diode is directly related to the diode's carrier lifetime, and the carrier lifetime is in turn influenced by temperature and the capacitance of the I-layer [11, 23].

Future work will extend the frequency range of the study to include X-band frequencies (8–12 GHz) or even 2–18 GHz for EW applications, building on a distributed multi-stage topology as shown in refs. [26] or [62]. This study will also be replicated for microelectronic integrated limiters, incorporating a wider variety of limiter topologies.

We further propose to extend the comparison of the single and anti-parallel diode topologies to other performance parameters, such as operating bandwidth, building on the prior work in ref. [63].

#### AUTHOR CONTRIBUTION

Cornelius Johannes Botha: Detail design, software development, experimentation, data curation, writing–original draft & editing. Prof. Tinus Stander: Conceptualisation, funding acquisition, supervision, writing–review & editing.

### ACKNOWLEDGEMENTS

The authors wish to thank Hensoldt SA for the PCB, facilities, and equipment, and RFDesign (Pty) Ltd for sampling the PIN diodes. This work was further supported by the National Research Foundation of South Africa (NRF) under grant UID137950.

### CONFLICT OF INTEREST STATEMENT

The authors declare no conflicts of interest.

#### DATA AVAILABILITY STATEMENT

Data available on request from the authors.

#### ORCID

Cornelius Johannes Botha D https://orcid.org/0009-0004-6089-9852

#### REFERENCES

- Skyworks Solutions, Inc.: PIN Limiter Diodes in Receiver Protectors. Skyworks Solutions, Inc. (2008)

- CPI Wireless Solutions: Beverly Microwave Division. Beverly, Massachusetts.Receiver Protector Technology

- Chaturvedi, S., Badnikar, S., Naik, A.A.: Ultra wideband receiver protection limiter using 0.13m pHEMT technology. 2017 IEEE MTT-S Int. Microw. RF Conf. (IMaRC) 5, 1–5 (2017)

- Seng, H.W., Sloan, R., Williams, K.: Implementing RF signal limiter with heterojunction devices. In: High Frequency Postgraduate Student Colloquium, pp. 195–198 (2004)

- Agilent Technologies: Low cost surface mount power limiters, application note 1050, (1999)

- Jag, B.-J., Yom, I.-B., Lee, S.-P.: An enhanced PIN diode model for voltage-controlled PIN diode attenuator. In: 33rd European Microwave Conference Proceedings, pp. 231–234. Munich (2003)

- Brown, N.J.: Design concepts for high-power PIN diode limiting. IEEE Trans. Microw. Theor. Tech. 15(12), 732–742 (1967). https://doi.org/10. 1109/tmtt.1967.1126573

- Caverly, R.H., Khan, S.: Electrothermal modeling of microwave and RF PIN Diode switch and attenuator circuits. In: 2013 IEEE MTT-S International Microwave Symposium Digest (MTT), pp. 1–4. Seattle (2017)

- Boles, T., Bukowski, J., Brogle, J.: Monolithic high power 300 watt, Sband, HMIC PIN diode limiter. In: 2019 IEEE International Conference on Microwaves, Antennas, Communications and Electronic Systems (COMCAS), pp. 1–5. Tel-Aviv, Israel (2019)

- Khalifa, E., Elhassane, A., Hamid, B.: Microwave power protectors: attenuators and limiters. In: Handbook of Research on Advanced Trends in Microwave and Communication Engineering, pp. 244–282. IGI Global, Hershey, PA (2016)

- Wang, Z., Cao, H., Zhang, C.: Research on the influence of PIN diode on limiter performance in power limiter. In: 2017 7th IEEE International Symposium on Microwave, Antenna, Propagation, and EMC Technologies (MAPE), pp. 220–223. Xi'an, China (2017)

- Wang, D., et al.: Investigation on the pulse characteristics of RF/microwave limiter based on multistage PIN diodes and Schottky diodes. In: Proceedings of 2014 3rd Asia-Pacific Conference on Antennas and Propagation, pp. 1366–1369. Harbin, China (2014)

- 13. Ward, A.L, Tan, R.J. and Kaul, R.: Spike leakage and burnout of silicon PIN diode microwave limiters, (1991)

- Caverly, R.H.: Time-domain electrothermal circuit-level modeling of microwave and RF PIN diodes. In: IEEE/MTT-S International Microwave Symposium Digest, pp. 1–3. Montreal (2012)

- Caverly, R.H., Hiller, G.: The temperature dependence of PIN diode attenuators. In: IEEE MTT-S International Microwave Symposium Digest, pp. 553–556. Atlanta (1993)

- Caverly, R.H.: Numerical modeling of surface effects in RF switching PIN diodes. In: 2018 IEEE MTT-S International Conference on Numerical Electromagnetic and Multiphysics Modeling and Optimization (NEMO), pp. 1–4. Reykjavik, Iceland (2018)

- Caverly, R.H.: Dual thermal time constant electrothermal modeling of PIN diode protection circuits. In: IEEE Topical Conference on Biomedical Wireless Technologies, Networks, and Sensing Systems (BioWireleSS), pp. 1–3. San Diego (2015)

- Caverly, R.H., et al.: Temperature effects on PIN diode forward bias resistance. Solid State Electron. 38(11), 1879–1885 (1995). https://doi. org/10.1016/0038-1101(95)00016-m

- Caverly, R.H.: Impact of temperature on the impedance of microwave and RF PIN diodes. In: *IEEE International Wireless Symposium*, X'ian, China, pp. 1–4 (2014)

- Hill, J., Maddix, H.: Thermal considerations in high average power microwave pin diode switches. IEEE Int. Dig. Microwave Symp. 11, 1325– 1328 (1990)

- Caverly, R.H.: RF technique for determining ambipolar carrier lifetime in pin RF switching diodes. Electron. Lett. 34(23), 2277–2278 (1998). https://doi.org/10.1049/el:19981568

- Gamal, S.H., Morel, H., Chante, J.: Carrier lifetime measurement by ramp recovery of PIN diodes. IEEE Trans. Electron. Dev. 37(8), 1921–1924 (1990). https://doi.org/10.1109/16.57146

- Li, Y.-N., Tan, Z.-L.: Simulation and design of RF front-end electromagnetic protection module based on VHF communication. In: 2018 International Conference on Electronics Technology (ICET), pp. 142– 146. Chengdu, China (2018)

- Li, S., et al.: High power X-band monolithic GaAs p-i-n balanced limiter. IEEE Trans. Power Electron. 38(4), 4623–4631 (2023). https://doi.org/ 10.1109/tpel.2022.3232612

- Zhu, H.-R., Wang, J.: Miniaturized, ultrawideband and low insertion loss ku -band GaAs on-chip limiter by improved π-type topology with capacitive loading. IEEE Trans. Electron. Dev. 70(3), 971–978 (2023). https://doi.org/10.1109/ted.2023.3239056

- Li, S., et al.: High power 10–18 GHz monolithic limiter based on GaAs p-i-n technology. IEEE Microw. Wireless Compon. Lett. 32(9), 1107– 1110 (2022). https://doi.org/10.1109/lmwc.2022.3161152

- Yang, L., et al.: A 27–35 GHz wideband PIN-diode limiter low noise amplifier MMIC with sub-2.4 dB noise figure. Microelectron. J. 126(C), 105507 (2022). https://doi.org/10.1016/j.mejo.2022.105507

- Yang, L., et al.: A compact Ka-band limiter-low noise amplifier MMIC with high power capability. Microw. Opt. Technol. Lett. 64(6), 1006–1011 (2022). https://doi.org/10.1002/mop.33222

- Zhu, H.-R., Wang, J., Tang, M.: Compact, high power capacity, and low insertion loss millimeter-wave on-chip limiting filter with GaAs PIN technology. IEEE Trans. Circuits Syst. Regular Pap. 70(3), 1175–1188 (2023). https://doi.org/10.1109/tcsi.2022.3228125

- Huang, Y., al, e.: A miniaturized ultra-broadband filtered electromagnetic protection component. In: International Conference on Microwave and Millimeter Wave Technology (ICMMT), 2022–2024. Harbin, China (2022)

- Li, S., et al.: High power X-band monolithic GaAs p-i-n balanced limiter. IEEE Trans. Power Electron. 38(4), 4623–4631 (2023). https://doi.org/ 10.1109/tpel.2022.3232612

- Liu, T., et al.: Joint analysis of front-door and back-door couplings of PIN limiter based on improved equivalent circuit model. Electronics 11(23), 3921 (2022). https://doi.org/10.3390/electronics11233921

- Chen, H., al, e.: A study on the high power microwave effects of PIN diode limiter based on deep learning algorithm. Nanotechnology 35(26), 1–12 (2024)

- Surdi, H., et al.: P-i-N and Schottky P-i-N diamond diodes for high power limiters. Appl. Phys. Lett. 124(6) (2024). https://doi.org/10.1063/ 5.0176966

- Jung, D.Y., et al.: Power limiter with PIN diode embedded in cavity to minimize parasitic inductance. J. Electromagn. Eng. Sci. 22(6), 686–688 (2022). https://doi.org/10.26866/jees.2022.6.1.10

- Woo, J.-M., et al.: Design and analysis of an adjustable diode-integrated waveguide-based electromagnetic pulse limiter for microwave receiver. IEEE Access 12(3), 41066–41073 (2024). https://doi.org/10.1109/ access.2024.3376743

- Gonya, S., et al.: Embedded PIN-diode die interconnections with aerosol-jet printing. IEEE Trans. Compon. Packag. Manuf. Technol. 14(4), 714–722 (2024). https://doi.org/10.1109/tcpmt.2024.3380468

- Xue, M., et al.: Design of L band leadless package limiter. In: International Conference on Microwave and Millimeter Wave Technology (ICMMT), pp. 1–3. Harbin, China (2022)

- Dai, Z., et al.: A C-band 370 W MMIC high-power PIN limiter with heterogeneous integration. Microw. Opt. Technol. Lett. 65(3), 798–803 (2023). https://doi.org/10.1002/mop.33576

- Li, S., et al.: High power 10-18 GHz monolithic limiter based on GaAs pi-n technology. IEEE Microw. Wireless Compon. Lett. 32(9), 1107–1110 (2022). https://doi.org/10.1109/lmwc.2022.3161152

- Zhao, J., et al.: Damage accumulation mechanism in PIN diode limiters induced via multiple microwave pulses. Sci. Rep. 10(1), 1709–2020 (2020). https://doi.org/10.1038/s41598-020-58710-3

- Yang, S.-S., et al.: A novel analysis of a ku-band planar p-i-n diode limiter. IEEE Trans. Microw. Theor. Tech. 57(6), 1447–1460 (2009). https://doi. org/10.1109/tmtt.2009.2019993

- Xu, K., et al.: A parameter extraction method of the PIN diode for physics-based circuit simulation over a wide frequency range. Int. J. RF Microw. Computer-Aided Eng. 30(11) (2020). https://doi.org/10.1002/ mmce.22385

- Mingxuan, G., Yang, Z., Jun, Z.: Influence of high-power microwave signal on temperature distribution of PIN limiter. High Power Laser Part Beams 36(4), 1–7 (2024)

- Chen, S., et al.: Electro-thermal analysis of microwave limiter based on the time-domain impulse response method combined with physicalmodel-based semiconductor solver. IEEE Trans. Microw. Theor. Tech. 68(7), 2579–2589 (2020). https://doi.org/10.1109/tmtt.2020.2987557

- Yi, S., Du, Z.: The influence of microwave pulse width on the thermal burnout effect of a PIN diode limiting-amplifying system. Microelectron. Reliab. 75, 102–109 (2017). https://doi.org/10.1016/j.microrel.2017. 06.025

- Gao, M., et al.: Simulation study on thermal effect of multistage PIN limiter. In: The Proceedings of the 10th Frontier Academic Forum of Electrical Engineering, pp. 899–910 (2023)

- Paek, M.-C., et al.: Characterization of thermal behavior of a silicon PIN diode package in a RF power limiter. New Phys. Sae Mulli 73(6), 563–570 (2023). https://doi.org/10.3938/npsm.73.563

- Zhao, J.C.Q.C.Z.e.a., et al.: Impact of the structure on the thermal burnout effect induced by microwave pulses of PIN limiter diodes. Sci. Rep. 12(1), 3230 (2022). https://doi.org/10.1038/s41598-022-07326-w

- Gao, M., Zhang, Y., Zhang, J.: Mechanism and rule of microwave pulse response of two-stage PIN limiter. Acta Phys. Sin. 73(6), 1–12 (2024). https://doi.org/10.7498/aps.73.20231495

- Ruan, B., et al.: Simulated analysis of PIN diode electro-thermal characteristics under electromagnetic pulse signal. In: International Applied Computational Electromagnetics Society Symposium (ACES-China), Xuzhou, China, pp. 1–4 (2022)

- 52. Wang, B., Huang, K.-m.: Effect of temperature on power response of PIN diode limiter. High Power Laser Part Beams 20(4), 645–648 (2008)

- Dai, Z., et al.: A C-band 370 W MMIC high-power PIN limiter with heterogeneous integration. Microw. Opt. Technol. Lett. 65(3), 798–803 (2023). https://doi.org/10.1002/mop.33576

- Zeng, H., Chen, X.: Nonlinear analysis for microwave limiter using a field-circuit simulator based on physical models. IEEE Microw. Wireless Compon. Lett. 30(2), 129–132 (2020). https://doi.org/10.1109/lmwc. 2019.2961840

- Microsemi: The PIN Diode Circuit Designers' Handbook. Microsemi Corporation, Watertown (1998)

- Skyworks Solutions, Inc.: CLA4608-085LF: Surface-Mount Limiter Diode. Data sheet. [Online]. https://www.skyworksinc.com/-/media/ SkyWorks/Documents/Products/1701-1800/CLA4608\_085LF\_ 202537E.pdf. Accessed Nov 2022

- 57. White, J.F.: Microwave Semiconductor Engineering, pp. 106. Van Nostrand Reinhold Company, New York (1982)

- Niekerk, C.V.: Multi-bias direct extraction of FET series parasitic elements, (2020)

- Van Niekerk, C., du Preez, J., Schreurs, D.: A new hybrid MultiBias analytical/decomposition-based FET parameter extraction algorithm with intelligent bias point selection. IEEE Trans. Microw. Theor. Tech. 51(3), 893–902 (2003). https://doi.org/10.1109/tmtt.2003.808631

- Lim, C.L.: Limiters protect ADCs without adding harmonics. Microw. RF 54(1), 56–60 (2015)

- Mazzillo, M., et al.: Temperature and light induced effects on the capacitance of 4H-SiC Schottky photodiodes. IEEE Sensors 12(5), 1127– 1130 (2012). https://doi.org/10.1109/jsen.2011.2166541

- Devlin, L., Dearn, A., Beasley, P.: A monolithic, dual channel, 0.5 to 20GHz limiter. In: 30th European Microwave Conference, pp. 1–4. Paris (2000)

- Tan, R., Kaul, R.: Dual-diode limiter for high-power/low-spike-leakage applications. IEEE Int. Dig. Microwave Symp. 2, 757–760 (1990)

How to cite this article: Botha, C.J., Stander, T.: The effect of temperature variation on the transient response of RF PIN diode limiters for very high frequency applications. IET Microw. Antennas Propag. 1–11 (2024). https://doi.org/10.1049/mia2.12508