# **Protection Testing for Multiterminal High-Voltage dc Grid:**

# **Procedures and Assessment**

Zhou Liu; Seyed Sattar Mirhosseini; Marjan Popov; Yash Audichya; Daniele Colangelo; Sadegh Jamali; Peter Palensky; Weihao Hu; Zhe Chen

#### Zhou Liu

Department of Energy Technology, Aalborg University, Aalborg, Denmark

Zhou Liu (zli@et.aau.dk) earned his Ph.D. degree in energy technology at Aalborg University, Denmark, in 2013. In December 2014, he began work as a postdoctoral researcher at the Department of Electrical Power Engineer, Norwegian University of Science and Technology. From 2017–2018, he worked as a postdoctoral fellow at the Department of Electrical Sustainable Energy, Technische Universiteit (TU) Delft, The Netherlands. Currently, he is an assistant professor in the Department of Energy Technology, Aalborg University, Denmark. He has been involved in the Progress on Meshed HVdc Offshore Transmission Networks project at TU Delft and the EUDP Voltage Control and Protection for a Grid Toward 100% Power Electronics and Cable Network project at AAU. He is a Senior Member of the IEEE.

#### Seved Sattar Mirhosseini

School of Electrical Engineering, Iran University of Science and Technology (IUST), Tehran, Iran Seyed Sattar Mirhosseini (s\_mirhoseini@elec.iust.ac.ir) earned his B.Sc. degree in electrical engineering from the Iran University of Science and Technology (IUST), Tehran, in 2010 and his M.Sc. degree in electrical engineering from the Shahed University, Tehran, Iran, in 2013. He is currently pursuing his Ph.D. degree in electrical engineering at IUST. His research interests include power system protection, in particular the protection of multiterminal high-voltage dc (HVdc) grids and HVdc circuit breakers. He has been involved in the Progress on Meshed High-Voltage dc Offshore Transmission Networks project as a visiting researcher at Technische Universiteit Delft. He is a Student Member of the IEEE.

# Marjan Popov

Electrical Power Engineering, Technische Universiteit, Delft, The Netherlands

Marjan Popov (M.Popov@tudelft.nl) earned his Ph.D. degree in electrical power engineering from Technische Universiteit Delft, The Netherlands, in 2002. In 1997, he was an academic visitor at the University of Liverpool. He is a member of CIGRE and actively participated in Working Group C4.502 and Working Group A2/C4.39. He was a recipient of the IEEE PES Prize Paper Award and the IEEE Switchgear Committee Award in 2011. He is an associate editor of International Journal of Electric Power and Energy Systems. His research interests include future power systems, large-scale power system transients, intelligent protection for future power systems, and wide-area monitoring and protection.

## Yash Audichya

System Design and Engineering, ABB, Sweden

Yash Audichya (yashaudichya@gmail.com) is the vice president of Faraday Grid, United Kingdom. He was a project manager with Power Research and Development Consultants Pvt Ltd, India, from 2003 to 2010; a system design and engineering manager with ABB, Sweden, from 2010 to 2012; principal consultant with Petrofac, TNEI, from 2012 to 2013; and the head of technology in Scottish and Southern Electricity Networks, United Kingdom, from 2013 to 2019.

# Daniele Colangelo

Electrical Engineering, Ecole polytechnique fédérale de Lausanne (EPFL), Switzerland Daniele Colangelo (daniele.colangelo3@gmail.com) earned his B.Sc. and M.Sc. degrees in electrical engineering from the University of Bologna, Italy, in 2006 and 2009, respectively. In 2013, he earned his Ph.D. degree in electrical engineering from the Ecole polytechnique fédérale de Lausanne (EPFL), Switzerland. From 2014 to 2016, he was a postdoctoral fellow at the Distributed Electrical System Laboratory, EPFL. He is currently with Services Industriels de Genève. His research interests include the calibration and development of phasor measurement units, real-time monitoring of active distribution networks, numerical modeling of electrothermal systems, smart meters, advanced metering infrastructure, supervisory control and data acquisition systems, and IT/operational technology security.

#### Sadegh Jamali

School of Electrical Engineering, Iran University of Science and Technology, Terhan, Iran Sadegh Jamali (sjamali@iust.ac.ir) earned his B.Sc. degree from Sharif University of Technology, Iran, in 1979; his M.Sc. degree from the University of Manchester, United Kingdom, in 1986; and his Ph.D. degree from the University of London, United Kingdom, in 1990, all in electrical engineering. He is currently with the School of Electrical Engineering at the Iran University of Science and Technology. He is a fellow of the Institution of Engineering and Technology and a chartered engineer in the United Kingdom. His research findings have been published in more than 250 articles in journals and international conferences. His research interests include power system protection, distribution systems, and railway electrification, where he is heavily involved in industrial consultancy.

#### Peter Palensky

Electric Power Grids, Technische Universiteit (TU), Delft, The Netherlands

Peter Palensky (P.Palensky@tudelft.nl) is a professor of intelligent electric power grids at Technische Universiteit (TU) Delft, The Netherlands. He previously worked as the principal scientist for complex energy systems at the Austrian Institute of Technology (AIT)/Energy Department, Austria; head of business unit "Sustainable Building Technologies" at the AIT; chief technology officer of Envidatec Corp., Hamburg, Germany; associate professor at the University of Pretoria, South Africa; and researcher at the Lawrence Berkeley National Laboratory, California. He works on the digital aspects of intelligent energy systems and operates an RTDS-based power system digital twin at TU Delft. He is a Member of the IEEE Industrial Electronics Society.

#### Weihao Hu

Institute of Smart Power and Energy Systems, University of Electronics Science and Technology of China Weihao Hu (whu@uestc.edu.cn) is currently a full professor and the director of the Institute of Smart Power and Energy Systems at the University of Electronics Science and Technology of China. He has led/participated in more than 15 research projects and has more than 140 publications. He has been the guest editor of IEEE Transactions on Power Systems Special Section: Enabling Very-High-Penetration Renewable Energy Integration Into Future Power Systems. He served as the technical program chair for IEEE International Innovative Smart Grid Technologies Conference—Asia 2019. His research interests include intelligent energy systems and renewable power generation. He is a Member of the IEEE Industrial Electronics Society.

### Zhe Chen

Department of Energy Technology, Aalborg University, Denmark

Zhe Chen (zch@et.aau.dk) earned his Ph.D. degree in electrical engineering from the University of Durham, United Kingdom. He is a full professor with the Department of Energy Technology, Aalborg University, Denmark. He is the leader of Wind Power System Research Program with the Department of Energy Technology, Aalborg University, and the Danish principal investigator for wind energy of the Sino-Danish Centre for Education and Research. He has led many research projects and has more than 500 publications in his technical fields. His current research interests include wind energy and modern power systems. He is a Fellow of the Institution of Engineering and Technology and the IEEE and is a chartered engineer in the United Kingdom. He is a Member of the IEEE Industrial Electronics Society.

## **Abstract**

The application of multiterminal (MT), high-voltage dc (HVdc) (MTdc) grid technology requires test procedures for the operation and implementation of the protection solutions. The test procedures are usually derived from experience and from extensive measurement data, which, at present, are still not widely available. Based on a hardware-in-the-loop (HIL) method, advanced dc protection testing strategies, utilizing existing experience for ac grids and requirements for MTdc grids, may overcome this gap.

This article proposes procedures and guidelines for testing system-level dc protection based on the functionality of MTdc grids for both primary and backup dc protection. Specific performance criteria have been defined, based on multicase testing and statistical analysis, with the considerations of related critical testing parameters for each functional requirement of the dc protection. Accordingly, procedures for a dc protection testing environment and various fault scenarios are defined. The proposed algorithm test procedures will contribute to the standardization of dc protection system design and testing.

# **Background**

Renewable energy sources (RESs) have many advantages for the environment and sustainable energy development. The replacement of traditional fossil fuels by RESs is an energy development trend and energy policy requirement for future power systems [1]. In northern Europe, in particular, the installation of offshore wind power is ever increasing; hence, the development of HVdc systems to support wind power integration is becoming more urgent. The evolution of HVdc systems from point-to-point connections and radial HVdc grids to meshed MTdc grids by making use of voltage source converter (VSC) technology, especially modular multilevel converter (MMC)-based schemes, is also a significant subject for the European power utilities and governments [2]. Worldwide, there are already many relevant projects commissioned or being developed, such as the Québec—New England three-terminal HVdc system [3], Nan'ao four-terminal HVdc system [4], and Zhoushan five-terminal grids [5].

One of the main challenges of the implementation of HVdc power grids is the unavailability of standardized approaches for grid protection, which is a significant barrier for the secure operations of new HVdc grids [5]. DC fault currents in MTdc networks increase rapidly in amplitude, and outages can be easily cascaded from one converter station to another. Thus, protection against these faults is very important to provide safety for the HVdc grid operation and to pave the way for the integration of bulk offshore wind power to the ac grid [6], [7].

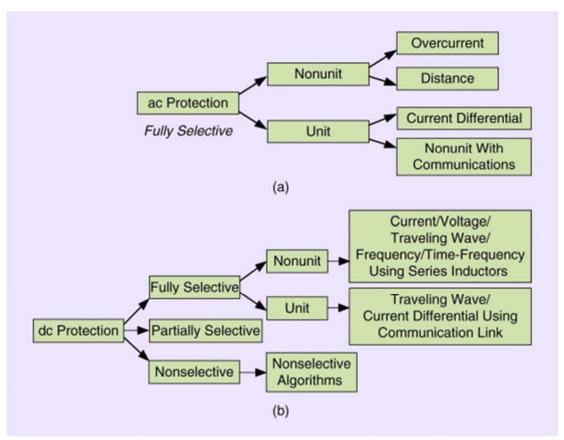

Existing HVdc protection concepts are derived from the well-known HVac protection concepts, as illustrated in Figure 1 [8]. Three kinds of protection philosophies are adopted in MTdc protection, i.e., fully selective, nonselective, and partially selective. In the fully selective philosophy, each line is protected using HVdc circuit breakers (dc CBs) at both ends, so power flow remains uninterrupted in the rest of the grid. In the nonselective philosophy, the whole HVdc grid is protected as one zone by converters with fault-blocking capability or by using acside CBs (ac CBs). The partially selective philosophy is a compromise between the two former ones, in which the grid is divided into several protection zones based on the placement of dc CBs, the converters with fault-blocking capability, and ac CBs [9].

**Figure 1.** The categories of the protection philosophies and examples of algorithms: (a) ac grid protection and (b) MTdc grid protection.

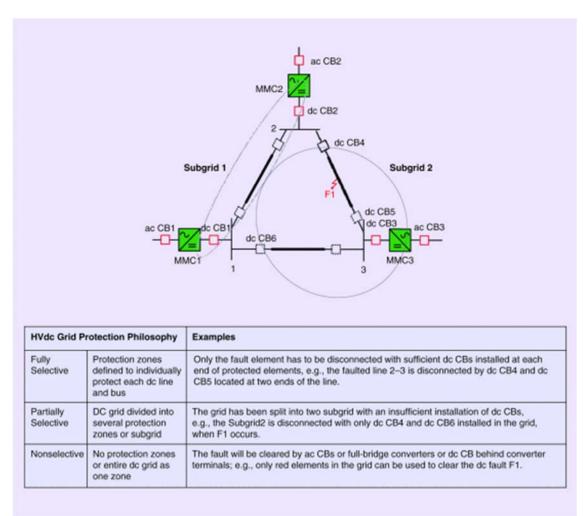

A simple illustration can be seen in Figure 2. When fault F1 occurs in the middle of lines 2 and 3 in the three-terminal HVdc grid, this faulty line will be only disconnected by the dc CB4 and dc CB5 at both line ends in the fully selective philosophy. In the partially selective philosophy, with an insufficient installation of dc CBs, subgrid2 will be disconnected due to F1 only if dc CB4 and dc CB6 are installed. The red elements [ac CBs, full-bridge (FB) converters, or dc CBs behind converter terminals] will be used to clear F1 in the nonselective philosophy, in which the whole dc grid will be isolated.

Figure 2. The different MTdc grid protection philosophies.

There have been many different HVdc grid protection algorithms proposed by academia and industry so far, which can be categorized as unit protection and nonunit protection. Unit protection algorithms are based on double-ended detection, which makes use of closed protection zones; nonunit protection algorithms are realized with single-ended detection and open zones. The nonunit protection algorithms are mainly used for the primary protection functions, which can be current/current derivative- [10], [11], voltage/voltage derivative- [12], [13], and traveling wave-based approaches [14]–[15][16]; different combinations of these approaches [17], [18]; and frequency or time domain approaches [19]–[20][21].

The unit protection algorithms mainly include the current differential [22] and traveling wave differential [23]. Since communication is required for unit protection, it is used for the primary protection functions of the bus bar or for the protection of short lines and as a backup protection function of longer dc lines [24]. Possible protection failures (including breaker failure and relay failure) need to be considered in backup protection functions of an MTdc grid protection system [25].

There are no consensus and standards, so far, about how the dc protection algorithms perform and how they could be used for practical implementation [8]. Considering that today's dc CBs can operate in several milliseconds, fault detection realized by the protection algorithms should

also be within the same timescale, which also depends on the speed of fault current development and the withstand capability of system components [26].

In HVdc systems, the current source converter (CSC)-based HVdc, which is known as *classic HVdc*, can control the dc current during a dc fault. However, the CSC HVdc is, currently, mainly limited to the applications of point-to-point connections, since the reversal of the power flow direction requires a change of voltage polarity on all terminals, and there are other bottlenecks associated with the control systems. The application of dc CBs in CSC HVdc systems is limited, and the maximum ratings are 250 kV, 8 kA or 500 kV, 4 kA, which are not more than 1.6 times the rated nominal current. An interruption time on the order of 35 ms is sufficiently fast for CSC HVdc systems, where large inductors serve to limit the rate of rise of the fault current. These dc CBs are very large and more expensive than the ac CBs for comparable current and voltage ratings. Therefore, for point-to-point CSC HVdc connections, the controlled converter stations or installed ac CBs at the ac side of CSCs are applied to disconnect the HVdc from the ac side [27].

Regarding the fault current characteristics, VSC HVdc systems are mainly distinguished from the CSC HVdc systems by the higher rates of rise and large magnitudes of the fault currents as well as the lower current withstand capability of VSC power electronics [27]. These differences necessitate higher fault current-breaking capabilities within shorter interruption times of the dc CBs in VSC-based HVdc grids.

For VSC HVdc, the MMC, as the most promising option to develop an MTdc grid, can adopt either a half-bridge (HB) or FB structure for each submodule. The HB MMC with freewheeling diodes is unable to stop ac grid contribution to the dc fault currents, and the excessive current stresses may damage the freewheeling diodes. Therefore, the requirement for fast dc CBs becomes inevitable. Moreover, to realize a fully selective protection philosophy and provide power supplying continuity for the healthy part of HVdc grids, more dc CBs are required to be installed to protect each line and bus in the grid, even though the FB MMC can block current flow in the converter during dc faults.

The objective of the protection testing is to determine whether the performance of an intelligent electronic device (IED) can meet the industry requirements before it can be commissioned in practical applications [28]. Since the converter self-protection scheme is vendor dependent, the scope of the future MTdc grid protection for MTdc grids, here, excludes converter protection. For ac protection testing, well-established designs and methods can be adopted according to IEEE and International Electrotechnical Commission (IEC) standards [29], [30]. In these ac protection standards, the performance test (or type testing) is normally conducted by IED vendors to verify, describe, and certify the performance of protection IEDs used in a specific application, which is normally tested by a simple power system model.

The application tests are normally driven by the users to determine the suitability of an IED for a specific protection system design application. The tests are based on a detailed model of the power system in question and include performance testing against a wide variety of possible fault conditions. The goal of application tests is to ensure that a specific protection IED can perform adequately for a specific application or location before actual installation. These general concepts and classifications of protection testing will be continuously applied in MTdc grids, even though the challenges and requirements are different for dc protection testing [31].

In this article, MTdc grids are the target test power systems, and the application tests are mainly focused from users' viewpoints to provide reasonable test procedures for dc protection testing. Although the fault dynamics and the related protection algorithms of MTdc grids have been investigated and designed by many researchers [10]-[25], no certified HVdc protection IED has been commissioned so far. Moreover, the relatively new testing considerations and methods of MTdc grid protection have rarely been discussed, and many published articles are mainly focused on one specific protection algorithm [32]-[37].

A fault detection and location scheme using the rate of change of voltage measured for an HVdc grid is proposed and tested in [32], where the different fault types and locations have been mainly considered in testing, and a systematic procedure for calibrating the protection threshold values is designed. A transient measured impedance-based protection scheme for HVdc line faults is proposed in [33], where numerous simulations on the power systems CAD/electromagnetic transients including dc (PSCAD/EMTDC) platform and field fault recording data-based tests have been utilized with the consideration of fault types, fault locations, and sampling frequency. A similar PSCAD/EMTDC-based test has been used in [34] for a generalized protection strategy of HB MMC-based MTdc grids with a fault current limiter branch and hybrid dc CBs, where the different fault resistances, line inductors, and types of dc CBs are considered during the testing.

The types of dc lines and prefault operation points of MTdc grids were used to test a proposed new protection method in [35]. A real-time OPAL-RT-based HIL testing platform was developed in [36] to demonstrate and validate an integrated control and protection scheme for HV ac/dc grids, where the fault types, locations, and combinations are mainly considered. In [37], HIL-based testing was regarded as an ideal choice to simulate the transients of MMC stations and to test the dynamic performance of a complete control and protection system for the Nan'ao VSC-MTdc grid (i.e., application test).

The aforementioned testing methods are normally introduced together with the new dc protection algorithms, which only consider several important factors or requirements about the specific protection algorithms simulated in the simulation software or hardware environment. They are not appropriate or efficient for industrial testing on multifunctional protection IEDs. In this article, one user-oriented application testing approach for industrial applications of HVdc grid protection is developed based on three steps:

- a systematic investigation and summary of new requirements along with testing considerations for HVdc grid protection in both the component and system levels

- new systematic test procedures for protection IEDs in HVdc grids, based on the statistical analysis of dc fault cases and performance criterion checking

- a new systematic assessment method for possible protection algorithms implemented in multifunction protection IEDs.

Thus, the main contribution of this article is to develop dc protection testing methods for systematic testing and assessment of the newly proposed MTdc grid protection algorithms. In this way, it can be determined whether the proposed algorithms can meet the operation requirements of the MTdc grids [38].

# **New Challenges and Requirements**

### **General Considerations**

The choice of a specific MTdc grid protection philosophy, i.e., fully selective, partially selective, and nonselective, fundamentally determines the size of the grid part that will be isolated from the rest of the grid during a fault at a particular location. Moreover, since the protection of MTdc grids deals with complex fault scenarios and fast operational performance and takes into account the performance of the dc CBs, the system-level protection of MTdc grids is regarded as one of the most difficult remaining technical challenges in the power system. Some related considerations for future dc applications can be listed as follows [8]:

- multivendor solutions with a proper consideration of interoperability

- the much quicker response of MTdc grid protection for dc faults without current zero crossings

- the development and implementation of dc protection testing methods for the newly available dc protection algorithms.

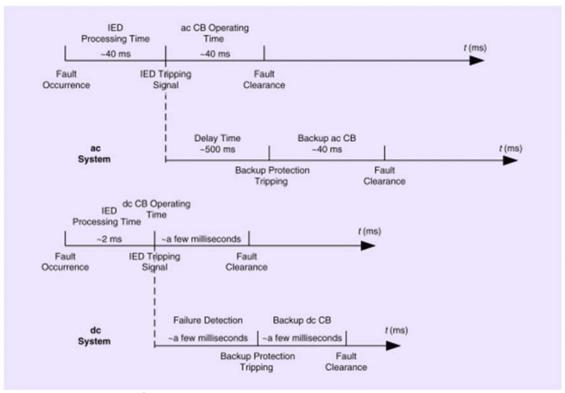

Figure 3. The typical times for primary and backup protection in ac and dc systems.

In addition to the general differences from ac protection shown in Figure 1, the fault-clearing times of both the primary and backup protections in MTdc grids are typically one order of magnitude faster compared to those in ac grids. For example, the fault-clearing time of the primary protection is, typically, in the range of several milliseconds, from which 2 ms are allocated for the protection IED processing time and several milliseconds for the dc CB operation time [31]. A related comparison of the time sequences of ac and dc protections can be observed in Figure 3 [8]. As there are only a few practical dc CB prototypes applicable for HVdc grids and

there is not much experience in this area, the term *a few milliseconds* is adopted based on the interruption time of the existing prototypes.

# Requirements and Constraints for dc Protection and Testing

The system-level protection of MTdc grids needs to consider the coordination between IEDs, dc CBs, and converters to secure the operation of a large meshed MTdc grid. If the whole operation environment of dc protection is considered, the requirements or constraints for the operation of ac/dc power grids need to be checked [9], [24]. The development and the investment of MTdc grid protection is a tradeoff between the costs and the availability. The constraints for MTdc grid protection are imposed by the following.

- The limits of MTdc system components: The maximum acceptable time for dc fault

clearing is mainly limited by the overcurrent capability of the power electronics of the

HVdc converters, and it also depends on the converter topology. Moreover, the dc CBs

applied at HV levels must be able to absorb the energy of the fault current by the surge

arresters during the fault current interruption.

- The stability of the control system in the MTdc grid: The control system responsible for the control of the voltage and the power flow to ensure stability of the MTdc grid imposes a limit on system-level protection. The related criteria and the stability limits have been discussed in CIGRE technical brochure 657 [9].

- The stability of ac systems: The loss of power due to a dc fault should not exceed the

maximum loss of infeed as designed, according to the ac grid codes of specific power

systems. Furthermore, dc faults should be cleared in a timely manner to avoid instability

issues in the ac grid.

When local dc protection is considered, the requirements can be listed as follows:

- functional requirements, as described in Table 1

- requirements on protection system components.

**Table 1** The functional requirements for dc protection [24].

| PROTECTION FUNCTIONAL REQUIREMENT | DEFINITION                                                                                                                                                                                       |  |  |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Sensitivity                       | Detection of every dc fault, including high-impedance faults                                                                                                                                     |  |  |

| Selectivity                       | Operating only after fault occurrence and only if the fault is in a related protection zone                                                                                                      |  |  |

| Speed                             | To be fast enough to interrupt faults before they may damage grid equipmen                                                                                                                       |  |  |

| Reliability                       | To perform a required function under given conditions for a given time interval, i.e., security and dependability                                                                                |  |  |

| Robustness                        | Having the ability to detect dc faults in normal operation mode as in<br>degraded operation mode and to discriminate faults from any other<br>operation occurrence (set point changes and so on) |  |  |

| Seamlessness                      | After the fault clearance, the ability to keep the remaining part of the system operating in a secure steady state                                                                               |  |  |

The requirements for the components, such as measuring, detecting, and acting components, can be determined according to how long the system can sustain a particular disturbance. The MTdc grid protection philosophy is fundamentally determined by the selectivity of the protection devices and the way of dc fault current interruption development. To effectively

implement dc protection algorithms and meet the speed requirement, nonconventional instrument transformers with a bandwidth of a few megahertz, e.g., fiber-optic current/voltage sensors [39], need to be adopted.

The main technologies and the bandwidth of today's instrument transformers are summarized in Table 2. As an example, the Rogowski coil has attracted much attention in the electric power industry, as it can meet the requirements of dc protection for frequency bandwidth and dynamic accuracy due to its superior performance, inherent linearity, outstanding dynamic response, wide bandwidth, and without magnetic saturation. These features can support accurate and reliable data measurement to trace the faulty dynamics in the dc system for those protection applications when the Rogowski coil is combined with the shunt capacitor [8].

Table 2 The technologies and bandwidths of the instrument transformers [8].

| TYPE     | TECHNOLOGY                                                | BANDWIDTH         | APPLICATION |

|----------|-----------------------------------------------------------|-------------------|-------------|

| CT       | Electromagnetic (iron core)                               | A few kilohertz   | ac          |

|          | Hybrid electro-optical (combined shunt and Rogowski coil) | A few megahertz   | ac/dc       |

|          | Fiber-optic current sensor (magneto-optic effect)         | A few megahertz   | ac/dc       |

|          | Zero flux (dc CT)                                         | A few hundred kHz | dc          |

|          | DC zero flux (Hall effect CT)                             | A few hundred kHz | dc          |

| VT       | Inductive VT                                              | few kHz           | ac          |

|          | Capacitor VT                                              | few kHz           | ac          |

|          | Compensated resistive-capacitive divider                  | few MHz           | ac/dc       |

|          | Fiber-optic voltage sensor (magneto-optic effect)         | few MHz           | ac/dc       |

| CT: curr | ent transformer; VT: voltage transformer.                 |                   |             |

The digital interface of instrument transformers for both ac and dc applications is specified by IEC 61869-9 [40]. To perform general measurement and protective data processing, the typical sampling rates for ac and dc measurements are 4.8 kilo samples (ksa)/s and 96 ksa/s, respectively. The fault current interruption capability of the dc protection system is determined not only by the capability of dc CBs but also by the system design of the converter and the current limiter. The speed requirement and the interaction between the dc CB and dc protection can be briefly observed in Figure 3. If more details and testing of dc protection are considered, the specific hardware, software, and communication protocols should be investigated [9], [29]:

- hardware platform: e.g., an HIL testing platform based on the real-time digital simulator (RTDS), protection IEDs, physical interfaces, and connections

- *software platform*: i.e., power system and control function models, reasonable test cases, protective function algorithms, and dc CB models

- *communication*: a hardware- or software-defined data transmission network for the links between any combinations of the hardware platforms and software platforms.

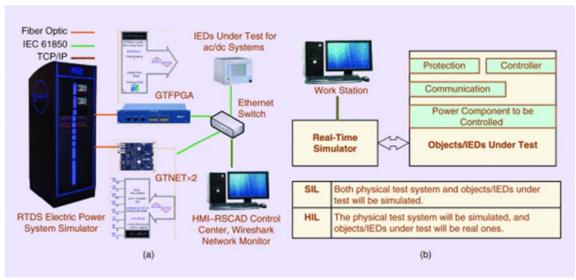

An example of a real-time cyberphysical testing platform can be seen in Figure 4(a). The test MTdc grid is first developed in RSCAD software and then simulated in real time using RTDS [41]. To simulate detailed models of HB MMC converters, dc CBs [26], [42] in small time-steps, and new dc protection algorithms, new generations of processors in RTDS are preferred. Furthermore, the IEC 61850-9-2LE sample value communication [43] has been developed based on one GTFPGA unit and one GTNETx2 card, together with the related software interface configuration within the RTDS racks.

**Figure 4.** The real-time simulation platforms. (a) One example based on RTDS and IEC 61850-based ICT infrastructure. (b) The general groups of real-time simulation: SIL and HIL. ICT: information and communications technology. HMI: human—machine interface. (Source: RTDS.)

The sample values of the critical measurement points in the MTdc grids are provided by GTFPGA-based merging unit functions to the local Ethernet network, while the GTNETx2 card is configured to obtain the sample values from the local network for the protection functions modeled in RTDS. The related message flows can be monitored and analyzed based on the manageable Ethernet switch and Wireshark network analyzer [44]. If the protection IEDs under test for ac/dc systems are available with the required communication interfaces, then the application performances of IED under test can be easily testified based on this simulation platform, shown in Figure 4(a).

There are many different schemes using real-time simulation for the testing and commissioning of protection, control, and communication systems, which can be mainly categorized into two groups, i.e., software in the loop (SIL) and HIL. A simple illustration can be seen in Figure 4(b). In an SIL scheme, both the controller and the physical test system are simulated by RTDS, when it is difficult to access IEDs. In an HIL scheme, the IED under test is accessed and connected to the real-time simulator through specific interface converters, e.g., amplifiers and sensors [45]. The test platform shown in Figure 4(a) can be regarded as SIL with additional communication links for IEC 61850-9-2LE, when the object under test is the simulated relay model in RTDS. When the object under test is the protection IEDs, then the related testing schemes based on the test platform in Figure 4(a) belong to HIL schemes.

In an RTDS-based simulation platform, the network solution technique is performed by nodal analysis. This is different from the OPAL-RT-based simulation, which is realized by a state—space nodal method to perform network calculations [46]. For every real-time simulator, the online simulation is discrete time based. With a large number of data points computed within a given power system cycle, the online simulation approximates the continuous time power system appropriately [47].

# **Test Procedures for MTdc Grid Protection**

### The Structure of Test Procedures for dc Protection

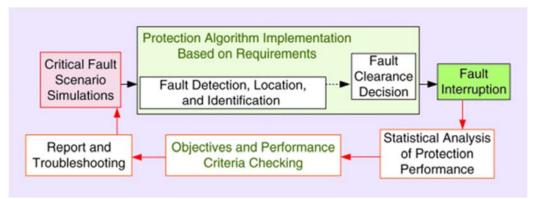

The script of protection performance testing is depicted in Figure 5. The blocks with black arrows represent the normal progress of fault development and protection performance, while the blocks with red arrows represent the evaluation and testing progress.

Figure 5. The general script of protection performance testing.

The general testing steps for the dc protection can be described as follows:

- step 1: fault scenarios: simulation-based fault studies

- step 2: statistical analysis of system-level performance

- step 3: threshold setting adjustment

- step 4: criteria checking

- step 5: report and troubleshooting.

The details of these five steps are different when the dc protection function is different, e.g., primary protection testing and backup protection testing are conducted with different fault scenarios, which will be introduced later.

### **Test Circuit and Fault Scenarios**

Figure 6 shows an example of a simulated dc fault current in the four-terminal meshed HVdc grid based on the testing platform in Figure 4(a). This MTdc grid is built on an HB MMC and cable lines, and each cable is terminated by mechanical dc CBs [6] and series inductors. The related specification of the MTdc grids is included in Table 3, and more data on the system and controllers can be found in CIGRE technical brochure 604 [48]. It should be noted that, in Figure 6, the MTdc test system, fault scenarios, and the current waveforms are simulated and produced based on the RTDS simulation platform, which aims to testify the system-level performances of studied protection IEDs. The main time-step in RTDS is set as 50  $\mu$ s, while VSCs and dc CBs make use of a small time-step of 3.124  $\mu$ s.

**Figure 6.** The fault interruption progress in the four-terminal HVdc grid. (a) The four-terminal HVdc test system in RTDS. Y and D represent the types of transformer winding: Y is the star type, and D is the delta type. (b) The fault interruption progress.

**Table 3** The AC grids and MMC parameters.

|                                   | CONVERTER           |                  |

|-----------------------------------|---------------------|------------------|

| PARAMETER                         | MMCs 1,<br>2, AND 4 | MMC 3            |

| DC voltage                        | ± 200 kV            | $\pm$ 200 kV     |

| Converter ac voltage              | 220 kV              | 220 kV           |

| Rated power                       | 800 MW              | 1,200 MW         |

| Number of sub-<br>modules per arm | 400                 | 400              |

| Arm resistance R <sub>arm</sub>   | $0.54~\Omega$       | $0.36~\Omega$    |

| Arm reactor L <sub>arm</sub>      | 29 µH               | 19 µH            |

| Arm capacitance C <sub>arm</sub>  | 25 µF               | 37.5 μF          |

| Transformer leakage reactance     | 0.18 per<br>unit    | 0.18 per<br>unit |

| AC grids                          |                     |                  |

| 1-ac grid and 2-ac grid           | 380 kV              |                  |

| 3-ac grid and 4-ac grid           | 145 kV              |                  |

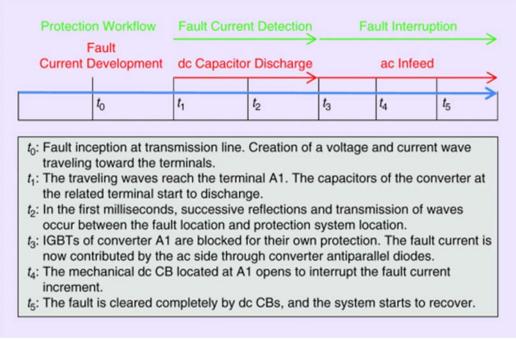

When a fault occurs at the end of the line between converters A1 and C1 at time  $t_0$ =0.1 s, the related traveling wave reaches the terminal A1 at  $t_1$ =0.1056 s. Then, the dc fault current quickly increases, and its rate of rise is limited by the series inductors. In the first millisecond, successive reflections (e.g., at  $t_2$ ) occur, caused by waves traveling along the line between the fault location and the protection system location. Furthermore, other terminals start to feed into the fault current. At  $t_3$ , converter A1 blocks its insulated-gate bipolar transistors (IGBTs), and the dc fault current is fed by the ac side. All converters in the system are blocked around  $t_3$ . At  $t_4$ , the mechanical dc CB located at A1 opens to interrupt the fault current increment. Eventually, after  $t_5$ , the fault is completely cleared by dc CBs installed in the faulty line between A1 and C1. A detailed overview of the phenomena, which occur during the fault, is given in Figure 7.

**Figure 7.** The progress of fault clearance.

It should be noted that the dc grid protection considered in this article excludes the converter protection that is normally designed by different converter vendors. However, in the real or simulated cases, these two protection systems are incorporated with each other. In the simulation example in Figures 6 and 7, the recommended parameters from [48] are directly adopted for the converter protection, e.g., the valve current threshold of 6 kA and dc bus voltage threshold of 0.9 per unit are considered. The fault current withstand capability of the freewheeling diodes is set based on their own design parameters, e.g., the thermal capability limits.

To deal with a possible current imbalance in the combination of diodes for the MMC, the thermal capability limit could be calculated based on the minimum current thermal limit of each diode, which could resort to a related reliability test. Moreover, when a hybrid dc CB is applied instead of a mechanical dc CB, the break time can be improved from approximately 8 to 2 ms [8], which can release the thermal stress on the remaining components in the fault current loop.

Based on the progress and mechanism analysis during the dc fault development and interruption, the critical parameters influencing the dc fault current and the related dc protection system can include the type of transmission lines, fault resistance, dc-side inductance, dc-side capacitance, converter blocking instant, ac system strength, earthing system, and converter topology [24]. The impact of these parameters is briefly explained in Table 4. In addition, the sampling frequency is critical for the signal processing and the operation speed of dc protection; a sampling frequency of 96 ksa/s is assumed here, considering the IEC 61869 standards [40].

**Table 4** The critical parameters influencing the dc fault current.

| CRITICAL PARAMETERS        | INFLUENCE ANALYSIS                                                                                                                                                                                                                                                                                                                                            |  |  |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Transmission line type     | The characteristic impedance of the overhead line (OHL) is larger than for cables, which causes current waves to be smaller in amplitude. The traveling wave speed of the OHL is about the speed of light, whereas, for cables, this is half to two thirds the speed of light.                                                                                |  |  |

| Fault resistance           | An increasing fault resistance leads to a smaller prospective steady-state fault current.                                                                                                                                                                                                                                                                     |  |  |

| DC-side inductance         | Increasing the dc-side inductance decreases the rate of rise of the current but does not make an impact on the prospective steady-state fault current.                                                                                                                                                                                                        |  |  |

| DC-side capacitance        | A dc-side capacitance (as, e.g., used in two-level topologies) initially provides a large discharge current.                                                                                                                                                                                                                                                  |  |  |

| Converter blocking instant | The converter blocking instant determines the amount of discharge of the submodule capacitors. Delaying the converter blocking instant increases the capacitor discharge.                                                                                                                                                                                     |  |  |

| AC system strength         | The ac system strength mainly determines the value of the prospective steady-<br>state current. An increased ac system strength leads to an increased value of the<br>prospective steady-state current, only limited by the short circuit impedance of<br>the connecting equipment, such as transformers.                                                     |  |  |

| System earthing            | Low impedance earthing results in a higher fault current, and high impedance earthing leads to a lower fault current. Earthing impedance and topology also have an effect on fault transient behavior.                                                                                                                                                        |  |  |

| Converter topology         | Where new VSC converter topology is concerned, HB MMC cannot block the fault current, since there is always an uncontrolled current path via the freewheeling diodes in this topology; FB MMC can block the fault current and reach current zero, since there are no fault current paths available when IGBTs have been switched off during the fault period. |  |  |

### **Test Procedures**

For the testing of a specific protection IED, the specifications of the protection functions should be provided by the IED vendor first. The critical ratings and the performance limitations of the basic protection functions, e.g., input, output, detection, directional determination, measurement accuracy, sampling rate, and so on, should be declared by the IED vendor as well. According to IEC 60255-1 [30], the general type (unit) testing is used to verify the new hardware/software designs against the product specifications and the standards. However, the verification procedure for the overall system is important to ensure that equipment is in accordance with its specifications, all functions perform correctly during the initial measurement at the beginning of the test sequence, and it maintains its design characteristics throughout all of the specified tests.

With the consideration of the fully selective fault-clearing strategy, the primary protection algorithms should be implemented together with the suitable dc CB models. The operation time and the sequences of the protection system can be obtained directly based on the RTDS models,

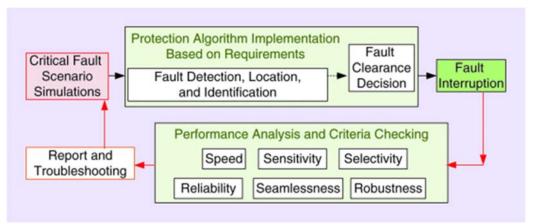

as shown in Figure 5. Then, the failure rate of the primary protection can be easily obtained based on the simulated performances. Different test scenarios will be required for different dc system configurations. It is assumed that the testing system is developed for a symmetric, monopole, HB MTdc grid, a fully selective fault-clearing strategy, and related dc CBs. The general testing progress of the primary protection's system-level performance is depicted in Figure 8. The detailed procedures of the related testing steps are listed as follows

Figure 8. The general process of primary protection performance testing.

### Step 1: Fault Scenarios: Simulation-Based Fault Studies

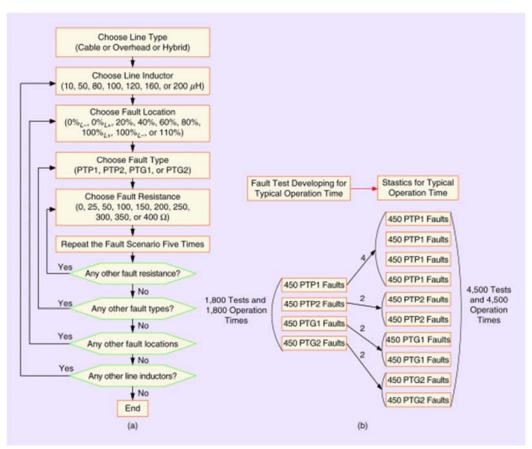

Table 5 shows the critical testing parameters and the related typical values, which could be different according to different testing systems and testing objectives. To perform multicase testing and record the responses of the objective protection systems or protection IEDs, these critical testing parameters can be changed in the proposed scopes. However, the choices of these parameters are system dependent and are, generally, decided by the user/vendor through the knowledge of system studies and operations.

**Table 5** The critical testing parameters for performance testing.

| TESTING PARAMETER    | TYPICAL VALUES                                                                                                                                                                                                                                                          |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fault resistance     | 0–400 $\Omega$ Variation: 0, 25, 50, 100, 150, 200, 250, 300, 350, or 400 $\Omega$                                                                                                                                                                                      |

| Fault type           | PTP1: PTP permanent fault PTP2: PTP self-clearing fault PTG1: PTG permanent fault PTG2: PTG self-clearing fault PTG11: positive PTG permanent fault PTG12: negative PTG permanent fault PTG21: positive PTG self-clearing fault PTG22: negative PTG self-clearing fault |

| Fault location       | 0-100% of the line with reasonable interval, 0% <sub>L-</sub> , 0% <sub>L+</sub> , 20%, 40%, 60%, 80%, 100% <sub>L+</sub> , 100% <sub>L-</sub> , or 110%                                                                                                                |

| Series line inductor | 0–200 μH with reasonable interval<br>0, 10, 50, 80, 100, 120, 160, or 200 μH                                                                                                                                                                                            |

|                      | r the series inductor close to the bus; L+: the fault is applied at the end of ductor; PTG: pole-to-ground; PTP: pole-to-pole.                                                                                                                                          |

### **Step 2: Statistical Analysis of System-Level Performance**

The basic accuracy checking of protection characteristics and the operation time based on the performance analysis will be mainly conducted in this step. The statistical analysis of IED system-level performance is important to find a fault type-based probability distribution, which is the precondition to obtaining and checking the related criteria. The classical transient overreach analysis used in IEC 60255-121 [49] is adopted here for the accuracy testing.

An example of the testing procedures can be seen in Figure 9(a). With the chosen testing parameters in Figure 9(a), multicase testing can be easily conducted. The repeating sequence of five times is a common practice in IED testing in terms of reliability checking.

**Figure 9.** The general procedures for system-level performance analysis: (a) the system-level accuracy testing and (b) the statistics for the typical operation times.

Based on the recorded test performances, the operation times can be determined in a statistical form. For example, the test data at the three fault positions (0%L+, 50%, and 80%) and with L=100 $\mu$ H for the line inductor are considered. This results in a total of 1,800 (600 operation times for the cable line tests, 600 operation times for the overhead line (OHL) tests, and 600 operation times for the hybrid line tests) obtained operation times. This is equal to 450 operation times for each fault type. To create a fault type distribution in the operation time statistics, the following weights are given to the available data according to the fault categories defined in [50].

1. The test results for PTP1 are weighted by a factor of four.

- 2. The test results for the fault types PTP2, PTG1, and PTG2 are weighted by a factor of two.

- 3. The test results for other faults are weighted by a factor of one. These factors are defined according to the fault occurrence probability and its impact on the system.

The weighting is done by simply repeating the available results. Figure 9(b) shows the fault statistics of the typical operation time. In total, 4,500 operation times are available for the statistics.

These tests are aimed at determining the accuracy of the operation times of primary functions. They are based on monitoring the time difference between the arriving instant of the first fault traveling wave to the line end and the operation output signals of the IED. The time range and the associated classes based on the operation time could be defined based on the collected data set. For example, the minimum and maximum operation times in the data set are min\_T=1,512 $\mu$ s, max\_T=4,167 $\mu$ s. Thus, the range of operation times could be defined as 1,500–4,200  $\mu$ s, similar to that reported in [30]. The classes of the performances of the IED under testing can be defined by making average groups with an interval of 300  $\mu$ s, as can be seen in Table 6. Here, it is necessary to point out that, under an IED class, a particular operation time range is chosen.

**Table 6** The critical testing parameters for performance testing.

| CLASS                                | FROM $t \ge [\mu s]$       | TO $t \leq [\mu s]$  | N                               | % N          |                              |

|--------------------------------------|----------------------------|----------------------|---------------------------------|--------------|------------------------------|

| Class 1 (min = 1,500 µs)             | min                        | min + 300            | The number of                   | The          |                              |

| Class 2                              | min + 300                  | min + 600            | operation times<br>belonging to | belonging to | probability<br>of N for each |

| Class 3                              | min + 600                  | min + 900            | each class (n)                  | class (n)    |                              |

| Class 4                              | min + 900                  | min + 1,200          |                                 |              |                              |

| ***                                  |                            |                      |                                 |              |                              |

| Class n                              | $min + (n - 1) \times 300$ | $min + n \times 300$ |                                 |              |                              |

| ***                                  |                            |                      |                                 |              |                              |

| Class <i>M</i> (max = 4,200 $\mu$ s) | $min + (M-1) \times 300$   | max                  |                                 |              |                              |

| max: maximum; min: mini              | mum.                       |                      |                                 |              |                              |

The number of operation times belonging to each class (N), with 300- $\mu$ s resolution, is counted to show the probability distribution of the operation times. The probability of N for each class is calculated, and the values can be filled in Table 6. These procedures are related generally for all IEDs, and the table refers to the IED that will be tested.

### Step 3: Threshold Setting Adjustment

The setting rules, variation range, and accuracy of the thresholds are introduced and analyzed in the type testing of protection IED specifications. However, for system-level testing, more influencing factors will be involved, and the corresponding thresholds can be optimally adjusted to achieve better system-level performance. Thus, the test settings of the thresholds can be expressed as percentages of the available range, with 0% being the minimum available setting, and 100% representing the maximum available setting. Similarly, 50% would indicate the midpoint of the available setting range. The actual setting to be used can be calculated using the following formula:

$$S_{\text{AV}} = (S_{\text{MAX}} - S_{\text{MIN}}) X + S_{\text{MIN}}, \tag{1}$$

where  $S_{\text{AV}}$  is the actual setting value to be used in the test,  $S_{\text{MAX}}$  is the maximum available setting value,  $S_{\text{MIN}}$  is the minimum available setting value, and X is the test point percentage value expressed in the test methodology. For example, assuming the available setting range is 0.1–5 A and the 40% test point percentage, the actual operating current settings are 2.06 A.

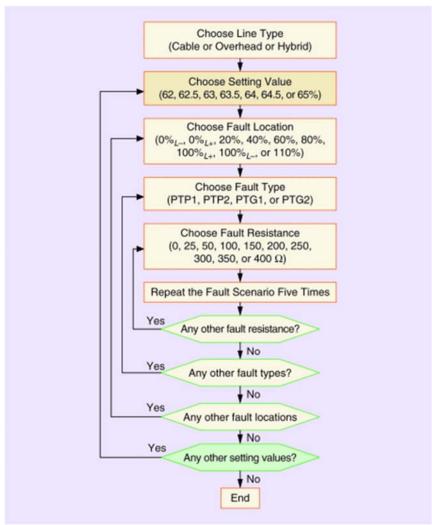

To tune the threshold setting, the testing procedures can be performed with the consideration of variable threshold setting values that will result in the determination of the most accurate threshold setting. For example, if the precalculated threshold setting is 63.5%, the threshold setting values change from 62 to 65% by 0.5%; then, the related testing procedures can be seen in Figure 10. The statistics data analysis can be conducted using the weighting factors of step 2 to obtain the best threshold settings corresponding to the highest probability of correct operation.

Figure 10. The testing procedures for threshold setting adjustment.

## Step 4: Criteria Checking

After the verification of the accuracy and the threshold settings for the specific system operation conditions, the primary protection functions need to be tested when the objectives of protection system performance are met. The critical criteria are speed, sensitivity, selectivity, reliability, seamlessness, and robustness, which were mentioned in the "New Challenges and Requirements" section. To develop these criteria, the performance of the dc protection is divided in three different operations.

- *Correct operations*: The protection system operates for faults in its protection zone within the required time.

- Failed operations: The protection system does not operate for faults in its protection zone within the required time.

- *Incorrect operations*: The protection system operates for faults out of its protection zone.

Then, the related qualification criteria can be expressed as follows:

where  $P_{\text{classes.seped}}$ ,  $-P_{\text{classes.-sensitivity}}$ ,  $P_{\text{classes.selectivity}}$ ,  $P_{\text{classes.dependability}}$ ,  $P_{\text{classes.dependability}}$ ,  $P_{\text{classes.reliability}}$ , and  $P_{\text{classes.robustness}}$  represent the probabilities of related operations for the checking of speed, sensitivity, selectivity, security, dependability, reliability, seamless, and robustness on the protection IED under the test, respectively.

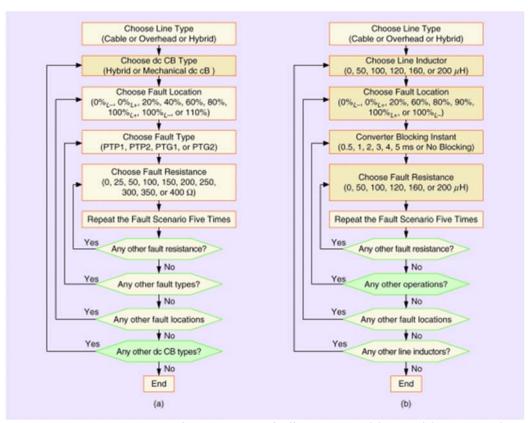

For the checking of each criterion, the critical testing parameters are revised according to specific requirements, which can be compared and observed from Figure 11. The testing procedures on speed, sensitivity, selectivity, and security can be seen from Figure 11(a), (b), (c), and (d), respectively. Thus, the meanings of (2), (3), (4) and (7) are different with different testing parameters, even though they are in the same form.

Figure 11. The testing procedures for the checking of different criteria: (a) speed, (b), sensitivity, (Continued)

Figure 11. (Continued) (c) selectivity, and (d) security checking.

Since the speed of the primary protection is related to the time when the current reaches the dc CB interruption capability, a fast breaker could allow more complex and time-consuming algorithms to be applied. Thus, the different dc CB types are considered in the test procedures of speed checking, as shown in Figure 11(a). For the sensitivity checking in Figure 11(b), those testing parameters, which have big impacts on the operation quantities to give the possible minimum faulty condition, will be considered more, e.g., high fault impedances, different line inductors, converter blocking instants, and fault locations.

PTG faults are mainly considered in the sensitivity checking. For the selectivity checking, the fault resistance, fault location, fault type, and line inductor are chosen as critical testing parameters, with a greater focus on the borders of protection zones. The related changes on the related parameters can be found in Figure 11(c).

For the security checking, the unnecessary protection operations could result from the loss of selectivity and sensitivity due to wrong thresholds or the operation condition changing, e.g., dc line outage (dcL), energization/deenergization of a converter, and so on. Thus, in addition to the

testing parameters considered for selectivity and sensitivity, the operation condition changes due to dcL and energization/deenergization of a converter must be considered in security-related testing. Neighboring dcL1 and deenergization of a local converter [converter event 1 (COE1)] are added in the fault type block in Figure 11(d).

After these multicase tests conducted by the corresponding testing procedures, the fault data statistics analysis is derived based on the user-defined ranges of testing parameters, which have been described in the former steps. Then, the related probabilities can be calculated based on (2)–(5). For the latter, the four criteria checks are related to (6)–(9), and the testing procedures or work flowcharts are similar to the first four criteria checks, but with a different focus. [See (2)–(9) at the bottom of the page.] The dependability is highly related to the sensitivity and the speed. Thus, in the related testing, similar testing parameters and critical time ranges based on dc CB types can be chosen as critical testing parameters. For the reliability, the total number of tests is the sum of the tests performed for the criteria of dependability and security.

| D                                                               | number of correct operations                                                                                                                                | (2)        |

|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| $P_{ m classes.speed} =$                                        | total number of tests                                                                                                                                       | (2)        |

| $P_{ m classes.sensitivity} =$                                  | number of correct operations                                                                                                                                | (3)        |

| r classes.sensitivity —                                         | total number of tests '                                                                                                                                     | (0)        |

| $P_{\text{classes,selectivity}} =$                              | number of correct operations                                                                                                                                | (4)        |

| 2 classes.selectivity —                                         | total number of tests '                                                                                                                                     | (1)        |

| $P_{ m classes.security} =$                                     | number of correct operations                                                                                                                                | (5)        |

| 2 Classes.security                                              | total number of correct and incorrect operations'                                                                                                           | (0)        |

|                                                                 |                                                                                                                                                             |            |

| P.1 J J. Liliu. —                                               | number of correct operations                                                                                                                                | (6)        |

| $P_{\rm classes. dependability} =$                              | $\frac{\text{number of correct operations}}{\text{total number of correct and failed operations}},$                                                         | (6)        |

|                                                                 | total number of correct and failed operations' number of correct operations                                                                                 | ` ′        |

| $P_{ m classes.dependability} = \ P_{ m classes.reliability} =$ | $\frac{\text{total number of correct and failed operations}}{\text{total number of tests}},$                                                                | (6)<br>(7) |

| $P_{ m classes.reliability} =$                                  | total number of correct and failed operations 'number of correct operations total number of tests 'number of effective operations                           | (7)        |

|                                                                 | total number of correct and failed operations ' number of correct operations total number of tests ' number of effective operations total number of tests ' | ` ′        |

| $P_{ m classes.reliability} =$                                  | total number of correct and failed operations 'number of correct operations total number of tests 'number of effective operations                           | (7)        |

The seamlessness of the MTdc grid protection refers to the ability to hold the remaining part of the grid to continue operating in a secure state after the fault clearance [51]. This is related to the continuous adaptability of the MTdc grid protection when the system transfers from a normal operation condition to N-1 or N-k conditions due to a fault clearance. In this case, the effective operations in (8) mean the correct operations of the protection with predefined settings (for specific operation conditions) in a postfault stage, such as the N-1 or N-k stages.

The robustness of the MTdc grid protection refers to the detection of faults in the normal or degraded mode and the discrimination from other operational events in the grid [50]. The difference with respect to seamlessness is that the adaptability to both normal and degraded operational modes is required, but continuous operation transition is not. Moreover, the discrimination from any other operational events causes the robustness to become a kind of reliability as well. Accordingly, in this case, the necessary operations in (9) mean the correct operation of the protection with different predefined settings for different stages, those being adaptive and available for several operation conditions.

## **Step 5: Report and Troubleshooting**

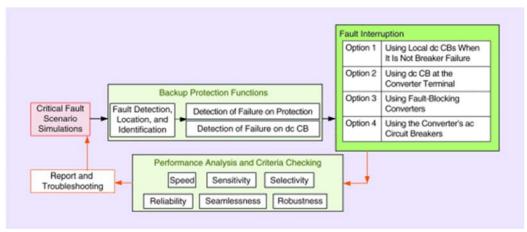

In this step, the summary of the data analysis should be given based on the previous work steps, and the limitations and related troubleshooting should be registered, as illustrated in Figure 8, so that this can be improved for all work steps in future work. For backup protection testing from the viewpoint of the IED under test, the different actions of the backup protection should be mapped to the backup fault-clearing options given for fault interruption and based on the categories in Figure 2 [52].

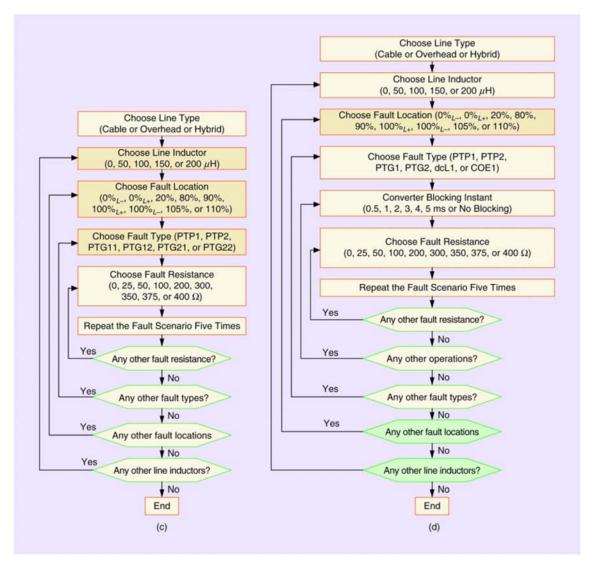

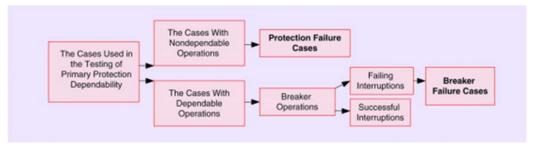

Due to rigorous requirements on the time of fault clearance and communication delays, only local backup will be considered here for the dc protection system. The general testing progress of the backup protection performance is depicted in Figure 12. The testing considerations and steps are similar to those in the primary protection testing, but the failure detection is a critical function of backup protection. Here, two kinds of failures have been considered, i.e., the failure of primary protection and the failure of dc CB operations.

Figure 12. The testing progress of backup protection performance testing.

Moreover, the test cases for backup protection testing need to be processed based on previous cases in primary protection testing. The cases used in the testing of dependability checking can be adopted directly here, since some nondependable operations (e.g., nontripping signals) in the required time interval are regarded as the failure of primary protection. Inversely, the failures of dc CB operations will be tested with those dependable cases, which are mainly induced by the dc CB's own capabilities and features. Thus, when the failure of primary protection and the failure of dc CB operation are identified, the backup protection functions will be initiated to choose one of the backup options of fault interruption to execute suitably. These two types of failures and their derived rules can be seen in Figure 13. Based on the obtained cases, similar performance analysis of related backup protection functions can be undertaken accordingly.

Figure 13. The evolution from primary protection to backup protection testing.

# Suggestions on Technical Guidelines for dc Protection Testing

### **Definitions of the Test Environment and Scenarios**

The critical requirements and testing parameters of the test environment and fault scenarios vary as the target MTdc grid under study and applied protection algorithms are changed. In case a reduction of the number of test scenarios is needed from several tens of thousands of scenarios [Figure 9(b)] to a reasonable number, it is proposed that test scenarios could be defined considering the limitations of the protection algorithms. For example, when an algorithm is intrinsically limited with respect to the fault resistance, the fault scenarios are determined with more focus on this parameter.

If more practical parameters are considered in the test environment, some standard or proposed models can be improved and adapted to the actual grid under study, with consideration of

- the types of transmission lines, including cable, overhead, and hybrid lines

- the length, parameters (resistance, inductance, and capacitance), and structure of transmission lines

- more fault types and resistances (e.g., a self-clearing fault in the case of OHLs and faults involving metallic return wire in bipolar HVdc grids with metallic return)

- more MMC converter station structures, including monopolar and bipolar

- the converter station earthing, including earthed (earth return or metallic return) and unearthed systems, and earthing method

- more converter topology, including two-level and MMC (FB, HB, and so on)

- the dc-side capacitance

- the control methods and control modes of the converters (PV, PQ, and so on)

- more types of dc CBs and other switchgears

- HVdc grid ratings such as voltage, current, and transferred power

- different ac-side equivalent systems.

With respect to fault scenarios, in addition to those parameters mentioned in the "Test Procedures for MTdc Grid Protection" section (i.e., fault resistance, fault location, dc-side inductance, and converter blocking instant), the measurement accuracy, sampling rate, and noise level on the voltage and current can be considered as well.

## **System-Level Assessment of dc Protection**

After a test of different protection algorithms is carried out, the performance of the algorithms can be analyzed. The algorithms show different performances in terms of different requirements. Therefore, it is necessary to classify the performance of the protection algorithms by considering each requirement or criterion. Here, the performance obtained by performed tests in the "Test Procedures for MTdc Grid Protection" section can be classified into low, medium, and high performance classes for all protection algorithms based on the values of the corresponding qualification criteria.

To determine the range of qualification criterion values of these classes for each requirement, the computed qualification criteria of each requirement for all protection algorithms are sorted in decreasing order. Then, these qualification criteria (of a particular requirement) and their corresponding algorithms are divided into three groups with equal (in the case of an odd number of algorithms) or almost equal (in the case of an even number of algorithms) members: groups 1, 2, and 3. An example with the consideration of nine algorithms and speed criteria is given in Table 7.

**Table 7** An example of the determination of performance classes based on speed.

| GROUPS  | ALGORITHM   | PCLASSES.SPEED (%) | CLASSES | RANGE (%)<br>(AVERAGE METHOD) | RANGE (%) (MIN<br>AND MAX METHOD) |

|---------|-------------|--------------------|---------|-------------------------------|-----------------------------------|

| Group 1 | Algorithm 5 | 99                 | High    | ≥ 97.66                       | ≥ 96                              |

|         | Algorithm 3 | 98                 |         |                               |                                   |

|         | Algorithm 4 | 96                 |         |                               |                                   |

| Group 2 | Algorithm 1 | 94                 | Medium  | 91.66- 97.66                  | 89-96                             |

|         | Algorithm 6 | 92                 |         |                               |                                   |

|         | Algorithm 8 | 89                 |         |                               |                                   |

| Group 3 | Algorithm 2 | 85                 | Low     | < 91.66                       | < 89                              |

|         | Algorithm 9 | 83                 |         |                               |                                   |

|         | Algorithm 7 | 80                 |         |                               |                                   |

The range of each performance class is defined by taking into account an average value of these three groups in the following way:

- high performance ≥ average of group 1

- average of group 2 ≤ medium performance < average of group 1</li>

- low performance < average of the group 2.</li>

It is also possible to use the minimum and maximum values of the groups instead of the average values:

- high performance ≥ minimum of group 1

- minimum of group  $2 \le \text{medium performance} < \text{minimum of group } 1$

- low performance < minimum of the group 2.

This classification method can be applied to all of the requirements in Table 1. Then, the performances of the algorithms can be compared considering each requirement. It should be

noted that the range of classes of each requirement may be different from other requirements and may also differ for different IEDs. Because the test procedures and assessment methods are designed in a systematic way, the efficiency for the full performance assessment of IEDs is higher and more difficult to quantify than the simple testing methods used in [32]–[33][34][35][36][37] for only single protection algorithms. By comparing them to single protection algorithm testing with lesser performance requirements, the computation efforts of the proposed testing method will be made to systematically consider all of the requirement criteria, i.e., speed, sensitivity, selectivity, security, dependability, seamless, and robustness, which are necessary for the industrial application and the certification of protection IEDs.

Compared to IEEE and IEC standards for ac protection testing, the proposed methods are more advanced and applicable for dc protection IEDs. The extra system-level assessment method proposed in the article can help evaluate the different kinds of dc protection algorithms implemented in the protection IEDs. It should be noted that the efficiency of the proposed method can be quantified by comparing the test results and practical results recorded in practical MT HVdc grids. However, performing such a study needs a reasonable amount of practical information about the performance of IEDs and the protection algorithms, which implies longer time exploitation and operation of MT HVdc grids. At this moment, such information is not available because there are a few newly commissioned practical MT HVdc grids and even fewer protection IEDs equipped with different protection algorithms.

#### Conclusion

This article first identifies challenges for system-level testing of MTdc grid protection, and it exploits the already available standard procedures for ac protection system testing to develop MTdc grid protection testing procedures. It also applies the knowledge of dc protection testing and makes recommendations based on the developed procedures and guidelines for both primary and backup dc protection functions. The specific performance criteria are designed, based on multicase testing and statistical analysis, with consideration of the related critical testing parameters for the functional requirements of dc protection. Suggestions for the dc protection testing environment and fault scenarios and the assessment methods of the algorithms' performances are provided, which will be important for the future standardization of MTdc grid development and related protection testing.

# Acknowledgments

This work received funding from the European Commission under project 691714–PROMOTioN (Progress on Meshed High-Voltage dc Offshore Transmission Networks) through the Horizon 2020 program and was supported by the EUDP project Voltage Control and Protection for a Grid Toward 100% Power Electronics and Cable Network (EUDP17-I: 12561).

#### References

**1.**H. Li and Z. Chen, "Overview of different wind generator systems and their comparisons", *IET Renew. Power Gener.*, vol. 2, no. 2, pp. 123-138, 2008.

- **2.**Y. Wang and R. Marquardt, "Performance of a new fast switching DC-Breaker for meshed HVDC-Grids", *Proc. 7th European Conf. Power Electronics and Applications (EPE'15 ECCE-Europe)*, pp. 1-9, 2015.

- **3.**National Grid and ABB celebrate 25th anniversary of HVDC in New England, Nov. 2015, [online] Available: https://www.tdworld.com/overhead-transmission/article/20965931/national-grid-and-abb-celebrate-25th-anniversary-of-hvdc-in-new-england.

- **4.**G. Tang, Z. He, H. Pang, X. Huang and X. Zhang, "Basic topology and key devices of the five-terminal DC grid", *CSEE J. Power Energy Syst.*, vol. 1, no. 2, pp. 22-35, 2015. **5.**G. Li, J. Liang, S. Balasubramaniam, T. Joseph, C. Ugalde-Loo and K. Jose, "Frontiers of DC circuit breakers in HVDC and MVDC systems", *Proc. IEEE Conf. Energy Internet and Energy System Integration*, pp. 1-6, 2017.

- **6.**S. Liu, Z. Liu, J. Chavez and M. Popov, "Mechanical DC circuit breaker model for real time simulations", *Int. J. Elect. Power Energy Syst.*, vol. 107, pp. 110-119, May 2019.

- **7.**L. Liu, M. Popov, M. van der Meijden and V. Terzija, "Optimized control of LCL-VSC converter with refined s-parameter", *IEEE Trans. Power Del.*, vol. 32, no. 4, pp. 2101-2110, Aug. 2017.

- **8.**M. Wang et al., "A review on AC and DC protection equipment and technologies: Towards multivendor solution", *Proc. Cigre Winnipeg 2017 Collog.*, pp. 1-11, 2017.

- **9.** *Guidelines for the preparation of 'connection agreements' or 'grid codes' for multi-terminal DC schemes and DC grids*, 2016, [online] Available: https://e-cigre.org/publication/657-guidelines-for-the-preparation-of-connection-agreements-orgrid-codes-for-multi-terminal-schemes-and-dc-grids.

- **10.**R. Torres-Olguin and H. Hoidalen, "Inverse time overcurrent protection scheme for fault location in multi-terminal HVDC", *Proc. IEEE Eindhoven PowerTech*, pp. 1-6, 2015.

- **11.**S. Pirooz Azad and D. Van Hertem, "A fast local bus current-based primary relaying algorithm for HVDC grids", *IEEE Trans. Power Del.*, vol. 32, no. 1, pp. 193-202, 2016.

- **12.**C. Kim, V. K. Sood, G. Jang, S. Lim and S. Lee, "Fault behavior and protection of HVDC system" in HVDC Transmission: Power Conversion Applications in Power Systems, Hoboken, NJ:Wiley, pp. 257-277, 2010.

- **13.**J. Descloux, B. Raison and J.-B. Curis, "Protection algorithm based on differential voltage measurement for MTDC grids", *Proc. IET Int. Conf. Developments Power System Protection (DPSP 2014)*, pp. 1-5, 2014.

- **14.**Y. Zhang, N. Tai and B. Xu, "Fault analysis and traveling-wave protection scheme for bipolar HVDC lines", *IEEE Trans. Power Del.*, vol. 27, no. 3, pp. 1583-1591, 2012.

- **15.**N. Johannesson, S. Norrga and C. Wikstrom, "Selective wave-front based protection algorithm for MTDC systems", *Proc. IET 13th Int. Conf. Development Power System Protection (DPSP)*, pp. 1-6, 2016.