# REACH THROUGH HOT CARRIER SILICON ELECTROLUMINESCENCE IN STANDARD CMOS

by

**Petrus Johannes Venter**

Submitted in partial fulfilment of the requirements for the degree

Philosophiae Doctor (Electronic Engineering)

in the

Department of Electrical, Electronic and Computer Engineering Faculty of Engineering, Built Environment and Information Technology UNIVERSITY OF PRETORIA

May 2013

# REACH THROUGH HOT CARRIER SILICON ELECTROLUMINESCENCE IN STANDARD CMOS

by

#### **Petrus Johannes Venter**

| Promoter(s): | Prof Monuko du Plessis and Prof Enrico Bellotti                         |

|--------------|-------------------------------------------------------------------------|

| Department:  | Electrical, Electronic and Computer Engineering                         |

| University:  | University of Pretoria                                                  |

| Degree:      | Philosophiae Doctor (Electronic Engineering)                            |

| Keywords:    | silicon, hot carrier, electroluminescence, avalanche, breakdown, integ- |

|              | rated circuit, photonics, microdisplay, reach through, CMOS             |

The elusive art of integrating an efficient light source into standard CMOS ICs would unlock exciting possibilities for inexpensive integrated photonics. By nature, silicon is ill-suited as an optically emitting material. Electroluminescence based on hot carrier emission offers an integration capability where light sources can coexist and interact with other circuitry on chip without altering the process. Hot carrier electroluminescence in reverse biased silicon pn-junctions usually occurs under avalanche breakdown conditions with high associated electric fields. The available junctions and doping concentrations in a standard CMOS process are limited by the process implant steps designed to cater for transistors. A circuit designer is confronted by the restrictive ability to define geometries only through mask definitions allowed by the foundry with no means to control the operating voltage of hot carrier silicon light sources. Since avalanche occurs at high voltages, hot carrier light sources therefore operate at high voltages, usually to the detriment of interaction with other circuits on-chip. The work in this thesis starts with investigating and developing a method for integrating light sources with other digital circuitry in order to prove the integration possibilities afforded by an integrated light source. The resulting work manifests in the creation of a  $64 \times 8$  pixel microdisplay designed with state of the art light sources which operate at the process defined minimum breakdown voltage. A technique is then developed whereby the breakdown voltage of light sources can be lowered through the use of electric field reach through between two highly doped regions available in practically all standard CMOS processes. By terminating the electric field existing in a reverse biased junction prematurely, the operating voltage of the light source can be reduced and tailored by the circuit designer using geometrical design input while requiring no changes to the process. An additional improvement beyond the state of the art is presented where field oxide channels are formed at the Si/SiO<sub>2</sub> interface which provides more predictable and reliable electrical behaviour while improving the light extraction efficiency. These improved reach through light sources with field oxide channels are subsequently used in a  $128 \times 96$  pixel microdisplay. The scope of integration is increased with additional functions and video capability added on-chip. The display operates at a lower voltage and improved efficiency. A luminance analysis and comparison between the two microdisplays implemented in this work show that although the photopic output power is improved substantially using the reach through light sources, the luminance remains sensitive to the emission area and nature of the radiation pattern of the light sources used in the microdisplay systems. This has a substantial impact on microdisplay performance. Integrated silicon light sources indeed offer exciting possibilities, and while difficult by nature, it is possible by design.

# DEURGESPERDE WARMDRAER SILIKON ELEKTROLUMINESSENSIE IN STANDAARD CMOS

deur

#### **Petrus Johannes Venter**

| Promotor(s):   | Prof Monuko du Plessis en Prof Enrico Bellotti                     |

|----------------|--------------------------------------------------------------------|

| Departement:   | Elektriese, Elektroniese en Rekenaar-Ingenieurswese                |

| Universiteit:  | Universiteit van Pretoria                                          |

| Graad:         | Philosophiae Doctor (Elektroniese Ingenieurswese)                  |

| Sleutelwoorde: | silikon, warmdraer, elektroluminessensie, lawine, deurbraak, geïn- |

|                | tegreerde stroombaan, fotonika, mikrovertoon, deursper, CMOS       |

Die ontduikende vermoë rakende die integrasie van 'n effektiewe ligbron in 'n standaard CMOS geïntegreerde stroombaan skep opwindende moontlikhede vir lae koste geïntegreerde fotonika. Silikon is weens sy aard nie die ligskeppende materiaal van keuse nie. Straling wat berus op elektries-gedrewe warmdraer ligbronne bied egter die vermoë om ligbronne wat saamwerk met ander stroombane op 'n vlokkie te vestig sonder om die proses te verander. Warmdraer straling in trugespande silikon pnvoegvlakke vind gewoonlik plaas onder lawine-deurbraak waar hoë elektriese velde ter sprake is. Die voegvlakke en doteerkonsentrasies beskikbaar in 'n standaard CMOS proses word beperk deur die implanteringstappe eie aan die proses en is gemik op transistorimplementering. 'n Stroombaanontwerper beskik slegs oor die vermoë om geometriese maskeruitlegte te definieer. Dit ontneem die ontwerper die moontlikheid om deurbraakspanningsvlakke van silikon ligbronvoegvlakke te wysig deur prosesstappe. Omdat lawine-deurbraak gewoonlik teen hoë spannings plaasvind skep dit ongunstige omstandighede vir ander stroombaankomponente om met die ligbronne te skakel. Die werk in hierdie proefskrif ondersoek die moontlikhede en vereistes rondom die integrering van warmdraer ligbronne met ander stroombane om die integrasievermoëns te bepaal. Die resultaat manifesteer in die implementering van 'n  $64 \times 8$ -piksel mikrovertoon wat gebruik maak van die huidige stand van die tegniek ligbronne. Hierdie ligbronne funksioneer teen die minimum deurbraakspannings soos deur die proses gedefinieer. 'n Tegniek word vervolgens ontwikkel waar die deurbraakspanning van die ligbronne verlaag kan word sodra die elektriese veld tussen twee hoog-gedoteerde gebiede, soos beskikbaar in feitlik alle CMOS prosesse, deursper. Deur die elektriese veld in die trugespande sperlaag voortydig te beëindig kan die dryfspanning van die ligbronne bepaald verlaag word deur 'n stroombaanontwerper, deur slegs die geometriese instruksies aan die vervaardiger te wysig. Hierdie benadering verg dus geen verandering aan die proses self nie. Verder word die deurspertegniek uitgebrei deur die veldoksied te omskep in kanaal-tipe strukture wat gevorm word deur die Si/SiO2-intervlak. Hierdie wysiging voorsien die ligbronne met meer voorspelbare en betroubare elektriese eienskappe sowel as 'n verbetering in die ligonttrekkingseffektiwiteit. Vervolgens word die verbeterde ligbronne in deursper-modus met veldoksied kanale in 'n geïntegreerde 128×96-piksel mikrovertoon gebruik. Die vlak van integrasie word aansienlik verhoog met meer funksies, insluitend video vermoë, ingebou op dieselfde mikrovlokkie. Die 128×96-piksel vertoon funksioneer teen 'n laer dryfspanning en verbeterde drywingseffektiwiteit. Luminansie-analise en 'n vergelyking tussen die twee mikrovertone wys dat hoewel die fotopiese drywingseffektiwiteit verbeter is deur van die verbeterde ligbronne gebruik te maak, bly die luminansie sensitief vir die stralingsarea sowel as die ruimtelike hoeke van die betrokke stralingspatrone. Dit het 'n wesenlike impak op die werksverrigting van die mikrovertoon. Geïntegreerde silikon ligbronne bied opwindende moontlikhede en die werklikheid van 'n volledig geïntegreerde bron, hoewel uitdagend, is moontlik deur ontwerp.

# LIST OF ABBREVIATIONS

| ADC   | Analogue to digital converter                       |

|-------|-----------------------------------------------------|

| BEOL  | Back end of line                                    |

| BER   | Bit error rate                                      |

| BTE   | Boltzmann Transport Equation                        |

| CAD   | Computer assisted design                            |

| CE    | Chip enable                                         |

| CEFIM | Carl and Emily Fuchs Institude for Microelectronics |

| CMOS  | Complimentary metal-oxide-semiconductor             |

| CVD   | Chemical vapour deposition                          |

| DAC   | Digital to analogue converter                       |

| DC    | Direct current                                      |

| DI    | Data input                                          |

| DIBL  | Drain-induced barrier lowering                      |

| DRAM  | Dynamic random access memory                        |

| EPE   | External power efficiency                           |

| EQE   | External quantum efficiency                         |

| ESD   | Electrostatic discharge                             |

| FOX   | Field oxide                                         |

| FPGA  | Field programmable gate array                       |

| HBT   | Heterojunction bipolar transistor                   |

| I/O   | Input/Output                                        |

| IC    | Integrated circuit                                  |

| ILD   | Inter-metal layer dielectric                        |

| LCD   | Liquid crystal display                              |

| LCoS  | Liquid crystal on silicon                           |

| LDD   | Lightly doped diffusion                             |

| LED   | Light emitting diode                                |

|       |                                                     |

| LiPo   | Lithium polymer                                     |

|--------|-----------------------------------------------------|

| LOCOS  | Local oxidation of silicon                          |

| MC     | Monte Carlo                                         |

| MCLK   | Master clock                                        |

| MCLR   | Master clear                                        |

| MOS    | Metal-oxide-semiconductor                           |

| MOSFET | Metal-oxide-semiconductor field effect transistor   |

| MPW    | Multi-project wafer                                 |

| MTTF   | Mean time to failure                                |

| MUX    | Multiplexer                                         |

| NCL    | Nitride-clad LOCOS                                  |

| NIR    | Near infrared                                       |

| OLED   | Organic light emitting device                       |

| PBL    | Polysilicon buffered LOCOS                          |

| PERL   | Passive emitter, rear locally-diffused              |

| PICA   | Picosecond imaging circuit analysis                 |

| PMT    | Photon multiplier tube                              |

| PSi    | Porous silicon                                      |

| PSL    | Polysilicon spacer LOCOS                            |

| PWM    | Pulse width modulation                              |

| RF     | Radio frequency                                     |

| RIE    | Reactive ion etch                                   |

| RT     | Reach through                                       |

| RTL    | Register transfer level                             |

| SOI    | Silicon on insulator                                |

| SPICE  | Simulation Program with Integrated Circuit Emphasis |

| SPM    | Serial-to-parallel memory                           |

| STI    | Shallow trench isolation                            |

| SWAMI  | Sidewall masked isolation                           |

| TDDB   | Time dependent dielectric breakdown                 |

| ТМ     | Typical mean                                        |

| TZDB   | Time zero dielectric breakdown                      |

| VGA    | Video graphics adapter                              |

|        |                                                     |

| VHDL | VHSIC hardware description language                            |

|------|----------------------------------------------------------------|

| VIS  | Visible, refers to spectral range covering visible wavelengths |

| VLSI | Very large scale integration                                   |

| WP   | Worst power                                                    |

| WS   | Worst speed                                                    |

|      |                                                                |

# LIST OF SYMBOLS

| $\psi_{bi}$    | Built-in junction potential                                     |

|----------------|-----------------------------------------------------------------|

| $E_g$          | Band gap energy                                                 |

| $E_{\Gamma 1}$ | Energy gap between valence and first conduction band at $k = 0$ |

| $J_n$          | Current density due to electrons                                |

| $J_p$          | Current density due to holes                                    |

| Ε              | Electric field                                                  |

| q              | Magnitude of electron charge                                    |

| ρ              | Charge density                                                  |

| $\mu_{n,p}$    | Electron and hole mobility                                      |

| D              | Diffusion constant                                              |

| $\epsilon_0$   | Vacuum permittivity                                             |

| $K_S$          | Relative permittivity of silicon                                |

| $r_{n,p}$      | Electron and hole recombination rates                           |

| $g_{n,p}$      | Electron and hole generation rates                              |

| Т              | Temperature                                                     |

| $T_e$          | Effective carrier temperature                                   |

| $C_S$          | Velocity of sound                                               |

| $v_d$          | Drift velocity                                                  |

| $\mu_0$        | Low field carrier mobility                                      |

| ħ              | Reduced Planck's constant                                       |

| $m_0$          | Carrer mass in free space                                       |

| $m^*$          | Effective carrier mass                                          |

| F              | Force                                                           |

| $lpha_{n,p}$   | Impact ionisation coefficients for electrons and holes          |

| $M_{n,p}$      | Avalanche multiplication factor for electrons and holes         |

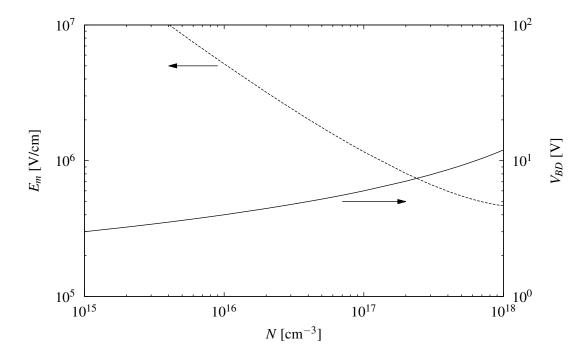

| $V_{BD}$       | Breakdown voltage of <i>pn</i> -junction                        |

| $E_m$          | Maximum electric field strength                                 |

|                |                                                                 |

| W <sub>Dm</sub>   | Maximum depletion region width                            |

|-------------------|-----------------------------------------------------------|

| N                 | Background doping concentration                           |

|                   |                                                           |

| $V_R$             | Reverse-biased voltage applied to <i>pn</i> -junction     |

| $I_s$             | Saturation current in <i>pn</i> -junction                 |

| k                 | Boltzmann's constant                                      |

| $	au_{n,p}$       | Electron and hole carrier lifetimes                       |

| n <sub>i</sub>    | Intrinsic carrier concentration                           |

| $N_{D,A}$         | Donor and acceptor impurity concentration                 |

| $\sigma_{n,p}$    | Electron and hole capture cross section                   |

| V <sub>th</sub>   | Carrier velocity at thermal equilibrium                   |

| $N_t$             | Trap density                                              |

| $E_i$             | Intrinsic Fermi-energy level                              |

| $E_t$             | Trap energy level                                         |

| $J_0$             | Total equilibrium current density                         |

| $W_D$             | Depletion region width                                    |

| $J_{ge}$          | Current density due to carrier generation                 |

| $	au_g$           | Carrier generation lifetime                               |

| $\eta_{eqe}$      | External quantum efficiency                               |

| $\eta_{epe}$      | External power efficiency                                 |

| $E_{ph}$          | Photon energy                                             |

| h                 | Planck's constant                                         |

| С                 | Velocity of light                                         |

| λ                 | Wavelength                                                |

| Popt              | Optical power, usually output power, same as radiant flux |

| $P_e$             | Electric power, usually input power                       |

| $I_e$             | Electrical current, sometimes radiant intensity           |

| Ecrit             | Critical electric field                                   |

| Ψ                 | Potential                                                 |

| x <sub>sep</sub>  | Separation distance between two highly doped regions      |

| V <sub>CY</sub>   | Cylindrical depletion region breakdown voltage            |

| $V_{SP}$          | Spherical depletion region breakdown voltage              |

| $r_j$             | Junction curvature radius                                 |

| n <sub>Si</sub>   | Refractive index of silicon                               |

| n <sub>SiO2</sub> | Refractive index of silicon dioxide                       |

|                   |                                                           |

| $t_{g,ox}$                    | Gate oxide thickness                                      |

|-------------------------------|-----------------------------------------------------------|

| $E_{g,max}$                   | Maximum electric field across the gate oxide              |

| V <sub>sup</sub>              | Supply voltage                                            |

| $\phi$                        | Metal ion activation energy                               |

| $L_{\nu}$                     | Luminance in cd/m <sup>2</sup>                            |

| A                             | Area                                                      |

| Ω                             | Solid angle in steradian or electrical resistance in Ohms |

| $\Phi_v$                      | Luminous flux                                             |

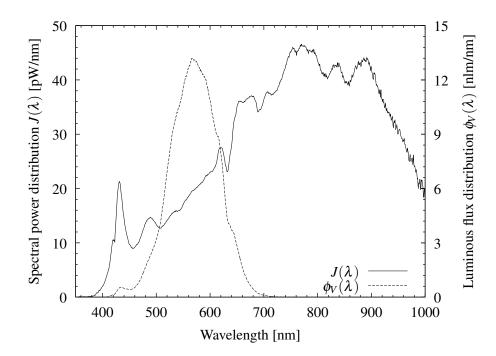

| $J(\lambda)$                  | Spectral power distribution                               |

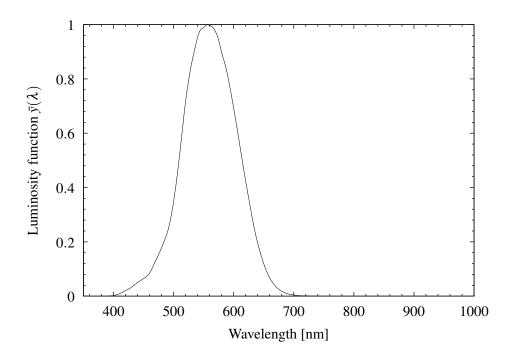

| $ar{y}(oldsymbol{\lambda})$   | Luminosity function                                       |

| $\phi_ u(oldsymbol{\lambda})$ | Spectral distribution of luminous flux                    |

| $I_{v}$                       | Luminous intensity                                        |

| $\mathcal{E}_{Si}$            | Permittivity of silicon                                   |

| κ                             | Surface reaction rate                                     |

| $\Phi_e$                      | Radiant flux, sometimes called optical power              |

| I <sub>e</sub>                | Radiant intensity in context of luminance calculations    |

|                               |                                                           |

## ACKNOWLEDGEMENT

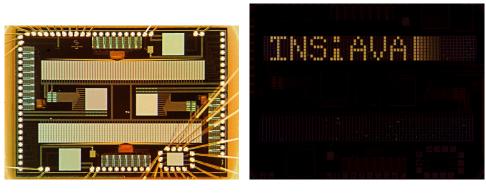

The work described in this thesis has not happened in isolation. INSiAVA (Pty) Ltd is a company aiming at commercialising silicon light emission technologies. The majority of this work has been funded by INSiAVA (Pty) Ltd in agreement with the University of Pretoria. The Carl and Emily Fuchs Institute for Microelectronics (CEFIM) houses a group of talented researchers working on silicon light emission. I am indebted to all of my colleagues, especially Marius Goosen and Christo Janse van Rensburg, who have been the ears and sounding board in many discussions pertaining to this work, and the rest of the team, Dr Pieter Rademeyer, Niklaas Faure, Antonie Alberts, Paula Grove and Vianca Mocke, with whom it is a pleasure to work. A thanks to Dr Trudi Joubert who has been the chief designer in most of the logic associated with the 128×96 pixel microdisplay, which helped me in proving the integration capabilities of my designs. I would like to extend my gratitude to Ms Tilla Nel who keeps the CEFIM heartbeat ticking and who always has ears to listen and to the rest of my CEFIM colleagues, Professor Saurabh Sinha and Johan Schoeman, who help in creating the world class characteristic of the CEFIM group.

I am also thankful for my co-promotor, Professor Enrico Bellotti, who has introduced me to the field of quantum mechanics and numerical simulation of semiconductor devices and his guidance on a whole range of topics during the number of visits I have made to Boston and his visits to South Africa.

The guidance and mentorship of Gerrie Mostert have been extremely valuable, both in my professional and personal life. His experience in the intersection of science and business, with his insight and knowledge in intellectual property strategy, has given a breadth to my understanding of our world which I dearly appreciate.

Finally I would like to thank Professor Monuko du Plessis, who has been a role model for me since the undergraduate ELK220 class in 2002. The combination of his methodical approach to science, his focus, creativity and intuition has led to some of the most interesting inventions and insights. In addition, he has the ability to impart his knowledge of the complex and difficult concepts in semiconductor science in such a way that a layman would understand. Fortunately, I was able to draw extensively on this ability of his. His guidance in this work has been invaluable. To my loving wife and children who simultaneously distracted and supported me in the most wonderful ways, my family and

ana

in memory of my brother

# **TABLE OF CONTENTS**

Introduction

**CHAPTER 1**

## 1.1 1.2 Problem statement 1.3 1.4 Hypothesis and research questions 1.4.1 1.5 Research questions 1.6 Research methodology 1.7 1.8 1.9 1.10 List of publications 1.10.2 Peer reviewed international conference contributions . . . . . . . . . . . . . . **CHAPTER 2** Literature review of related work 2.1 Electroluminescence in semiconductors

1

1

2

3

4

4

4

5

5

6

7

9

9

9

10

11

11

|     | 2.1.1  | Light emission from indirect band gap materials        | 11 |

|-----|--------|--------------------------------------------------------|----|

|     | 2.1.2  | Summary                                                | 14 |

| 2.2 | Hot ca | rrier photon emission from indirect band gap materials | 15 |

|     | 2.2.1  | First observation                                      | 15 |

|     | 2.2.2  | Radiative mechanism and modelling                      | 15 |

|     | 2.2.3  | Intrinsic bandwidth                                    | 16 |

|     | 2.2.4  | Reliability                                            | 17 |

|     | 2.2.5  | Improvement techniques                                 | 17 |

| CMOS    | integration of silicon light sources                                                                                                                                                                                                                                                            | 18                                                                                                                                                           |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.3.1   | Characterisation applications                                                                                                                                                                                                                                                                   | 18                                                                                                                                                           |

| 2.3.2   | Integration of silicon light emitters                                                                                                                                                                                                                                                           | 19                                                                                                                                                           |

| 2.3.3   | Optical communications                                                                                                                                                                                                                                                                          | 19                                                                                                                                                           |

| 2.3.4   | Integrated microdisplays                                                                                                                                                                                                                                                                        | 20                                                                                                                                                           |

| Conclu  | ision                                                                                                                                                                                                                                                                                           | 20                                                                                                                                                           |

| TER 3   | Theory on device operation                                                                                                                                                                                                                                                                      | 22                                                                                                                                                           |

| Carrier | transport                                                                                                                                                                                                                                                                                       | 22                                                                                                                                                           |

| 3.1.1   | Boltzmann Transport Equation                                                                                                                                                                                                                                                                    | 22                                                                                                                                                           |

| 3.1.2   | Low field transport                                                                                                                                                                                                                                                                             | 23                                                                                                                                                           |

| 3.1.3   | High field transport                                                                                                                                                                                                                                                                            | 24                                                                                                                                                           |

| 3.1.4   | Full band approach                                                                                                                                                                                                                                                                              | 24                                                                                                                                                           |

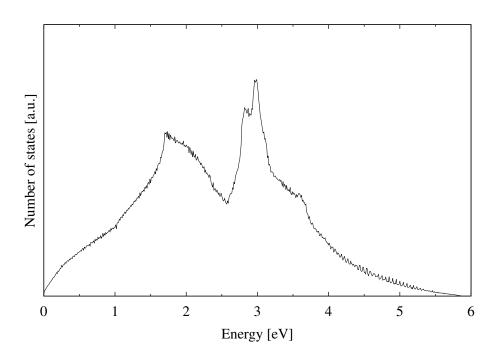

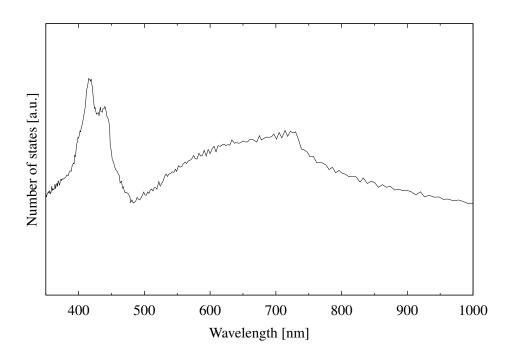

| 3.1.5   | Density of states                                                                                                                                                                                                                                                                               | 25                                                                                                                                                           |

| Transp  | ort in reverse-biased <i>pn</i> -junctions                                                                                                                                                                                                                                                      | 26                                                                                                                                                           |

| 3.2.1   | Avalanche multiplication                                                                                                                                                                                                                                                                        | 26                                                                                                                                                           |

| 3.2.2   | Band-to-band tunnelling and Zener-breakdown                                                                                                                                                                                                                                                     | 28                                                                                                                                                           |

| 3.2.3   | Minority carrier drift current in reverse-biased <i>pn</i> -junctions                                                                                                                                                                                                                           | 29                                                                                                                                                           |

| 3.2.4   | Generation and recombination                                                                                                                                                                                                                                                                    | 29                                                                                                                                                           |

| Hot ca  | rrier luminescence                                                                                                                                                                                                                                                                              | 30                                                                                                                                                           |

| 3.3.1   | Establishing a high electric field                                                                                                                                                                                                                                                              | 30                                                                                                                                                           |

| 3.3.2   | Establishing transport                                                                                                                                                                                                                                                                          | 30                                                                                                                                                           |

| 3.3.3   | Efficiency calculations                                                                                                                                                                                                                                                                         | 31                                                                                                                                                           |

| Propos  | ed technique for electric field reach through                                                                                                                                                                                                                                                   | 32                                                                                                                                                           |

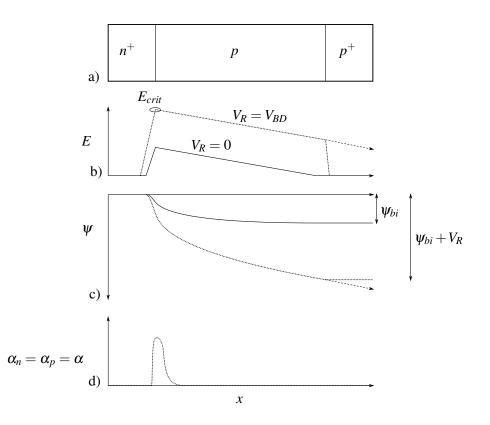

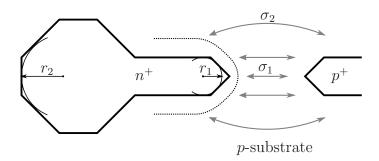

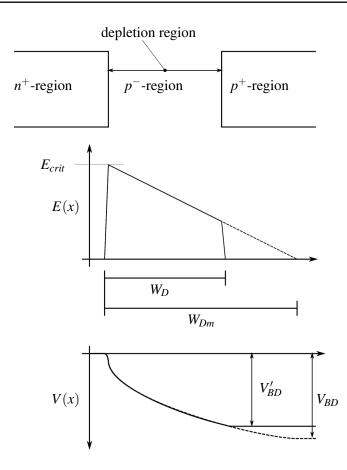

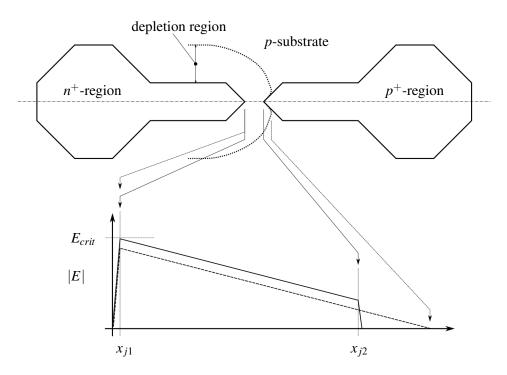

| 3.4.1   | Electric field profile in reach through                                                                                                                                                                                                                                                         | 32                                                                                                                                                           |

| 3.4.2   | Reduced potential integral                                                                                                                                                                                                                                                                      | 34                                                                                                                                                           |

| 3.4.3   | Improving light extraction efficiency                                                                                                                                                                                                                                                           | 35                                                                                                                                                           |

| Conclu  | sion                                                                                                                                                                                                                                                                                            | 35                                                                                                                                                           |

| TER 4   | A 64 x 8 pixel microdisplay in standard CMOS                                                                                                                                                                                                                                                    | 36                                                                                                                                                           |

| Introdu | ction                                                                                                                                                                                                                                                                                           | 36                                                                                                                                                           |

| 4.1.1   | Target CMOS technology and generalisation                                                                                                                                                                                                                                                       | 36                                                                                                                                                           |

| 4.1.2   | Light emitting point sources in standard CMOS                                                                                                                                                                                                                                                   | 37                                                                                                                                                           |

| 4.1.3   | CMOS integration of point sources                                                                                                                                                                                                                                                               | 37                                                                                                                                                           |

|         | 2.3.1<br>2.3.2<br>2.3.3<br>2.3.4<br>Conclu<br><b>ER 3</b><br>Carrier<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>Transp<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>Hot ca<br>3.3.1<br>3.3.2<br>3.3.3<br>Propos<br>3.4.1<br>3.4.2<br>3.4.3<br>Conclu<br><b>ER 4</b><br>Introdu<br>4.1.1<br>4.1.2 | 2.3.2       Integration of silicon light emitters         2.3.3       Optical communications         2.3.4       Integrated microdisplays         Conclusion |

|       | 4.1.4   | CMOS microdisplay based on point sources        | 37 |

|-------|---------|-------------------------------------------------|----|

| 4.2   | Target  | CMOS technology and generalisation              | 37 |

|       | 4.2.1   | Definition of standard CMOS                     | 38 |

|       | 4.2.2   | Target technology for this research             | 38 |

| 4.3   | Light e | mitting point sources in standard CMOS          | 39 |

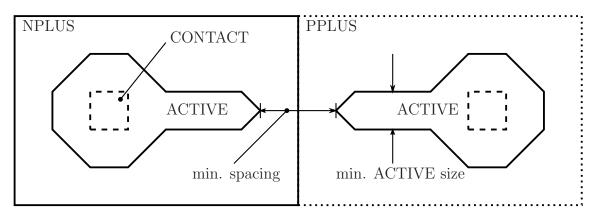

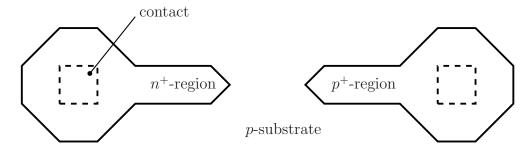

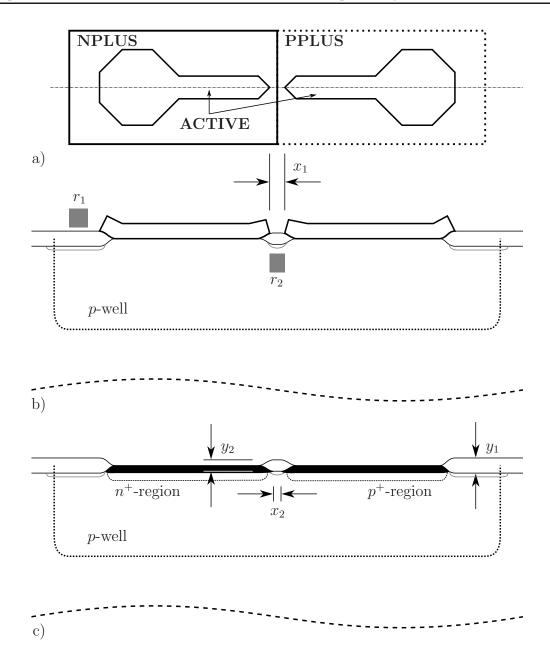

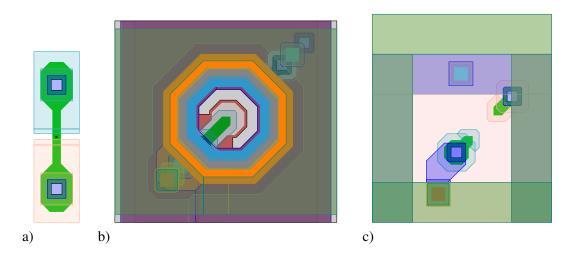

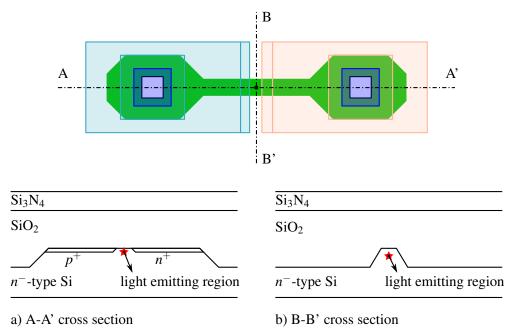

|       | 4.3.1   | Point source design                             | 39 |

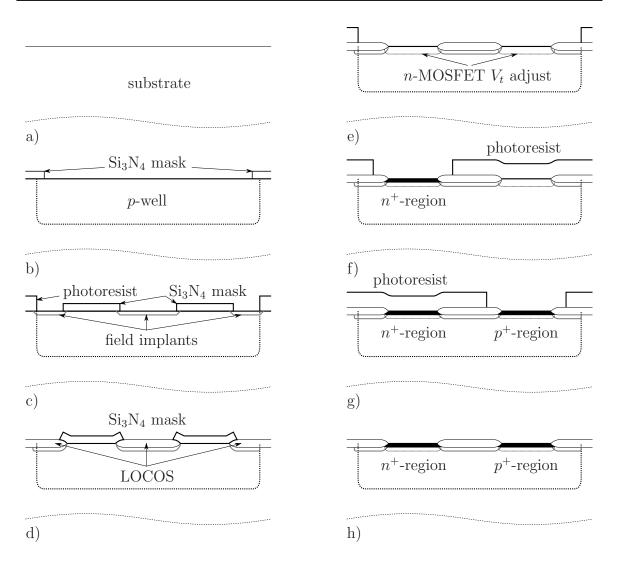

|       | 4.3.2   | Processing steps for creating point sources     | 41 |

|       | 4.3.3   | Breakdown localisation                          | 42 |

|       | 4.3.4   | Optical path for light emission                 | 44 |

|       | 4.3.5   | Light directing structures                      | 47 |

|       | 4.3.6   | Arraying of point sources                       | 48 |

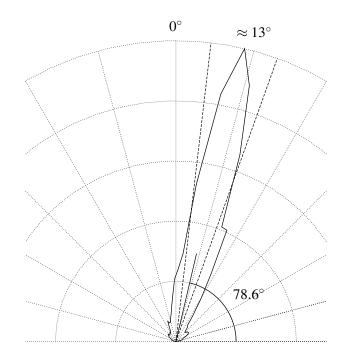

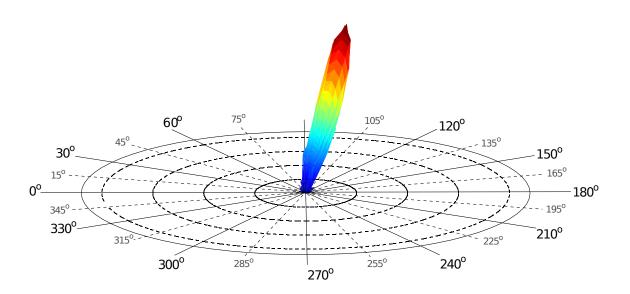

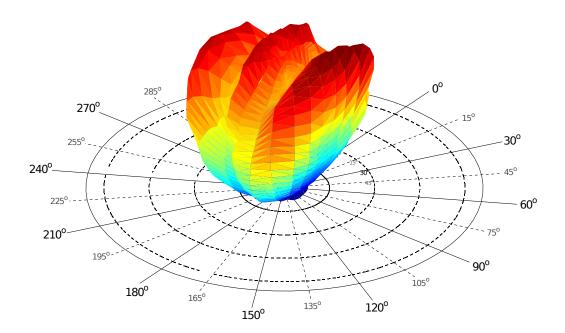

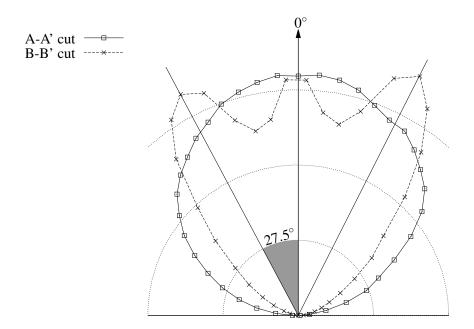

|       | 4.3.7   | Radiation pattern                               | 48 |

| 4.4   | CMOS    | integration of point sources                    | 49 |

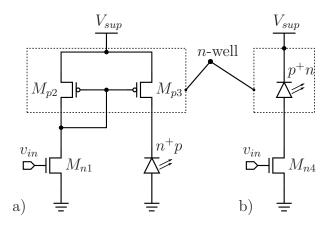

|       | 4.4.1   | Well structure and available diodes             | 50 |

|       | 4.4.2   | Limitations on operating voltage of MOS devices | 50 |

|       | 4.4.3   | High voltage integration                        | 52 |

|       | 4.4.4   | Current densities and electromigration of metal | 54 |

|       | 4.4.5   | Series resistance                               | 55 |

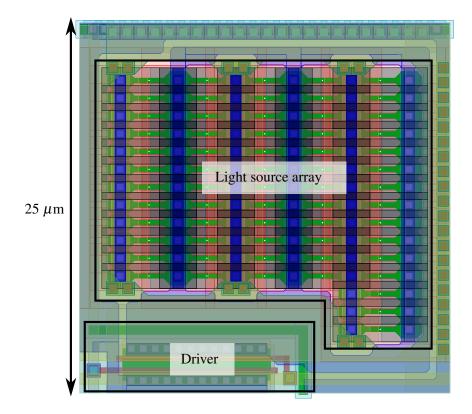

| 4.5   | CMOS    | microdisplay based on point sources             | 56 |

|       | 4.5.1   | Point source characteristics                    | 56 |

|       | 4.5.2   | Pixel design                                    | 57 |

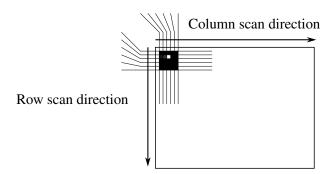

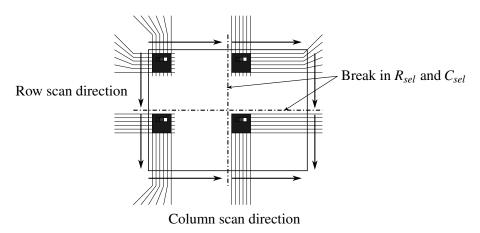

|       | 4.5.3   | Scanning architecture                           | 60 |

|       | 4.5.4   | Controller design                               | 62 |

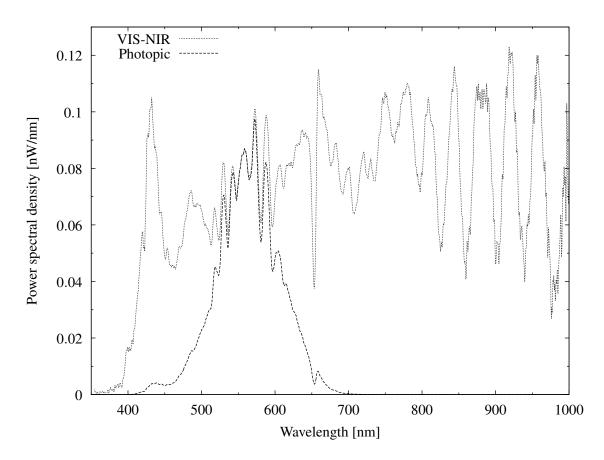

|       | 4.5.5   | Spectral characteristics                        | 63 |

|       | 4.5.6   | Radiation pattern                               | 63 |

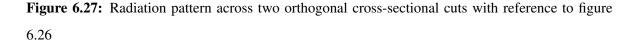

|       | 4.5.7   | Luminance                                       | 64 |

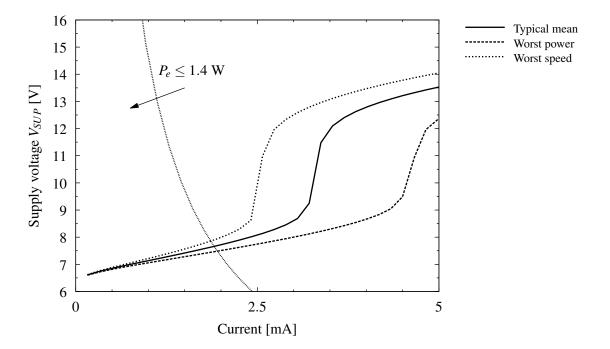

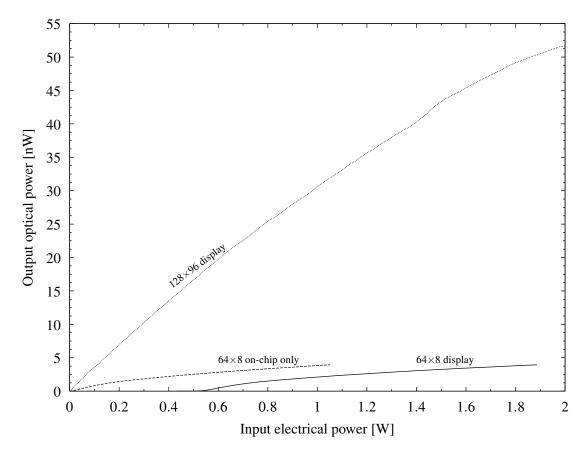

|       | 4.5.8   | Electrical characteristics                      | 66 |

| 4.6   | Conclu  | sion                                            | 68 |

| СНАРТ | ER 5    | Improved light sources in standard CMOS         | 70 |

| 5.1   | Approa  | ach                                             | 71 |

|       | 5.1.1   | Breakdown voltage                               | 71 |

|       | 5.1.2   | Proposed approach                               | 72 |

|       | 5.1.3   | Conceptual CMOS implementation                                  | 73  |

|-------|---------|-----------------------------------------------------------------|-----|

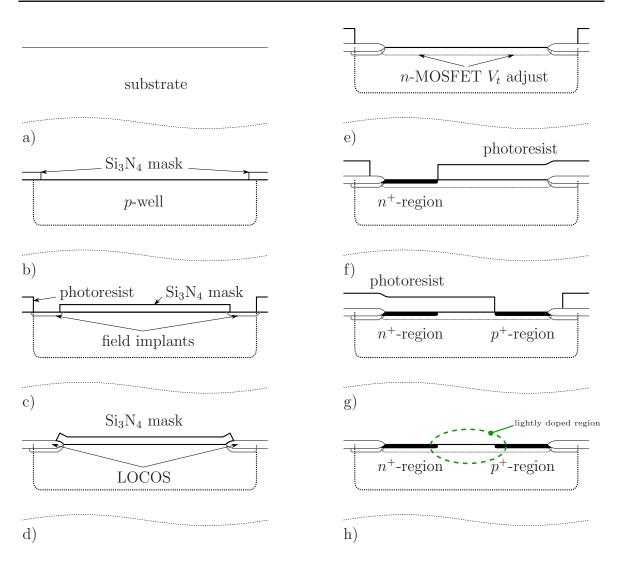

| 5.2   | Process | sing considerations                                             | 73  |

|       | 5.2.1   | Scaling theory for CMOS and device density                      | 73  |

|       | 5.2.2   | Oxidation of silicon                                            | 74  |

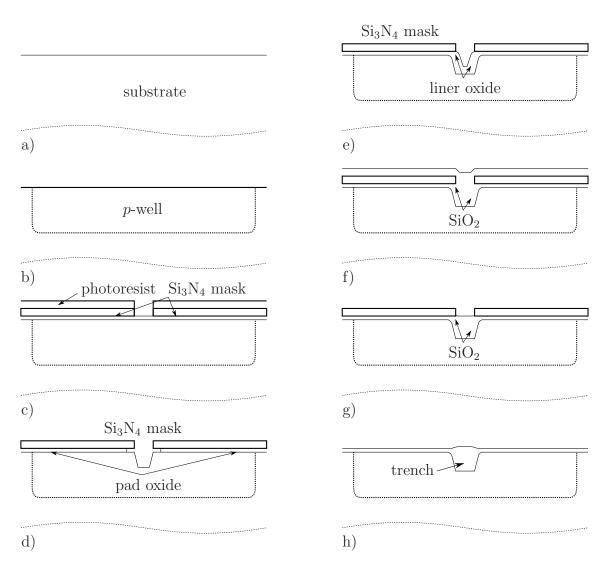

|       | 5.2.3   | LOCOS and field oxide                                           | 75  |

|       | 5.2.4   | Shallow trench isolation (STI)                                  | 78  |

|       | 5.2.5   | Processing limits                                               | 80  |

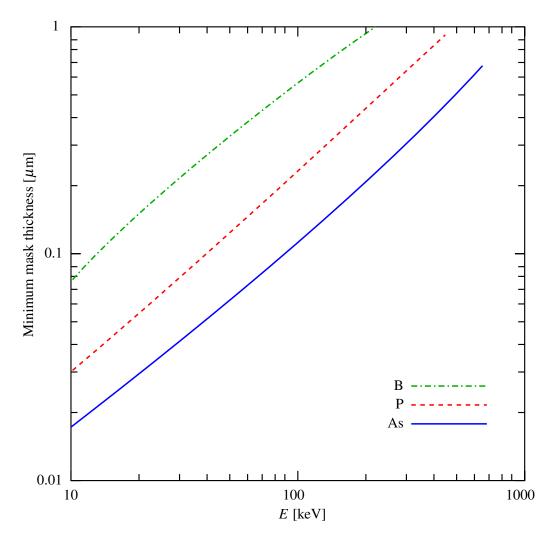

|       | 5.2.6   | Ion implantation                                                | 81  |

| 5.3   | Referen | nce device and experimental approach                            | 84  |

|       | 5.3.1   | Reference device for individual point sources                   | 85  |

| 5.4   | Design  | for electric field reach through in point sources               | 85  |

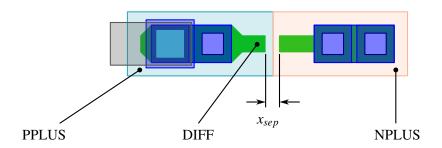

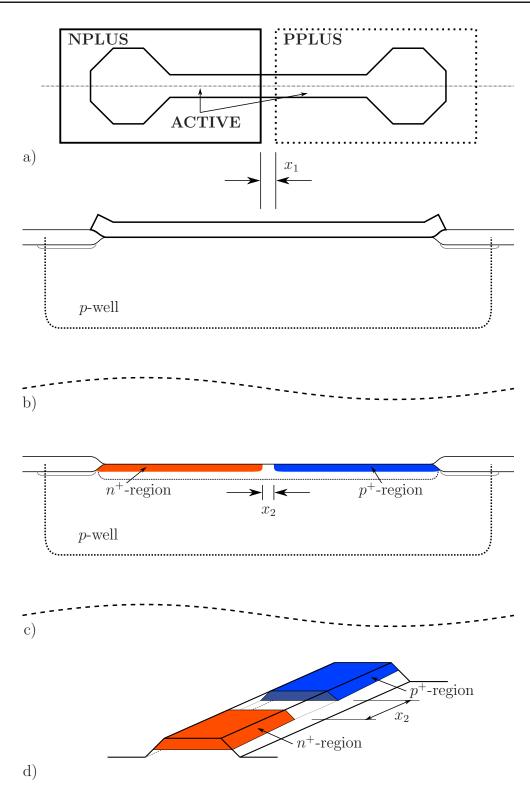

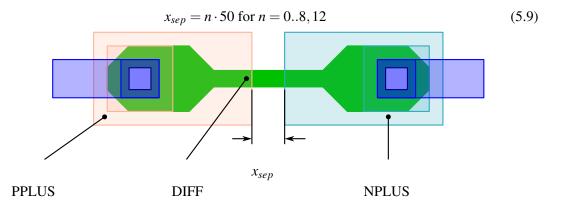

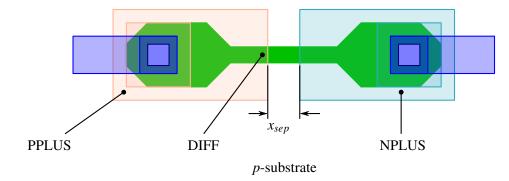

|       | 5.4.1   | Geometrical adaptations of point sources                        | 85  |

|       | 5.4.2   | Localisation due to reduced barrier potential                   | 85  |

|       | 5.4.3   | Layout of a point source using drawn layers in a CMOS process   | 86  |

| 5.5   | Results | s for point sources in reach through                            | 87  |

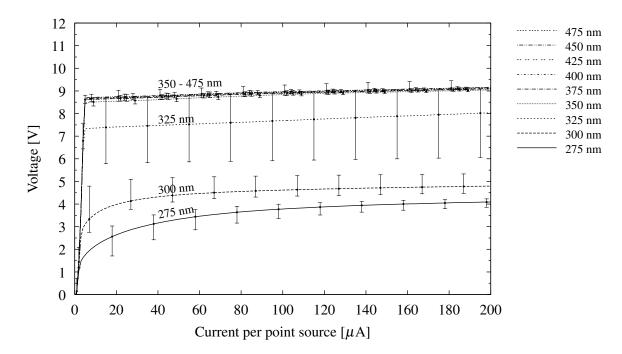

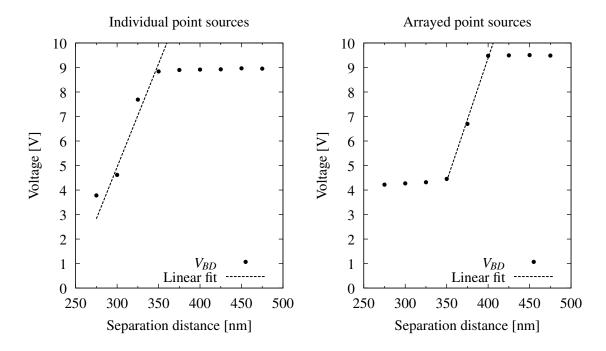

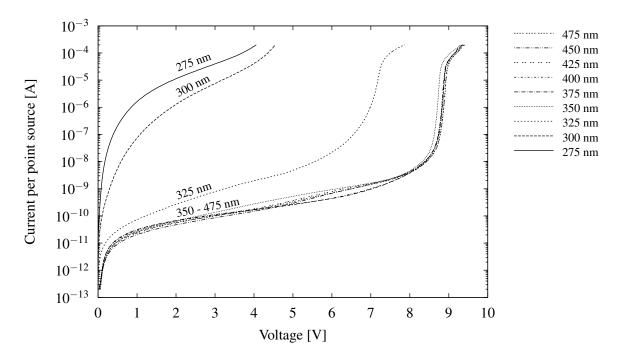

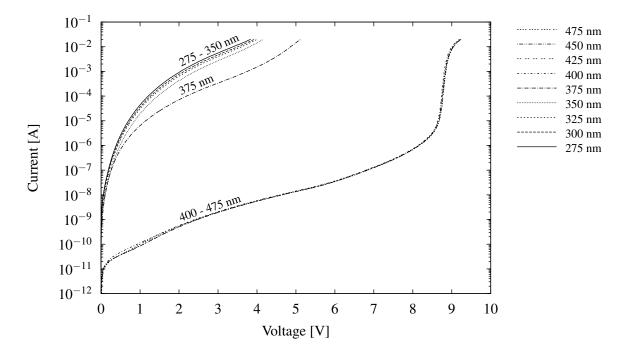

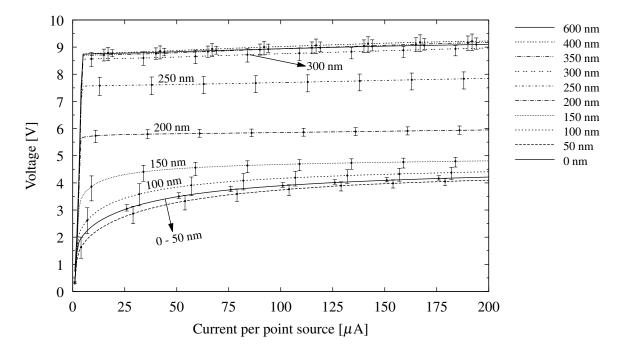

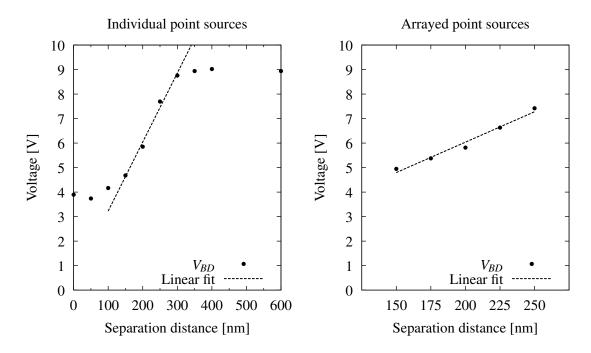

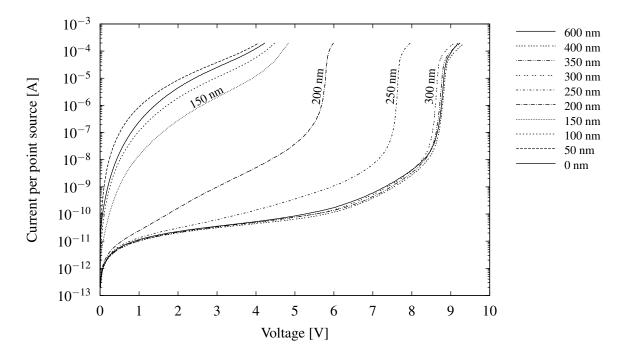

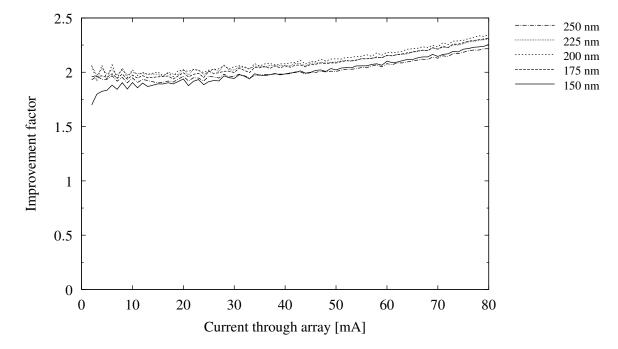

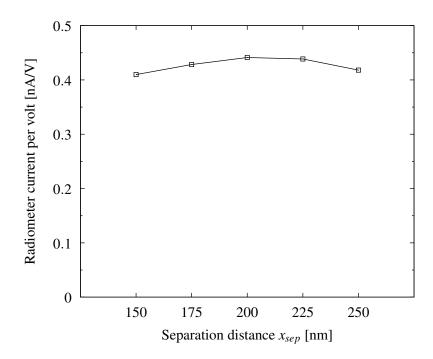

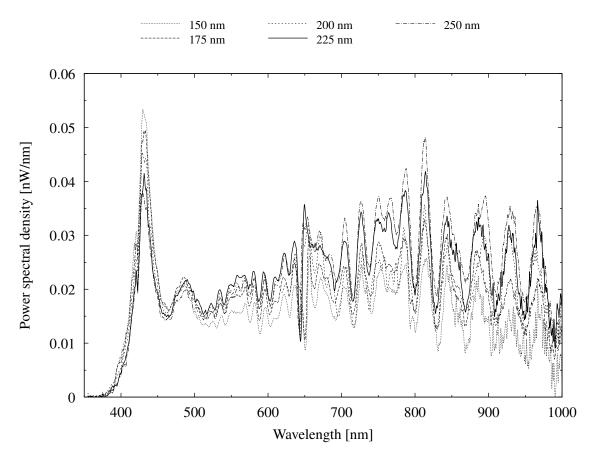

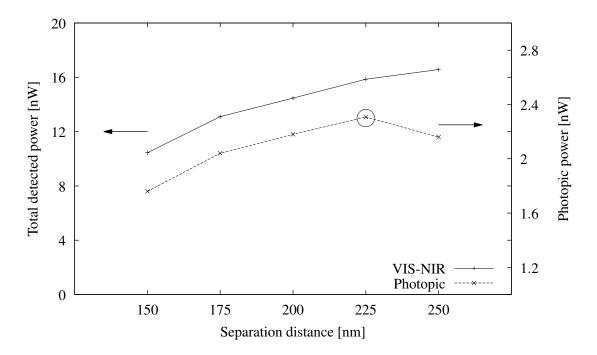

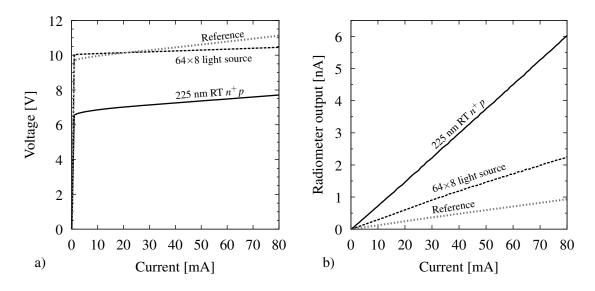

|       | 5.5.1   | Electrical characteristics                                      | 88  |

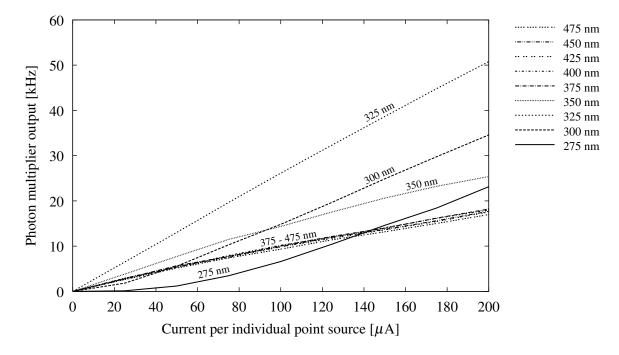

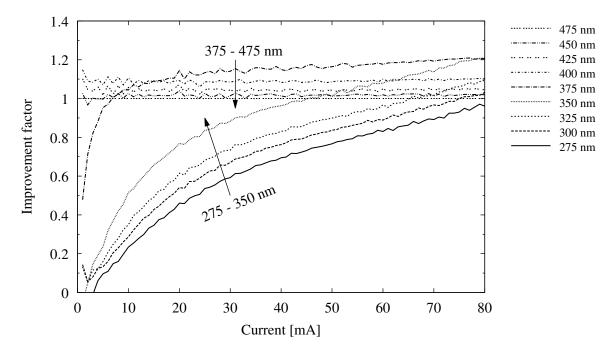

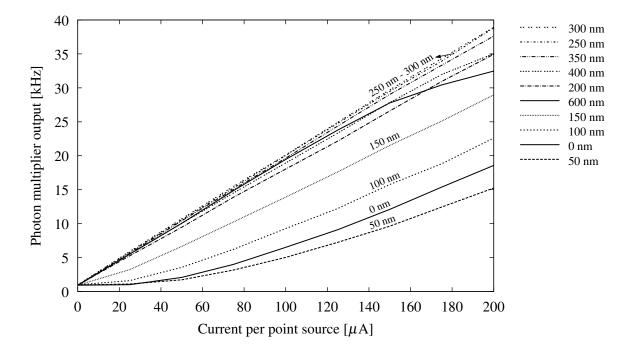

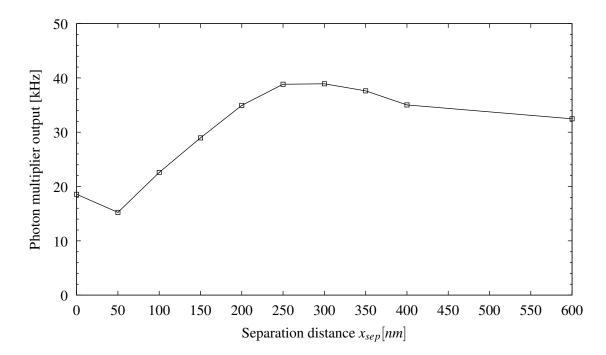

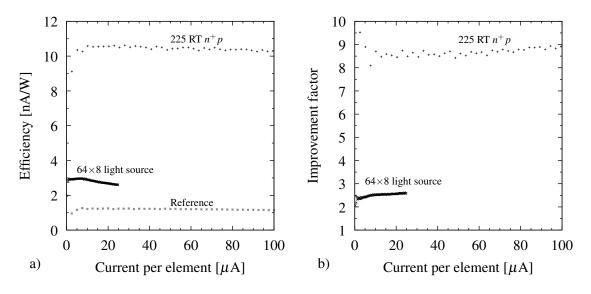

|       | 5.5.2   | Optical characteristics                                         | 92  |

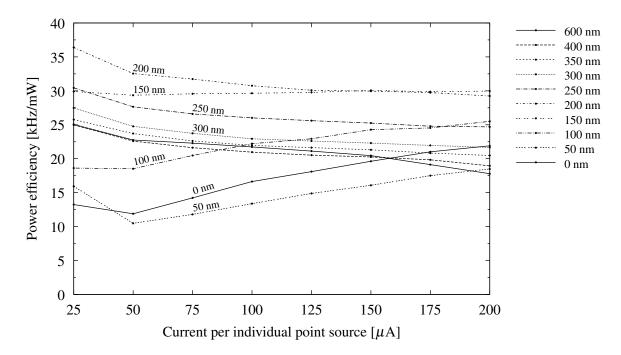

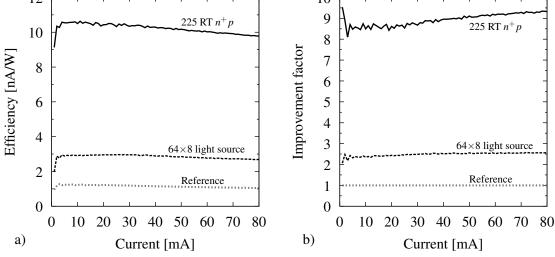

|       | 5.5.3   | Efficiency                                                      | 96  |

|       | 5.5.4   | Summary of results                                              | 98  |

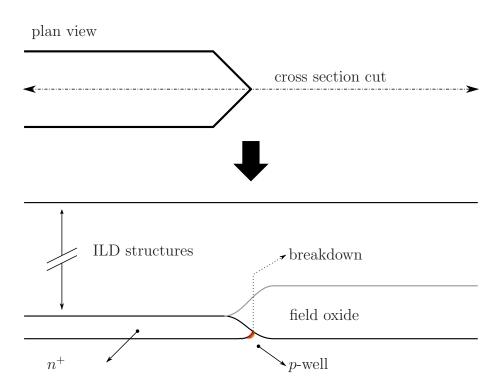

| 5.6   | Improv  | red CMOS geometry with field oxide channels                     | 100 |

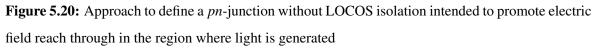

|       | 5.6.1   | Geometrical approach                                            | 100 |

|       | 5.6.2   | Design of junctions with oxide channels                         | 103 |

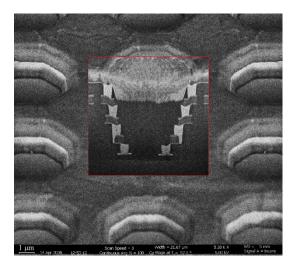

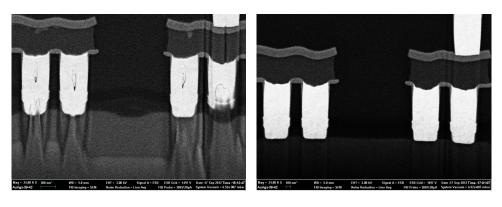

|       | 5.6.3   | Fabrication and resulting structures                            | 103 |

| 5.7   | Results | s for improved sources in reach through                         | 105 |

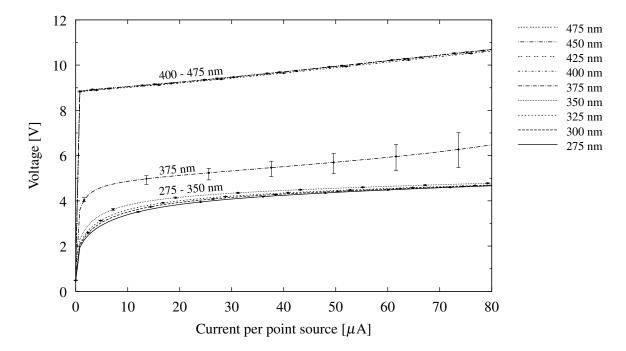

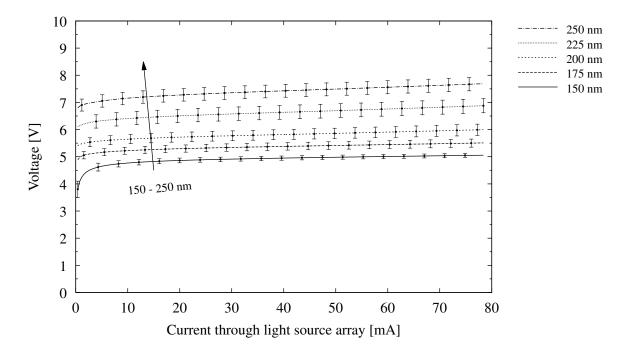

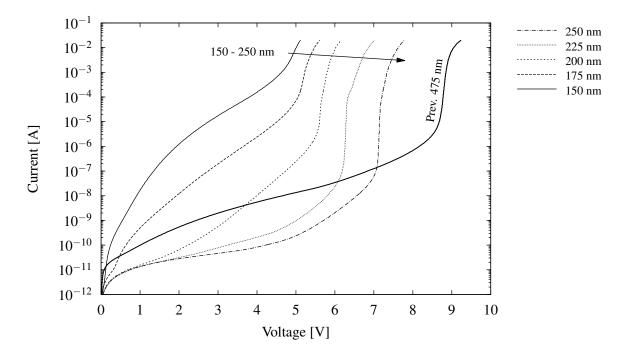

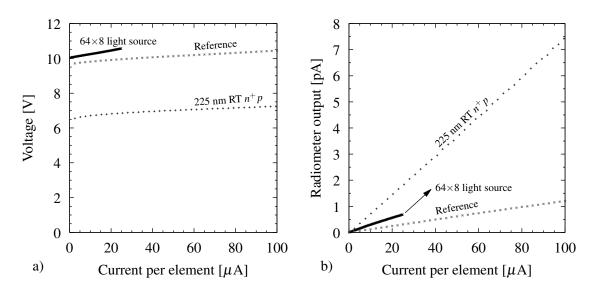

|       | 5.7.1   | Electrical characteristics                                      | 105 |

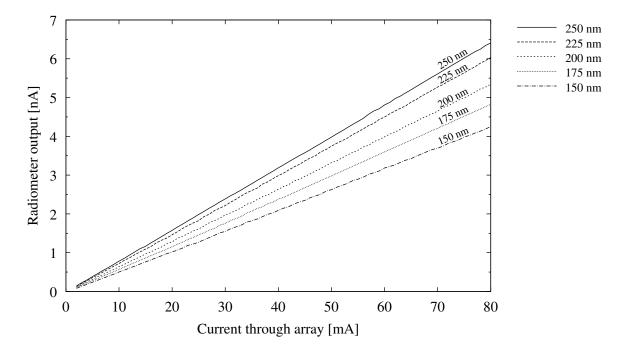

|       | 5.7.2   | Optical characteristics                                         | 110 |

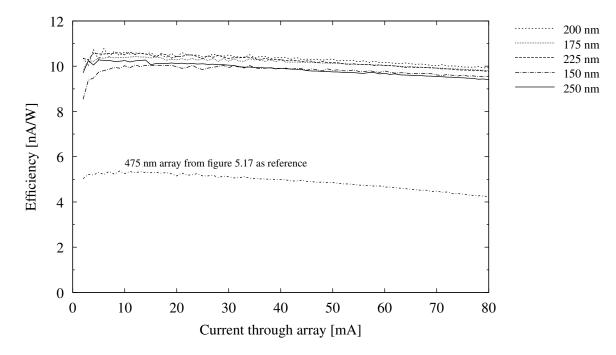

|       | 5.7.3   | Efficiency                                                      | 112 |

|       | 5.7.4   | Summary of results                                              | 114 |

| 5.8   | Conclu  | sion                                                            | 116 |

| СНАРТ | ER 6    | A 128 x 96 pixel CMOS microdisplay using improved light sources | 119 |

| 6.1   | Introdu | uction                                                          | 119 |

| 6.2   | Requir  | ements                                                          | 120 |

|       | 6.2.1       | Qualitative objectives                                   |

|-------|-------------|----------------------------------------------------------|

|       | 6.2.2       | Quantitative objectives                                  |

| 6.3   | Light s     | ource                                                    |

|       | 6.3.1       | Spectral analysis                                        |

|       | 6.3.2       | Point source improvement                                 |

|       | 6.3.3       | Point source design                                      |

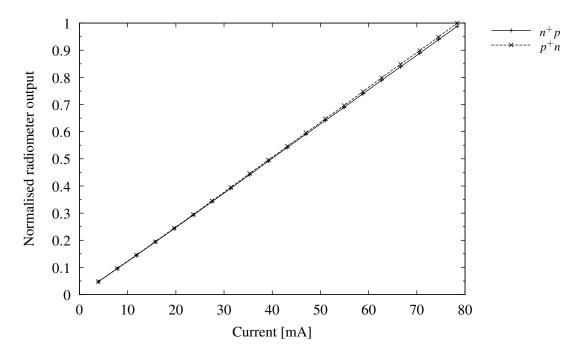

|       | 6.3.4       | Polarity comparison                                      |

| 6.4   | Integra     | ted pixel design                                         |

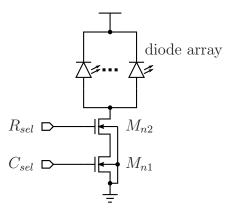

|       | 6.4.1       | Light source array                                       |

|       | 6.4.2       | Driving circuitry                                        |

|       | 6.4.3       | Layout                                                   |

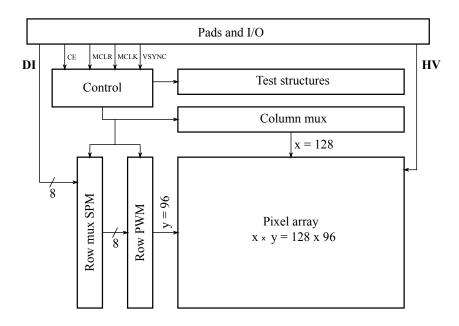

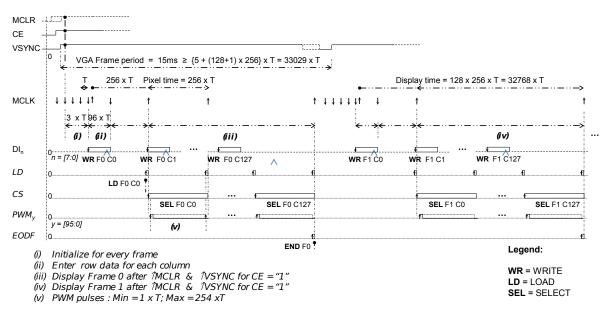

| 6.5   | Microd      | isplay architecture                                      |

|       | 6.5.1       | Luminous intensity control                               |

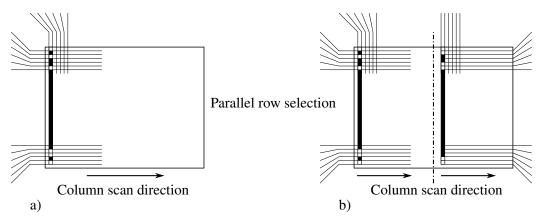

|       | 6.5.2       | Scanning architecture for pixel matrix                   |

|       | 6.5.3       | Integrated controller                                    |

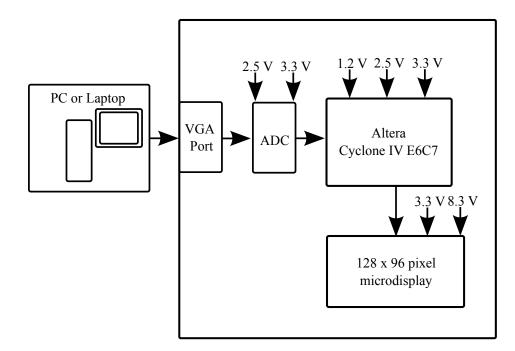

|       | 6.5.4       | External controller                                      |

| 6.6   | Results     |                                                          |

|       | 6.6.1       | Electrical characteristics                               |

|       | 6.6.2       | Optical characteristics                                  |

|       | 6.6.3       | Luminance                                                |

|       | 6.6.4       | Summary                                                  |

| 6.7   | Conclu      | sion                                                     |

| СНАРТ | тр <b>7</b> | Conclusion 156                                           |

|       |             | rry of work                                              |

| 7.1   |             |                                                          |

| 7.2   |             | l analysis                                               |

|       | 7.2.1       | Hypothesis                                               |

|       | 7.2.2       | Research questions                                       |

|       | 7.2.3       | Comparison of efficiency in relation to other work       |

| 7.0   | 7.2.4       | Comparison of CMOS integration in relation to other work |

| 7.3   |             | pution                                                   |

| 7.4   | Future      | work                                                     |

|       |             |                                                          |

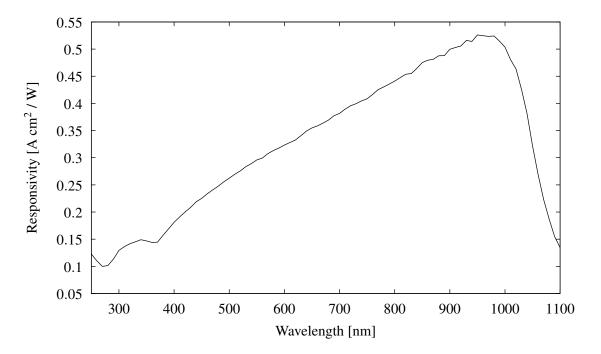

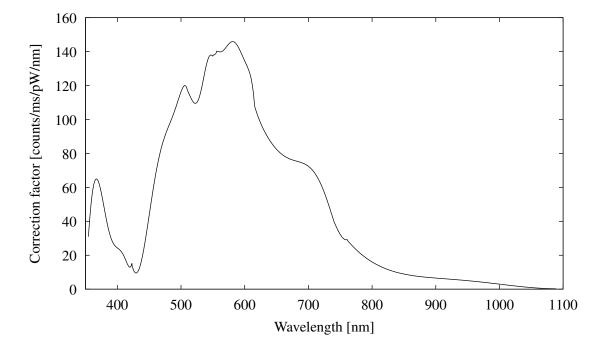

| A.1 | Radiometer                          | 175 |

|-----|-------------------------------------|-----|

| A.2 | Parameter analysis                  | 176 |

| A.3 | Spectral analysis                   | 177 |

| A.4 | Method for calculating radiant flux | 178 |

| A.5 | Conclusion                          | 179 |

# **CHAPTER 1**

## **INTRODUCTION**

Silicon light emission through hot carrier luminescence has the potential to provide integrated circuits with a light source, resulting in a disruptive capability for standard CMOS circuits to address markets that are inaccessible under conventional wisdom. The electro-optical conversion efficiency is naturally low because silicon is an indirect band gap material. This research work describes a novel way of improving the usability and efficiency of silicon light sources in standard CMOS without process alterations.

## 1.1 BACKGROUND

Silicon is the element that is fundamentally responsible for the most influential paradigm shift in electronics history. Although the first successful transistor was made of germanium, it was silicon that enabled monolithic integration of multiple functions on a single substrate, utilising the field-effect introduced by Lilienfeld in 1925. Native oxide growth enabled almost perfect gate dielectrics, while the nature of the MOS transistor allowed for ease of scaling seen through much of the 20th century, continuing the trend established by Moore even today.

Silicon domination in all things electronic overshadows one inherent disadvantage: silicon is an indirect band gap material. In an age where bandwidth and data density is becoming increasingly important, a shift to the optical domain is often seen as the next necessary step. Furthermore, as scaling in integrated circuits reduces device dimensions at an unsustainable rate, the "More than Moore"movement leans towards more integrated functional systems on chip and package rather than just more transistors [1]. Although silicon is often used as a photodetecting material its indirect band gap crystal electronic structure cannot compete with the radiative efficiency of III-V materials and other direct band gap semiconductors. This fact alone leaves silicon to remain an exclusively electronic material until an integrated light source becomes feasible.

There are two ways of generating light from silicon often reported on in literature. The first is through radiative recombination of free minority carriers as a result of diffusion across a forward biased *pn*-junction. The majority of radiative action occurs through indirect, phonon-assisted recombination, where the probability of radiation is adversely affected by the available phonon dispersion statistics. As the lifetime of minority carriers in the quasi-neutral regions are relatively long, the devices are not inherently fast. The body of knowledge includes a reasonable amount of work in this field. The second method for light generation is through avalanche electroluminescence. Literature typically sees this as a curiosity and a limited number of authors have empirically tried to explain certain observances noted in experimental results, usually based on spectral results. There have been a limited number of attempts to explain the origins of the radiative mechanisms and to explain the behaviour of carriers under the conditions in which this phenomenon occur.

This work focuses on the usability of the second phenomenon *supra*. Since the optically active material is silicon, it becomes possible to work towards an integrated light source in silicon-based electronics and very specifically, standard CMOS processes aimed at manufacturing digital and mixed-signal circuits.

## **1.2 PROBLEM STATEMENT**

Conventional electron-hole recombination in silicon is generally non-radiative and slow due to a misalignment of the lowest conduction band valley and the  $\Gamma$ -point in momentum space. In contrast, the conduction valley and valence peak align at the  $\Gamma$ -point in a direct band gap material such as GaAs. This is an inherent material property.

The fundamental problem is therefore that the need for an integrated light source cannot be fulfilled by reverting to conventional radiative recombination mechanisms in standard CMOS circuits.

Hot carrier luminescence is a term referring to radiative mechanisms associated with carrier actions when the carriers are "heated" by using very high electric fields. Carriers are shifted away from the lowest energy valleys and spread to other states of higher energy in the Brillouin-zone. The exact photon-generating mechanisms are beyond the scope of this work, although the means for establishing radiation gives rise to difficulties addressed in this research. For example, hot carrier luminescence requires carrier transport in regions of high electric field. One way of establishing both at the same time is by reverse-biasing a *pn*-junction to the point of avalanche breakdown. The voltage required is usually fixed by the specific doping implants used for transistors in standard CMOS processes. This value is often high enough to prevent practical integration of light sources with other electronic circuitry on-chip. Although the nature of the radiative mechanism differs from conventional LEDs, the efficiency is still low. Therefore, any improvement in efficiency is conducive to creating an attractive light source for integration in a standard CMOS process.

The problem addressed in this work is creating a means for integrating silicon light sources based on hot carrier luminescence suitable for use in standard CMOS while improving the electro-optical conversion efficiency.

## **1.3 MOTIVATION**

Silicon, and more specifically the CMOS platform, is the most widely used semiconductor in electronic devices, covering an estimated market of over \$300 billion in the semiconductor domain. The physical nature of crystalline silicon and the associated crystal electronic structure makes spontaneous emission in forward biased junctions both slow and inefficient due to its indirect band gap nature.

The ability to employ hot carrier luminescence in silicon eliminates the speed constraint of conventional diffusion LEDs, while the quantum and power efficiency, although not good compared to direct band gap semiconductors, may be improved to a point of usability in integrated circuit environments.

The biggest advantage offered by silicon light sources, particularly when CMOS compatible, is the integration opportunities and cost benefits offered by CMOS. Current infrastructure and over 40 years of technological experience and maturity are proof of how ingrained CMOS is in the electronics market and also indicative of a platform that will likely extend well into the future.

In a broad sense, the motivation for this research is therefore driven by the opportunities which will arise when bridging the gap between CMOS and the optical domain, thereby enabling CMOS to contend in the field of optics, which is usually reserved for the more exotic and expensive direct band gap semiconductors such as GaAs and InP. With a feasible silicon light source, this may be possible.

From a narrow perspective this research is motivated by a need to find practical solutions for integrating light sources in a technology well suited for low voltage digital circuitry, without any optical devices in mind, and using CMOS compatible improvement techniques for enhancing device efficiency and performance.

## 1.4 HYPOTHESIS AND RESEARCH QUESTIONS

## 1.4.1 Hypothesis

The operating voltage of a *pn*-junction in avalanche is the result of the integral of the internal electric field. Only a small region within the electric field is responsible for avalanche multiplication. It is therefore envisaged that by using a highly doped field stop it is possible to terminate the electric field without affecting carrier generation due to the avalanching region, thereby reducing the operating voltage of such a light source. This will facilitate integration and coexistence with other on-chip circuitry and may improve the power efficiency of the light sources.

The hypothesis can therefore be stated as

If the electric field distribution can be changed through geometrical adaptations which will result in effects such as electric field reach through between two highly doped regions in a pn-junction, the electrical and optical characteristics of silicon hot carrier luminescent light sources may be altered and optimised in such a way as to facilitate the integration of these light sources in standard CMOS as usable components in integrated systems such as microdisplays.

## 1.5 RESEARCH QUESTIONS

1. What is the correlation between the length of the electric field in each through on the operating voltages of hot carrier light sources?

- 2. If correlation exists, what are the bounds and means to improve and optimise devices for integration?

- 3. How does electric field reach through affect power efficiency in hot carrier luminescent silicon light sources?

- 4. What are the issues when integrating hot carrier luminescent light sources into standard CMOS while coexisting with other circuitry?

- 5. What are the considerations when harnessing the visible part of the light emission for use in CMOS microdisplays?

## 1.6 JUSTIFICATION OF RESEARCH

Junctions in standard CMOS processes are limited to only a few available configurations. The doping levels are fixed according to what is required for transistor implementation. While light emission from silicon has been reported from CMOS junctions in avalanche- and field emission breakdown modes, most CMOS process rules do not afford the circuit designer structures to control the breakdown voltage of these mechanisms. This work aims to introduce a technique which does offer a circuit designer a deterministic way of controlling the breakdown voltage, without affecting the power efficiency of the electro-optical conversion process. Since hot carrier luminescence in silicon emits visible light, the application of this technique in a microdisplay application proves that it is possible to use this technique from a CMOS circuit designer perspective, without process alterations. It now becomes possible to define a CMOS light source as a predictable component in a CMOS foundry's standard cell library.

#### 1.7 RESEARCH METHODOLOGY

- A literature study of hot carrier luminescence in semiconductors will serve as a starting point for investigating the radiative phenomenon involved and establishing the conditions under which the phenomenon occurs. The review will also include a comparison of the approaches taken to integrate hot carrier light sources with on-chip circuitry in standard CMOS processes.

- 2. State-of-the-art in silicon hot carrier luminescent light sources will be investigated and techniques will be developed for integration of these light sources in standard silicon, using a mi-

crodisplay application as a test case.

- 3. The nature of CMOS, in terms of opportunities and constraints will be investigated for a typical CMOS process technology. The mismatch between operating voltages required, optimisation of surface profile at the Si/SiO2 interface and doping related aspects will be considered and evaluated in terms of its compatibility with the proposed efficiency improvement technique.

- 4. Improved light sources will be developed targeted at certain shortcomings of the state of the art light sources with an improvement of efficiency and ease of integration in mind.

- 5. The improved light sources will be used in a microdisplay with scaled up performance specifications in order to evaluate the extent to which the research questions are satisfied.

- 6. Multiple integrated circuit designs in a standard CMOS process will be designed from first principles to evaluate the premises of this work. This will include designs with the intent to investigate and evaluate the following:

- Electrically characterise the operation of light sources

- Optically evaluate the emission characteristics of the luminous phenomenon

- A comparison of the efficiency improvement between state of the art and improved light sources

- The evaluation of considerations for integration where light sources need to coexist with digital and analogue circuitry on a standard CMOS integrated circuit

- The proof of the possibility of such integration

- Experimental and analysis work and its interpretation in proving the hypothesis.

## 1.8 CONTRIBUTION TO BODY OF KNOWLEDGE

• This work describes the first directly observable microdisplay based on silicon light sources in standard CMOS using state of the art silicon light sources with usable luminance values for direct observation without image intensification.

- This work is the first to prove that, by using electric field reach through, it is possible to modify the operating voltage of a silicon light source according to the application need.

- This work presents a novel way of improving the reliability and extraction efficiency of a silicon light source by using a field oxide LOCOS structure in a channel-like configuration.

- This work presents the first 128×96 pixel microdisplay, with architecture considerations, capable of being produced in a standard CMOS process and suited for use with the naked eye.

- The results of this work show a strong correlation between external quantum efficiency and device potential. This is indicative of a relation between quantum efficiency and the time a carrier spends under a high electric field.

## **1.9 OUTLINE OF THESIS**

**Chapter 1** is an introduction to the relevance of this work in relation to the body of knowledge surrounding silicon hot carrier luminescence. A background is given on the luminescent phenomena in semiconductors. The specific problems associated with the need for an integrated light source in silicon are addressed as well as the problem addressed by this research work. A motivation for this research and hypothesis along with its associated research questions is formulated which is given due consideration throughout the remainder of this thesis. The research methodology is discussed along with the contribution to the body of knowledge arising from this work. Journal articles and conference contributions originating from this work are summarised to substantiate the relevance of the approaches developed herein.

**Chapter 2** contains an overview of the approaches followed in trying to create useful light emission from indirect band gap semiconductors. A more detailed investigation into the observations on hot carrier luminescence in silicon provides for a solid foundation on which to compare this work. Although there have been a number of publications on hot carrier luminescence and the modelling thereof, few groups have tried to convert this phenomenon into a useful addition to the set of components in standard CMOS. The efficiency performance of hot carrier luminescence is examined from results by various groups. This serves as a relevant figure of merit with which to compare the results obtained in this work. Finally, the attempts by the few groups to integrate a light source as a standard CMOS component are mentioned.

**Chapter 3** contains some background knowledge which is useful and/or necessary to understand the design approaches in this work. Some of the observations gained during experimental work can also be understood in the light of the theoretical tools discussed in this chapter. High field carrier transport considerations are mentioned, as well as expectations in terms of observables, while the reach through approach is considered from an abrupt junction approximation.

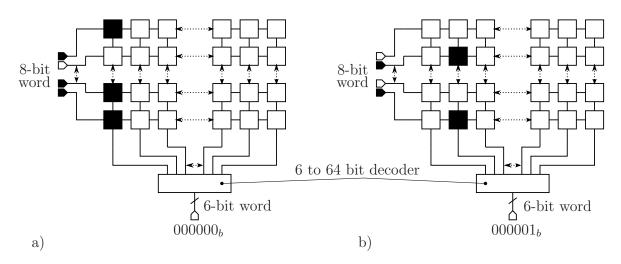

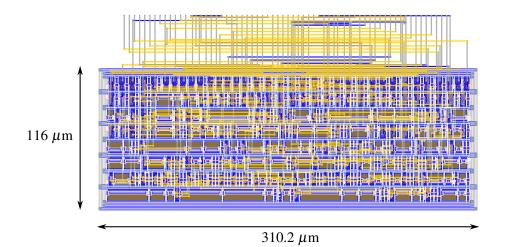

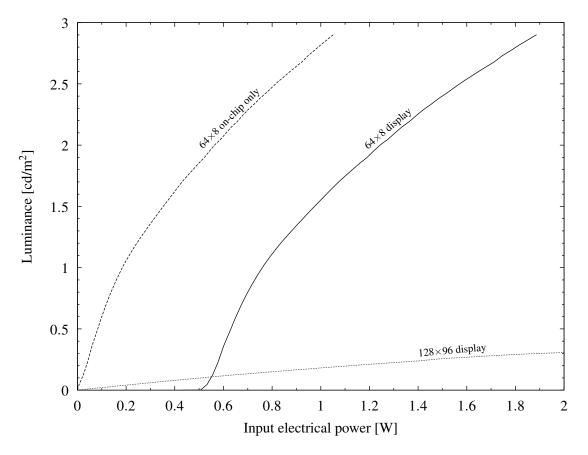

**Chapter 4** introduces the state of the art CMOS light sources developed by our group at the Carl and Emily Fuchs Institute for Microelectronics (CEFIM), University of Pretoria, where aspects such as the layout masks and geometry of the processed structures are discussed. Localisation of the breakdown region is necessary to ensure uniformity of emission. A technique to accomplish this is explained. Light sources are employed in a pixel and integrated with on-chip driver circuitry and a scanning decoder in order to create a  $64 \times 8$  pixel CMOS microdisplay capable of directly observable luminance levels. The performance of this microdisplay is characterised and some of the difficulties of integration are stated.

**Chapter 5** proposes a technique which can be used for creating layout geometries where the reach through condition is established. The first approach follows the obvious route of reducing the spacing between two highly doped regions using conventional diode layout structures mentioned in the design documents supplied by the foundry. Problems arise pertaining to the field oxide profile between junctions. An improved approach is introduced and shown to result in devices which outperforms the previous approach as well as the state of the art light sources. The improved light sources are electrically more predictable, exhibit an improved optical extraction efficiency and provide predictable operating voltage behaviour as a function of the junction separation distance.

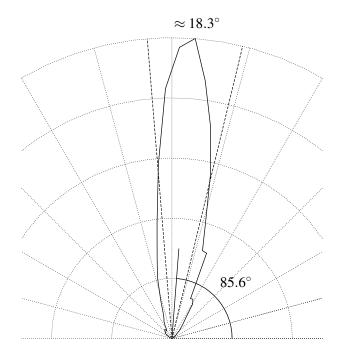

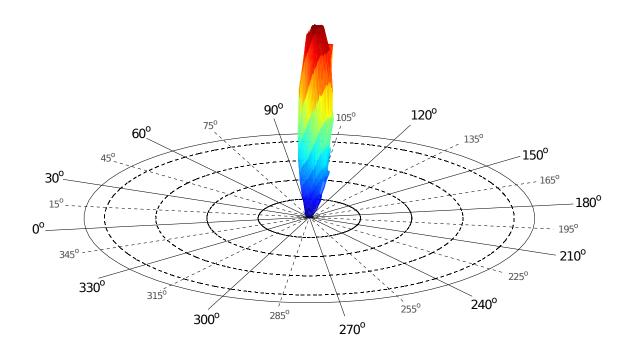

**Chapter 6** combines the integration aspects identified and developed in **chapter 4** and the light sources developed in **chapter 5** in a design for a much larger, more integrated microdisplay with an array of  $128 \times 96$  pixels where each pixel utilised the improved light sources. The driving architecture is improved compared to the  $64 \times 8$  pixel display to enable a single high voltage feed to the optical array. This voltage is substantially reduced compared to the design employing state of the art light source and becomes compatible with power sources often used in mobile environments. Finally, the power efficiency of the microdisplay is improved by a substantial factor, although the luminance results suffer in the light of the radiation pattern of the improved light sources.

**Chapter 7** concludes the study with a critical analysis on this work compared to other works of similar nature. The results of this work are summarised and the contribution to the body of knowledge is highlighted. Future gaps in the body of knowledge are identified and suggested as work to evolve into future studies.

## 1.10 LIST OF PUBLICATIONS

## 1.10.1 Peer reviewed journal publications

- 1. M. du Plessis, P. J. Venter and E. Bellotti, "Spectral characteristics of hot electron electroluminescence in silicon avalanching junctions," *IEEE J. Quantum Electron.*, to be published.

- P. J. Venter, M. du Plessis, A. W. Bogalecki, M. E. Goosen and P. Rademeyer, "An 8x64 pixel dot matrix microdisplay in 0.35-µm complementary metal-oxide semiconductor technology," *Optical Engineering*, vol. 51, no. 1, pp. 014003-1-014003-7, Jan. 2012.

- M. E. Goosen, M. du Plessis, P. J. Venter, A. W. Bogalecki, A. C. Alberts and P. Rademeyer, "CMOS avalanche electroluminescence applications - microdisplay and high speed data communication," *Trans. SAIEE*, vol. 103, no. 1, pp. 24-28, 2012.

#### 1.10.2 Peer reviewed international conference contributions

- P. J. Venter, A. C. Alberts, M. du Plessis, T.-H. Joubert, M. E. Goosen, C. Janse van Rensburg, P. Rademeyer and N. M. Fauré, "A CMOS microdisplay with integrated controller utilizing improved silicon hot carrier luminescent light sources," in *Proc. SPIE 8643, Advances in Display Technologies III, 864309*, 2013 ©SPIE Digital Library, doi: 10.1117/12.2004277.

- P. J. Venter, M. du Plessis, A. W. Bogalecki and P. Rademeyer, "Late-news poster: An all-CMOS microdisplay utilizing integrated novel avalanche light-emitting sources," *SID Symp. Digest of Technical Papers*, vol. 42, no. 1, pp. 1512-1515, 2011.

- P. J. Venter, A. W. Bogalecki, M. du Plessis, M. E. Goosen, I. J. Nell and P. Rademeyer, "CMOS dot matrix microdisplay," in *Proc. SPIE 7956, Advances in Display Technologies and E-papers and Flexible Displays, 79560Y*, 2011 ©SPIE Digital Library, doi:10.1117/12.875131.

- P. J. Venter, M. du Plessis, I. J. Nell, M. E. Goosen and A. W. Bogalecki, "Improved efficiency of CMOS light emitters in punch through with field oxide manipulation," in 2010 International Conference on Microelectronics (ICM), Cairo, 2010, pp. 36 - 39.

- A. W. Bogalecki, M. du Plessis, P. J. Venter, I. J. Nell and M. E. Goosen, "Integrated optical light directing structures in CMOS to improve light extraction efficiency," in 2010 International Conference on Microelectronics (ICM), Cairo, 2010, pp. 168 - 171.

- P. J. Venter and M. du Plessis, "Improved silicon light emission for reach- and punch-through devices in standard CMOS," in *Proc. SPIE 7607, Optoelectronic Interconnects and Component Integration IX, 76070Z*, 2010 ©SPIE Digital Library, doi:10.1117/12.841357.

- M. du Plessis, P. J. Venter and A. W. Bogalecki, "Using reach-through techniques to improve the external power efficiency of silicon CMOS light emitting devices," in *Proc. SPIE 7606*, *Silicon Photonics V*, 760612, 2010 ©SPIE Digital Library, doi:10.1117/12.840646.

## 1.10.3 Patents applications filed and granted

- 1. South African patent granted (RSA no. 2012/04957)

- 2. China patent application no. 201180006581

- 3. European patent application no.11705035.1

- 4. Japanese patent application no. 2012-549458

- 5. USA patent application no. 13/574,333

# **CHAPTER 2**

# LITERATURE REVIEW OF RELATED WORK

#### 2.1 ELECTROLUMINESCENCE IN SEMICONDUCTORS

Electroluminescence from semiconductors was first observed by Howard Round as a glow observed from a silicon carbide diode in 1907 [2] and independently in 1927 by Oleg Losev [3], who went further to create devices utilising the phenomenon and patenting applications around its use. Throughout the 1950s, a number of authors [4], [5] observed radiance from diodes and noted that the emission spectrum coincided with the band gap energy associated with the semiconductor. Observations linked the radiative mechanism to the recombination of electrons and holes, as described by Shockley [6] as an interband process. Note that the mechanism does not involve phonon action if carrier recombination occurs in direct band gap semiconductors, such as GaAs, making the probability of direct recombination much higher. This is the reason direct band gap semiconductors are much more efficient when depending on electron-hole recombination for radiative action. Silicon has an indirect band gap structure which requires phonon-assisted recombination where these transition rates has to compete with other dominating non-radiative processes [7]. Due to this indirect band gap nature of the crystal electronic band structure, silicon is inherently an inefficient, slow light emitting material. Interband recombination processes are the *de facto* standard way for light emission from semiconductors rendering direct band gap materials as the preferred choice for this purpose.

#### 2.1.1 Light emission from indirect band gap materials

Silicon is used in almost all integrated circuits, rendering silicon as a ubiquitous electronic material. Germanium, with a much higher electron and hole mobility [8] compared to silicon [8], is also used in modern devices, for example, to increase the transconductance of bipolar transistors [9]. It is quite

common to see SiGe HBTs coexisting with CMOS in analogue and RF applications today. Both silicon and germanium are indirect band gap materials and are therefore inefficient optical emitters. A lot of time has therefore been invested in investigating techniques for creating efficient optical emitters using indirect band gap materials.

#### 2.1.1.1 Bulk silicon *pn*-junctions

Forward-biased *pn*-junctions emit light with a photon energy close to the band gap energy [4] of the material. This mechanism will always by nature be slow due to the requirement of phonons with the correct momentum to establish electron-hole recombination for photon emission. Interdigitated *pn*-junctions have been shown to emit light with external power efficiencies of around  $10^{-4}$  at a wavelength of 1.16  $\mu$ m [10] implemented in standard CMOS. Power efficiencies of up to  $10^{-2}$  have been reported by making use of passive emitter, rear locally-diffused (PERL) techniques [11] although the minority carrier lifetimes are of such longevity that its usefulness is limited to slow switching applications. The designs using PERL techniques are inherently incompatible with CMOS integration without process modifications. More recent work [12] shows results similar to what we have observed in a standard CMOS process with power efficiencies of  $\approx 1.2 \times 10^{-6}$ , with optical power reaching levels of around 100 nW with interdigitated structures. Since the absorption wavelength of silicon falls off sharply at the band gap wavelength [13], it is impractical to use a forward-biased approach in bulk CMOS in all-silicon communication systems.

## 2.1.1.2 Dislocation loop engineering

An interesting approach is to utilise the implantation of Boron ions, available in standard CMOS processes, for creating dislocation loops [14]. Dislocation loops modify the band structure of the silicon crystal by introducing a local strain field. This technique has shown to emit 19.8  $\mu$ W at 100 mA with an external quantum efficiency of  $\approx 2 \times 10^{-4}$ . The approach has drawn critical review [15] regarding the origin of light and the effect of lattice damage. This technique has not yet led to any commercially available integrated light source.

#### 2.1.1.3 Rare earth elements

Erbium doping of the gate oxide in MOS transistors has also shown to allow electroluminescent emission at 1.54  $\mu$ m with operation at room temperature [16]. The same work also reports on various other

rare earth ions and the quantum efficiencies associated with these. An external quantum efficiency of  $\approx 2 \%$  proves emission output powers of usable values. Hot electron and Si nanocrystal interaction with the Erbium ions are reported to be the cause of emission. It is mentioned that reliability of these devices is still preventing commercial use, although it has been a decade since this work was published, without a commercial example to date.

#### 2.1.1.4 Porous silicon

It was observed in 1990 that porous silicon emits light when optically pumped [17]. This has led to a number of investigative works. Electrochemical processing proved to enable the creation of silicon nanowires resulting in porous silicon without reverting to lithographical techniques. Although the hurdles towards commercial application did not seem high [18], the reliability and stability, bandwidth and integration with commercial processes were identified as challenges. Although PSi LEDs are electroluminescent and their potential was showcased as a possible display technology [19], [20], to date no commercial product exists which makes use of this technology.

#### 2.1.1.5 Nanostructures and superlattices

Visible emission from porous silicon has resulted in attention to optical gain from silicon nanocrystals [21]. Silicon nanocrystals are formed in SiO<sub>2</sub> usually through implantation and have been seen to obtain quantum efficiencies as high as 60 % [22]. Most of the successful results are, however, due to photoluminescent pumping [23] and cannot easily be achieved by using conventional carrier injection means for electroluminescent stimulation. In other words, it is difficult to use these structures as electronic components. Furthermore, the implantation of silicon is not a standard CMOS processing step. Nanostructures have also been successfully used to create electrically excited surface plasmon polaritons between metal and dielectric interfaces [24]. Since this approach can potentially utilise the back end of line stack, it may be reconcilable with CMOS processes by changing the BEOL stack.

#### 2.1.1.6 Germanium epitaxial techniques and state filling

Germanium exhibits an indirect band gap much like silicon. One aspect of germanium's electronic band gap structure has received a lot of research attention: while the L-valley determines the conduction band edge with  $E_g = 0.664$  eV, the  $\Gamma$ -valley is separated by only  $E_{\Gamma 1} = 0.8$  eV from the valence band edge which provides for a valley "almost within direct band gap reach". There are two approaches currently under active investigation which aim to capitalise on this feature.

- 1. By creating tensile strain in the correct crystallographic direction, it is possible to "convert" the electronic band structure of germanium to a direct band gap material [25]. This occurs due to the physical deformation of the crystal lattice. A tensile strain of around 1.8 % allows for the  $\Gamma$ -valley to determine the conduction band edge.

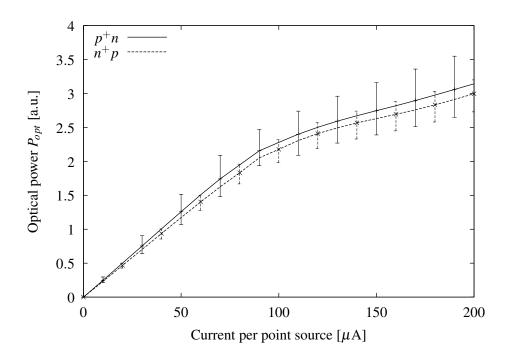

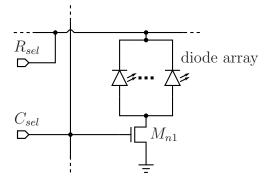

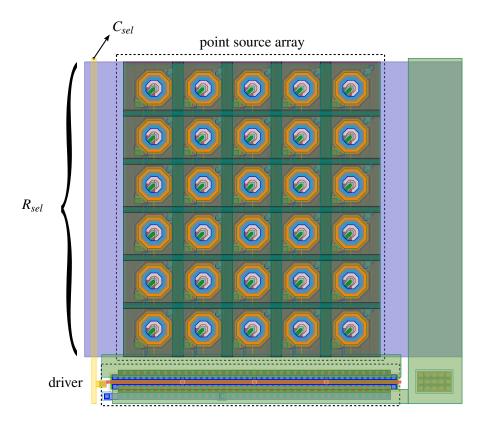

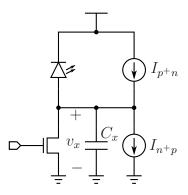

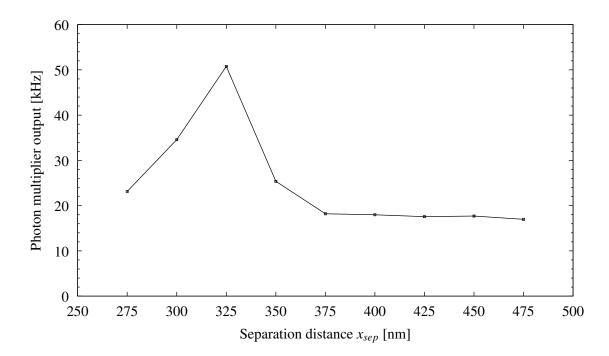

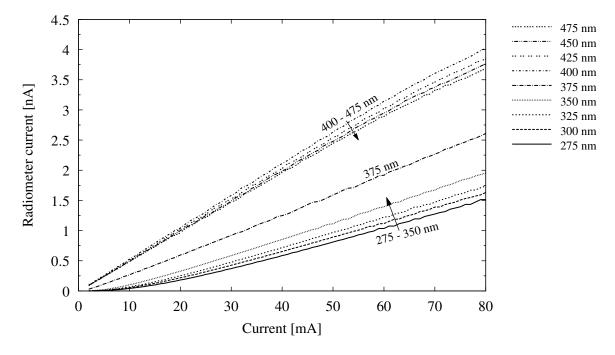

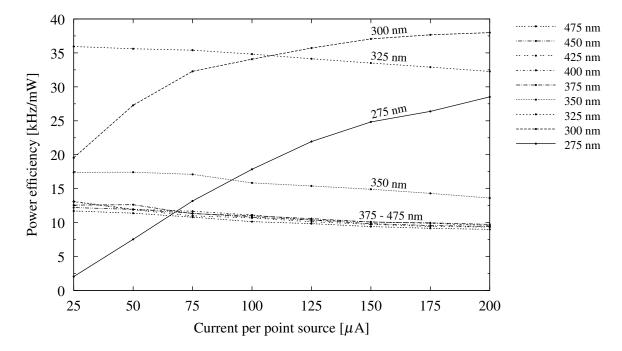

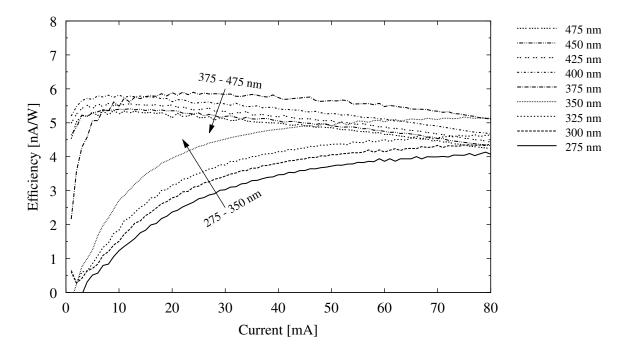

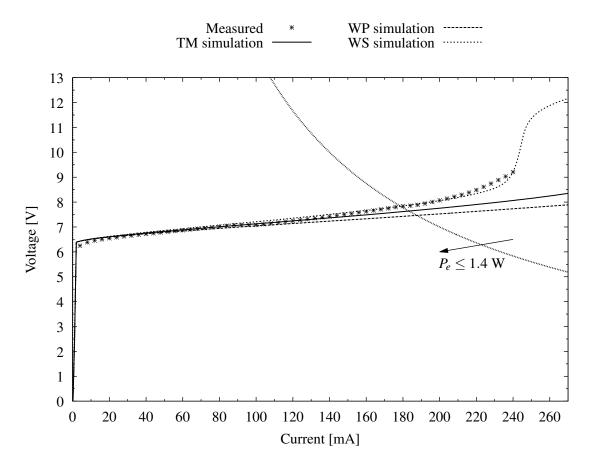

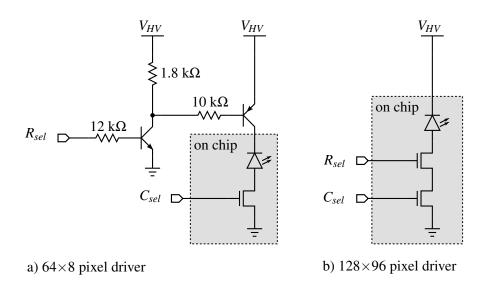

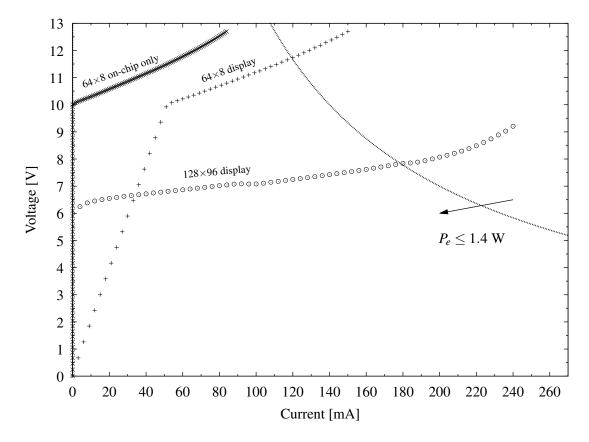

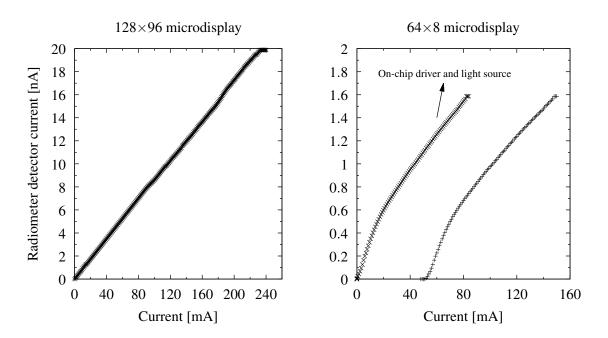

- 2. Under high level injection it is possible to fill the states around the L-point and carriers will start to spill into the  $\Gamma$ -region [26] resulting in direct interband transitions. Another similar approach is to introduce large *n*-type dopants in order to lift the Fermi-energy to a point where state filling will saturate the L-valley and carrier population will start to occur at the  $\Gamma$ -point [27].