### ON THE IMPROVEMENT OF PHASE NOISE IN WIDEBAND FREQUENCY SYNTHESIZERS

by

Pandelani Reuben Munyai

Submitted in partial fulfilment of the requirements for the degree

Master of Engineering (Electronic Engineering)

in the

Department of Electrical, Electronic and Computer Engineering Faculty of Engineering, Built Environment and Information Technology UNIVERSITY OF PRETORIA

January 2017

#### SUMMARY

### ON THE IMPROVEMENT OF PHASE NOISE IN WIDEBAND FREQUENCY SYNTHESIZERS

by

#### Pandelani Reuben Munyai

| Supervisor(s): | Prof. B.J.T Maharaj                                                       |

|----------------|---------------------------------------------------------------------------|

| Department:    | Electrical, Electronic and Computer Engineering                           |

| University:    | University of Pretoria                                                    |

| Degree:        | Master of Engineering (Electronic Engineering)                            |

| Keywords:      | Phase noise, phase error, phase noise tracking, phase noise correction    |

|                | technique, phase noise correction, cascaded resonator feedback, poles     |

|                | and zeros, sigma delta modulator, adaptive filtering, fractional-N phase- |

|                | locked loop.                                                              |

Wireless communication systems are based on frequency synthesizers that generate carrier signals, which are used to transmit information. Frequency synthesizers use voltage controlled oscillators (VCO) to produce the required frequencies within a specified period of time. In the process of generating frequency, the VCO and other electronic components such as amplifiers produce some unwanted short-term frequency variations, which cause frequency instability within the frequency of interest known as phase noise (PN). PN has a negative impact on the performance of the overall wireless communication system. A literature study conducted on this research reveals that the existing PN cancellation techniques have some limitations and drawbacks that require further attention.

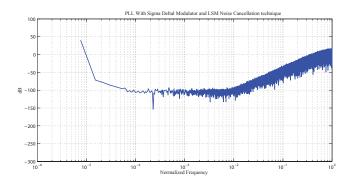

A new PN correction technique based on the combination of least mean square (LMS) adaptive filtering and single-loop single-bit Sigma Delta ( $\Sigma\Delta$ ) modulator is proposed. The new design is also based on the Cascaded Resonator Feedback (CRFB) architecture. The noise transfer function (NTF) of the architecture was formulated in way that made it possible to stabilize the frequency fluctuations within the in-band (frequency of interest) by locating its poles and zeros within the unit circle.

The new design was simulated and tested on a commercially available software tool called Agilent

Advanced Design System (ADS). Simulation results show that the new technique achieves better results when compared with existing techniques as it achieves a 104 dB signal-to-noise (SNR), which is an improvement of 9 dB when compared with the existing technique accessed from the latest publications. The new design also achieves a clean signal with minimal spurious tones within the inband with a phase noise level of -141 dBc/Hz (lower phase noise level by 28 dBc/Hz) when compared with the existing techniques.

### ACKNOWLEDGMENTS

I would like to extend my sincerest gratitude to the following people for their tireless effort and contribution towards this work:

- My supervisor and mentor, Prof B.T. Maharaj for his expert guidance and support.

- My wife, for her encouragement and support throughout the course of this work.

# LIST OF ABBREVIATIONS

| ADC   | Analog to Digital Converters        |

|-------|-------------------------------------|

| ADS   | Advanced Design System              |

| AR    | Auto-Regressive                     |

| AWGN  | Additive White Gaussian Noise       |

| BPSK  | Binary Phase Shift Keying           |

| BER   | Bit Error Rate                      |

| BS    | Base Station                        |

| CPE   | Common Phase Error                  |

| CRFB  | Cascade of Resonators with Feedback |

| DAC   | Digital to Analog Converters        |

| DSS   | Direct Digital Synthesis            |

| EKF   | Extended Kalman Filter              |

| FDC   | Frequency-to-Digital Converter      |

| FNPLL | Fractional-N Phase locked Loop      |

| HSPA  | High Speed Packet Access            |

| ICI   | Inter Carrier Interference          |

| i.i.d | Independent Identically Distributed |

| IBN   | In-band Noise                       |

| ISI   | Intersymbol Interference            |

| KF    | Kalman Filter                       |

| LMS   | Least Mean Square                   |

| LOS   | Line Of Sight                       |

| LS    | Least Square                        |

| LTE   | Long Term Evolution                 |

| MASH  | Multi-stAge noise SHaping           |

| ML    | Maximum Likelihood                  |

| MLE   | Maximum Likelihood Estimation       |

| MMSE  | Minimum Mean Square Error           |

| MS    | Mobile Station                      |

| MSE   | Mean Square Error                   |

| NPM   | Normalized Projection Misalignment  |

| NTF   | Noise Transfer Function             |

|       |                                     |

| OFDM | Orthogonal Frequency Division Multiplexing |

|------|--------------------------------------------|

| OBG  | Out of Bound Gain                          |

| OSR  | Oversampling Ratio                         |

| PLL  | Phase-Lock Loop                            |

| PDF  | Probability Distribution Function          |

| PSD  | Power Spectral Density                     |

| PN   | Phase Noise                                |

| PSK  | Phase Shift Key                            |

| QAM  | Quadrature Amplitude Modulation            |

| RLS  | Recursive Least Square                     |

| RF   | Radio Frequency                            |

| SISO | Single Input Single Output                 |

| SQNR | Signal to Quantization Noise Ratio         |

| SNR  | Signal to Noise Ratio                      |

| STF  | Signal Transfer Function                   |

| VCO  | Voltage Control Oscillator                 |

| PN   | Phase Noise                                |

| PSK  | Phase Shift Key                            |

| QAM  | Quadrature Amplitude Modulation            |

| RLS  | Recursive Least Square                     |

| RF   | Radio Frequency                            |

| SISO | Single Input Single Output                 |

| SQNR | Signal to Quantization Noise Ratio         |

| SNR  | Signal to Noise Ratio                      |

| STF  | Signal Transfer Function                   |

| VCO  | Voltage Control Oscillator                 |

|      |                                            |

# TABLE OF CONTENTS

| СНАРТ | TER 1 | INTRODUCTION                                     | 1  |

|-------|-------|--------------------------------------------------|----|

| 1.1   | BACK  | GROUND                                           | 1  |

|       | 1.1.1 | Fundamentals of Phase Noise                      | 2  |

|       | 1.1.2 | Components of PN                                 | 4  |

|       | 1.1.3 | Frequency Synthesizers                           | 6  |

|       | 1.1.4 | Sigma Delta Quantization Noise                   | 7  |

|       | 1.1.5 | Performance criteria for PN reduction techniques | 8  |

| 1.2   | RELA  | TED WORK                                         | 12 |

| 1.3   | RESE  | ARCH HYPOTHESIS                                  | 18 |

| 1.4   | RESE  | ARCH METHODOLOGY                                 | 18 |

| 1.5   | RESE  | ARCH CONTRIBUTION                                | 18 |

| 1.6   | PUBL  | ICATIONS                                         | 20 |

|       | 1.6.1 | Conference Article                               | 20 |

|       | 1.6.2 | Journal Article                                  | 20 |

| 1.7   | DISSE | RTATION OUTLINE                                  | 21 |

| СНАРТ | TER 2 | PHASE NOISE CANCELLATION                         |    |

|       |       | TECHNIQUES                                       | 22 |

| 2.1   | CHAP  | TER OBJECTIVES                                   | 22 |

| 2.2   | ADAP  | TIVE FILTER NOISE CANCELER                       | 22 |

|       | 2.2.1 | Performance criteria                             | 23 |

|       | 2.2.2 | Least Mean Square Algorithm                      | 27 |

|       | 2.2.3 | Recursive Least Square                           | 33 |

|       | 2.2.4 | Kalman Filter                                    | 38 |

|       | 2.2.5 | Simulation results of KF                         | 39 |

| 2.3   | PHAS  | E LOCKED LOOP TECHNIQUE                          | 44 |

|       | 2.3.1 | PLL Noise Blocks                                   | 45 |

|-------|-------|----------------------------------------------------|----|

|       | 2.3.2 | Phase error tracking with PLL                      | 54 |

|       | 2.3.3 | PLL with Additive Noise                            | 56 |

|       | 2.3.4 | Phase error tracking with $2^{nd}$ order PLL       | 60 |

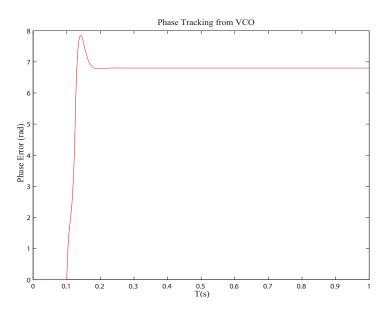

|       | 2.3.5 | Analysis of phase error tracking using PLL         | 61 |

|       | 2.3.6 | Phase change at the input                          | 62 |

|       | 2.3.7 | Shift in Input frequency                           | 63 |

|       | 2.3.8 | Analysis of Results                                | 64 |

| 2.4   | PLL W | /ITH SIGMA DELTA MODULATOR                         | 68 |

|       | 2.4.1 | Phase error as main cause of Spurs                 | 68 |

| 2.5   | LOW   | ORDER $\Sigma\Delta$ MODULATOR                     | 70 |

|       | 2.5.1 | Simulation of Low order $\Sigma\Delta$ modulator   | 72 |

|       | 2.5.2 | Higher-order $\Sigma\Delta$ modulators             | 74 |

|       | 2.5.3 | $N^{th}$ Order $\Sigma\Delta$ modulators           | 75 |

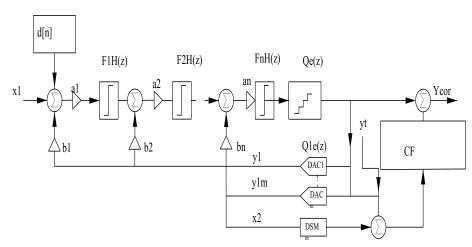

| 2.6   | PHAS  | E NOISE CANCELLATION WITH DIGITAL ERROR CORRECTION | 78 |

|       | 2.6.1 | System stability                                   | 80 |

| 2.7   | RESEA | ARCH GAP AND PROBLEM                               |    |

|       | FORM  | ULATION                                            | 81 |

|       | 2.7.1 | Analysis and evaluation of the FNPLL drawback      | 83 |

|       | 2.7.2 | Conclusion                                         | 87 |

| CHAPT | TER 3 | RESEARCH METHODOLOGY                               | 88 |

| 3.1   | CHAP  | TER OBJECTIVES                                     | 88 |

| 3.2   | ADOP  | TED RESEARCH STRATEGY                              | 88 |

| 3.3   | SIMUI | LATION PROCEDURE                                   | 90 |

|       | 3.3.1 | Frequency Range                                    | 90 |

|       | 3.3.2 | Frequency Divider                                  | 90 |

|       | 3.3.3 | VCO                                                | 91 |

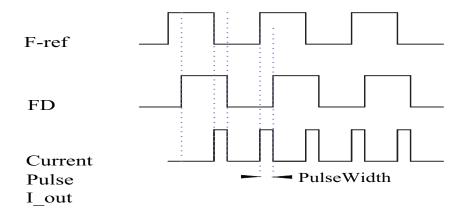

|       | 3.3.4 | Phase Frequency Detector                           | 92 |

| 3.4   | CONC  | LUSION                                             | 97 |

| CHAPT | TER 4 | DESCRIPTION OF PROPOSED                            |    |

|       |       | TECHNIQUE                                          | 98 |

| 4.1   | CHAP  | TER OVERVIEW                                       | 98 |

| 4.2  | DESIGN AND SYSTEM DESCRIPTION                                                                   | 98  |

|------|-------------------------------------------------------------------------------------------------|-----|

| 4.3  | RESOLVING SHORT-PERIODIC CYCLE                                                                  |     |

|      | PROBLEM                                                                                         | 100 |

|      | 4.3.1 Proposed method to resolve short periodic cycles                                          | 100 |

|      | 4.3.2 Maintaining stability of the input data within the in-band                                | 103 |

|      | 4.3.3 Application of higher order $\Sigma\Delta$ modulator and LMS to filter noise              | 105 |

| 4.4  | MODIFIED FOURTH-ORDER CASCADE                                                                   |     |

|      | OF RESONATORS WITH FEEDBACK                                                                     | 108 |

| 4.5  | CONTROLLING THE STABILITY OF THE                                                                |     |

|      | MODIFIED ARCHITECTURE                                                                           | 111 |

| 4.6  | CONCLUSION                                                                                      | 113 |

| CHAP | TER 5 RESULTS AND DISCUSSION                                                                    | 114 |

| 5.1  | CHAPTER OVERVIEW                                                                                | 114 |

| 5.2  | IMPLEMENTATION OF THE PROPOSED                                                                  |     |

|      | ARCHITECTURE                                                                                    | 114 |

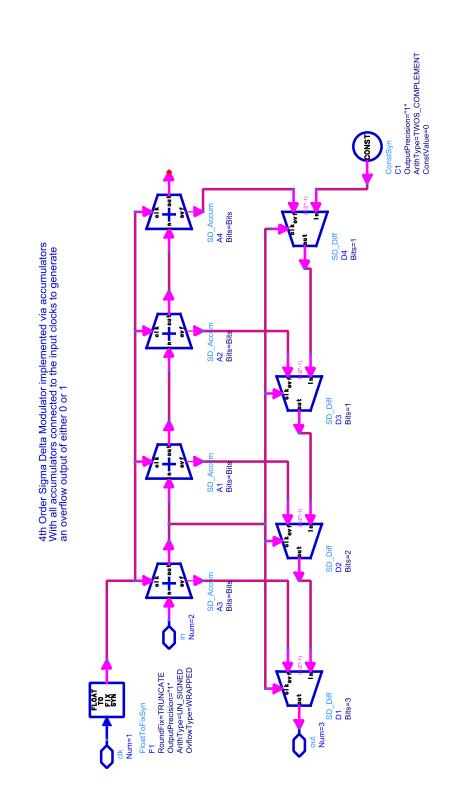

|      | 5.2.1 Implementation and Simulation of $4^{th} order - \Sigma \Delta$ modulator with accumulat- |     |

|      | ors and differentiators                                                                         | 116 |

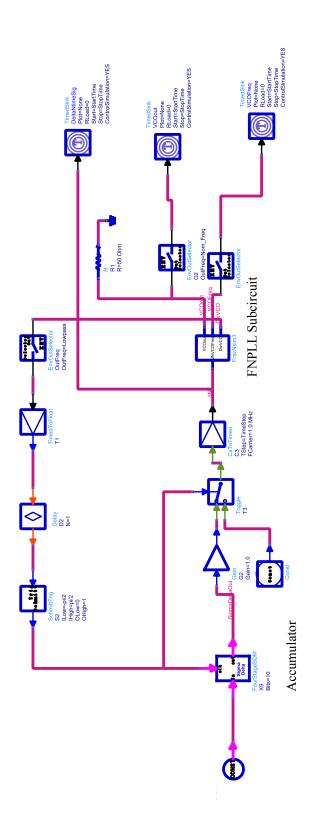

|      | 5.2.2 FNPLL sub-circuit                                                                         | 120 |

|      | 5.2.3 Stabilization of Signal fluctuation within the in-band                                    | 125 |

|      | 5.2.4 Performance Results                                                                       | 127 |

| 5.3  | COMPARISON OF THE SIMULATED RESULTS                                                             |     |

|      | WITH EXISTING LITERATURE                                                                        | 130 |

| 5.4  | VERIFICATION OF THE PROPOSED TECHNIQUE                                                          |     |

|      | ON 3GPP-LTE RECEIVER                                                                            | 132 |

|      | 5.4.1 Phase noise performance                                                                   | 135 |

|      | 5.4.2 BER performance evaluation                                                                | 136 |

| 5.5  | CONCLUSION                                                                                      | 137 |

| CHAP | TER 6 CONCLUSION                                                                                | 138 |

| 6.1  | NEW PN ARCHITECTURE                                                                             | 138 |

| 6.2  | SUPPRESSION OF SPURIOUS TONES                                                                   | 138 |

| 6.3  | ACHIEVED RESULTS                                                                                | 139 |

#### 6.4 RECOMMENDATIONS FOR FUTURE

| RESEA | ARCH                                                                | 139 |

|-------|---------------------------------------------------------------------|-----|

| 6.4.1 | Implementation of the proposed solution on NMLS and RLS             | 139 |

| 6.4.2 | Implementation of the proposed technique on a 65 nm CMOS technology | 140 |

# LIST OF FIGURES

| 1.1  | Phasor diagram representing two noise components at offset $\pm f_n$              | 2  |

|------|-----------------------------------------------------------------------------------|----|

| 1.2  | PN power spectrum                                                                 | 3  |

| 1.3  | Representation of PN components                                                   | 4  |

| 1.4  | Representation of PN                                                              | 6  |

| 1.5  | Depiction of Frequency of Interest and quantization noise.                        | 7  |

| 1.6  | Phase Noise performance metrics.                                                  | 11 |

| 1.7  | Schematic representation of $\Sigma\Delta$ Fractional-N PLL [28]                  | 14 |

| 2.1  | Schematic representation of MSE performance surface simulated at M=2 with filter  |    |

|      | weights $w_0$ and $w_1$ .                                                         | 26 |

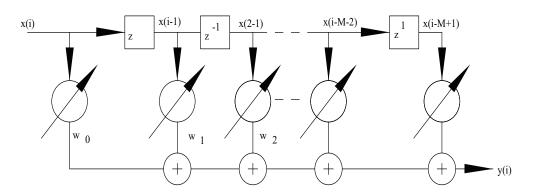

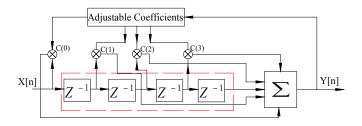

| 2.2  | Schematic representation of M-tap adaptive filter.                                | 27 |

| 2.3  | Schematic representation of ANC with LMS algorithm.                               | 28 |

| 2.4  | Magnitude of Weights $W_0$ and $W_1$ versus Number of Iterations                  | 32 |

| 2.5  | MSE Estimation in dB vs no. of iterations (mu=.005)                               | 33 |

| 2.6  | Schematic representation of adaptive noise canceler with RLS                      | 34 |

| 2.7  | The top plot of Figure 2.7 shows the simulated signal with noise while the bottom |    |

|      | plot shows the convergence characteristic of the RLS algorithm.                   | 36 |

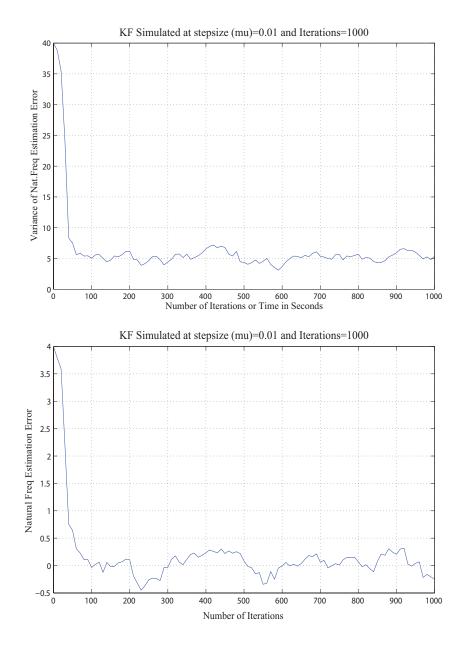

| 2.8  | Signal Error Estimation with Kalman Filter.                                       | 40 |

| 2.9  | Variance of the estimation error.                                                 | 41 |

| 2.10 | MSE of Natural Frequency and it's variance.                                       | 42 |

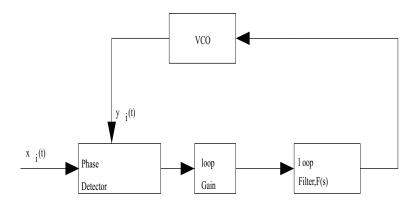

| 2.11 | Basic Model of PLL.                                                               | 44 |

| 2.12 | Noise contribution by individual blocks.                                          | 45 |

| 2.13 | Frequency divisions and reference waveforms [57]                                  | 50 |

| 2.14 | Schematic representation of PLL simulation parameters.                            | 52 |

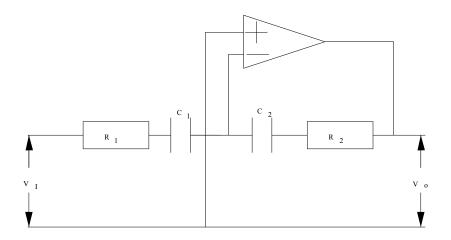

| 2.15 | Schematic representation of active lead-lag filter.                               | 52 |

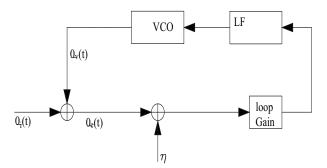

| 2.16 | Structure of PLL phase noise model with additive noise.                           | 57 |

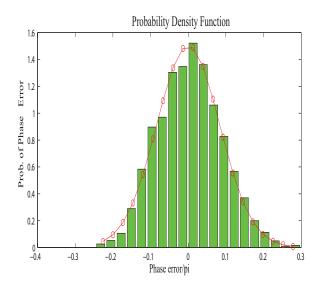

| 2.17 | Probability Density Function of Phase Error                                                     | 59       |

|------|-------------------------------------------------------------------------------------------------|----------|

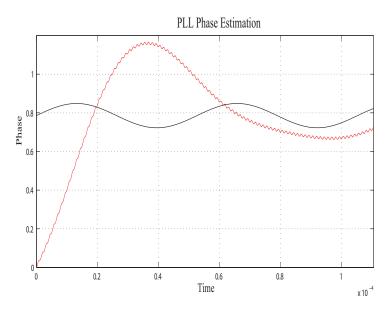

| 2.18 | Simulation of PLL phase error estimation with loop filter parameter                             | 64       |

| 2.19 | Simulation of PLL phase error estimation using an integrator                                    | 64       |

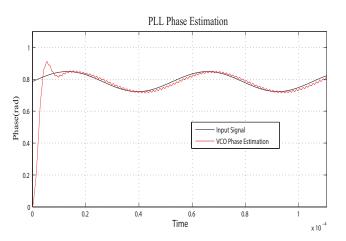

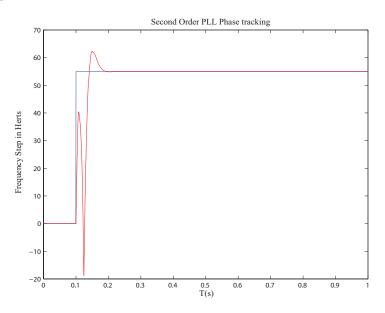

| 2.20 | Phase error tracking with second-order PLL                                                      | 65       |

| 2.21 | Corresponding phase error plot                                                                  | 65       |

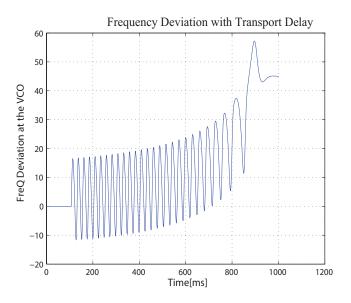

| 2.22 | Frequency deviation with transport delay.                                                       | 66       |

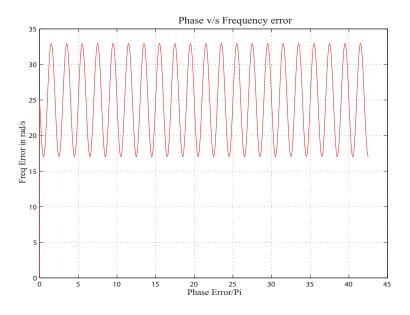

| 2.23 | Phase error versus frequency error plot for first order PLL                                     | 67       |

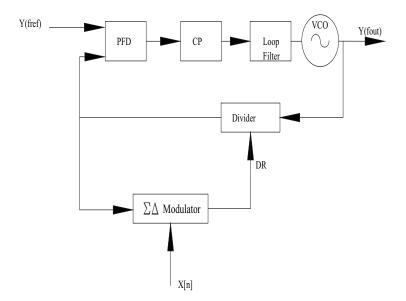

| 2.24 | PLL with digital $\Sigma\Delta$ modulator                                                       | 68       |

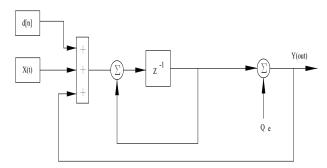

| 2.25 | First Order $\Sigma\Delta$ modulator                                                            | 70       |

| 2.26 | Representation of the first order $\Sigma\Delta$ noise shaper.                                  | 73       |

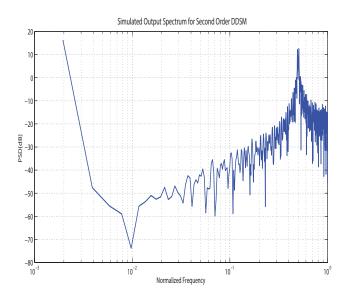

| 2.27 | Simulated Output Spectrum of low order $\Sigma\Delta$ modulator                                 | 73       |

| 2.28 | Third Order MASH 1-1-1 with digital $\Sigma\Delta$ modulator.                                   | 74       |

| 2.29 | Higher-order $\Sigma\Delta$ modulator with error correction function $(-2z^{-1}+z^{-M})$        | 79       |

| 2.30 | Schematic representation of PLL-based fractional-N integer frequency Synthesizer [28].          | 81       |

| 2.31 | Third order MASH 1-1-1 digital $\Sigma\Delta$ modulator.                                        | 83       |

| 2.32 | Simulated output spectrum of low order $\Sigma\Delta$ modulator                                 | 86       |

| 3.1  | Research methodology flow diagram.                                                              | 89       |

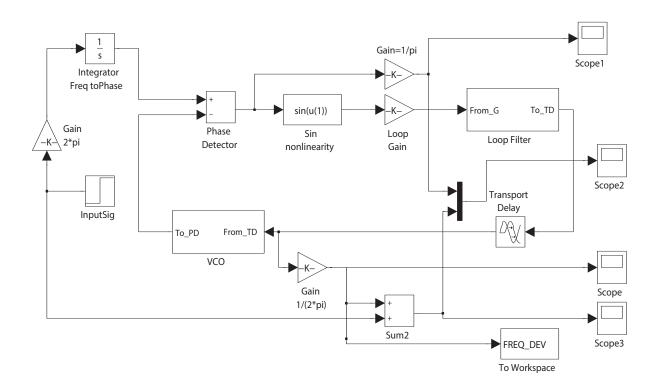

| 3.1  | A phase frequency detector block diagram drawn in Matlab (simlink) package.                     | 89<br>92 |

|      |                                                                                                 |          |

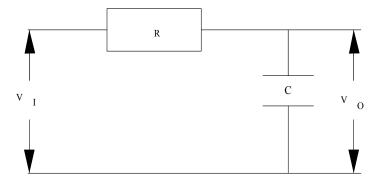

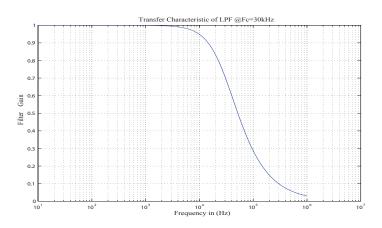

| 3.3  | Transfer characteristic of a low pass filter.                                                   | 93       |

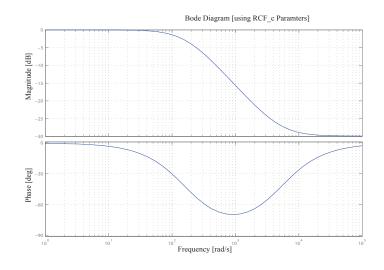

| 3.4  | Bode Plot of a second a transfer function.                                                      | 96       |

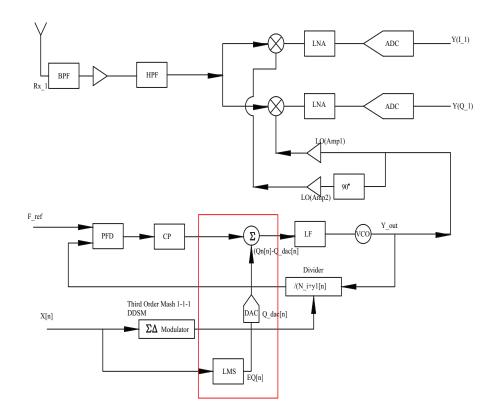

| 4.1  | Proposed FPLL FS $\Sigma\Delta$ modulator and adaptive filtering module                         | 99       |

| 4.2  | Coefficients of Adaptive filtering.                                                             | 100      |

| 4.3  | MSE Estimation in dB vs no. of Iterations ( $\mu = .005$ )                                      | 102      |

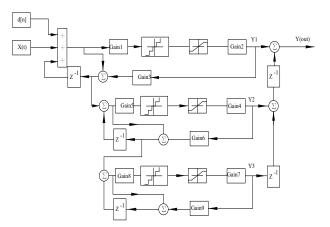

| 4.4  | Multistage (Cascade) $\Sigma\Delta$ modulator.                                                  | 105      |

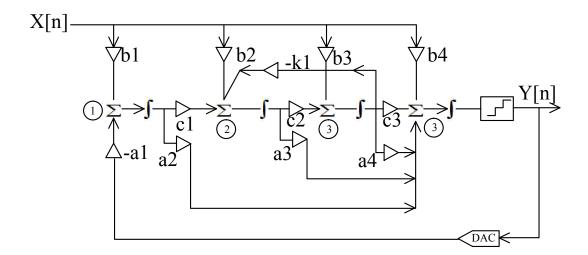

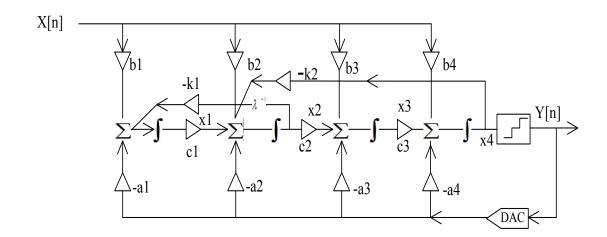

| 4.5  | Fourth-Order CRFB 1-bit $\Sigma\Delta$ modulator.                                               | 108      |

| 4.6  | Modified 4 <sup>th</sup> -order with both NTF coefficients (feedforward, feedback and the coup- |          |

|      | ling coefficients).                                                                             | 109      |

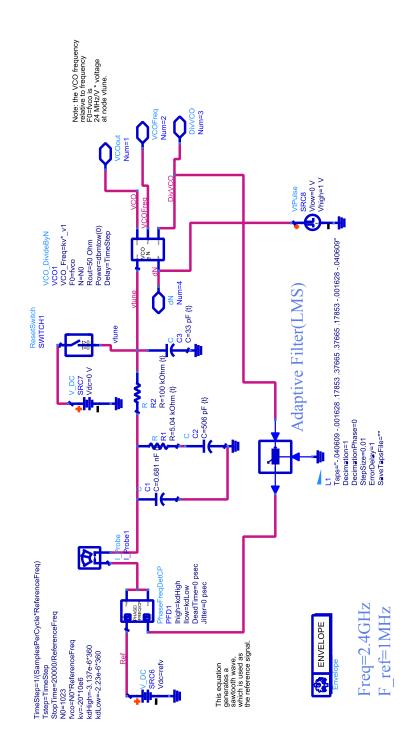

| 5.1  | Implementation of the proposed architecture in ADS                                              | 115      |

| 5.2  | Implementation of $4^{th}$ -order $\Sigma\Delta$ modulator via accumulators                     | 117      |

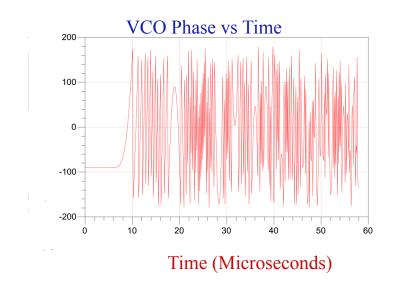

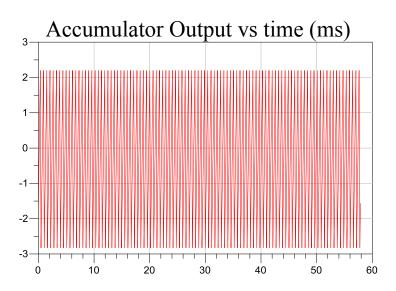

| 5.3  | Phase noise fluctuation at the VCO.                                                             | 118      |

|      |                                                                                                 |          |

| 5.5  | Simulated Output Spectrum of low order $\Sigma\Delta$ modulator                          | 119 |

|------|------------------------------------------------------------------------------------------|-----|

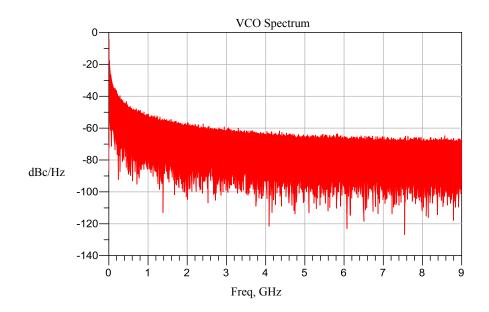

| 5.6  | Simulated output spectrum of a VCO $\Sigma\Delta$ modulator                              | 120 |

| 5.7  | Implementation of FNPLL sub-circuit.                                                     | 121 |

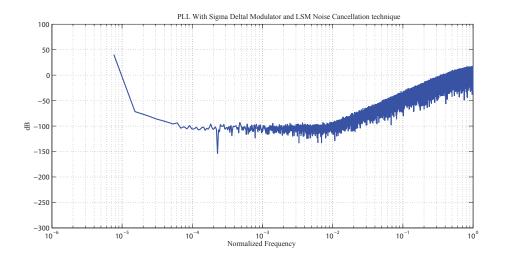

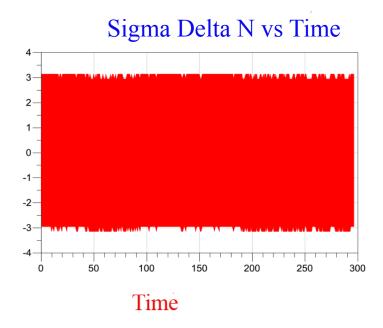

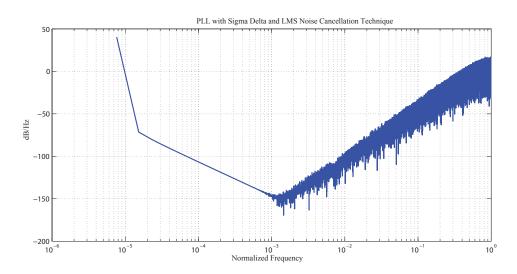

| 5.8  | Sigma N modulator versus time ( $\Sigma\Delta$ input signal)                             | 123 |

| 5.9  | Simulated Output phase noise Spectrum of FNPLL with $\Sigma\Delta$ modulator and LMS Ad- |     |

|      | aptive                                                                                   | 123 |

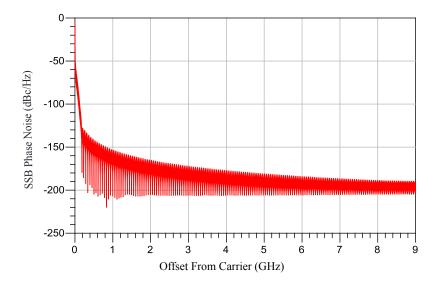

| 5.10 | Simulated Output Phase Noise Spectrum of FNPLL with $\Sigma\Delta$ modulator and LMS     |     |

|      | Adaptive filter                                                                          | 124 |

| 5.11 | NTF poles and zeros location within the Unit circle                                      | 126 |

| 5.12 | Quantization Noise of NTF with different coefficients.                                   | 127 |

| 5.13 | Output Spectrum of NTF zeros and poles Optimized Sigma Delta Modulator simu-             |     |

|      | lated at different values of OSR                                                         | 129 |

| 5.14 | Block diagram of a 3GPP-LTE wireless receiver.                                           | 132 |

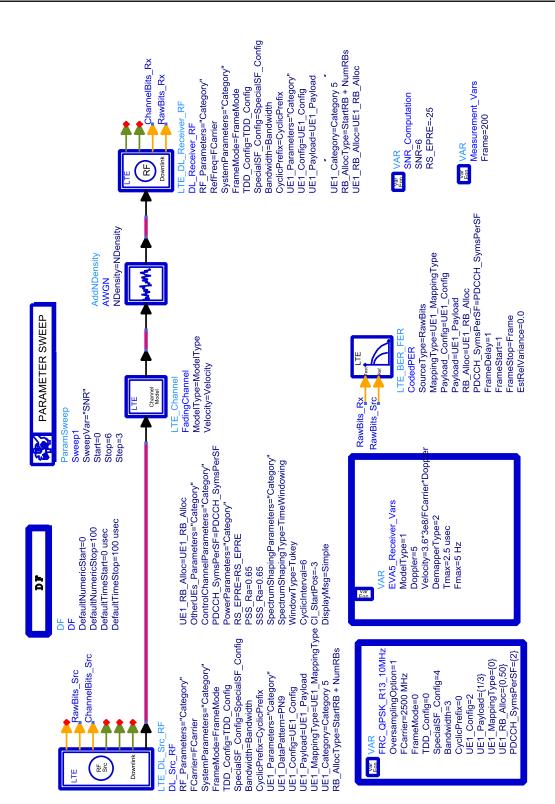

| 5.15 | ADS 3GPP-LTE receiver test bench.                                                        | 134 |

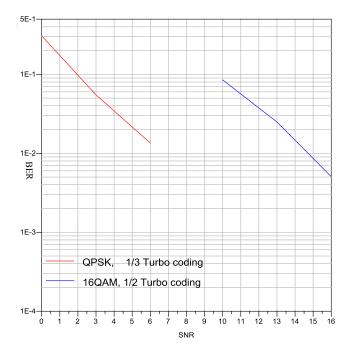

| 5.16 | BER Performance evaluation of the proposed model on Agilent ADS LTE DL source.           | 136 |

### **CHAPTER 1** INTRODUCTION

### **1.1 BACKGROUND**

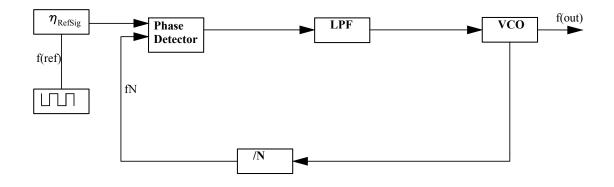

The emergence of phase noise (PN) at the transceiver ends affects the performance of modern wireless communication systems negatively. Wireless communications systems use frequency synthesizers to generate carrier signals that contain useful information to be transmitted. Frequency synthesizers consist of signal generator components (voltage control oscillator (VCO), local oscillator (LO), Phase Frequency Detector (PFD), Charge-Pump (CP) and Loop Filter (LF)). The LO generates unwanted time-varying and randomly distributed waveforms that form the basis of the PN errors that emerge in the baseband signal as an additional phase and amplitude modulated waveform propagated through a dissipative Additive White Gaussian Noise (AWGN) channel.

Estimating the received data sequence in the presence of PN and additive white noise poses major challenges to the receivers and it is a problem that requires attention to enhance the performance of modern wireless communication system.

The signal to noise ratio (SNR), which provides immunity to a wireless system in a multipath fading environment, gets impacted by the emergence of PN in the transceiver ends. The reduction of SNR causes the wireless communication systems to degrade as the bit error rate of the system increases. PN errors also affect symbol or data sequence synchronization, which causes the receiver to misinterpret the received data. It is for these reasons that PN remains a major problem in modern wireless communication and it is very critical for researchers and design engineers to have a better understanding of the behavior of PN to be able to design wireless communication systems with low levels of PN.

#### 1.1.1 Fundamentals of Phase Noise

PN can be realized as nothing else but the short-term random fluctuations in the phase or frequency of a signal, which can be expressed in terms of a sinusoid waveform as;

$$V(t) = \left[V_o + \lambda(t)\right] \cos\left(2\omega_o t + \phi(t)\right).$$

(1.1)

The  $V_o$ ,  $\lambda$ ,  $\omega$  and  $\phi$  terms in equation (1.1) are defined as follows;

١

- $V_o$  = The Peak amplitude in Volts

- $\lambda(t)$  = Time-varying amplitude or noise amplitude.

- $\omega_o$  = Natural frequency of the signal in rad/sec.

$\phi(t)$  = Time-varying PN or phase fluctuation of the output signal.

(1.2)

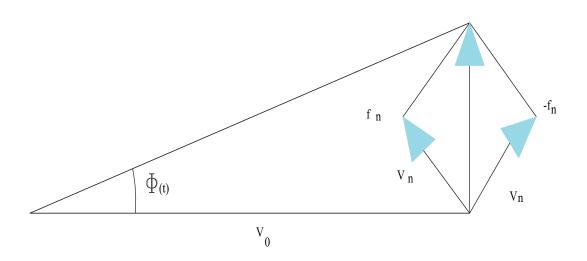

**Figure 1.1:** Phasor diagram representing two noise components at offset  $\pm f_n$ .

From Equation (1.1) and Figure 1.1 it is possible to model the PN contribution as narrowband Frequency modulation (FM), where the corresponding phase modulation is given by [1];

$$\phi(t) = \frac{2V_n \sin(\omega_n t)}{V_o}$$

$$= \frac{2V_n \sin(2\pi f_n t)}{V_o}.$$

(1.3)

If the sinusoidal waveform in (1.1) is assumed to follow a random process, the PN can be defined in terms of its power spectral density function as;

$$L(f_m) = \frac{S_v(f_m)}{\lambda^2(t)/2}.$$

(1.4)

$S_v(f_m)$  = The Power Spectral Density of the sinusoidal signal , V(t).

$\lambda(t) =$  Time-varying amplitude or noise amplitude.

(1.5)

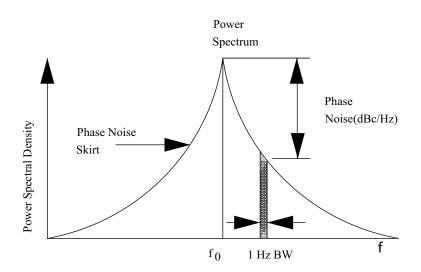

Figure 1.2: PN power spectrum.

As shown in Figure 1.2, PN can be expressed as a ratio of noise contained in a 1-Hz bandwidth at a certain frequency offset,  $f_m$ , to the amplitude of the oscillator signal with a carrier frequency  $f_o$ .

The power spectral density of a single side-band noise of Figure 1.2 is given by;

$$(\Delta \omega) = 10 \log \left[ \frac{P_{SSB}(\omega_0 + \Delta \omega, 1Hz)}{P_{signal}} \right].$$

(1.6)

where

$P_{SSB}(\omega_0 + \Delta \omega, 1Hz) =$  SSB power of an output frequency spectrum with respect to  $\Delta \omega$  measured from 1Hz  $P_{signal} =$  Total carrier power of the output spectrum

(1.7)

#### 1.1.2 Components of PN

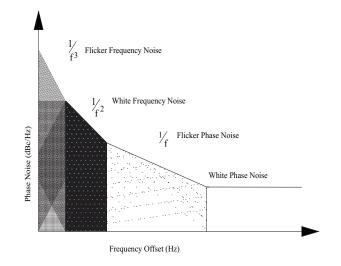

Various PN components are normally modeled with the Leeson model, which suggests that PN consists of white noise, flicker PN, random phase walk, flicker frequency noise and random frequency walk. The Leeson model is given by [2, 3];

$$L(fm) = 10\log \frac{FKT}{2P_{avg}} \left[ 1 + \frac{f_c}{f_m} + \left(\frac{f_o^2}{2fmQ}\right)^2 \left(1 + \frac{f_c}{f_m}\right) \right]$$

=  $10\log \frac{FKT}{2P_{avg}} \left[ 1 + \frac{f_o}{f_m} + \frac{1}{f_o^2} \left(\frac{f_o^2}{2Q}\right)^2 + \frac{f_o}{f^3} \left(\frac{f_o}{2Q}\right)^2 \right].$  (1.8)

Figure 1.3: Representation of PN components

The Leeson model suggests that PN may be improved by increasing the signal power, reducing the device flicker frequency  $(f_o)$  and the half bandwidth term  $(f_o/2Q)$ .

However, the main challenge with PN is that oscillators tend to amplify any noises that are closer to their harmonics and oscillation frequency, which makes it more complicated for modern communication systems that use multiple transmitters and receivers.

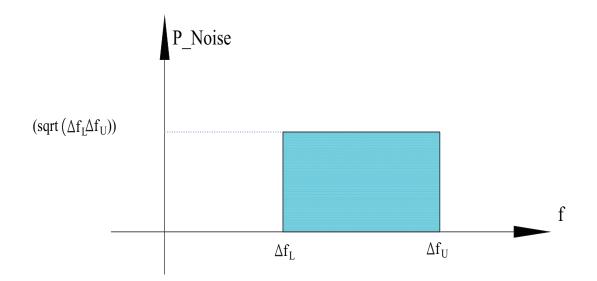

The single side-band (SSB) noise spectral density can be used to determine the maximum allowable PN required to achieve the desired signal-to-noise ratio (SNR) by estimating the in-band noise relative to the carrier using Figure 1.4 as follows;

$$P_{noise} = \int_{\Delta f_L}^{\Delta f_U} (\Delta f) d(\delta f).$$

(1.9)

The slope  $(1/f^2)$  can be determined from Figure 1.3 as  $(\Delta f) = k/\delta f^2$  such that;

$$P_{noise} = \int_{\Delta f_L}^{\Delta f_U} \frac{k}{\Delta f} d(\Delta)$$

=  $\frac{k(\Delta f_U - \Delta f_L)}{\sqrt{(\Delta f_L - \Delta f_U)^2}}$

=  $(\sqrt{\delta f_L \times \delta f_U})(\Delta f_U - \Delta f_L).$  (1.10)

If the minimum SNR is known, the maximum allowable PN can be determined from Equation (1.11);

$$10\log(P_{noise}) = 10\log(P_{signal}) - 10\log(SNR) - 10\log(P_{Interfere} - 10\log(\Delta f_U - \Delta f_L)).$$

(1.11)

#### Figure 1.4: Representation of PN.

#### 1.1.3 Frequency Synthesizers

Frequency synthesizers that are used to generate carrier waves employ local oscillators that use  $\Sigma\Delta$  fractional PLL to eliminate phase noise components in the wide-band (GHz) frequency range. The wide-band PLL is very useful in many applications due to its ability to filter the flicker noise  $(\frac{1}{f^3})$  generated by the oscillator component. The range of frequencies generated by the fractional PLL are used for up-converting and down-converting the transmitted and received data sequences.

There are two types of fraction PLL synthesizers that are used to generate a wide range of frequency bands, namely;

- Interger-N PLL

- Fractional-N PLL

#### 1.1.3.1 Integer-N PLL

The desired frequency output  $(f_{vco})$  is generated by multiplying the reference frequency with the negative feedback path as follows;

$$f_{vco} = f_r \times N. \tag{1.12}$$

#### 1.1.3.2 Fractional-N Frequency synthesis

The multiplication of the reference frequency by an integer N has some unintended consequences as it raises the phase margin of the signal by a factor of  $20\log(N)$  dB. For example, of a channel spacing of 30 kHz (for cellular) is assumed, a noise of about 90 dB will be added to the PFD ( $20\log(30,000)$ ). To avoid this situation a fractional-N synthesis is adopted, which uses division by fractional ratios as opposed to integer ratios.

#### 1.1.4 Sigma Delta Quantization Noise

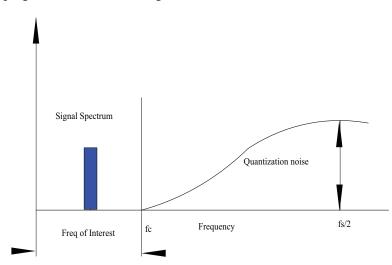

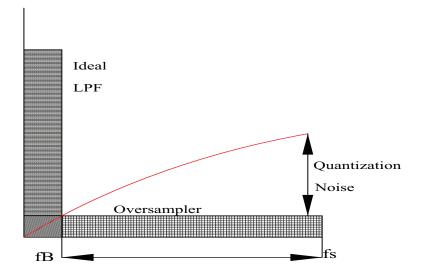

The fundamental principle of quantization noise (error) is depicted in Figure 1.5, which shows a classic noise shaping characteristics of a sigma delta modulator.

Figure 1.5: Depiction of Frequency of Interest and quantization noise.

The quantization noise is eliminated by the implementation of the digital filter (low pass filter) at the end of the signal delta modulator, which retains the signal of interest and eliminates quantization noise by pushing them to the higher frequency portion.

#### **1.1.5** Performance criteria for PN reduction techniques

Several studies conducted in the field of noise cancellation techniques employed the mean square error (MSE), convergence rate, tracking capability and normalized projection misalignment (NPM) as performance measures [4, 5, 6].

#### 1.1.5.1 Mean Square Error

If the source signal is assumed to be uncorrelated with the emerging random sequence noise, the filter algorithm such as adaptive filter, will seek to minimize the square of the error output. The adaptive filter reduces the noise part of the contaminated signal by subtracting the undesired signal from the main or reference signal. The mean square error (MSE) for the convergence parameters of the error and estimated signals is statically modeled as;

$$MSE = \frac{1}{N} \sum_{n=0}^{N} \left[ x(n) - (\hat{x}) \right]^2.$$

(1.13)

where

x(n) = is the original signal.

$(\hat{x}) =$  is the filter output.

The adaptive algorithm seeks to minimize the MSE between the error and the estimated signal. An algorithm is deemed to have better performance if it convergences faster at less MSE. Larger MSE values implies that the algorithm fluctuated about the filter coefficients after undergoing a high sample rate or iteration number.

#### 1.1.5.2 Convergence rate

Many PN cancellation techniques that are based on adaptive algorithms are said to have high performance if they converge faster within few iterations [5]. In other words, it is desirable to design an algorithm that achieves the steady state MSE within few iteration.

#### 1.1.5.3 Tracking capability

The tracking capability is a performance measure that indicates the ability of the algorithm to track statistical variations within a non-stationary environment.

#### 1.1.5.4 Normalized Projection Misalignment (NPM)

The normalized projection misalignment (NPM) performance criterion provides a means of measuring separation between the estimated and original impulse responses. The closeness between these two impulse responses can be determined by Equation(1.14).

$$NPM(n) = 20 \log \left[ \frac{1}{\|y\|} \frac{\|y - y^T \hat{y}(n)\|}{\hat{y}^T \hat{y}(n)} \right].$$

(1.14)

where

y = The impulse response to the original signal to be estimated.

A well designed filter should approximate 0 dB NPM, meaning that the estimated and original impulses are closely aligned.

#### 1.1.5.5 Computational complexity

Although many algorithms perform well at a cost of high complexity, it is normally desirable to reduce the complexity as higher computational complexity requires higher storage capacity which comes at a cost. Another problem of higher computational complexity is that it takes longer computation time, which may result in some errors and affects the quality of the proposed solution.

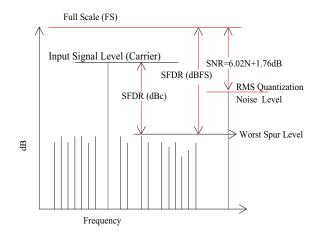

#### 1.1.5.6 SNR and SNDR

The SNR and signal to noise and distortion ratio (SNDR) are important performance metrics that are widely used in the performance analysis of  $\Sigma\Delta$  modulators. The SNR is used to measure the sensitivity of the transceiver. The greater the difference between the signal power and the noise power the better the performance of the transceiver sensitivity. This justifies why it is necessary to have a transceiver with higher SNR for better performance. SNDR is even a better performance metric than SNR in that it takes signal harmonics into consideration and compares them with the power of the noise signal or residual signal. The performance level of these metrics are depicted in Figure 1.6.

The spurious free dynamic range (SFDR) is the minimum level of signal power that can be identified from a dominant interfering signal. As shown in Figure 1.6, the SFDR can be determined as the difference between the root mean square (rms) value of the carrier power (dBc) and the rms value of the next signal with the highest visible spur. This implies that dynamic range is free of spurious frequencies. SFDR is normally represented as full-scale (dBFS) or with the actual amplitude of the carrier (dBc). The SNDR is another important metric which is given by the ratio of the rms signal amplitude to the mean value of the root-sum-square (rss) of all harmonics and spectral components. The significance of the SNDR is that it includes all components that cause signal distortion. SNDR is almost

Figure 1.6: Phase Noise performance metrics.

the same as the SNR except that the frequency harmonics are excluded from the SNR calculation, which makes it easier to deal with noise terms only. SNR is used to measure the noise performance of the receiver by comparing the signal and noise level of the known signal level [7].

The effective number of bits (ENOB) is another metric that is used to measure the dynamic range where the associated bits are used to specify the system resolution. The effective number of bits (ENOB) is given by;

$$ENOB = \frac{SNDR - 1.76dB}{6.02}$$

(1.15)

$$SNR = 6.02 \times ENOB - 1.767.$$

where the 6.02 term is used to convert decibel  $(\log_{10} x)$  to  $(\log_2 x)$ , i.e.,  $(6.02 = 20 \log_2)$ .

# **1.2 RELATED WORK**

Multi-carrier systems are hailed as high capacity systems that enhance the data rates of broadband networks (3G, HSPA+, and LTE). However they are very sensitive to PN as they cause severe signal degradation in multipath fading environments [8]. In [9, 10, 11, 12] the impact, influence and effects of PN on multi-carrier system were analyzed where it was shown that PN errors remain the major cause of impairments in wireless communication systems. In [13] the term PN is described as the short-term random fluctuations of a signal caused by the transmitter and receiver oscillators. The lack of synchronization at both the receiver and transmitter oscillator causes random PN that can be described by the Brownian motion process where the zero mean, line-width and variance terms of the PN are discussed in [13]. PN causes sub-carrier signals to lose orthogonality patterns that results in common phase error (CPE) and inter-carrier interference (ICI) [13], which causes interference among sub-carriers and reduce the performance of overall system. The correction techniques that cancels CPE in multi-carrier systems such as orthogonal frequency division multiplex (OFDM) was presented in [11], which increases the theoretical SNR marginally. However this technique is limited by the radio symbol rate, which makes it difficult to correct LO PN for the system whose LO's frequency offset is closer to the actual radio symbol rate.

Several noise cancellation techniques (such least mean square, recursive least mean square, Kalman filter, phase locked loop) have been proposed to mitigate the effect of PN on multi-carrier systems [14, 15, 16, 17, 18, 19].

Recently Kaned [20] investigated the effect of PN on the equalization of communication channels using least mean square (LSM) and recursive least square (RLS), where it was observed that LSM and RLS techniques improved the bit error performance (BER) of the communications when compared to the system that operates without any PN correction technique. Awachat and Godbole [21] evaluated the performance of LMS algorithm as a technique for noise cancellation in speech signals. LMS has been shown to be more stable within the in-band. Although LMS has the desirable stability characteristic with less signal fluctuation in the in-band, it takes some time to filter the noise completely. This results in a lengthy convergence rate that can be improved by varying the step size of the algorithm through trial and error. In a bid to improve the performance of the LMS, an RLS technique was introduced and later evaluated by Dhubkarya *et al.* [4]. In their investigations, Dhubkarya *et al.* simulated and evaluated the performance of adaptive algorithms (RLS and LMS) in terms of the performance

criteria (mean square error, convergence rate, computational complexity, stability and signal to noise improvement) and observed that RLS estimates errors quicker with a faster convergence rate albeit at a cost of high complexity.

Another adaptive filter that had been used as a noise cancellation technique is the Kalman Filter [22], a technique that was designed on the premise of the recursive least square error (RLSE) with low and efficient computational complexity. Recent studies by Bhattacharjee and Das [22] on the performance evaluation of the Wierner and Kalman Filters show that Kalman Filter is an efficient noise reduction technique although it achieved significant results when used in combination with the Wierner Filter.

In [14], a decision directed Extended Kalman Filter (EKF) was proposed for tracking the PN errors in wireless sensor networks due to its ability to filter and track random signal, where it was found that the BER performance results show some encouraging performance as they were close to that of synchronous case. However, a fundamental drawback of this technique is that it is limited to linear and Gaussian assumptions [14]. Although the Kalman Filter is widely used to correct and estimate PN errors it does not achieve optimal performance due to the complex receiver structure that makes it difficult to align all model coefficients. While the EKF might be an ideal method to deal with PN caused by channel imperfections, it lacks some intelligence to correct PN errors caused by the imperfections of the local oscillators in the transmitter and receiver ends respectively [23].

Another technique that estimates the carrier phase from the received signal is the Phase-Lock Loop (PLL). PLL was proposed to filter unwanted PN in multiple channel applications [24]. Since PLL schemes are based on sets of linear equations, interpreting and analyzing the results of PLL in terms of physical behavior of the system becomes very difficult and time consuming due to the structure of their complicated and difficult designs [25]. Although PLL technique is very popular in correcting PN errors, it's suitability to correct PN errors has been widely applied in SISO systems and to some extent in multicarrier systems such as OFDM.

The effect of PN can be eliminated by improving the performance of the voltage control oscillator (VCO). Unfortunately, the improvement of the VCO tends to be a costly exercise, which further strengthens the case for the proposal of a robust PN correction method that is simple to implement.

The squaring loop carrier phase recovery technique discussed in [26] tracks the phase of the incoming

signal perfectly. However it should be pointed out that the significant BER results achieved by this technique were based on simple modulation schemes (such as BPSK, PSK) and have not been tested for a multicarrier system.

A low noise-phase modulator with a finite impulse response filtering and sigma delta ( $\Sigma\Delta$ ) modulator fractional-N Phase locked loop (FNPLL) frequency synthesizers was introduced and investigated in [27] and found to be capable of generating carrier waves with well-defined carrier frequencies that are free of spurious tones. The requirement to design systems that have less or no spurious tones with the frequency of interest necessitated further frequency synthesizer's evolution and more advanced architectures that seek to minimize spurious tones to the lowest level.

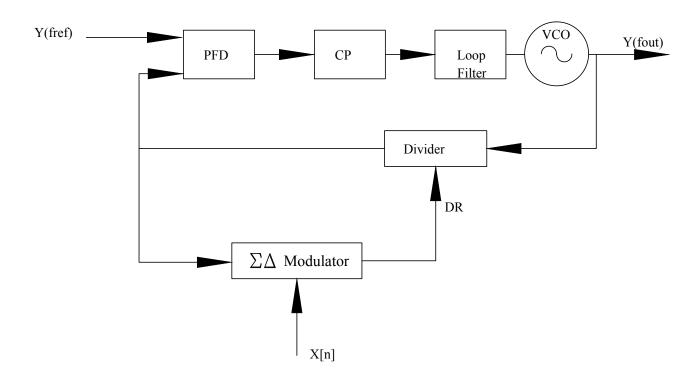

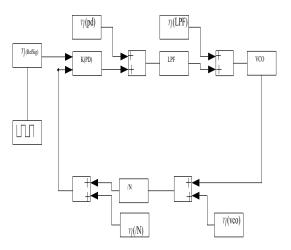

As shown in Figure 1.7, the output of the  $\Sigma\Delta$  modulator controls the divide modulo, which realizes the fractional division and converts local oscillator (LO) frequency and frequency step to fractional multiples of reference frequency, which is normally tuned within the frequency of interest. The signal is controlled by the fractional division, D, which is obtained from the output of the  $\Sigma\Delta$  modulator's accumulator.

Figure 1.7: Schematic representation of  $\Sigma\Delta$  Fractional-N PLL [28].

The reference output is determined by assuming that the synthesizer divides the reference output by  $D_0 + 1$  every  $C_0$  cycles and by  $D_0$  the rest of the times, the average ratio will be  $D_{avg} = D_0 + \frac{1}{C_0}$  and the resulting VCO reference output will be given by Equation (1.16);

$$Y_{fref} = \left[ (D_0 + 1)(\frac{1}{C_0}) + N(1 - \frac{1}{C_0}) \right]$$

=  $\left( D_0 + \frac{1}{C_0} \right) Y_{fout}.$  (1.16)

Equation (1.16) shows that the output bit stream is cyclical and repetitive, which may result in unnecessary visible harmonics.

This approach has a drawback where the output is completely locked to the reference frequency of the PLL. It is also noted in [29] that an attempt to reduce the reference frequency has undesired consequences as it increases settling time, which in turn decreases the bandwidth of the overall system and introduces system instability. When the bandwidth is reduced significantly it becomes difficult to flatten and reduce noise with the in-band or frequency of interest.

The  $\Sigma\Delta$  modulator as shown in Figure 1.7 was included to take advantage of its ability to move the quantization noises away from the frequency of interest, which in turn can be removed by the loop filter (LF). The FNPLL's ability to handle the additional  $\Sigma\Delta$  component gives them the flexibility to operate within a more flexible wider range of step-sizes that result in better control and elimination of spurs within the frequency of interest. However, one fundamental drawback that needs to be pointed out is that when implemented at low-order  $\Sigma\Delta$ , FNPLL's capability to shape and randomize noise is minimal.

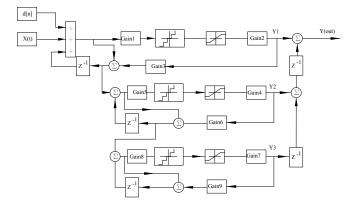

Generally, higher order  $\Sigma\Delta$  modulators have better noise shaping characteristics and they are often used to shift the quantization noise from the frequency of interest to higher frequencies. Their main constraint is that the signal is highly dependent on the gain of the quantizer, where a high gain (that is introduced by the digital to analog converter) normally degrades the smooth noise-shaped spectra. A proposal was made in [30] to control the gain of the quantizer, which employs LMS algorithm to match the gain adaptively. This technique controls the gain effectively when the LMS bandwidth is low enough to enable the quantization error-term to be suppressed.

A technique that optimizes the gain and loop coefficients of the  $\Sigma\Delta$  modulator architecture's transfer

functions was proposed in [31], which allows for the selection of the suitable noise transfer function that gives the required SNR. A major advantage of introducing poles in the signal band is that the out-of-band gain (OBG) can be reduced by moving and adjusting poles within the unit circle [32]. It is through this technique where loop filters are treated as quantization noise and get minimized by adjusting the coefficients of the loop filters. However, this technique has a challenge in that suppressing quantization noise in low frequency bands may results in spurs emerging at higher frequencies, which normally causes signal instability.

| Summary of reviewed PN Cancellation Techniques |                                    |                        |                  |  |

|------------------------------------------------|------------------------------------|------------------------|------------------|--|

| Authors                                        | Techniques                         | Achieved PN $(dBc/Hz)$ | Output Frequency |  |

| [33]                                           | Single VCO +Div/MUX                | -111 @ 5 GHz           | 6.25 GHz         |  |

| [34]                                           | PLL DSS                            | -90 @ 10 kHz           | 2.06 – 2.16 GHz  |  |

| [35]                                           | Analog Feed-Forward Adapt-         | -105 @ 1 MHz           | 5 GHz            |  |

|                                                | ive PN cancellation                |                        |                  |  |

| [36]                                           | Dual Path Control Scheme           | -113 @ 1 MHz           | 5 GHz            |  |

|                                                | with smoothed Varactors            |                        |                  |  |

| [27]                                           | FIR with $\Sigma\Delta$ Modulators | -120 @ 400 kHz         | 1.8 GHz          |  |

| [37]                                           | Fractional-N Frequency Syn-        | -92.27 @ 600 kHz       | 832-936 MHz      |  |

|                                                | thesizer                           |                        |                  |  |

| [38]                                           | Digital Fractional-N PLL           | -123 @ 1 MHz           | 3.5 GHz          |  |

|                                                | based on 2nd Order FDC             |                        |                  |  |

| [39]                                           | Hybrid Fractional-N Fre-           | -113 @ 1MHz            | 2.41 GHz         |  |

|                                                | quency with Noise Filtering        |                        |                  |  |

| [40]                                           | Cascaded PLL with an               | -53.9 @ 50 MHz         | 2.55 – 3 GHz     |  |

|                                                | Integer-N digital bang-bang        |                        |                  |  |

|                                                | PLL                                |                        |                  |  |

| [41]                                           | Fractional-N Synthesis for         | -120 @ 1 MHz           | 900 MHz          |  |

|                                                | UHF Transceiver                    |                        |                  |  |

**Table 1.1:** Phase noise performance of reviewed techniques.

Table 1.1 summarizes the PN performances of the existing techniques. It is important to note that the techniques presented in [35], [36], [38], [39] and [41] were based on 1 MHz offset frequency. The techniques presented in [38] and [41] performed better than others as they achieved low levels of PN of about -123 and -120 dBc/Hz respectively at 1 MHz frequency offset.

# **1.3 RESEARCH HYPOTHESIS**

The hypothesis of this masters study was framed as follows: "Is it possible to reduce the spurious tones within the frequency of interest to achieve a low phase noise level that is better than those achieved by the existing phase noise correction techniques?" Simulation results of the proposed phase noise cancellation technique were expected to show a phase noise improvement with the minimal spurious tones within the frequency of interest when compared to the existing techniques..

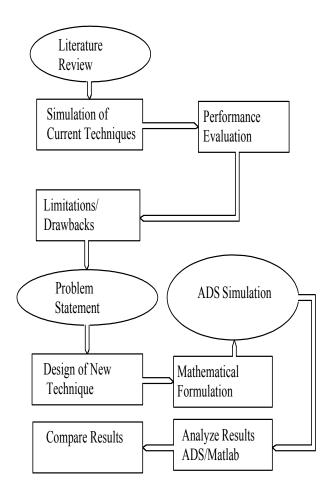

# **1.4 RESEARCH METHODOLOGY**

To gain insight into the limitation of the conventional phase noise cancellation techniques, an in-depth literature review on current techniques was conducted. Existing techniques were analyzed where the simulation results were used to identify the weakness or limitations of these techniques (research gap).

Several modifications were made to the existing architectures, which resulted in a completely new model that seeks to improve and enhance the limitations of the existing techniques. The proposed technique was implemented and tested on the Agilent ADS LTE Downlink (DL) test set-up [42], which is a leading electronic design software tool for high speed digital automation. ADS has built in modules LTE standards-based design and verification with wireless libraries and circuit-system-EM co-simulation in an integrated platform. The simulations results were compared with those of the existing techniques to check if there is an improvement that is realized.

# **1.5 RESEARCH CONTRIBUTION**

Detailed literature review on the cancellation of phase noise within the frequencies synthesizers was conducted, which forms part of the body of knowledge in the area of wireless communication systems.

The following distinct contributions were made:

• A comprehensive literature review was conducted where the limitations of the existing PN schemes were presented.

- Key performance metrics that are used to evaluate the performance of PN were reviewed.

- Theoretical analysis and performance evaluations of current phase noise techniques were conducted.

- Specification (design parameters for the proposed system) for the implementation of a PN correcting techniques developed.

- A new architecture that produces a clean spectrum without spurious tones is presented.

- Existing literature resolves the short periodic cycle by using a random dither sequence to disrupt the periodic cycles [43]. Although this process results in smooth noise-shaped spectra it adds noise to the spectra. The proposed approach uses an adaptive filtering algorithm to control the data sequence, which allows flexibility even at wider bandwidth.

- The mathematical expressions for the proposed architecture are formulated and presented in this dissertation.

- The proposed technique was simulated and tested for a long-term evolution (LTE) communication system where it is shown to outperform the existing techniques.

# **1.6 PUBLICATIONS**

The following articles were authored based on the work presented in this dissertation;

#### **1.6.1** Conference Article

The following published peer reviewed paper won the best paper award at the IEEE AFRICON 2015 conference held at the United Nations Conference Center (UNECA) in Addis Ababa, Ethiopia from 14-17 September:

(i) P.R. Munyai and B.T. Maharaj, "On the Improvement of phase noise errors in wireless communication systems"; *12th IEEE AFRICON Conference on Communications Systems*,14-17 September, 2015.

#### 1.6.2 Journal Article

The following journal article was submitted to the International Journal of Communication systems:

(i) P.R. Munyai and B.T. Maharaj, "A Phase Noise Improvement Technique For Wireless Communication System", *International Journal of Communication systems*, November 2016 (in review).

# **1.7 DISSERTATION OUTLINE**

Chapter 1 (Introduction) a comprehensive background to phase noise concepts and its components. The fundamentals of phase noise and metrics that are used to evaluate the performance of wireless communication systems are presented. This chapter also covers a comprehensive literature review of the published journal articles on phase noise cancellation techniques.

Chapter 2 (Phase noise cancellation techniques) presents the analysis of existing phase noise cancellation techniques that are based on adaptive filtering (MSE, LSM, RLS) algorithms. The performance results of these techniques are analyzed, compared and discussed in this chapter. The chapter also presents phase noise cancellation techniques that are based on phase-locked loop (PLL) concepts, which include  $\Sigma\Delta$  modulators embedded on PLL architectures.

Chapter 3 (Research Methodology) describes the research strategy that was followed to achieve the objective and hypothesis of this research. This chapter discusses and presents all parameters (Frequency range, frequency divider, voltage control gain of the VCO, the gain at the PFD, capacitor and resistor values of the loop filter, etc) that were used during simulation.

Chapter 4 (Description of proposed technique) discusses the architecture and circuit design of the new technique. This chapter presents all mathematical expressions that were formulated to describe the behavior of the proposed architecture.

Chapter 5 (Discussion of Results) presents the schematic layout of the proposed model as implemented and simulated in Advanced Design System (ADS). This chapter also presents the comparison table of the achieved results and those obtained from the existing literature.

Chapter 6 (Conclusions and recommendations for future research) summarizes the achieved objectives, hypothesis and solved problem statement. This chapter concludes by suggesting possible areas for future research.

# CHAPTER 2 PHASE NOISE CANCELLATION TECHNIQUES

### 2.1 CHAPTER OBJECTIVES

Several studies were conducted on the performance of phase noise cancellation techniques that are based on adaptive filtering (such as mean square error, least mean square, recursive least mean square Algorithms) [20] and phase locked loop methods [4]. This chapter presents the analysis of the existing phase noise cancellation techniques. Furthermore, the limitations and challenges of the existing techniques will be highlighted.

### 2.2 ADAPTIVE FILTER NOISE CANCELER

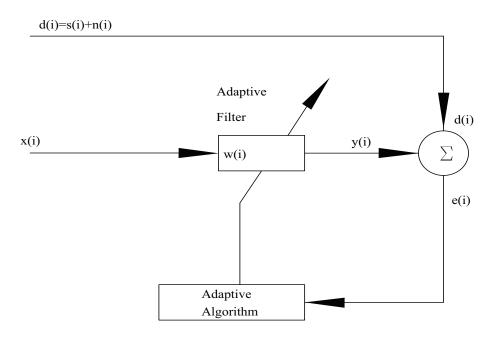

The main aim of the adaptive filter noise canceler (ANC) is to minimize the difference between the desired and output signal, e(i) = d(i) - y(i), where the computed difference is passed through the adaptive algorithm stage to adjust the time-varying tap weights that can be expressed in vector form as;

$$w(i) = [w_0(i), w_1(i), \cdots, w_{M-1}(i)]$$

(2.1)

The input and output data sequences are given by;

$$x(i) = [x(i), x(i-1), \cdots, x(i-M+1)]^T$$

$$y(i) = \sum_{i=0}^{M-1} w_m(i) x(i-m)$$

$$= w^T(i) x(i).$$

(2.3)

where

$$M$$

= Number of adaptive tap filters

$w$  = Filter coefficients

Now the errored-signal can be tracked by making use of the following expression

$$e(i) = d(i) - w^{T}(i)x(i).$$

(2.4)

where

x(i) = Column vectors of the input signal that are updated iteratively until e(i) reaches the minimum value.

#### 2.2.1 Performance criteria

The most widely used criterion for judging the performance of the adaptive filter is the minimization of the mean square error (MSE),  $E\{e^2(k)\}$ , which is given by;

E = Represent the expectation of operation e(k) = d(k) - y(k) d(k) = Desired signal y(k) = Output of the filter response.

The MSE is normally defined as the expectation of the squared error, which is given by;

$$\mathbf{J} = E\left[e^{2}(i)\right]$$

$$= E\left[(d(i) - w^{T} \cdot x(i))^{2}\right]$$

$$= E\left[d(i)^{2} - 2d(i) \cdot w^{T} \cdot x(i) + w^{t} \cdot x(i) \cdot x^{T}(i) \cdot w\right]$$

$$= E\left[d(i)^{2} - 2\rho_{xy}^{T}w + w^{t}\rho_{xx}w\right].$$

(2.5)

# PHASE NOISE CANCELLATION TECHNIQUES

### where

| $\rho_{xx} = Ex(i)x(i)^T$ , is the NxN correlation matrix                                              | (2.6)     |

|--------------------------------------------------------------------------------------------------------|-----------|

| $\rho_{xy} = Ed(i)x(i)$ , is the Nx1 cross-correlation matrix vector between the input and the desired | l signal. |

(2.7)

The auto-correlation vector is given by;

$$\rho_{xx} = E\{x(i)x^{T}(i)\}$$

$$= E \times \begin{bmatrix} x(i)x(i) & x(i)x(i-1) & \cdots & x(i)(i-N+1) \\ x(i-1)x(i) & x(i-1)x(i-1) & \cdots & x(i-1)(i-N+1) \\ \vdots & \vdots & \ddots & \vdots \\ x(i-L+1)x(i) & x(i-N+1)x(i-1) & \cdots & x(i-N+1)(i-N+1) \end{bmatrix}$$

(2.8)

The cross-correlation vector takes the following form;

$$\rho_{xy} = E\{y(i)x(i)\} \\

= E \times \begin{bmatrix} y(i)x(i) \\ y(i)x(i-1) \\ \vdots \\ y(i)x(i-N+1) \end{bmatrix}$$

(2.9)

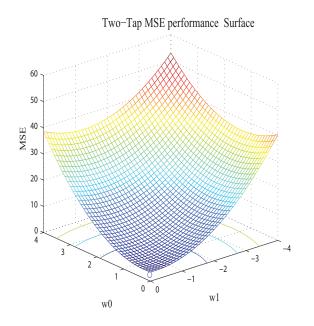

Equation 2.5 indicates that the MSE cost function behaves like a quadratic equation, which makes it easier to analyze and measure its performance by means of plotting a hyperbolic figure in Matlab [44] as shown in Figure 2.1, which is also referred to as performance surface of the MSE.

Figure 2.1 is also referred to as the performance surface of the MSE.

The MSE filter is designed in such a way that it operates at this minimum point by taking the derivative of equation (2.5) as follows;

**Figure 2.1:** Schematic representation of MSE performance surface simulated at M=2 with filter weights  $w_0$  and  $w_1$ .

$$\frac{jw}{dw}(d^2(i)) = 0$$

(2.10)

where  $d^2(i)$  is a constant variance

$$\frac{jw}{dw}(\rho_{xy}^T w) = 0$$

$$\frac{jw}{dw}(\rho_{xx}w^T) = 2$$

$$\frac{jw}{dw}(w\rho_{xx}w^T) = 2\rho_{xx}w.$$

(2.11)

The gradient of the MSE ( $\Delta$ ) with respect to the tap-weight *w* is;

$$\Delta = \frac{jw}{dw}$$

= -2\rho\_{xy} + \rho\_{xx}w. (2.12)

Equation (2.12) approaches zero at the bottom of the surface, such that the autocorrelated and crosscorrelated input sequences are linked by the filter coefficients as follows;

$$\rho_{xx}w_0 = \rho_{xy} \tag{2.13}$$

$$w_0 = \rho_{xx}^{-1} \rho_{xy}.$$

(2.14)

26

## © University of Pretoria

Figure 2.2: Schematic representation of M-tap adaptive filter.

At this point the filter,  $(w_0)$ , is able to deal with noise decisively.

The weight vectors  $\vec{w} = [w_0, w_1, \vec{\cdots}, w_{M-1}]^T$  shown in Figure 2.2 are computed in such a way that the performance surface has a single minimum MSE centered at the optimum vector,  $\vec{w_0}$  [45].

## 2.2.2 Least Mean Square Algorithm

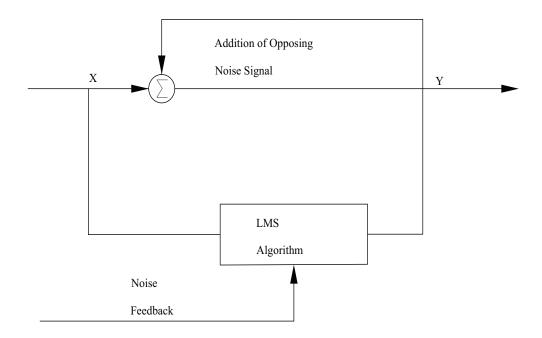

ANC is a commonly used technique that cancels noise by adding an alternating signal noise that is 180 deg out of phase with the original signal. This opposing signal dampens the energy of the original signal noise. As shown in Figure 2.3 the LMS algorithm has the filtering and adaptive processes and the main components. The filtering process generates the output signal and the estimation error. The adaptive process adjusts the filter tap weights automatically.

LMS has attracted a lot of attention [21, 46] due to its flexibility that makes it possible to operate as an automatic control system. The LSM algorithm is derived from the fact that MSE seeks to minimize  $Ee^{2}(i)$  until the Wierner solution is optimized such that;

$$\lim_{i \to \infty} W(i) = W_{MMSE}$$

$$= (\rho_{xx})^{-1} \rho_{xy}.$$

(2.15)

The Wierner solution is normally determined from the Newton and Steepest Descent Methods proposed in [47].

Figure 2.3: Schematic representation of ANC with LMS algorithm.

## 2.2.2.1 Newton Method

A Newton Method seeks to optimize the filter weights as follows [48];

$$\Delta W(i) = \mu \rho_{xx}^{-1} \left[ \frac{\partial E\{e^2(i)\}}{\partial W(i)} \right].$$

(2.16)

The LMS algorithm is obtained by substituting e(i) and W(i) into (2.16) as follows [48]

$$W(i+1) = W(i) - \mu \rho_{xx}^{-1} \left[ \frac{\partial E\{e^{2}(i)\}}{\partial W(i)} \right]$$

= W(i) - \mu \rho\_{xx}^{-1} \cdot 2(\rho\_{xx}W(i) - \rho\_{xy})

= (1 - 2\mu)W(i) + 2\mu \rho\_{xx}^{-1} \rho\_{xy}

= (1 - 2\mu)W(i) + 2\mu W\_{MMSE}. (2.17)

The filter weights are set from the initial W(0) condition to the optimum setting  $W_{MMSE}$  as follows;

$$W(i) = W_{MMSE} + (1 - 2\mu)^{i} [W(0) - W_{MMSE}].$$

(2.18)

where

$\mu =$  Is the step size that controls the convergence rate and stability of the filter.

### 2.2.2.2 Steepest Descent Method

The Steepest Descent Method seeks to reduce computational complexity by avoiding the matrix inversion as follows;

$$\Delta W(i) = -\mu \left[ \frac{\partial E\{e^{2}(i)\}}{\partial W(i)} \right]$$

$$W(i+1) = W(i) - \mu \left[ \frac{\partial E\{e^{2}(i)\}}{\partial W(i)} \right]$$

$$= W(i) - \mu .2(\rho_{xx}W(i) - \rho_{xy})$$

$$= (I - 2\mu \rho_{xx})W(i) + 2\mu \rho_{xx}W_{MMSE}$$

$$= (I - 2\mu \rho_{xx})[W(i) - W_{MMSE}] + W_{MMSE}.$$

(2.19)

Finally, the LMS algorithm is obtained by applying the Widrow method [48] to the Steepest descent expression where the estimation operator is omitted as follows;

$$W(i+1) = W(i) - \mu \left[\frac{\partial e^2(i)}{\partial W(i)}\right]$$

=  $W(i) - \mu \left[\frac{\partial e^2(i)}{\partial e(i)}\right] \cdot \left[\frac{\partial e(i)}{\partial W(i)}\right]$

=  $W(i) - 2\mu e(i) \cdot 2 \frac{[d(i) - W(i)^T \cdot X(i)]}{2W(i)}$

=  $W(i) + 2\mu e(i)X(i).$  (2.20)

Now filter weights can be modeled as;

$$W_0(i+1) = W_0(i) + 2\mu e(i)X(i)$$

(2.21)

$$W_1(i+1) = W_1(i) + 2\mu e(i)X(i-1).$$

(2.22)

As seen from Equation (2.20), the algorithm has low complexity as it does not depend on the signal statistics or metric inversion (i.e.,  $\rho_{xx}^{-1}$  and  $\rho_{xy}$ ).

The LMS algorithm consists of the filtering and adaptive process, which involves automatic adjustment of the filter parameters w(i+1) until all weights are updated. The algorithm is given by;

$$w(i+1) = w(i) + \mu x(i)e(i).$$

(2.23)

29

where

$\mu$  = Step-size (convergence factor). w(i) = tap-weights. w(i+1) = Updated tap-weight vectors.

The LMS algorithm seeks to adapt the filter tap weights until the error signal e(i) is minimized in accordance with the MSE process. Equation 2.23 confirms that the LMS iterative process does not depend on prior knowledge of the correlation coefficients  $\rho_{xx}$  and  $\rho_{xy}$ . Instead it uses instantaneous estimations, which makes it more robust and fast to converge. When simulating the LMS algorithm the following convergence condition is useful in defining the convergence range;

$$0 < \mu < \frac{1}{\lambda_{max}}.\tag{2.24}$$

where

$\lambda_{max}$  = Is the largest Eigenvalue of the correlation matrix  $\rho_{xx}$ .

A faster rate of convergence can be realized through the following convergence range that resolve the instability problems and adjusts the step size to [21];

$$0 < \mu < \frac{2}{\lambda_{max}}.\tag{2.25}$$

The earlier work conducted by Rajesh and Sumalatha [49] demonstrates the performance and effectiveness of the stepsize as a tool to improve voice quality of a telephone call. As shown in (2.25), the larger the step size the faster the convergence rate. However some larger stepsizes may cause signal instability.

| Design Parameters             |        |                   |

|-------------------------------|--------|-------------------|

| Parameters                    | Symbol | Calculated values |

| Step Size(Convergence factor) | μ      | 0.05              |

| Filter Order                  | Ν      | 10                |

| Filter length                 | L      | 150               |

| No. Of Iterations             | i      | 1000              |

**Table 2.1:** Parameters used for the analysis of LMS algorithm.

## 2.2.2.3 Simulation of LMS Algorithm

The LMS algorithm was evaluated for convergence criterion where the optimum complex weights were simulated using Equation (2.20) and Table (2.1).

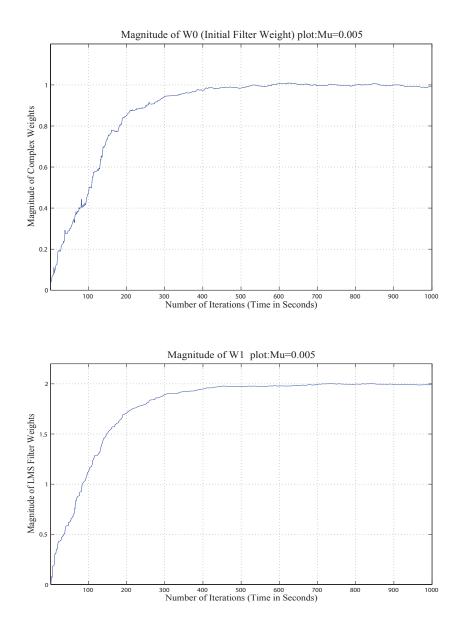

Figure 2.4 is a plot of weight convergence where the magnitude of the weights is plotted against the number of iterations, indicating the convergence of the weights to their optimum values. Here the magnitudes of the weights  $(W_0)$  are seen to converge after 600 iterations whereas those of  $(W_1)$  converge after 700 samples.

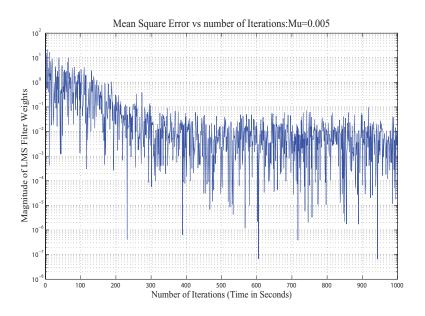

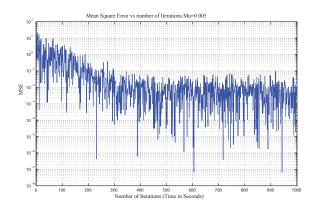

The step size parameter was also selected by trial and error with the guidance of Equation (2.24). After several simulations and different selections of  $\mu$  it was found that the convergence rate tends to be slow for small values, which results in high error signals. The best case scenario for this study was found when  $\mu = 0.005$  that causes the LMS algorithm to settle at an MSE of about  $10^{-2.9} = 0.001585$  and progresses until it reaches a steady-state error. As seen from (2.24), LMS is highly unstable and take too long to reach a steady-state error value.

However, the faster convergence can be obtained by varying the step size,  $\mu$ , which improves the convergence rate significantly. It was also observed through this simulation study that a smaller step size reduces the instability for larger filter orders. On the other hand, low filter orders requires higher step sizes to attain stability. This confirms that stronger signals requires small step sizes whereas weak signals require larger step sizes.

As shown in Figure 2.1, the MSE criterion always dictates that for the noise cancellation technique to exhibit excellent performance the error signal should approach zero as the number of iterations

### PHASE NOISE CANCELLATION TECHNIQUES

Figure 2.4: Magnitude of Weights  $W_0$  and  $W_1$  versus Number of Iterations.

progresses.

The simulation results show that although the LMS algorithm finally achieves the steady state-error it does so after several iterations, which implies that the LMS has a long convergence rate [50]. From this simulation it is concluded that although LMS has lower complexity it takes longer to converge at fixed step sizes although the convergent rate can be improved by changing step sizes (variable step sizes) through trial and error.

### PHASE NOISE CANCELLATION TECHNIQUES

Figure 2.5: MSE Estimation in dB vs no. of iterations (mu=.005).

### 2.2.3 Recursive Least Square

The performance of recursive least square (RLS) algorithm has been studied in [4], where it was shown that the RLS's performance is slightly better than LMS. However, Iliev and Kasabov [51] conducted a study on adaptive filtering with averaging in noise cancellation for voice and speech recognition and observed that the main drawback for RLS is the instability problem.

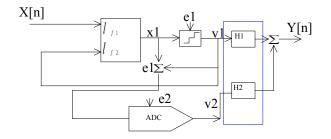

Figure 2.6 shows a schematic representation of an adaptive noise canceler, where the output of a filter is computed from;

$$y(i) = X^T W(i). (2.26)$$

The error signal is given by;

$$e(i) = s(i) + n(i) - y(i)$$

=  $s(i) + n(i) - [X^T W(i)].$  (2.27)

Changes in signal characteristics can be very fast and sometimes uncontrollable. This problem can be resolved by implementing a recursive algorithm that adjusts the filter coefficients. The recursive algorithm is able to achieve a faster rate of convergence through the adjustment of filter coefficients. The RLS tap weights are given by;

$$w(i) = \bar{w}^T(i-1) + k(i)\bar{e}_{i-1}(i).$$

(2.28)

33

Figure 2.6: Schematic representation of adaptive noise canceler with RLS.

where the gain vectors k(i) and x(i) are given by;

$$k(i) = \frac{x(i)}{\lambda + x^{T}(i)x(i)}$$

$$x(i) = \frac{(i-1)x(i)}{\bar{w}_{\lambda}}.$$

(2.29)

The fact that RLS algorithm computes filter weights by estimating previous samples of output signals,  $(\bar{y}_{i-1}(i) = \bar{w}^T(i-1)x(i))$ , leads to computational complexity.

| Design Parameters             |        |                                  |

|-------------------------------|--------|----------------------------------|

| Parameters                    | Symbol | Calculated values/Specifications |

| Step Size(Convergence factor) | μ      | 0.05                             |

| Filter Order                  | Ν      | 10                               |

| Filter length                 | L      | 150                              |

| No. Of Iterations             | i      | 8000                             |

## 2.2.3.1 Simulation of RLS Algorithm

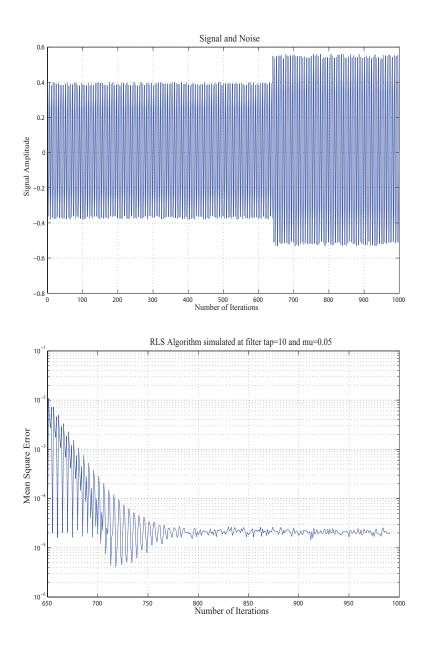

The RLS algorithm was implemented in Matlab with the reference signal assumed to follow a white Gaussian noise distribution of 1-dB. The noise was assumed to be random and was implemented in matlab using *randn* function. The errored signal of Equation 2.27 was evaluated. The main algorithm specification is given in Table 2.2.

## PHASE NOISE CANCELLATION TECHNIQUES

**Figure 2.7:** The top plot of Figure 2.7 shows the simulated signal with noise while the bottom plot shows the convergence characteristic of the RLS algorithm.

It can be observed from Figure 2.7 that at first the signal experiences high amplitude oscillations but converges faster at smaller iterations [52]. Figure 2.7 shows a very fast convergence rate that is achieved barely after 100 iterations (750-650) and the steady state errors continues with the number of iterations. The convergences characteristic of the RLS algorithm is more effective as it takes a smaller number of iterations when compared with the LMS although there are some high amplitude fluctuations at the beginning due to the recursive nature of the RLS algorithm. From the simulation results it is seen that RLS converges faster than the LMS algorithm. These results are in agreement

with observation made in [53]. As compared to LMS, the RLS algorithm was able to settle within 100 iterations and remain stable throughout until 1000 iterations. By selecting 10 as the tap weight and 0.05 as the step size the RLS algorithm reduced the mean square error by 0.0099 (0.01 to 0.0001), which is roughly 20dB.

However the RLS achieves a remarkable faster convergence rate at the cost of high complexity.

## 2.2.4 Kalman Filter

Kalman Filter can be thought of as an adaptive Filter that seeks to combine the strength of the least square error (LSE) and RSE to provide a more efficient algorithm with more computational efficiency [22, 54, 55, 56]. The KF uses mathematical techniques to model the observed values that contain noise to estimate the values that are closer to the true values.

The basic operation of the KF is that it generates estimates values of the true (and calculated values) by predicting a value, calculate the uncertainty of the value and then determine the weighted average of the predicted and measured values. The KF corrects the phase noise through the prediction of a new state from the previous estimation by introducing a correction term that is proportional to the prediction error. This allows the KF to reduce the effects of phase noise on the required signal by minimizing mean square error (MSE) between the desired signal and the filter response.

### 2.2.4.1 Signal Estimation

The KF estimates the values that are closer to the true values by making use of the linear stochastic difference equations as follows;

$$x_i = Ax_i + Bu_i + w_i. \tag{2.30}$$

$$y_i = Cx_i + v_i. \tag{2.31}$$

where

| $x_i =$ n-dimensional state vector.       |        |

|-------------------------------------------|--------|

| A = State transition matrix.              |        |

| $y_i =$ m-dimensional measurement vector. |        |

| C = Observation matrix.                   |        |

| $w_i =$ Process noise.                    |        |

| $v_i$ = Measurement noise vector.         | (2.32) |

Here the sequence  $v_i$  and  $w_i$  are assumed to be uncorrelated and independent of each other. The noise is normally modeled as white noise with normal probability distributions, where the process, **Q**, and

measurement, **R**, noise covariances are given by;

$$p(w) \approx \aleph(0, Q) \tag{2.33}$$

$$p(\mathbf{v}) \approx \aleph(0, R). \tag{2.34}$$

### 2.2.4.2 Error Computation with KF

The KF computes errors by making use of *a priori* state estimate at time *i* by assuming that the process prior to step *i* is known such that;

$$e_i^- \equiv x_i - \hat{x}_i. \tag{2.35}$$

and *a posteriori* estimate at time *i* after taking a measurement, such that;

$$e_i \equiv x_i - \hat{x}_i. \tag{2.36}$$

The covariances of the *a priori* and *a posteriori* errors are respectively given by;

$$P_i^- = E \begin{bmatrix} e_i^- & e^{-T} \end{bmatrix}.$$

(2.37)

$$P_i = E \begin{bmatrix} e_i & e^T \end{bmatrix}.$$

(2.38)

Now *a posteriori* estimate is computed as a linear combination of *a priori* estimate and the weighted average between the actual and predicted measurement by Equation (2.39);

$$\hat{x}_i = \hat{x}_i^- + K(y_i - C\hat{x}_i^-).$$

(2.39)

The KF gain, *K*, in 2.39 is given by;

$$K = P_i^- C^T (CP_i^- C^T + R)^{-1}$$

=  $\frac{P_i^- C^T}{CP_i^- C^T + R}$ . (2.40)

#### 2.2.5 Simulation results of KF

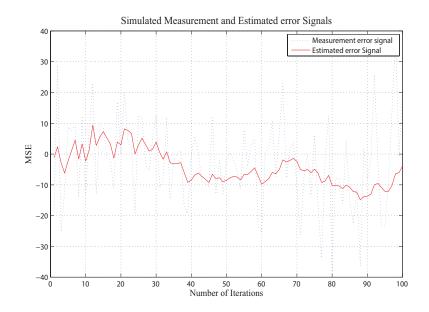

The performance evaluation of KF was conducted with Matlab where the Gaussian noise was implemented as a process and the amplitude was estimated using the KF procedure discussed in the preceding sections. The estimated and original signals were analyzed to determine if the estimation process was effective.

Figure 2.8: Signal Error Estimation with Kalman Filter.

Figure 2.8 shows that the at lower sample values the measurement and estimated signal errors track each other very well. However as the number of iterations progress, misalignment of the two signals becomes more visible. As seen in Figure 2.8, KF does not perform well at larger filter gains in that the amplitudes measurement error signal are much higher than that of the estimated signal. The height transients in the measurement error signal can be reduced by changing the covariance of the error signal.

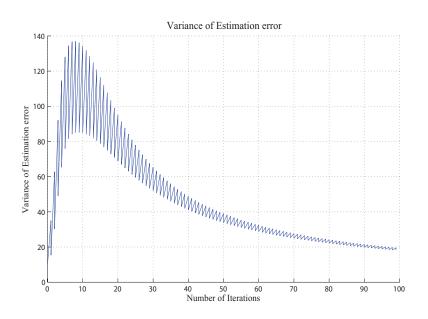

Figure 2.9 shows that the variance of the estimation error can be controlled to force the estimation signal to track the measurement signal error properly.

Figure 2.9: Variance of the estimation error.

As seen in figure 2.9, the main drawback of the KF is the requirement to establish the initial condition of mean and variance to initiate the recursive process. In this simulation the KF was initialized by starting  $\hat{x}_0$  state at the initial time and the initial estimation error covariance,  $\hat{P}_0$ . The problem in initializing  $\hat{x}_0$  and  $\hat{P}_0$  is that if  $\hat{P}_0$  is unknown with known  $\hat{x}_0$ , then  $\hat{P}_0$  will be too small. And if  $\hat{x}_0$  is initially assumed to be unknown, then  $\hat{P}_0$  becomes large. After some time, these initialization values become more difficult to be recognized in the overall filter performance.

Figure 2.10 indicates that the KF converges at about 80ms when the step size is at 0.01 and converges at 100ms when the step size is 0.05. This implies that the KF converges on the 100th sample, which is far much faster when compared with the LMS that converges on the 400th sample.

## PHASE NOISE CANCELLATION TECHNIQUES

Figure 2.10: MSE of Natural Frequency and it's variance.

The most widely used techniques (LMS, RLS, Kalman and PLL) were evaluated for performance using the performance criteria (MSE, Convergence rate, NPM, Stability and computational complexity. Table 2.3 gives a summary of the results of investigation, where the limitations and drawbacks of each technique are displayed.

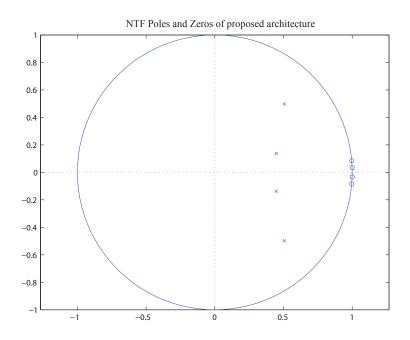

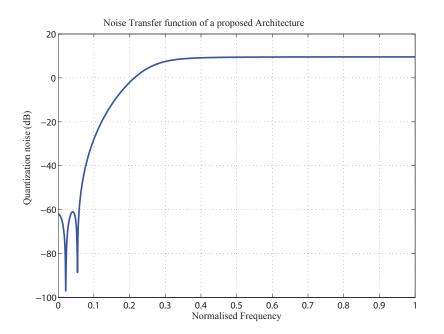

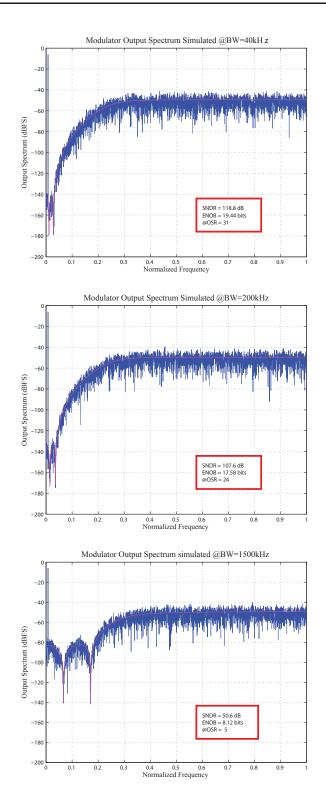

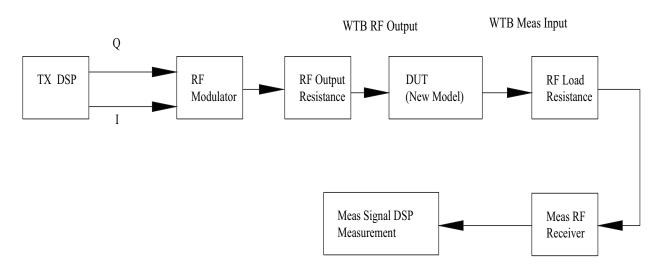

| Performance criteria       | LMS    | RLS  | KF    |