## IMPLEMENTATION OF A LOW-COST PASSIVE BISTATIC RADAR

by

# Joshua Leigh Sendall

Submitted in partial fulfilment of the requirements for the degree

Master of Engineering (Electronic Engineering)

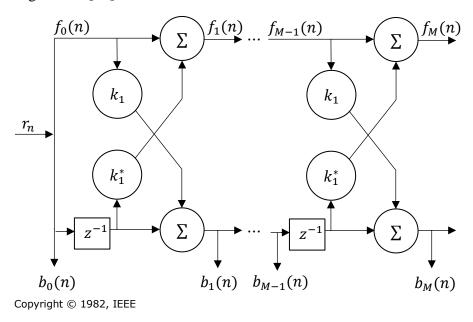

in the

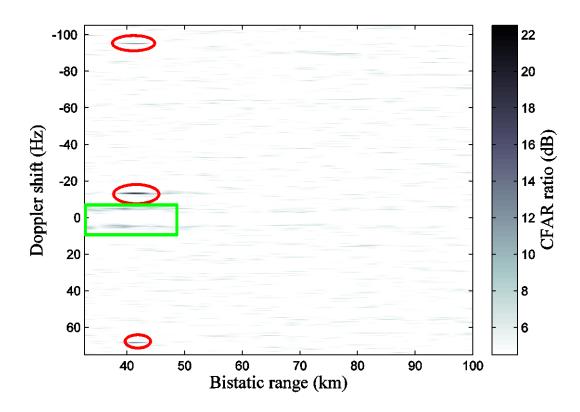

Department of Electrical, Electronic and Computer Engineering Faculty of Engineering, Built Environment and Information Technology

UNIVERSITY OF PRETORIA

September 2016

#### **SUMMARY**

#### IMPLEMNTATION OF A LOW-COST PASSIVE BISTATIC RADAR

by

## Joshua Leigh Sendall

Supervisor: Prof. W.P. du Plessis

Department: Electrical, Electronic and Computer Engineering

University: University of Pretoria

Degree: Master of Engineering (Electronic Engineering)

Keywords: Radar, passive radar, low-cost, adaptive filtering, clutter cancellation,

direct-path interference cancellation, matched filtering, tracking filter,

broadcast radio

Passive radar detects and ranges targets by receiving signals which are reflected off targets. Communication transmissions are generally used, however, theoretically any signal with a suitable ambiguity function may be used. The exploitation of an existing transmitter and the removal of emissions allow passive radars to act as a complementary sensor which is useful in environments where conventional active radar is not well suited. Such environments are in covert operations and in situations where a low cost or spectrally efficient solution is required.

Most developed passive radars employ intensive signal processing and use application specific equipment to achieve detection. The high-end processors and receiver equipment, however, detract from some of the inherent advantages in the passive radar architecture. These include the lower cost and power requirements achieved by removing transmitter hardware.

This study investigates the challenges faced when removing application-specific and high end components from the system and replacing them with low-cost alternatives. Solutions to these challenges are presented and validated by designing and evaluating a radar using these principles.

It was found that the major limitation in passive radar is the dynamic range of the receiver. While processing the signals was, and is, a significant challenge, be implemented on a low-cost, low-power embedded processor. This was achieved by asserting a few limitations to the configuration, exploiting the subsequently generated redundancy, and taking advantage of the parallelism by using general purpose graphics processing. Even on this processor, the system was able to run in real time and able to detect targets up to 91 km (bistatic range of 195 km) from the radar.

#### **OPSOMMING**

#### IMPLEMENTERING VAN 'N LAEKOSTE- PASSIEWE BISTATIESE RADAR

deur

#### Joshua Leigh Sendall

Studieleier: Prof. W.P. du Plessis

Departement: Elektriese, Elektroniese en Rekenaaringenieurswese

Universiteit: Universiteit van Pretoria

Graad: Magister in Ingenieurswese (Elektroniese Ingenieurswese)

Sleutelwoorde: Radar, passiewe radar, laekoste, aanpasbare filter, sluierkansellasie,

direkte baan-versteuringskansellasie, aangepaste filter, volgfilter,

uitsendingsradio

Passiewe radar spoor teikens op en meet die afstand na hulle toe deur seine te ontvang wat van die teikens af gereflekteer word. Uitgesaaide kommunikasieseine word meestal gebruik, maar teoreties kan enige sein met 'n geskikte dubbelsinnigheidsfunksie gebruik word. In 'n passiewe radar word senderhardeware en beheerde versendings nie benodig nie en daarom kan dit as 'n aanvullende sensor gebruik word in omgewings waar konvensionele aktiewe radar nie geskik is nie. Voorbeelde van sodanige omgewings is koverte operasies en situasies waar 'n goedkoper oplossing of effektiewer spektrumgebruik verlang word.

Meeste bestaande passiewe radars maak gebruik van intensiewe seinverwerking en benut toegewyde hardeware om opsporing moontlik te maak. Die gebruik van gesofistikeerde prosesseerders en ontvangstoerusting doen egter afbreuk aan die inherente voordele wat passiewe radars sou kon inhou, byvoorbeeld die laer koste en laer kragvereistes wat verkry word deur sendinghardeware te verwyder.

In hierdie studie is die uitdagings ondersoek wat vorendag kom wanneer toegewyde hardeware van die stelsel verwyder word en vervang word deur alternatiewe, laekoste-komponente. Oplossings vir hierdie uitdagings is gevolglik voorgestel en getoets

deur 'n radar wat van hierdie beginsel gebruik maak, te ontwerp en te evalueer. Die resultate van die praktiese radartoetse dui daarop dat die voorgestelde oplossings wel werkbaar is.

Daar is in hierdie studie bevind dat die grootse beperking van passiewe radar die dinamiese reikwydte van die ontvanger is. Seinprosessering was 'n groot uitdaging en het 'n paar beperkinge op die konfigurasie geplaas. Daar was egter steeds 'n mate van prosesseringsoortolligheid wat benut kon word en parallelle prosesseringstegnieke is gebruik om die stelsel op 'n laekoste- en laekrag- ingebedde prosesseerder te implementeer. Sodoende was dit moontlik om 'n eenvoudiger prosesseerder suksesvol te implementeer. Die prosesseerder het die stelsel in staat gestel om intyds te werk en om teikens tot en met 91 km (193 km bistaties afstand) van die ontvanger af op te spoor.

## ACKNOWLEGEMENTS

I would like to thank the following persons for their support.

My supervisor, Warren Paul du Plessis: for the guidance, support and inspiration during my studies. Also for reading and correcting all of my reports and papers, and teaching me so much.

Francois Maasdorp, Craig Tong, Christo Cloete, Rossouw van der Merwe and the CSIR: for supporting my research and "showing me the ropes".

My loving girlfriend, Melissa Reed: for being a foundation in my life.

My parents: for their love and support, which is always there unconditionally.

My Lord and saviour Christ Jesus: whom is my strength and shield, and through whom all thing are possible.

# LIST OF ABBREVIATIONS

ADC Analogue to Digital Converter

ADS-B Automated Dependent Surveillance Broadcast

AGC Automatic Gain Control

ALU Arithmetic-logic Unit

ARD Amplitude-Range-Doppler

ATC Air Traffic Control

AWGN Additive White Gaussian Noise

BLAS Basic Linear Algebra Subroutines

CFAR Constant False Alarm Rate

CGLS Conjugate Gradient Least Squares

CISC Complex Instruction Set Computing

CPI Coherent Processing Interval

CPR Compact Position Report

CPU Central Processing Unit

CUT Cell Under Test

CW Continuous Wave

DFT Discrete Fourier Transform

DMA Direct Memory Access

DPI Direct Path Interference

EM Electromagnetic

FAR False Alarm Rate

FDC Frequency-domain Correlation

FDTC Frequency-domain Time Correlation

FFT Fast Fourier Transform

FIR Finite Impulse Response

FLOP Floating Point Operation

FM Frequency Modulation

GAL Gradient Adaptive Lattice

GPGPU General Purpose Graphics Processing Unit

GPU Graphics Processing Unit

LNA Low-noise Amplifier

LPF Low-pass Filter

LSB Least Significant Bit

MAC Multiply-Accumulate

MIMD Multiple Instruction Multiple Data

MIMO Multiple Input Multiple Output

MKL Math Kernel Library

NaN Not a Number

NLMS Normalized Least Mean Squared

OEM Original Equipment Manufacturer

OTS Off-the-Shelf

PC Personal Computer

PFA Probability of False Alarm

PLL Phase-locked Loop

PPS Pulse per Second

RAM Random Access Memory

RCS Radar Cross-section

RF Radio Frequency

RISC Reduced Instruction Set Computing

RMS Root Mean Square

RMSE Root Mean Square Error

SDR Software Defined Radio

SFDR Spurious Free Dynamic Range

SIMD Single Instruction Multiple Data

SIMT Single Instruction Multiple Thread

SISD Single Instruction Single Data

SLL Sidelobe Level

SM Streaming Multiprocessor

SNR Signal to Noise Ratio

TDR Target to Direct-path Ratio

TDTC Time-domain Time Correlation

# TABLE OF CONTENTS

| CHAP | TER 1 INTRODUCTION                             | 1  |

|------|------------------------------------------------|----|

| 1.1  | PROBLEM STATEMENT                              | 1  |

|      | 1.1.1 Context of the problem                   | 1  |

|      | 1.1.2 Research gap                             | 2  |

| 1.2  | RESEARCH OBJECTIVE AND QUESTIONS               | 3  |

| 1.3  | SCOPE                                          | 4  |

| 1.4  | RESEARCH CONTRIBUTION                          | 7  |

| 1.5  | OVERVIEW OF STUDY                              | 7  |

|      | 1.5.1 Chapter 2 Passive Radar                  | 7  |

|      | 1.5.2 Chapter 3 Signal Acquisition             | 7  |

|      | 1.5.3 Chapter 4 Processing Platforms           | 7  |

|      | 1.5.4 Chapter 5 Processing Chain               | 8  |

|      | 1.5.5 Chapter 6 Results                        | 8  |

|      | 1.5.6 Chapter 7 Conclusion and Future Work     | 8  |

| СНАР | TER 2 PASSIVE RADAR                            | 9  |

| 2.1  | INTRODUCTION                                   | 9  |

| 2.2  | BASIC PASSIVE RADAR ARCHITECTURE               | 9  |

| 2.3  | PASSIVE RADAR IN CONTEXT                       | 11 |

|      | 2.3.1 Transmitter/receiver orientation         | 11 |

|      | 2.3.2 Continuous and pulse radar               | 12 |

| 2.4  | HISTORY OF FM-BASED PASSIVE RADAR              | 13 |

| 2.5  | COMPONENTS OF THE RECEIVED SIGNALS AND ANTENNA |    |

|      | CONFIGURATION                                  | 15 |

| 2.6  | PASSIVE RADAR PROCESSING                       | 16 |

|      | 2.6.1 Matched filtering                        | 16 |

|      | 2.6.2 DPI cancellation                         | 18 |

|      |                                                |    |

|      | 2.6.3 CFAR detection                           | 18 |

| CHAP | TER 3 SIGNAL ACQUISITION                         | 21 |

|------|--------------------------------------------------|----|

| 3.1  | PERFORMANCE FACTORS                              | 21 |

|      | 3.1.1 Active interference                        | 22 |

|      | 3.1.2 Sensitivity                                | 24 |

|      | 3.1.3 Dynamic range                              | 24 |

| 3.2  | SITE AND TRANSMITTER SELECTION                   | 25 |

|      | 3.2.1 Optimal position                           | 28 |

|      | 3.2.2 Antenna selection                          | 29 |

|      | 3.2.3 Additional considerations                  | 31 |

|      | 3.2.4 Transmitter selection                      | 31 |

| 3.3  | RECEIVER SELECTION                               | 32 |

|      | 3.3.1 Channel coherency                          | 34 |

|      | 3.3.2 Conclusion                                 | 38 |

| 3.4  | SUMMARY                                          | 38 |

|      |                                                  |    |

| CHAP | TER 4 PROCESSING PLATFORMS                       | 39 |

| 4.1  | CENTRAL PROCESSING UNIT                          |    |

|      | 4.1.1 Multithreading                             | 39 |

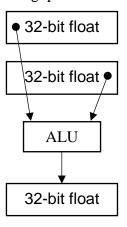

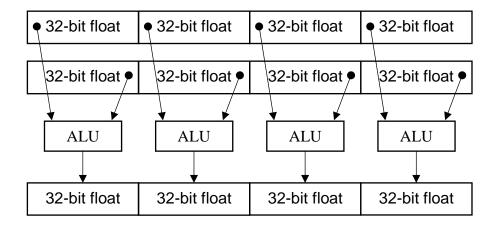

|      | 4.1.2 SIMD instructions and processor intrinsics | 40 |

| 4.2  | GRAPHICS PROCESSING UNIT                         | 42 |

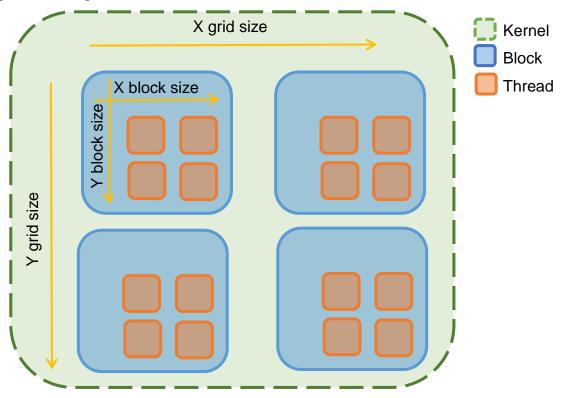

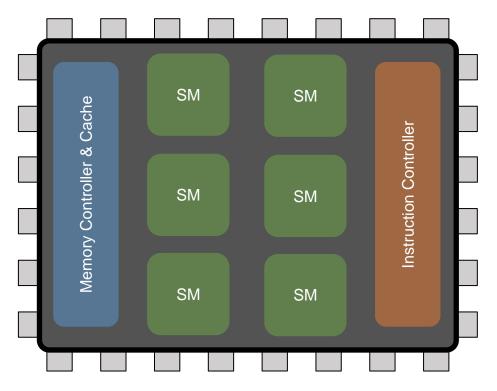

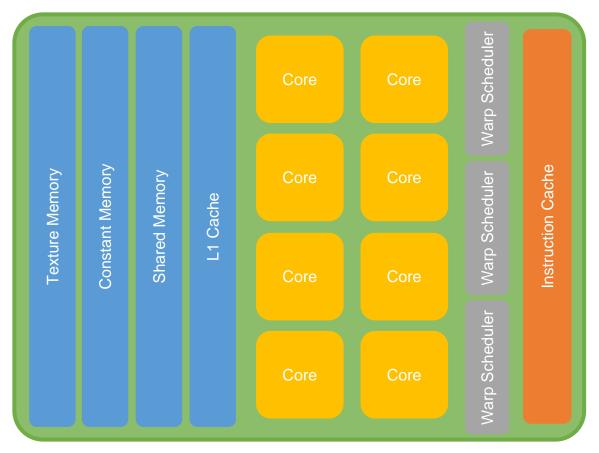

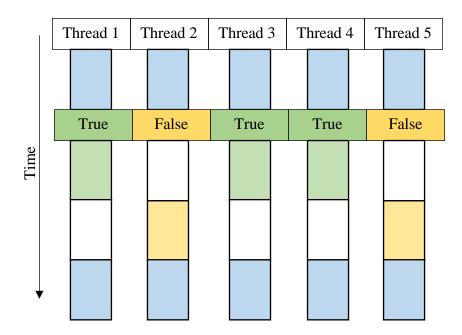

|      | 4.2.1 Threading model                            | 43 |

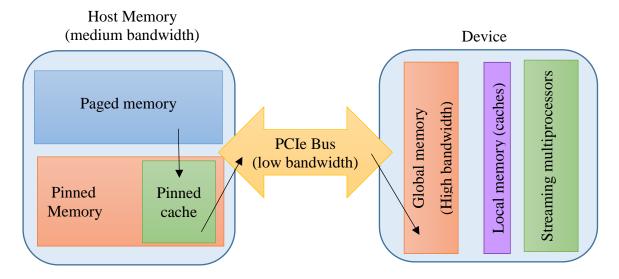

|      | 4.2.2 Memory structure                           | 47 |

| 4.3  | COMPARING GPU AND CPU PROCESSORS                 | 49 |

|      | 4.3.1 Task and data parallelism                  | 49 |

|      | 4.3.2 Latency and throughput                     | 50 |

| 4.4  | IMPLEMENTATION HARDWARE                          | 51 |

|      | 4.4.1 Mobile system                              | 51 |

|      | 4.4.2 Embedded system                            | 52 |

| 4.5  | SUMMARY                                          | 53 |

|      |                                                  |    |

|      | TER 5 PROCESSING CHAIN                           |    |

| 5.1  | INITIAL EVALUATION                               |    |

| 5.2  | CANCELLATION FILTER                              | 55 |

|      | 5.2.1 Choice of cancellation region | 56  |

|------|-------------------------------------|-----|

|      | 5.2.2 Wiener-Hoph Filter            | 58  |

|      | 5.2.3 Linear least squares          | 60  |

|      | 5.2.4 Miscellaneous Filters         | 60  |

|      | 5.2.5 Optimisation                  | 61  |

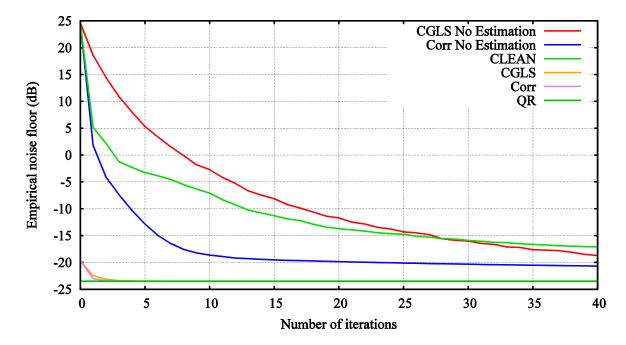

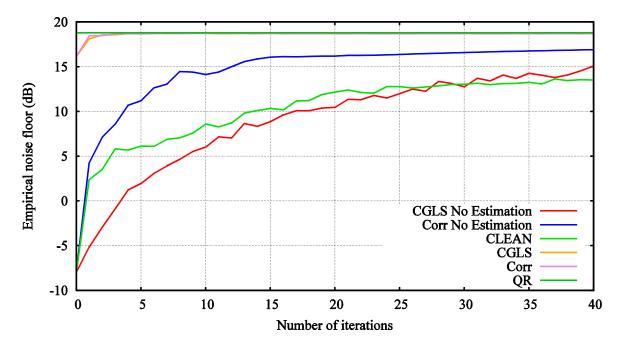

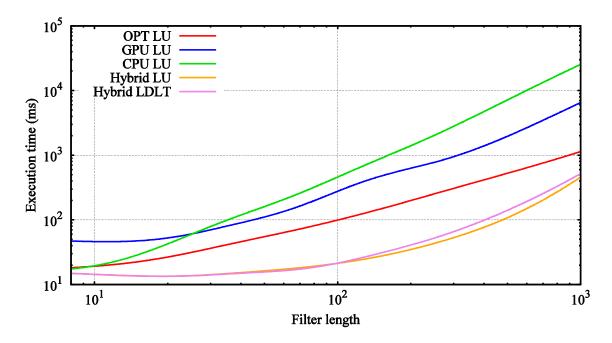

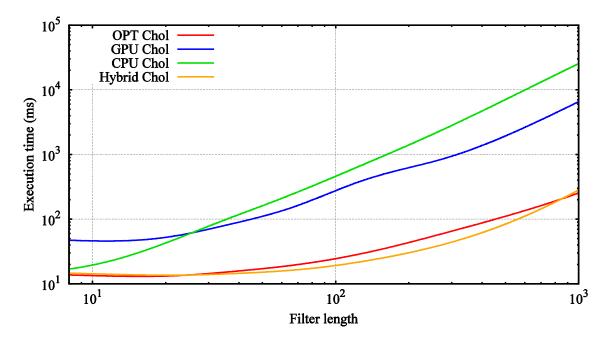

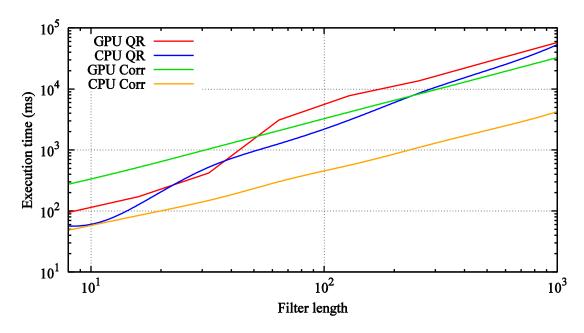

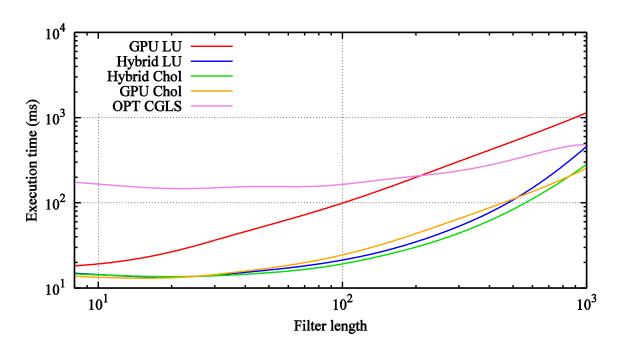

|      | 5.2.6 Experiments and results       | 67  |

|      | 5.2.7 Conclusion                    | 84  |

| 5.3  | MATCHED FILTER                      | 86  |

|      | 5.3.1 Time correlation              | 86  |

|      | 5.3.2 Frequency correlation         | 88  |

|      | 5.3.3 Reduced computation filters   | 89  |

|      | 5.3.4 Matched filter performance    | 89  |

| 5.4  | TARGET DETECTION AND EXTRACTION     | 92  |

|      | 5.4.1 Detection                     | 92  |

|      | 5.4.2 Target extraction             | 93  |

| 5.5  | TARGET STATE SMOOTHING              | 95  |

|      | 5.5.1 Target model                  | 95  |

|      | 5.5.2 Model estimation              | 96  |

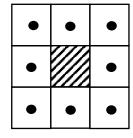

|      | 5.5.3 Detection association         | 98  |

| 5.6  | SYSTEM OUTPUT                       | 100 |

| 5.7  | SUMMARY                             | 100 |

| CHAD | TER 6 RESULTS                       | 102 |

| 6.1  | CONFIGURATION AND IMPLEMENTATION    |     |

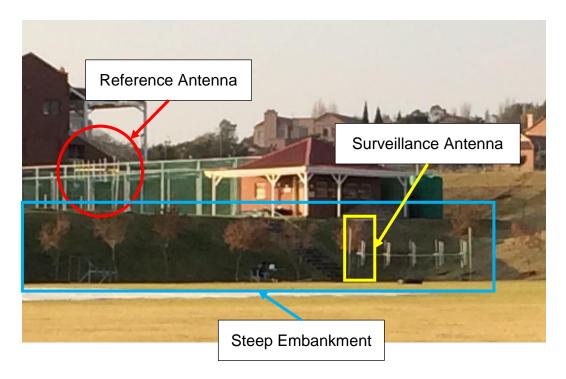

| 0.1  | 6.1.1 Deployment site               |     |

|      | 6.1.2 Configuration                 |     |

| 6.2  | DETECTION CAPABILITY                |     |

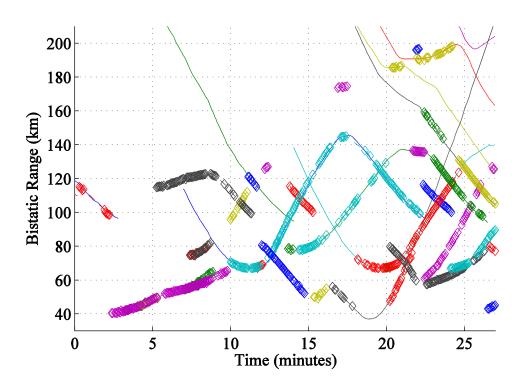

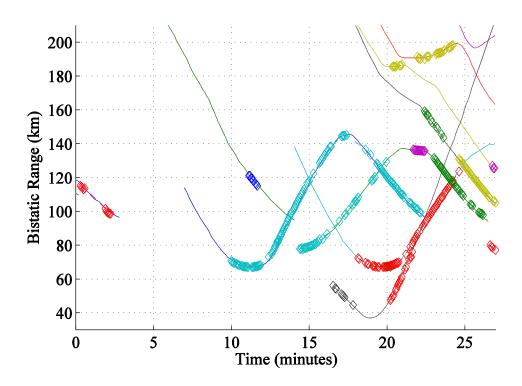

| 0.2  | 6.2.1 Control data                  |     |

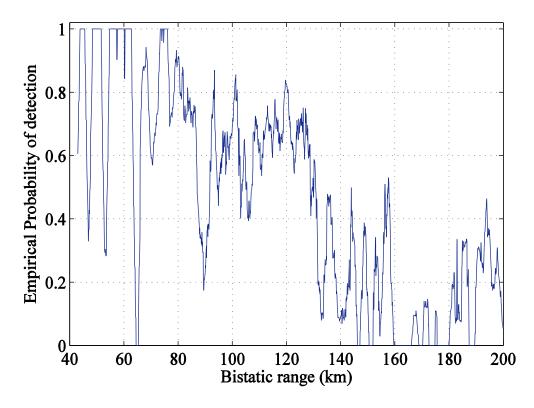

|      | 6.2.2 Detection probability         |     |

|      |                                     |     |

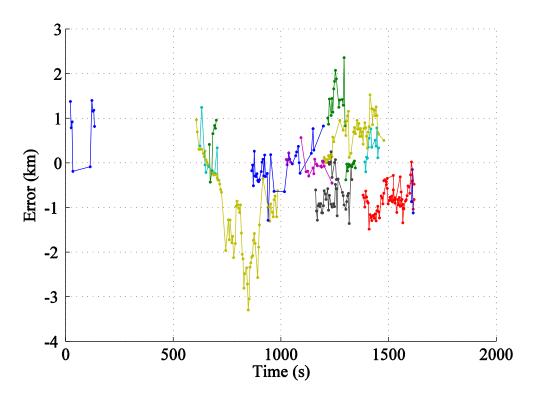

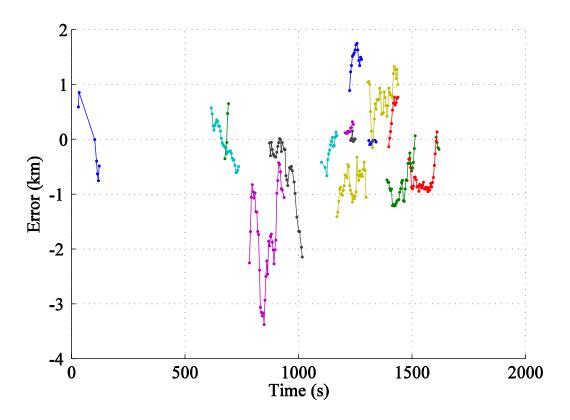

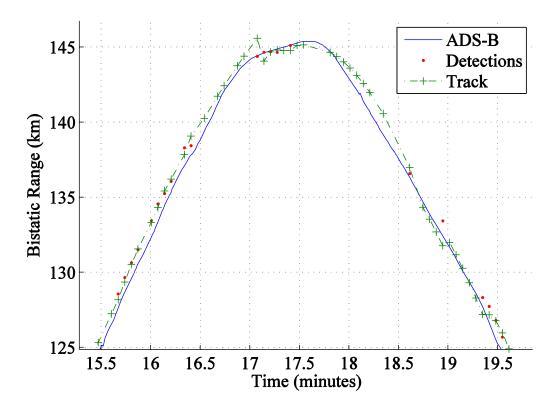

| 62   | 6.2.3 Location error                |     |

| 6.3  | PROCESSING PERFORMANCE              |     |

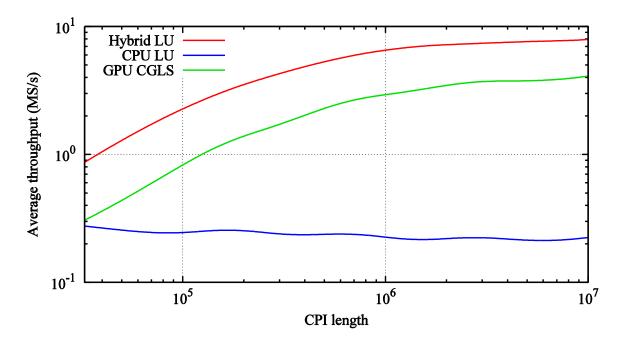

|      | 6.3.1 Mobile platform               |     |

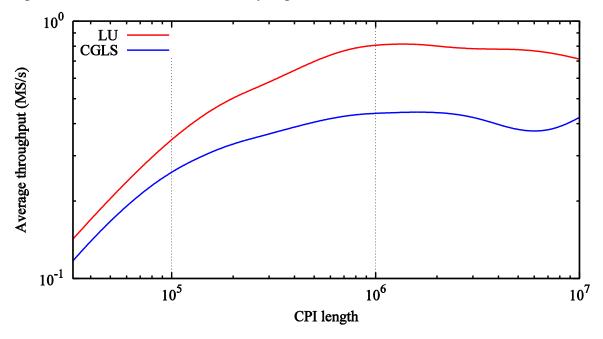

|      | 6.3.2 Embedded platform             | 123 |

Department of Electrical, Electronic and Computer Engineering University of Pretoria

| 6.4    | COST                                          | 124     |

|--------|-----------------------------------------------|---------|

| 6.5    | DISCUSSION OF RESULTS                         | 124     |

|        | 6.5.1 Detection capability                    | 124     |

|        | 6.5.2 Processing performance                  | 126     |

|        | 6.5.3 Comparison to existing systems          | 127     |

| 6.6    | SUMMARY                                       | 129     |

|        |                                               |         |

| CHAP'  | TER 7 CONCLUSION AND FUTURE WORK              |         |

| 7.1    | CONCLUSION                                    | 130     |

|        | 7.1.1 Passive radar performance               | 130     |

|        | 7.1.2 Optimum position                        | 130     |

|        | 7.1.3 Antenna and transmitter selection       | 131     |

|        | 7.1.4 Cancellation filter schemes             | 131     |

|        | 7.1.5 Matched filter processing               | 131     |

|        | 7.1.6 Radar performance                       | 131     |

| 7.2    | FUTURE WORK                                   | 132     |

|        | 7.2.1 Analogue DPI cancellation               | 132     |

|        | 7.2.2 Improved filtering                      | 133     |

|        | 7.2.3 Unambiguous target position             | 133     |

|        | 7.2.4 Independent channel gain                | 133     |

|        |                                               |         |

| REFEI  | RENCES                                        | 134     |

| ADDE   | NDUM A DERRIVATION OF COMPUTATIONAL COMPLEXIT | IFS 141 |

|        | LU FACTORIZATION                              |         |

|        | CHOLESKY FACTORIZATION                        |         |

|        | LDL FATORIZATION                              |         |

|        | QR FACTORIZATION                              |         |

|        | CONJUGATE GRADIENT LEAST SQUARES              |         |

|        | CLEAN CANCELLATION                            |         |

|        | CORRELATIVE CANCELLATION                      |         |

|        | GRADIENT ADAPTIVE LATTICE FILTER              |         |

| - 1.0. |                                               |         |

| ADDE | NDUM B GPU MEMORY TYPES    | 155 |

|------|----------------------------|-----|

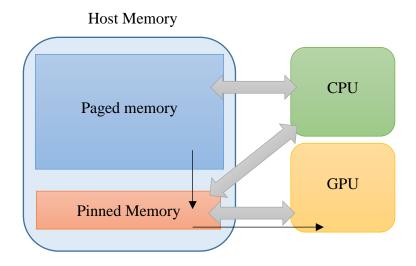

| B.1. | PAGED MEMORY               | 155 |

| B.2. | PINNED MEMORY              | 155 |

| B.3. | GLOBAL MEMORY              | 155 |

| B.4. | SHARED MEMORY              | 156 |

| B.5. | REGISTERS                  | 156 |

| B.6. | CONSTANT MEMORY            | 156 |

| B.7. | TEXTURE MEMORY             | 157 |

|      |                            |     |

| ADDE | NDUM C EVALUATION METRICS  | 158 |

| C.1. | ARITHMETIC METRICS         | 158 |

|      | Time cost                  | 158 |

|      | FLOPs                      | 158 |

| C.2. | ARCHITECTURAL METRICS      | 158 |

|      | Registers per thread/block | 158 |

|      | Shared memory per block    | 159 |

|      | Implementative metrics     | 159 |

|      | Execution time             | 159 |

|      | Maximum throughput         | 159 |

|      | FLOPS                      | 159 |

|      | Occupancy                  | 159 |

#### 1.1 PROBLEM STATEMENT

#### 1.1.1 Context of the problem

Passive coherent radars have been an area of recent interest as they have the potential to meet needs which conventional active radars cannot. The primary advantage of a passive radar is that it does not transmit a signal. Instead of transmitting a signal, passive radars use transmitters of opportunity, such as television, radio, or cellular transmissions [1]. Removing the transmission of a signal provides several benefits including being difficult to detect in covert scenarios [2, 3], reduced vulnerability to anti-radiation armaments [4], requiring potentially less power (as no power needs to be transmitted), and not requiring a new frequency band allocation [2] (i.e. reduced electromagnetic pollution [3]). A practical motivation for a low-cost passive radar has been identified [5], whereby developing countries, such as those found in Africa, are unable to afford and maintain primary air traffic control (ATC) radar systems [5].

A passive radar may use any transmitter of opportunity that the system deems suitable. However, various signal properties such as bandwidth, transmission power, and ambiguity functions may impose limits and place unacceptable demands on a system, in order for that signal to be used.

The absence of transmitter hardware has the potential to reduce capital and operational costs of implementing a passive radar system [3]. However, the increased demand for processing [6] depreciates the economic benefit of removing the transmitting components from the system by requiring more expensive and power hungry processors.

Replacing conventional custom receivers [7] with low-cost off-the-shelf (OTS) digital receivers reduces the cost of the system, but sacrifices performance for cost. As such, this trade off dramatically affects the system's ability to recover target reflections from the

received signals. The main factors which contribute to the decreased target detection capability are:

- Non-coherency between receiver channels, which degrades the performance of direct-path interference (DPI) removal and the matched filter,

- decreased SFDR of the reciever,

- analogue to digital converters (ADCs) with lower bit depth, which increases the systems minimum signal required for detection [8], and

- wider analogue filters, which reduce the effective bit depth of the receiver.

These factors introduce challenges into the system by making DPI mitigation before, and after digital sampling a high priority. By understanding the performance critical factors of the receiver with regard to a passive radar, intelligent selection of components can allow for the performance/cost ratio to be maximised.

In order to remove DPI and clutter, which is required before targets can be detected, digital adaptive filters are employed [9]. The adaptive filters, which typically implement least-squares algorithms, are computationally intensive and traditionally require the majority of available processing power [6, 9]. Compounding the challenges incurred when implementing a DPI cancellation filter is the high dynamic range of the signals (with the direct path signal being in excess of 100 dB larger than typical target signals) [1].

Reducing the signal processing requirements allows low-cost processing components to be considered. While contributing to a reduction in capital cost, low-cost processors can also exhibit lower power consumption, thereby further reducing the operational costs of the system.

### 1.1.2 Research gap

Many passive radar systems exist, but due to the general market requiring high specification and high performance systems, they often rely on specialized and high-end hardware to realize real-time processing. However, there is little research into implementing a low-cost system which can be deployed in financially sensitive scenarios. Previous attempts have

either resulted in poor performance [10], or the need for custom hardware [7] [11]. Furthermore, the reduction in cost of any system increases the resistance to competitor market entry.

The single site system here cannot unambiguously detect a target. A multi-site or multi-channel system is required for such detection. This work, therefore, focuses on a low-cost single site system which can be incorporated into a larger network of sensors.

### 1.2 RESEARCH OBJECTIVE AND QUESTIONS

The research questions posed are:

- 1. Is real-time processing achievable using mobile non-specialized OTS hardware?

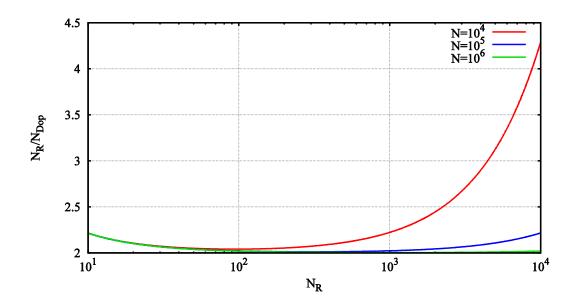

- With most passive radar systems, the objective has been performance and, as such, high-end processing hardware has been used, even to the extent of computer clusters [12]. However, in a power and cost sensitive environment, is it possible to achieve real-time processing on low-power mobile processors, and what steps/restrictions/simplifications are necessary to achieve it? This has been previously considered [13], however, it was performed for a specific cases and the underlying trends were not explored.

- 2. Which factors constrain the performance of a low-cost passive radar?

As with any system, it is important to understand the performance limiting factors within the system. In systems with highly constrained resources it is even more critical. A low-cost passive radar is an example of such a system, and in order to successfully implement it, the factors which limit its performance must be understood so that the resources available can be optimally distributed, thereby maximising performance. A similar analysis has been performed focusing on the receiver [7]. The analysis in this study extends this to the rest of the system.

3. Is it possible to detect aircraft with non-specialized receivers, such as a low cost OTS SDR?

The receiver is a key component which imposes many limitations on the system. As such, it necessary to determine what these are and, if a decrease in the receiver performance can be tolerated, still allow for adequate performance. This has been previously explored in literature [10], but with limited detection ranges displayed and exploration into the reasoning behind the limited performance.

4. What are the considerations necessary when selecting a site for a low-cost passive radar and do the priorities differ from conventional passive radar site selection?

The reduction in performance of key system components, necessary to decrease the overall system cost, may impose additional restrictions on the system (such as vulnerability to out-of-band interference). These need to be understood and quantified.

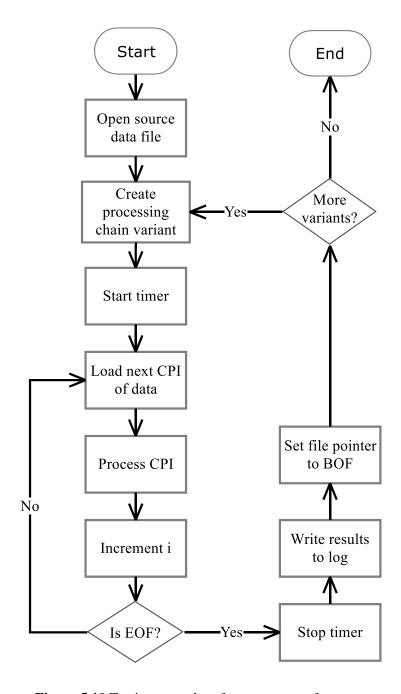

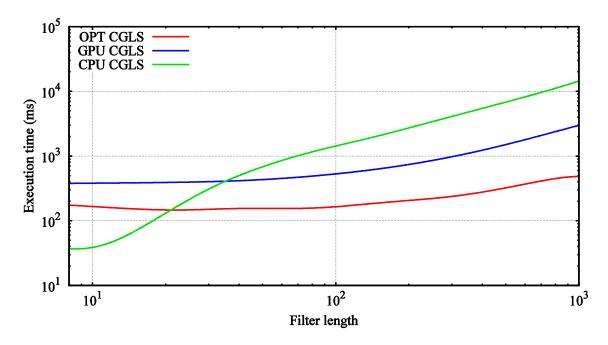

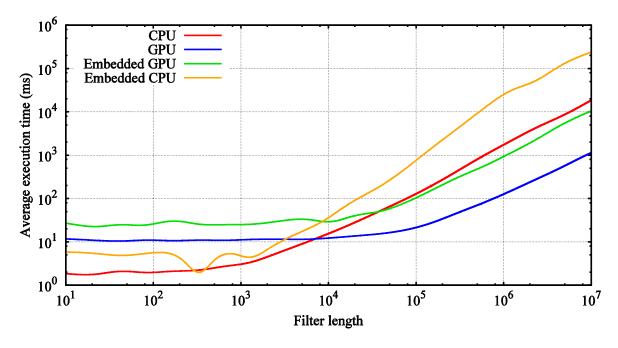

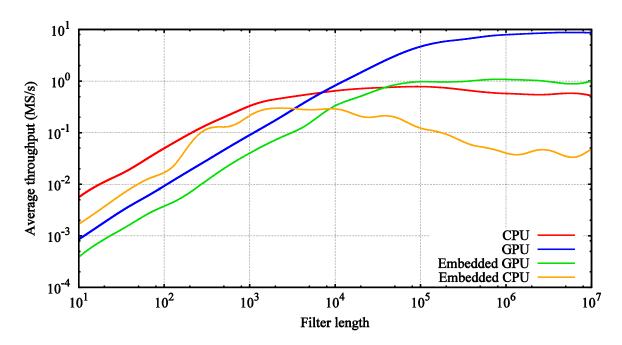

5. Which floating-point capable processors are best suited to a low-cost passive radar system?

Different processor architectures must be explored, not only for performance, but in order to find a solution that provides sufficient performance at a minimum cost, i.e. providing a suitable cost-performance trade-off. Some exploration into this has been performed in literature [11], but the analysis has only been done for specific configurations.

#### 1.3 SCOPE

Due to the vastness of passive radar, the subject in its entirety is not considered in this study. The following constraints are imposed on this study to limit this scope.

#### **Transmitter**

In order to condense the topic to a manageable scope, only commercial FM radio based passive radar is considered. This implies a limit on the bandwidth of the signal of 150 kHz, and that the centre frequency lies between 88 and 108 MHz.

FM passive radar was chosen due to its suitability in the area where the study was based. This decision also allows the results of the study to be used in the study of the deployment of passive radar as a low cost radar in Africa, where analogue FM remains a vital and abundant communication medium.

#### **Mobility**

It is further assumed that the radar's transmitter and receiver are static, and thus clutter lies close to and is typically centred on a zero Doppler shift. This leaves the radar defined as a passive bistatic radar.

#### **Direction finding**

In this study the direction of targets is not considered. This constraint was applied as direction finding in passive bistatic radar still requires research and development. One solution which is currently under development uses multiple sites [14] [15] (either transmitters or receivers), i.e. a multistatic system [16]. In such a system the processing at each site is identical to that considered in this study, and the position of a target is determined by integrating and comparing the results of each site [15]. Hence a number of systems could be combined to enable unambiguous detection.

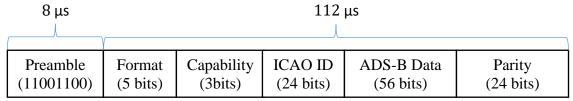

#### **Targets**

To evaluate the radar system, only aircraft with ADS-B transceivers were considered, as this provided a means of control data, which was used to verify the position of the aircraft. An obvious limitation is that the detection accuracy measurable is limited by the accuracy of the ADS-B detections. Furthermore, civilian aircraft typically have a large RCS and have

significant velocity so as to allow distinction from clutter. This has been an approach in a number of studies [5,7,11-13,17]

#### **Processors**

Of the five major processor families (ASIC, FPGA, DSP, GPP, and GPU) only GPUs and GPPs, or more specifically CPUs, were considered in this study. ASIC solutions were excluded as they typically have the highest development and production cost (in the low quantities expected for this system) of the families.

The passive radar environment lends itself well to floating point processing because of the high dynamic range of components of the signals received and processed by the system. Furthermore, many of the computationally intensive operations can be heavily parallelised. The processors considered were thus selected to support floating point processing and parallel architectures.

The development cost of both DSPs and FPGAs, both in terms of time and development tool cost, typically is significantly higher than the CPU variant for two reasons.

Firstly, the drivers and operation software for the receivers considered in this study were only available for CPU based systems with full OS. The use of a platform without such an OS would require the development of driver and communication software/hardware to allow the integration of an OTS receiver. This development is significant and was beyond the scope of this study.

Secondly, while DSPs and FPGAs may provide a lower cost system when the packages themselves are considered, the requirement for their integration into a development board (or custom board) results in increased cost for a one-off unit. This was found to negate many of the benefits gained by using a DSP or FPGA processor for such low quantities. As such both FPGAs and DSPs are beyond the scope of this study.

GPUs are considered as they are paired with a CPU which allows the benefits of integrating a low-cost CPU into a system with a full OS. Furthermore, the algorithms used in performing the radar processing can exploit parallel processing architectures [5], and require high dynamic range (which can be achieved by using floating point data structures). Additionally, GPUs can allow both a high performance to power ratio [18] and a high performance to cost ratio, conforming well to the requirements of the problem.

#### 1.4 RESEARCH CONTRIBUTION

A DPI and clutter cancellation algorithm was developed which was not based on the conventional least squares principle, but rather correlation. This was done in an attempt to reduce the processing requirements of the passive radar system, of which the adaptive cancellation filter contributes the majority. A paper was submitted for publication based on this filter architecture and the analysis conducted in Section 5.2.6.1.

#### 1.5 OVERVIEW OF STUDY

The structure of the study and the content of each chapter is summarised below.

#### 1.5.1 Chapter 2 Passive Radar

Chapter 2 provides an introduction to passive radar, and thus outlining how passive radar functions. In order to gain full understanding, a brief introduction to some important general radar concepts is also provided.

#### 1.5.2 Chapter 3 Signal Acquisition

Chapter 3 discusses the non-digital design aspects. These include receiver selection, site selection and antenna selection. The factors which influence the performance of a passive radar are discussed here and strategies on how to approach these challenges are presented.

#### 1.5.3 Chapter 4 Processing Platforms

Chapter 4 introduces the processing platforms which were investigated for the implementation of the passive radar. The differences between and structures of CPUs and

GPUs are discussed. Their general operation is also discussed as an understanding thereof is required to effectively optimise their use.

#### 1.5.4 Chapter 5 Processing Chain

Chapter 5 discusses the digital signal processing chain used for passive radar. Algorithms and applicable optimizations are presented and evaluated. Each processing chain is discussed in terms of its effectiveness and performance on each of the processing platforms.

#### 1.5.5 Chapter 6 Results

Chapter 6 demonstrates the functionality of a radar system designed and implemented using the principles presented in the previous chapters. The system was deployed and its output was recorded. The detection capability, accuracy, and financial implications of the implemented system are evaluated in this chapter using the recorded data.

## 1.5.6 Chapter 7 Conclusion and Future Work

Chapter 7 presents a summary of the study and its achievements as well as improvements which may be implemented in the future.

#### 2.1 INTRODUCTION

Radar is defined as "an electromagnetic system for the detection and location of objects that operates by transmitting electromagnetic signals, receiving echoes from objects (targets) within its volume of coverage, and extracting location and other information from the echo signal" [19]. While this indeed describes a traditional active radar, radars have expanded beyond this meaning. At their essence, however, radars still remain systems which use electromagnetic signals reflected off objects to detect the object's presence.

A passive radar, rather than transmitting signals which then reflect off objects and are received, receives the reflections from transmissions of opportunity [9] (much like the human eye uses light originating from the sun). While various designs for passive radar exist, the scope for this research is on a separated reference architecture, as this is the simplest form of passive radar, requiring the least hardware and processing, and which aligns well with the goal of a low-cost passive radar.

#### 2.2 BASIC PASSIVE RADAR ARCHITECTURE

In its simplest form, the separated reference architecture uses two antennas and receiver channels [5]. A passive radar does not have direct access to the transmitted signal, which is required for coherent processing. Instead, an approximation of the transmitted signal is received via one of the receiver channels, i.e. the reference channel. Ideally, only the transmitted signal is received, but this is not achievable in practical systems [20].

When the transmitter of opportunity is transmitting certain digital signals, such as DAB+, the reference channel can be extracted from the surveillance channel via the use of a channel model. In this case, a separate reference antenna is not required. However, this study does not include this case, as the signals considered useable by the system are FM analogue signals (see Section 1.3).

The purpose of the other receiver channel, the surveillance channel, is to receive the signals reflected off of objects of interest (and ideally nothing else). In practice, only a small portion of the signals reflected from targets ever reach the surveillance antenna [12]. Without careful design, these signals would fall below the SFDR of the receiver and not be detectable [8]. The reason that SFDR is generally a larger problem than receiver sensitivity, is due to the relatively large amount of energy which is received directly from the transmitter of opportunity [1]. Even with careful design extensive signal processing is required to suppress DPI and detect targets [9].

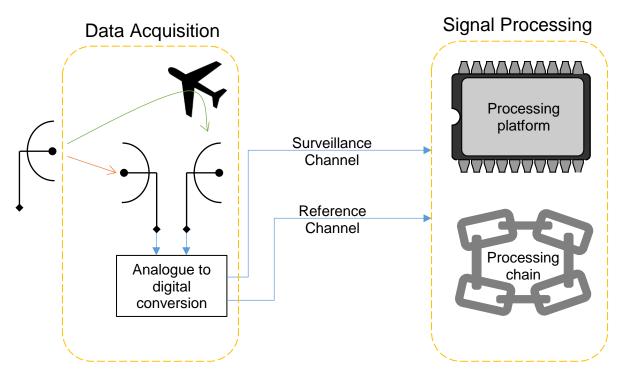

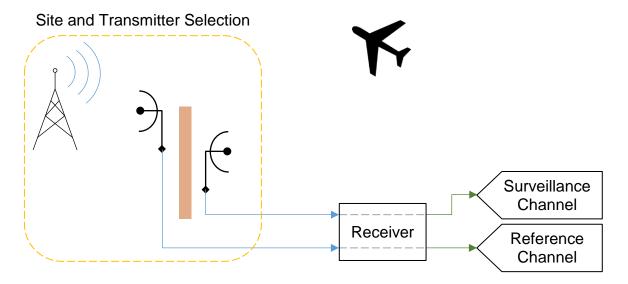

Figure 2.1 System diagram of an analogue passive radar.

A conceptual diagram of a generalised passive radar is shown in Figure 2.1. Data Acquisition concerns the process of receiving useful signals and manipulating them to the point where they can be processed. Signal processing is the process of manipulating the received data channels such that targets may be detected.

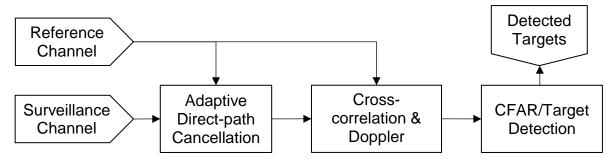

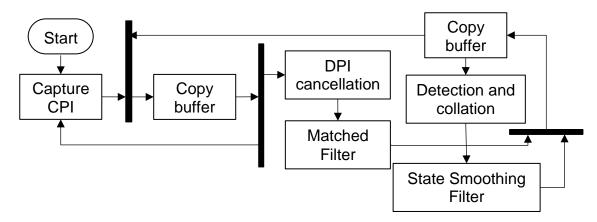

A typical processing chain is shown in Figure 2.2. In active radar, the cross-correlation and Doppler processing stage comprises the majority of processing [21], although, due to the control which active radar has over the transmitted signal, this processing stage is

implemented differently to how it is performed in passive radar [12]. This description of the matched filter is expanded on in Section 2.6.1.

Figure 2.2 Typical passive radar processing chain.

An additional step, which active radar does not typically include, is the removal of DPI. This step is required to remove large signals the sidelobes of which would otherwise mask any targets [5]. The functionality of this processing block is covered in Section 2.6.2.

Lastly, a target detection scheme is required to automatically detect targets. This normally comprises, but is not limited to, a CFAR detector. However, due to some of the unique aspects of passive radar, the implementation of the detector differs somewhat from conventional active radar [5]. This is discussed in Section 2.6.3. Finally, the raw detections need to be associated with their respective targets. This is performed by a tracking filter.

#### 2.3 PASSIVE RADAR IN CONTEXT

In this section passive radar is contextualised and classified within the field of radar.

#### 2.3.1 Transmitter/receiver orientation

The vast majority of radars are monostatic [21], i.e. the distance between the transmitter and receiver is negligible and can be considered to be in the same location. Many pulse radars go further than this and use the same antenna for transmitting and receiving.

Alternatively, the transmitter and receiver can be separated creating a bistatic system. Most passive radars are bistatic systems, with the receiver in one location and the transmitter in

another [22]. There are also passive radars which use multiple receiver or transmitter sites. This is termed a multistatic system [22].

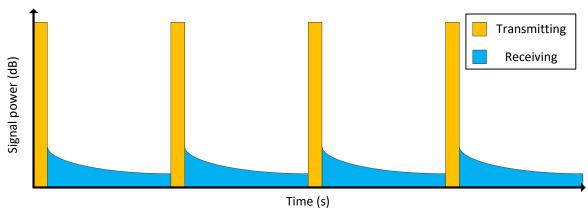

#### 2.3.2 Continuous and pulse radar

Pulsed radar operates by transmitting a short pulse, and remaining silent while listening for echoes [21], as shown in Figure 2.3. This architecture has been widely adopted as it reduces the dynamic range of the system by only receiving when the transmitter has stopped transmitting. Unfortunately, it also means that the echoes received from targets cannot be integrated over the entire CPI. Instead, each pulse can only be integrated for as long as its duration [21]. Thus, pulsed radars typically have a higher peak-to-average transmission power than continuous radar.

Figure 2.3 Diagram of pulsed radar signal strength.

Continuous radar transmits and receives signals simultaneously. This allows the echoes to be integrated over the entire CPI, thus allowing for reduced peak transmit power. One of the major challenges in CW radar is reducing the leak through from the transmitter to the receiver channel, which degrades the radar's performance [23].

Passive radar is a special case of bi/multistatic CW radar. DPI is a major design challenge in active CW, where the designer has control over the receiver and transmitter. In passive radar, where one cannot control the transmitter, DPI becomes a critical performance limiting factor.

#### 2.4 HISTORY OF FM-BASED PASSIVE RADAR

The first passive radar was developed as a by-product of the development of radar. This was during the Daventry experiment in 1935 [4]. This radar detected a Heyford bomber at a distance of 8 km using a shortwave radio transmitter. Other passive radar systems were also deployed by the German armed forces, which exploited the transmissions of the British Chain Home Radars [4].

After WWII little interest remained in passive radar until the advent of high performance digital signal processing hardware. In 1986 an experiment was conducted using television broadcasts [24], which were chosen due to their resemblance to a pulsed wave form. Due to the limitations posed by the available ADC hardware, the system was unable to successfully detect targets. However, the experiment uncovered the major challenges in passive radar (such as dynamic range), and thus opened the door to future work.

A further system was developed, in 1997 that exploited television broadcasts [25]. This system was able to detect aircraft at a range of 260km (with a direct path distance of 150km). While the system was able to detect aircraft at a vastly improved range, it was only able to determine their Doppler shift and bearing.

Further investigation into passive radar [26] was conducted in the 1990's [4]. The investigation found potential in broadcast transmitters as transmitters of opportunity, as well as an additional motivation for passive radar in that it holds potential for stealth mitigation.

FM-based passive radar was first introduced in 2005 [1]. A detailed design of the system was presented, which used SDRs to digitise the signal, and used a computing cluster to achieve real-time processing. The system was able to detect targets at up to a range of 150km, with a direct path distance of approximately 50 km. In the same year the theoretical performance of FM-based passive radar was published [27]. In this work, the radar range equation was derived in the context of passive radar.

In 2007 FM signals were analysed for their role in passive radar [28]. Here it was shown that the range resolution of the system is dependent on the standard deviation and kurtosis of the transmitted signal.

This led to an investigation into improving this limit, which in turn led to a method being developed that combined multiple FM-channels [29]. In the same work, a comparison between super heterodyne and direct receiver architectures was conducted. It found that, while comparable, the direct sampling architecture yielded performance advantages over the super-heterodyne architecture.

In 2010 an airborne passive radar demonstrator [30] was experimented. The system was able to detect high velocity airborne targets at ranges (as shown in the publication) up to 35 km. However, the signal had to be recorded and processed at a later stage.

A passive radar based on an SDR and using generic processing software was demonstrated in 2011 [10]. However, the system was only able to detect targets with a bistatic range of 63 km, with a direct path distance of approximately 47 km. The system was also unable to operate in real-time, and processing was performed on recorded signals.

A long-range FM-based passive radar was demonstrated in 2012 [31]. This was able to detect targets up to a range of 300 km, while 60 km from the transmitter. It was shown that a high dynamic range is essential for long range detection, and that a greater direct path distance lessens the required dynamic range requirement of the system.

In 2014, a generalised processing architecture for passive radar was presented [13]. Here the term "separated reference architecture" was coined, and an exploration into the use of GPU's was investigated.

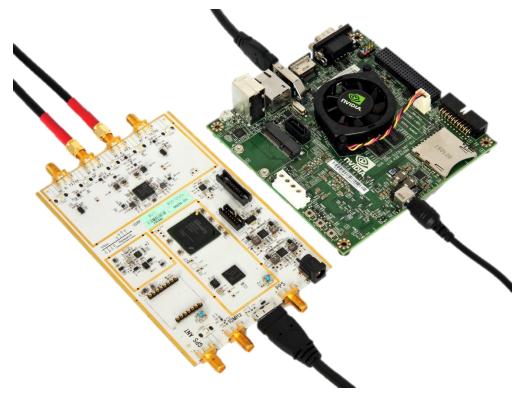

A system [11] using an SDR with a custom fixed frequency RF front-end [7], and an NVIDIA Jetson TK1 Development Board to process the data was demonstrated. The system

could detect targets up to a range of approximately 100 km, with a direct path distance of approximately 100 km. The system employed a CGLS filter to perform DPI cancellation, and was just able to run in real-time.

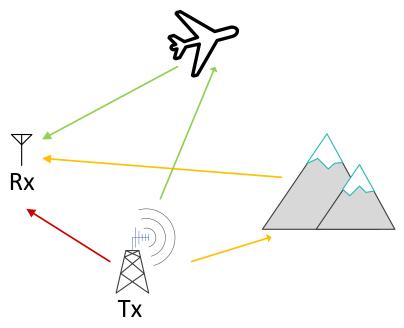

# 2.5 COMPONENTS OF THE RECEIVED SIGNALS AND ANTENNA CONFIGURATION

Theoretically, signals received by a passive radar's reference channel are composed of three major components [5], shown in Figure 2.4. The largest contribution is DPI, which is the signal received directly from the transmitter [2] (the red signal in Figure 2.4). The second largest contribution (the yellow signal) typically found in received passive signal consist of reflections from large stationary objects such as buildings, mountains and hills [2]. The final component (the green signal) is comprised of reflections from moving objects which are the reflections of interest [2].

Figure 2.4 Diagram of the signal components received by a passive radar.

A certain level of DPI is required by the passive radar system. However, it is only desirable in the reference channel [2]. The DPI (in a static system) has approximately no delay and no Doppler shift and thus approximately resides at a range of 0 km with a Doppler shift of 0 Hz. Clutter is a comparatively large signal, although smaller than the DPI, and is normally

characterised by a low Doppler shift, although its range (or delay) may vary. Finally, target reflections are characterised by a low signal amplitude with a significant Doppler shift generated by their higher velocities.

#### 2.6 PASSIVE RADAR PROCESSING

In order to detect target reflections among the much larger unwanted reflections, interference and noise, the signal needs to be filtered and processed. The components of the processing chain have been widely discussed in literature [11], and these are introduced below.

#### 2.6.1 Matched filtering

In order to increase the SINR, a matched filter is used to determine the probability of a reflection's presence. A matched filter is defined as a filter used to maximise the SNR of a target derived from the transmitted signal [21]. The mathematical description of the filter starts with the definition of the reference and surveillance channels as vectors r and s respectively. Given that a CPI consists of N samples s and r are both N element vectors.

The filter coefficients for the matched filter are given as

$$h(t) = \hat{r}^*(-t) \tag{2.1}$$

where

$\hat{r}$  is a delayed and/or modulated version of r, and t is time.

In pulse-Doppler radar this process is carried out in two steps [21]. In the first step each pulse is compressed by applying a matched filter via correlation. Following this, the second step uses a DFT on inter pulse samples to extract frequency, i.e. Doppler information. Doppler processing is one of the most valuable tools available to the radar designer, as it allows targets of interest (which are generally moving) to be distinguished according to their radial or bistatic velocity.

In continuous wave and passive radar (which is not taking advantage of a pulsed source) there are no pulses and, as such, pulse compression and Doppler processing are combined

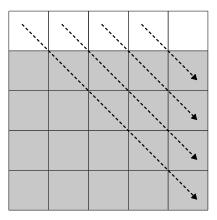

and performed simultaneously [12]. In passive radar this can be achieved by cross-correlating the surveillance and modified reference channel in either the time [12] or frequency domain [5]. These techniques are compared in Section 5.3, but a brief explanation of the differences is given below.

The time domain method is the closest to the pulse compression technique seen in pulse radar. In this method, each Doppler index is generated by cross-correlating the surveillance channel with an appropriately modulated reference channel in the time domain.

$$y(t) = \int_{-\infty}^{\infty} s(t)\hat{r}^*(-t) \, \partial t \tag{2.2}$$

Frequency correlation is the opposite, where each range index is generated by cross-correlating the surveillance channel with an appropriately delayed version of the reference channel in the frequency domain.

Before pulse compression and, therefore, the matched filter, the range resolution of the system is related to the pulse length. In CW radar this would make the range resolution equal to the CPI. However, pulse compression decouples these two parameters and instead couples the range resolution to the bandwidth of the transmitted signal, specifically [21]

$$\Delta R = \frac{c_0}{2B} \tag{2.3}$$

where

$c_0$  is the speed of light in a vacuum, and

B is the instantaneous bandwidth of the transmitted signal.

This has been shown to hold true for passive radar where B is the instantaneous bandwidth and  $\Delta R$  is the range resolution [32].

Target separation is also achievable in the Doppler dimension. Here the Doppler resolution is given as

$$\Delta R' = \frac{1}{CPI}. (2.4)$$

This is clearly more consistent than the range resolution, as it is not dependent on the transmitted signal, which in passive radar is not controllable or predictable.

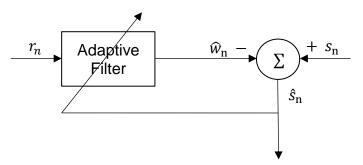

#### 2.6.2 DPI cancellation

As a result of the matched filter, the signal space is transformed to an amplitude-range-Doppler (ARD) map, with the amplitude representing the received signal strength at a range-Doppler index. However, the sidelobes from strong signal components mask the smaller desirable reflections [1]. In order to remove the sidelobes, the contribution of the large unwanted components is estimated and subtracted from the surveillance channel, [9] [2]

$$\hat{s} = s - A\hat{x} \tag{2.5}$$

where

$\hat{s}$  is the surveillance channel after cancellation,

A is a matrix of signal components which are removed, and

$\hat{x}$  is a vector of weights estimating the contribution of each of the signal components in A.

The estimation can be performed using a linear least-squares algorithm [2], a clean technique [9], adaptive filters [12] [33], or correlative cancellation.

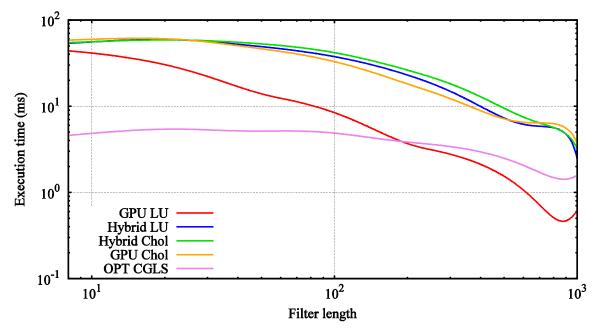

Studies have previously been conducted into effectiveness of various filters for the application of DPI cancellation. It has been found that Wiener-Hoph filters achieve near optimal performance [9], but can be computationally intensive. Some adaptive filters were found to have satisfactory performance [9], but incurs significant computational cost. CGLS has been proposed as an alternative to solve the least squares problem [13], with significantly fewer computations.

The various implementations are compared in Section 5.2, and an introduction to each is given in Addendum A.

#### 2.6.3 CFAR detection

CFAR is a common and well-studied automatic thresholding scheme used to detect targets in radar systems [21]. The technique is based on a likelihood ratio hypothesis test [21].

If the interference power is assumed to be Gaussian distributed, the variance of the noise is known, and a desired probability of false alarm  $(P_{FA})$  is given, a threshold which maximises the probability of detection  $(P_D)$  can be defined using the Neyman-Pearson bound [21]

$$T = \sqrt{-E\sigma_n^2 \ln(P_{FA})} \tag{2.6}$$

where

$\sigma_n^2$  is the variance of the interference, and

*E* is the energy in the matched filter coefficients.

In practice this is difficult to implement, as the interference level is often unknown and fluctuating. To compensate for this CFAR is used to estimate the interference variance.

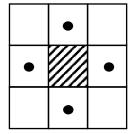

CFAR begins by defining a number of bins that are used to estimate the interference level.

Cell averaging is a simple CFAR technique and uses an average to estimate the interference. The threshold is then defined as

$$T_{CA} = \alpha_{CA} \hat{\sigma}_N^2 \tag{2.7}$$

with  $\alpha_{CA}$  the CFAR constant defined as [21]

$$\alpha_{CA} = N(P_{FA}^{-1/N} - 1).$$

(2.8)

In active radar, the interference bins can be allocated in all dimensions. This is because the range, angular, and Doppler resolution remain constant. In passive radar, however, the fluctuating bandwidth [32] in signals, transmitted by the transmitter of opportunity, causes the range resolution of the radar to fluctuate. This makes the choice of the number of guard bins in the range dimension difficult to determine and inconsistent. As such, in passive radar systems, interference estimation is often constrained to the Doppler and angular dimensions. Alternatively, the range resolution needs to be estimated before the detection stage.

#### 2.7 SUMMARY

FM-based passive radar is an extension of active continuous wave radars. It shares many of the same principles and performance characteristics. There are however, some additional challenges to face; key among these is DPI.

Passive radar has been around since the advent of radar, but FM-based passive radar only became useable in the early 2000s. Since then these systems have become cheaper and have been slowly maturing, but a successful system built on commercial OTS components has not been seen.

# **CHAPTER 3** SIGNAL ACQUISITION

The passive radar system designed is based on a commercial FM transmitter (88 to 108 MHz). The choice of using commercial FM transmitters was made as these transmitters typically transmit with high power, and coverage is readily present throughout Africa [34] (where this study was located).

The signal acquisition sub-system of a passive radar, as is depicted in Figure 2.1, can be broken into multiple sub-sections. The components of the signal acquisition subsystem are shown in Figure 3.1. Here there are two major divisions.

The first, site and transmitter selection (covered in Section 3.2), concerns receiving the most desirable analogue signals. The second, the receiver, is responsible for bringing the signals to baseband and digitising them.

**Figure 3.1** System diagram of the signal acquisition sub-system.

#### 3.1 PERFORMANCE FACTORS

Before delving into the sub-systems of signal acquisition, it worth understanding the major parameters and factors which govern the performance of the signal acquisition sub-system.

Similar to active radar, the objective of signal acquisition in passive radar is to maximise the signals received from potential targets and to minimise the signals received from interference and noise. To this extent, the passive radar may face similar restrictions to a conventional radar.

Noise is defined as, "an unwanted disturbances superposed upon a useful signal that tend to obscure its information content" [35]. Within the system there are many sources of noise, from thermal noise within components to jamming. Most of this noise is combated by using integration gain. However, there are also coherent sources of noise which must be intentionally removed. The major performance constraints and the factors which influence these are discussed below.

#### 3.1.1 Active interference

Active interferers are interferers which emit energy into the system's antennas within the band of operation. These interferers can take many forms, from pirate transmitters to intentional electronic attacks. Such interference reduces the performance of the system and can even result in false targets being produced.

Active jamming can affect the system in a number of ways, depending on the knowledge the attacking system has about the radar and the type of jamming implemented. However, in the context of the experimental system, a deliberate electronic attack is a fairly remote possibility. A more likely scenario is one where another transmitter is projecting energy in the band, unintentionally interfering with the radar.

There is little literature on the subject [36]. As such, a rudimentary analysis of the effect of a pirate transmitter on a passive radar is presented here. The reference signal is modelled as

$$r(t) = pk(t) + ql(t) + n(t)$$

(3.1)

where

k(t) is the normalised signal transmitted by the transmitter of opportunity,

l(t) is the normalised signal transmitted by the interfering source (assumed to be uncorrelated),

n(t) is AWGN, and

p and q are complex weights which account for the gain of the signals as received by the reference antenna.

The surveillance signal is modelled as

$$s(t) = rk(t) + sl(t) + m(t) + n(t)$$

(3.2)

where

m(t) comprises of target echoes received by the surveillance antenna, and r and s are complex weights which account for the gain of the signals as received by the surveillance antenna.

Therefore, in order to allow for successful DPI cancellation, by implementing (5.1),

$$\frac{p}{q} \approx \frac{r}{s} \tag{3.3}$$

must hold.

As there are likely to be spatial differences between sources, it is unlikely that this equality will hold, and, therefore, the cancellation will be impaired and targets are likely to be masked by the DPI's sidelobes. This analysis does not take into account the effect that an additional in-band transmitter will have on l(t), as well as the actual representation of targets. However, given the effect an additional interferer has on the reference signal and cancellation it can already be established that the presence of an additional, in-band interferer is highly detrimental to system performance. The high vulnerability is also found in simulations [36] where a noise jammer with a power output of 1-10 W (-77.10 dB to -57.10 dB compared to the transmitter power) has a dramatically detrimental effect on the radar. With a jammer transmit power of 10 W, the simulated radar was incapable of detecting the simulated target.

# 3.1.2 Sensitivity

Sensitivity of an electronic system can be described as the smallest signal level which can create a desired output. In a radar, sensitivity can also be termed as a minimum detectable signal [37]. In terms of the radar system, this level can be governed by a number of factors, although the level is predominantly governed by the receiver. i.e. the smallest signal which can be digitized. This level is determined by the receiver's capability to digitize a signal, as well as the efficiency with which energy is harvested and delivered to the receiver.

# 3.1.3 Dynamic range

The dynamic range of the system refers to the smallest signal which can be utilized compared to the largest. In terms of this specific system, dynamic range refers to the smallest signal which can be utilized compared to magnitude of the direct path signal (as the direct path signal can be assumed to be the largest signal present on the system [12].

The dynamic range of any digital system is related to the quantisation of the signal level. In a fixed point system, this level sets a minimum signal which can be represented relative to full scale. This level is referred to as the quantisation noise and is given as [38]

$$n_q = -6.02b - 1.76 \text{ dBFS}$$

(3.4)

where

b is the number of bits used for quantisation.

Equation (3.4) is, however, only a true representation when the signal is sampled at the Nyquist rate. Oversampling can effectively result in a higher dynamic range, or bit depth. The additional dynamic range in bits achieved by oversampling is [39]

$$b_{os} = \log_2\left(\frac{f_s}{f_N}\right) \tag{3.5}$$

where

$f_s$  is the sampling frequency, and

$f_N$  is the sampling frequency where  $f_N < f_s$ .

It should be noted that practically a few of the LSBs may not be correctly quantised by the ADC, and as such the theoretical dynamic range of the quantisation should be considered as a best-case scenario, rather than the expected value.

Aside from the dynamic range limitation imposed by digitisation, the analogue components of the receiver impose a limitation known as the SFDR. This limitation defines "the available signal range as the difference in magnitude between the amplitude of the fundamental and the amplitude of the largest spurious component in the frequency band of interest" [40]. The presence of the distortion effectively masks signals less powerful than it and thus limits the dynamic range. The dynamic range achieved is governed by the smallest of these ranges, presented above.

### 3.2 SITE AND TRANSMITTER SELECTION

The primary objective when selecting an appropriate site is to maximise the ratio between the received power from target and DPI (the reasoning for which is shown later in this section). Furthermore, due to relaxed filters found in lower end receivers, reducing just-out-of-band interference is also a consideration [7].

In order to find the optimal orientation/site, an estimation for the power received from a target and the DPI is required. This kind of estimation has been considered with in-depth models which take into account the terrain [41] and its effect on EM propagation [5]. However, this information was not available and, as such, a simpler model is considered where propagation and environmental effects are considered to be negligible.

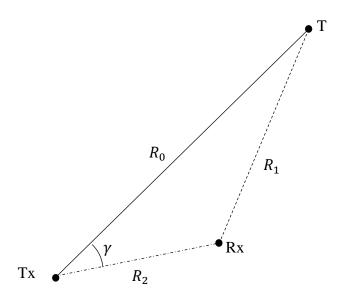

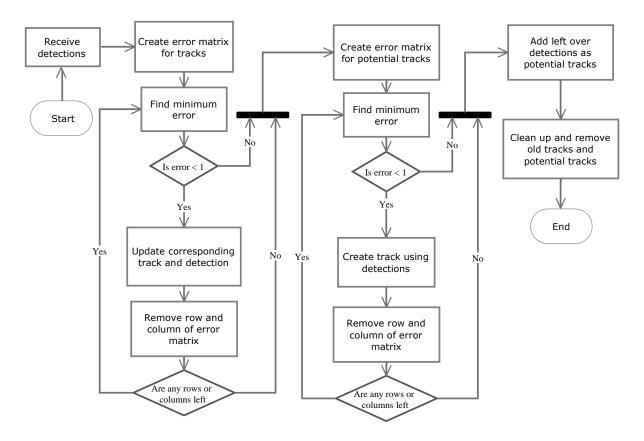

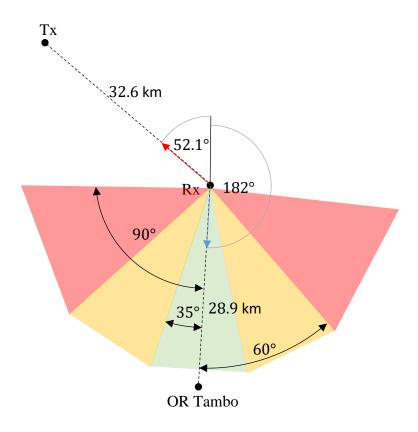

The layout of the environment is shown in Figure 3.2. In Figure 3.2 the transmitter is located at Tx and the target at T. The distance between T and Tx is given as  $R_0$ . The receiver is located at Rx with the distance between Rx and T denoted by  $R_1$  and the distance between Tx and Rx is denoted by  $R_2$ , i.e. the baseline distance. The angle between TxT and TxRx is given as  $\gamma$ .

Figure 3.2 Signals received at a passive radar site.

The power received from DPI can be approximated using the Friss transmission equation [42],

$$P_r = P_t G_r G_t \left(\frac{\lambda}{4\pi R}\right)^2 \tag{3.6}$$

where

$P_t$  is the power transmitted,

$G_t$  is the gain of the transmission antenna in the direction of transmission,

$G_r$  is the gain of the receive antenna in the direction of reception,

$\lambda$  is the wavelength of the carrier frequency, and

*R* is the distance between the reception and transmission antennas.

In the context of the passive radar environment this becomes

$$P_{DPI} = P_t G_{r2} G_t \left(\frac{\lambda}{4\pi R_2}\right)^2, \tag{3.7}$$

while power received from the target can be written by the bistatic radar equation [8] [43],

$$P_r = \frac{P_t G_r G_t \lambda^2 \sigma}{(4\pi)^3 R_{T_r}^2 R_{P_r}^2}$$

(3.8)

where

$R_{Tx}$  is the distance from the transmitter to the target, and

$R_{Rx}$  is the distance from the target to the receiver.

In terms of the environment in Figure 3.2, the power received from the target becomes

$$P_T = \frac{P_t G_r 1 G_t \lambda^2 \sigma}{(4\pi)^3 R_0^2 R_1^2}. (3.9)$$

Assuming that the transmission antenna is isotropic, the target to DPI ratio (TDR) becomes

$$TDR = \frac{G_{r1}R_2^2\sigma}{4\pi G_{r2}R_0^2R_1^2}. (3.10)$$

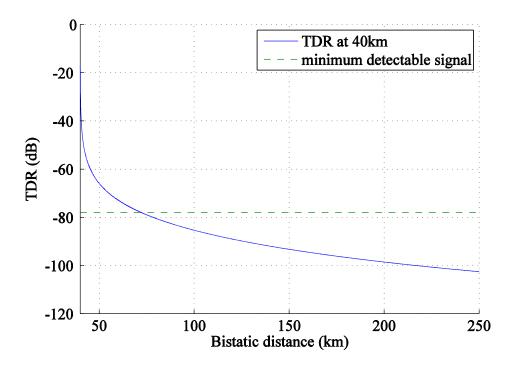

For example, it is assumed that a typical direct path distance of 40 km is present. The TDR, for this scenario, is shown in Figure 3.3. Here the TDR is that received at the site and, as such, both antenna gains are set to unity. The target is also set to exist on the vector originating at the receiver and crossing through the receiver which is shown in Section 3.2.1 to be the optimal configuration. The RCS of the target is set to be 100 m<sup>2</sup> which is representative of a large passenger aircraft [44].

Figure 3.3 Surveillance to direct path signal ratio.

Even in this near optimal configuration, the ADC has been fully saturated, and if no steps are taken to remove the DPI prior to digitisation, the maximum detectable bistatic range for

a receiver with a 78 dBc dynamic range is 72.0 km, which results in a 16.0 km distance from the receiver. It is, therefore, clear that, even in such convenient conditions, the radar would have a poor detection range for even the largest targets and is limited by the dynamic range of the receiver.

## 3.2.1 Optimal position

Setting the objective to maximise the TDR for a given target,  $R_1$  is then defined in terms of  $R_0$ ,  $R_2$ , and  $\gamma$ .

$$R_1^2(\gamma) = R_0^2 - 2R_0R_2\cos(\gamma) + R_2^2 \tag{3.11}$$

Therefore, it can be seen that  $R_1(\gamma)$  reaches maximum and minimum values

$$R_1(0) = R_0 - R_2 (3.12)$$

$$R_1(\pi) = R_0 + R_2 \tag{3.13}$$

with

$$TDR(0) = \frac{G_{r1}\sigma}{4\pi G_{r2}} \left( \frac{R_2^2}{R_0^2 (R_0 - R_2)^2} \right)$$

(3.14)

$$TDR(\pi) = \frac{G_{r1}\sigma}{4\pi G_{r2}} \left( \frac{R_2^2}{R_0^2 (R_0 + R_2)^2} \right). \tag{3.15}$$

Hence it can be seen that the TDR is maximised for a given range from the receiver when the site intersects the line between the transmitter and the target, i.e.  $\gamma = 0$ . Furthermore, it can be seen that, when  $\gamma = 0$ , as  $R_2$  increases so does the TDR, though this is intuitive as this moves the receiver closer to the target and further from the transmitter.

Additionally, the effect that increasing  $R_2$  has on the TDR with a constant  $R_1$ , needs to be determined, i.e. does increasing the direct path distance increase the surveillance range? Rewriting (3.14) in terms of  $R_1$  results in

$$TDR(0) = \frac{G_{r1}\sigma}{4\pi G_{r2}} \left(\frac{R_2}{R_1(R_1 + R_2)}\right)^2$$

(3.16)

which we can analyse using

$$\frac{R_2}{R_1 + R_2}. (3.17)$$

The expression in (3.17) begins at 0 when  $R_2 = 0$  and converges to 1 as  $R_2 \to \infty$ . Hence it can be seen that the TDR ratio is maximised when  $\gamma = 0$  and the baseline distance is maximised. The same result has been found in literature [31].

#### 3.2.2 Antenna selection

The requirements for a passive radar system differ slightly from conventional radar and communication systems. This is especially true in the directionless system considered in this report. The simplicity of the directionless system, does not allow nulls to be arbitrarily steered towards interference sources. Null steering has been shown to be an effective method of reducing interference and DPI [45].

#### 3.2.2.1 Surveillance antenna

The surveillance antenna has the primary function of receiving reflection from targets. As such, it should limit energy received from all other sources of radiation, primarily in-band sources. However, it should allow a wide beamwidth (in most cases) as to enable detection of targets from a wider range of angles [43].

There are two performance limiting parameters which a well-designed antenna can improve. The first is with the minimum signal power required for detection. This parameter is potentially limited by the sensitivity of the receiver. A higher gain in the direction of a target results in more energy being delivered to the receiver. The second is DPI rejection, which can be achieved by introducing nulls and low sidelobe levels in the direction of interference sources. However, it should be noted that beam width and gain are inversely related, as such both a wide beamwidth and a high gain cannot be achieved.

In passive radar this is not a common limitation as the minimum signal power required for detection is typically limited by the dynamic range of the receiver. The instantaneous dynamic range of the signal can be reduced by not receiving energy from the direct path. This appears in (3.10). The ratio between these gains,

$$G_p = \frac{G_{r1}}{G_{r2}},\tag{3.18}$$

represents the relative antenna gain between the direction of the direct path and the direction of the target.  $G_p$  can often have a significant influence over the TDR. As such, placing the antenna such that DPI lies in a null may be more beneficial than selecting an optimum position.

Therefore, selecting a surveillance antenna optimised for a high front-to-back ratio (or deep nulls) is more beneficial that an antenna optimised for absolute gain. This conclusion is only valid where the dynamic range of the receiver is the limiting factor.

#### 3.2.2.2 Reference antenna

The reference antenna is required to receive a copy of the transmitted signal. To this end, the signal received should match that transmitted as much as possible. However, in practice, it is found that non-idealities cause this not to be the case.

It was found that the main causes of poor reference signal recreation are multi-path [20] and antenna modulation. Multipath is caused by the transmitted signal reflecting off objects. These add additional signal components (similar to those which make up clutter in the surveillance channel) to the reference channel.

The additional components affect the cancellation filter by ensuring that each column of *A* not only affects its own range-Doppler index, but also those corresponding to the additional components (with the appropriate offsets). As these additional components are not ideally weighted, the flexibility of the filter is hindered, and it can no longer reach an optimal solution.

The matched filter is affected by correlating not only with the range-Doppler bin desired but also with the additional components. This increases cross-bin dependence and sidelobe levels.

Antenna modulation is the process where the movement of an antenna creates a modulation on the received signal. This can be seen on large flexible antennas. While the modulation is low, due to extremely long CPIs used in passive radar, it can have a large effect on the accuracy of the transmitted signal's copy received from the reference antenna.

A highly directional antenna with a narrow beam is desirable in order to limit the multipath received by the reference antenna. Antenna modulation is reduced by securing the antenna, or using a stable and inflexible design.

#### 3.2.3 Additional considerations

Beyond the position of the site, DPI rejection can be aided by placing the receiver behind a large object such as a hill or building, as depicted in Figure 3.1. This is termed DPI shielding. DPI shielding was found to be more effective than optimising the antenna pattern. It should be noted though, that large near-field structures alter the effective far-field antenna pattern of the antennas (although to an extent this is the objective with the DPI shielding). Consequently, the effectiveness of using a directional antenna can be inhibited. The effective antenna patterns must, therefore, be considered within their respective operational environments and not as independent element.

### 3.2.4 Transmitter selection

Transmitter selection is based on a number of factors but ultimately aims to increase SDR while ensuring that the transmitted signals remain as powerful as possible. In a system with poorer analogue filtering, a more powerful transmitter (in comparison to other sources in the spectral vicinity) is desirable as this improves the ratio between the desired signals and those of other transmitters, which in turn, results in the ADC being more effectively utilized, and thus enhancing its performance.

Finally, in the case where TDR is no longer the defining performance factor, a stronger transmitter increases the distance at which a target's reflection would fall within the minimum power receivable by a receiver [43].

### 3.3 RECEIVER SELECTION

The RF digital receiver, used to sample the reflections, is one of the most vital pieces of hardware in the system, due to its role sampling the EM spectrum into digital space. The receiver imposes fundamental limits on the system by defining the dynamic range, being the source of quantisation and other noise sources [7], and establishing and limiting the coherency between channels. Essentially, if the receiver fails to capture a signal, or distorts it, no amount of processing can detect or recreate it.

**Table 3.1** Potential receivers.

| Receiver   | ADC      | Operating | Analogue    | SFDR  | Price per unit [\$] |

|------------|----------|-----------|-------------|-------|---------------------|

|            | bits/Rx  | Frequency | bandwidth   | [dBc] |                     |

|            | channels | [MHz]     | range [MHz] |       |                     |

| Pervices   | 16/4     | 0 - 6000  | 322         | 40    | 6750-00             |

| Crimson    |          |           |             |       |                     |

| Ettus USRP | 14/1     | 40 - 2200 | 40          | 88    | 1717-00             |

| N210 (WBX) |          |           |             |       | (480-00)            |

| Ettus USRP | 12/2     | 70 – 6000 | 0.2 - 56    | 78    | 1100-00             |

| B210       |          |           |             |       |                     |

| Epiq       | 12/2     | 70 – 6000 | 0.4 - 50    | 68.7  | 8000-00             |

| solutions  |          |           |             |       |                     |

| sidekiq    |          |           |             |       |                     |

| Quadrus    | 16/2     | DC - 437  | 0.0008 - 40 | 80    | 1990-00             |

| DRU-244A-  |          |           |             |       |                     |

| 2-2-PCI    |          |           |             |       |                     |

| Airspy     | 12/1     | 24 – 1800 | 6 – 9       | 80    | 199-00              |

| HackRF One | 8/1      | 1 – 6000  | 1.75 – 20   | _     | 299-95              |

| RTL-SDR    | 8/1      | 24 - 1760 | ? -2.8      | ~45   | 19-95               |

| Dongle     |          |           |             |       |                     |

The receiver constitutes a large portion of the system's cost, as such, keeping the receiver's cost to a minimum had a large, positive, benefit on the system's cost. However, due to the importance of the receiver within the system, this cost saving had to be balanced against the receiver's performance, minimising cost without hindering the system's operation.

To achieve these goals, a range of SDRs were considered as they allowed for a configurable system with a software definable bandwidth and frequency, while still residing at a comparatively low price point. Any receiver considered must be able to operate in a configuration where at least two channels are synchronously and coherently sampled. The absence of thereof would render the reference and surveillance channels incoherent, resulting in any of the subsequent signal processing being ineffective. The receivers which were found to be potentially suitable for use as a low-cost passive radar receiver are shown in Table 3.1.

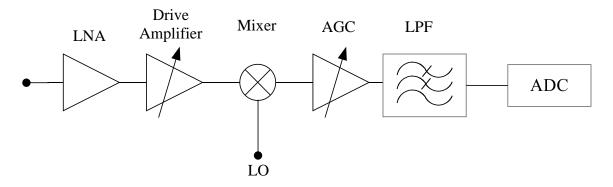

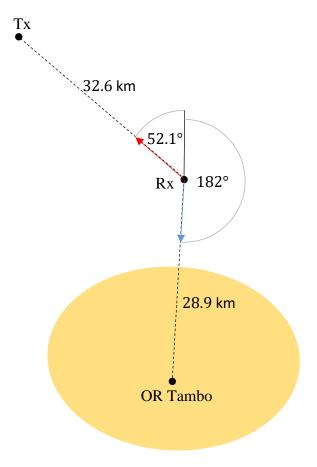

From Table 3.1 it can be seen that while some receivers can support narrow bandwidths, the majority are designed for wider bandwidth systems. Furthermore, it should be noted that even when the analogue bandwidth is narrow, due to the design of the RF receiver chain, full use of the ADC is not possible in congested spectra. An example of a common RF chain is shown in Figure 3.4. In this receiver chain the AGC is placed before the LPF. This is done in architectures such as the Ettus B210, Ettus WBX daughter board and Epiq solutions sidekiq.

Figure 3.4 Super heterodyne RF receiver chain.

This architecture results in the AGC setting the gain such that the sum of all the mixed down signals would saturate either the AGC amplifier or the ADC. The issue arises when the signals of interest are of sufficiently small bandwidth and amplitude that the power of the signal entering the LPF and leaving the LPF are significantly different. This architecture is used for its simplicity and to lower noise in wide bandwidth environments.

In the case of passive radar, the surveillance signal is usually smaller than other signals in the FM band. This results in the above architecture limiting the saturation level of the ADC, thus decreasing the effective bit depth and SFDR.

Two receivers were then chosen for further investigation. The USRP B210 was chosen as it allows for both channels to be supported on a single board, with a low price point and configurable analogue bandwidth. The USRP N210 was chosen as, although it resides at a higher price point, it has a larger SFDR and bit depth.

The Airspy and RTL-SDR were not chosen as they do not have digital synchronisation, and as such, significant development and/or processing would be required to ensure synchronous reception of data from the devices. The Quadrus was also not investigated as it uses direct sampling and, as such, it requires additional filtering to prevent aliasing, which increases the development time and cost. The Pervices Crimson and Epiq solutions Sidekiq where not evaluated as neither offered sufficient performance to justify the cost.

### 3.3.1 Channel coherency

The coherency between two receiver channels was evaluated. Intra-channel coherency is required as the processing blocks require that the reference and surveillance channels are coherent. This requires the channels to keep a constant phase difference and relative amplitude. It has been previously show that degradation in channel coherency significantly degrades SNR during processing [46].

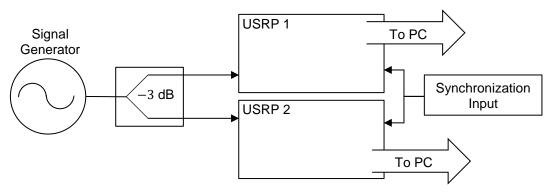

The phase stability was evaluated at 94.2 MHz as this corresponds with the frequency of a local radio station used to implement the radar (see Section 3.2.4). The experimental configuration is shown in Figure 3.5. A -10 dBm sinusoidal signal was generated using a signal source and fed through a power splitter directly to the inputs of each Rx channel on the receiver. This configuration ensured that the signals fed to the Rx channels were as coherent as possible.

Figure 3.5 Phase stability evaluation configuration for N210.

The sample streams from the receivers were then saved to file and processed offline to evaluate the coherency of each channel. This methodology ensures that any significant incoherency was solely resultant from the receiver/s.

Four receiver configurations were evaluated, the means by which synchronisation is achieved is discussed later in this chapter. The configurations evaluated are:

- 2x N210s with WBX daughter boards, synchronised via a MIMO cable,

- 2x N210s with WBX daughter boards, synchronised via a PPS system,

- a standalone B210, and

- a B210 using an external reference and PPS source.

Two synchronisation methods are provided by the USRP manufacturer to synchronise boards. The first is a MIMO cable which is a plug-and-play solution allowing two boards to share digital and analogue reference signals. The second is the PPS system which requires that a 10 MHz reference sinusoid and a PPS signal (i.e. a block wave with a period of 1 Hz) be fed to each board.

The experimental configuration was set to gather samples at a rate of 200 kS/s for 15 minutes.

### **3.3.1.1** Metrics

The metrics used to evaluate the data collected are defined below.

### **Phase Noise**

Relative phase is the difference in phase between two samples of the same signal. The phase error between two samples is calculated as

$$\phi_i = \arg(x_i y_i^*). \tag{3.19}$$

The phase noise for the channel is defined as the RMS phase noise between two vectors,

$$\varphi = \sqrt{\frac{1}{N} \sum_{i=1}^{N} \phi_i^2} - \frac{1}{N} \sum_{i=1}^{N} \phi_i.$$

(3.20)

### Phase drift

Phase drift is defined as the long term deviation in the relative phase between two channels. The major causes of phase drift in the receivers were found to be PLL slipping/ loss of lock and oscillator frequency offset. The phase drift was evaluated by fitting a line to the unwrapped relative phase between the channels. The gradient of that line is then the mean phase drift. The gradient for the line of best fit for a set of data is given as

$$m = \frac{\sum_{i=1}^{N} (x_i - \bar{x})(y_i - \bar{y})}{\sum_{i=1}^{N} (x_i - \bar{x})^2}$$

(3.21)

where

$x_i$  and  $y_i$  are elements of the data coordinates x and y, and

$\overline{a}$  represents the mean of a vector a.

In the context of the phase drift (3.21) becomes

$$\Delta \phi = \frac{\sum_{i=1}^{N} (t_i - \bar{t})(\phi_i - \bar{\phi})}{\sum_{i=1}^{N} (t_i - \bar{t})^2}$$

(3.22)

where

t is a vector containing the times at which the samples were taken, and

$\phi$  is a vector of containing the relative phase between two channels.

# 3.3.1.2 Synchronisation

Achieving synchronisation between boards is achievable using several methods which provided by the SDR OEM. Only two of these were relevant to this implementation and are described below.

#### MIMO cable

Synchronisation via MIMO cable uses a plug-and-play cable which allows one USRP to act as a slave to another, piggybacking on the host's synchronisation and data link to the PC. A MIMO cable allows a maximum of two SDRs to be synchronised.

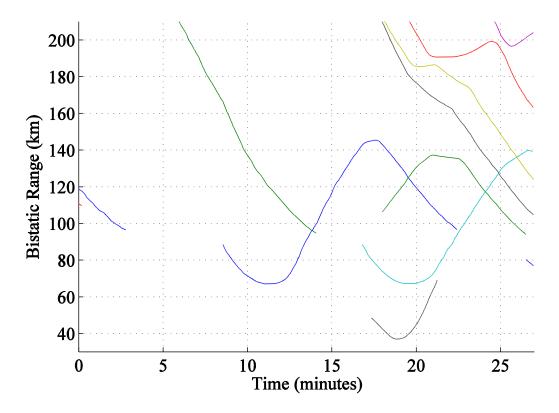

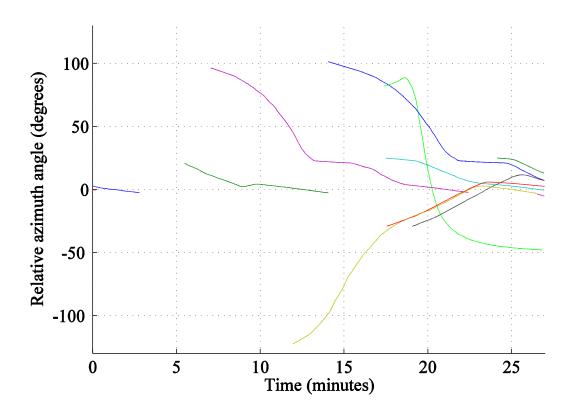

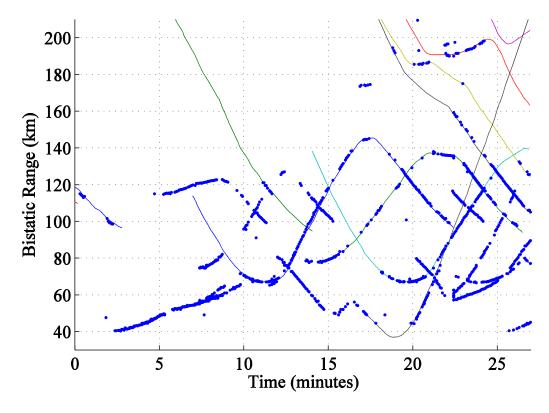

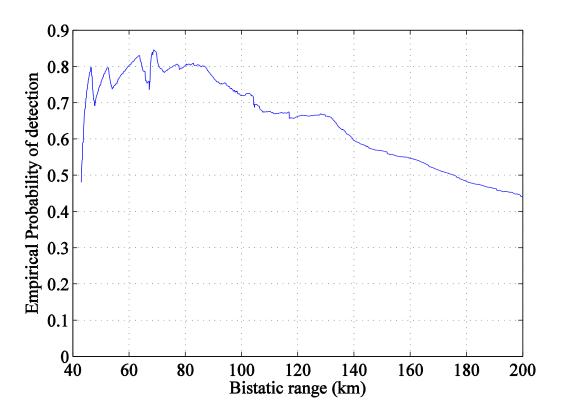

#### **PPS**