# CONDUCTED EMC MODELLING IN MODERN DC-DC POWER CONVERTERS

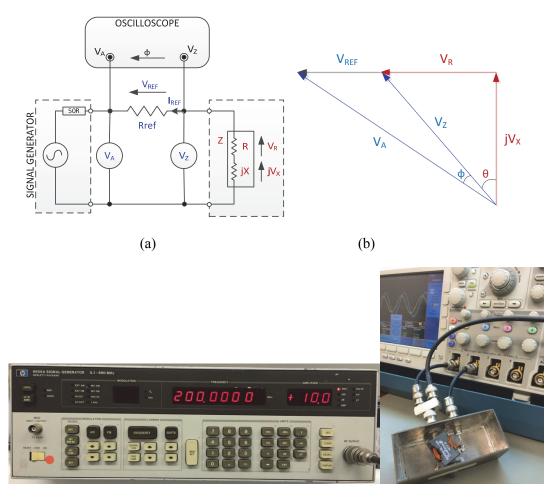

by

# **Inus Grobler**

Submitted in partial fulfilment of the requirements for the degree

Philosophiae Doctor (Electrical Engineering)

in the

Department of Electrical, Electronic and Computer Engineering

Faculty of Engineering, Built Environment and Information Technology

# UNIVERSITY OF PRETORIA

8 February 2017

### CONDUCTED EMC MODELLING IN MODERN DC-DC POWER CONVERTERS

by

#### **Inus Grobler**

| Supervisor: | Prof M. N. Gitau                                              |

|-------------|---------------------------------------------------------------|

| Department: | Electrical, Electronic and Computer Engineering               |

| University: | University of Pretoria                                        |

| Degree:     | Philosophiae Doctor (Electrical Engineering)                  |

| Keywords:   | Conducted EMC, conducted EMI, common-mode, differential-mode, |

|             | LISN, accreditation, component proximity, DC-DC conversion,   |

|             | components modelling, EMI modelling, LISN                     |

Conducted Electromagnetic Compatibility (EMC) is studied. High-density high-switching frequency modern power converter conducted Electro-Magnetic Interference (EMI) for low power applications, within the automotive and handheld applications, have been analysed. The noise source and path were modelled with accurate conducted Electro Magnetic Compatibility (EMC) noise levels comparable to accredited MIL-STD-461F noise measurements (100 kHz to 10 MHz) and expanded to 100 MHz. Common-mode conducted emissions in the high frequency band (beyond 30 MHz), were shown to appear as radiated emissions. A general lumped element high frequency analyses model was developed and verified utilising different analysis packages for accuracy, affordability and ease of use. Furthermore, the common-mode and differential-mode signals were separated digitally from the recorded Line Impedance Stabilising Network (LISN) data. These separations were verified for accuracy with a wideband LINDGREN EMC high frequency current probe.

Conducted noise effects of multilevel, multiphase and synchronous converters were investigated. In addition, the effects of very high switching frequencies on noise levels are presented. In addition, the effect of combining electrically conductive and non-conductive polymer heatsinks reducing common-mode noise was investigated. This will be shown to be a viable and very effective possible solution to reduce the increased common-mode noise levels due to higher switching frequencies.

# GELEIDENDE EMV MODELLERING IN MODERNE GS-GS KRAGOMSETTERS

deur

#### **Inus Grobler**

| Studieleier:   | Prof M. N. Gitau                                              |

|----------------|---------------------------------------------------------------|

| Departement:   | Elektriese, Elektroniese en Rekenaaringenieurswese            |

| Universiteit:  | Universiteit van Pretoria                                     |

| Graad:         | Philosophiae Doctor (Elektriese Ingenieurswese)               |

| Sleutelwoorde: | Geleidende EMV, Geleidende EMS, Gemeenskaplike modus,         |

|                | Differensiaalmodus, Akkreditasie, Komponent Nabyheidseffekte, |

|                | GS-GS Omsetters, Komponent Modellering, EMV Modellering,      |

|                | LISN                                                          |

Geleidende Elektromagnetiese Steurings (EMS) is ontleed vir moderne draagbare kragomsetters met hoë pakkingsdigthede sowel as hoë skakelfrekwensies. Die bron van die geraas asook die voerpad is gemodelleer en die resulterende geraasvlakke is vergelykbaar met Elektromagnetiese Versoenbaarheid (EMV) opstelling soos vervat in MIL-STD-461F (100 kHz tot 10 MHz) maar die ontleding daarvan is uitgebrei tot by 100 MHz. Daar is verder bewys dat die gemeenskaplike modus bokant 30 MHz uitstraalvlakke toon. 'n Algemene hoë frekwensie stroombaan elementmodel is ontwikkel en ontleed. Die resultate van verskillende analiseringspakkette is vergelyk met die werklike metings wat betref akkuraatheid, bekostigbaarheid en gemak vir die gebruiker as kriteria. Verder is die gemeenskaplike modus- en differensiaalseine digitaal geskei van die Lynimpedansie Stabiliseeringsnetwerk (LISN) data. Die akkuraatheid van die skeidingstegniek is vergelyk met metings van 'n wyeband LINDGREN EMV hoë frekwensie stroomtaster.

Die geraaseffekte van multivlak en multifase asook gesinchroniseerde omsetters is verder ondersoek. Die gevolge van baie hoë skakelfrekwensies op geraasvlakke is ook ontleed en verduidelik. Verder is die gebruik van 'n termies-geleide polimeer hitteput ondersoek met die oog op die vermindering van gemene modus geraas. Dit bewys dat polimeer hitteputte 'n lewensvatbare en effektiewe oplossing bied om die verhoogde gemenemodus geraasvlakke te verminder.

# LIST OF ABBREVIATIONS

| ABM      | Analog Behavioural Model                                                                                                              |

|----------|---------------------------------------------------------------------------------------------------------------------------------------|

| ACEC     | Advisory Committee on Electromagnetic Compatibility (International Electrotechnical Commission; Switzerland)                          |

| ANSI     | American National Standards Institute                                                                                                 |

| Aux.     | Auxiliary                                                                                                                             |

| BGA      | Ball Grid Array                                                                                                                       |

| CDN      | Coupling/Decoupling Network                                                                                                           |

| CE       | Conducted Emissions (MIL-STD-461-F)                                                                                                   |

| CEN      | Comité Européen de Normalisation (French: European Committee for Standardization)                                                     |

| CENELEC  | Comité Européen de Normalisation Électrotechnique (French: European<br>Committee for Electrotechnical Standardisation)                |

| CISPR    | Comité International Spécial des Perturbations Radioélectriques (Special<br>International Committee on Radio Interference; est. 1934) |

| CNC      | Computer Numerical Control                                                                                                            |

| .CSV     | Comma Separated Values (datafile)                                                                                                     |

| Cu       | Copper                                                                                                                                |

| CSIR     | Counsel of Scientific and Industrial Research                                                                                         |

| DCB      | Direct Copper Bond                                                                                                                    |

| DC-DC    | Direct Current to Direct Current                                                                                                      |

| DCE      | Defence Conducted Emission (DEF STAN 59-411)                                                                                          |

| DEF STAN | Defence Standard (UK)                                                                                                                 |

| DIN      | Deutsches Institut für Normung eV (Institute for Standardization; similar to US ANSI)                                                 |

| DoD      | Department of Defence (USA)                                                                                                           |

| DUT      | Device Under Test                                                                                                                     |

| EM      | Electromagnetic                                                 |

|---------|-----------------------------------------------------------------|

| EMC     | Electromagnetic Compatibility                                   |

| EMI     | Electromagnetic Interference                                    |

| ESL     | Effective Series Inductance                                     |

| ESR     | Effective Series Resistance                                     |

| ETSI    | European Telecommunications Standards Institute (France)        |

| EUT     | Equipment Under Test                                            |

| eV      | eingetragener Verein (registered association)                   |

| FEA     | Finite Element Analysis                                         |

| FCC     | Federal Communications Commission                               |

| FM      | Frequency Modulation                                            |

| GaN     | Gallium Nitride                                                 |

| GPIB    | General Purpose Interface Bus                                   |

| HF      | High Frequency (3 MHz to 30 MHz)                                |

| IEC     | International Electrotechnical Commission (Geneva, Switzerland) |

| IEEE    | Institute of Electrical and Electronics Engineers               |

| IET     | Industrial Engineering Technology                               |

| ISO     | International Organisation for Standardisation                  |

| IT      | Information Technology                                          |

| ITU     | International Telecommunication Union                           |

| JESTPE  | Journal of Emerging and Selected Topics in Power Engineering    |

| LED     | Light Emitting Diode                                            |

| LISN    | Line Impedance Stabilisation Network                            |

| MathCAD | Mathematical Computer Aided Device Software Package             |

| MATLAB  | Matrix Laboratory Software Package                              |

| NATO    | North Atlantic Treaty Organization                              |

| NTIA   | National Telecommunications and Information Administration |

|--------|------------------------------------------------------------|

| PC     | Private Computer                                           |

| PCB    | Printed Circuit Board                                      |

| PDN    | Passive Distribution Network                               |

| PSIM   | Power Simulation Package                                   |

| PWM    | Pulse Width Modulation                                     |

| QP     | Quasi-Peak                                                 |

| R&S    | Rohde&Schwarz                                              |

| RTCA   | Radio Technical Commission for Aeronautics                 |

| SiC    | Silicon Carbide                                            |

| SPICE  | Simulation Program with Integrated Circuit Emphasis        |

| STANAG | Standardization Agreement (for NATO)                       |

| ТС     | Technical Committee                                        |

| .TNO   | Transient Numeric Output (Spectrum Software File)          |

| USA    | United States of America                                   |

| USB    | Universal Serial Bus                                       |

| VF     | Vector Fitting                                             |

| VHF    | Very High Frequency (30 MHz to 300 MHz)                    |

| VG     | Verteidigungs Geräte (Defense Structure)                   |

| via    | Vertical Interconnected Access                             |

# LIST OF SYMBOLS

| А                                                                                                              | Waveform Amplitude [V]                                                                                                                                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>c</sub>                                                                                                 | Core Cross Section [m <sup>2</sup> ]                                                                                                                                                                                                                                                                           |

| A <sub>cu</sub>                                                                                                | Copper Area [m <sup>2</sup> ]                                                                                                                                                                                                                                                                                  |

| A <sub>t</sub>                                                                                                 | Tab Area [m <sup>2</sup> ]                                                                                                                                                                                                                                                                                     |

| $A_v$                                                                                                          | Amplifier Gain                                                                                                                                                                                                                                                                                                 |

| $A_{\rm w}$                                                                                                    | Wire Area [m <sup>2</sup> ]                                                                                                                                                                                                                                                                                    |

| B <sub>max</sub>                                                                                               | Maximum Magnetic Flux Density [T]                                                                                                                                                                                                                                                                              |

| b                                                                                                              | PCB Trace Thickness [m]                                                                                                                                                                                                                                                                                        |

| α                                                                                                              | Damping Coefficient                                                                                                                                                                                                                                                                                            |

| Κ                                                                                                              | Cathode                                                                                                                                                                                                                                                                                                        |

| C <sub>0</sub>                                                                                                 | Low Frequency Capacitance [F]                                                                                                                                                                                                                                                                                  |

| $C_{cg}$                                                                                                       | Collector-Gate Capacitance [F]                                                                                                                                                                                                                                                                                 |

| C                                                                                                              | Diada Canacitanaa [F]                                                                                                                                                                                                                                                                                          |

| C <sub>Diode</sub>                                                                                             | Diode Capacitance [F]                                                                                                                                                                                                                                                                                          |

| C <sub>Diode</sub><br>C <sub>ds</sub>                                                                          | Drain-Source Capacitance [F]                                                                                                                                                                                                                                                                                   |

|                                                                                                                |                                                                                                                                                                                                                                                                                                                |

| C <sub>ds</sub>                                                                                                | Drain-Source Capacitance [F]                                                                                                                                                                                                                                                                                   |

| $C_{ds}$<br>$C_{gd}$                                                                                           | Drain-Source Capacitance [F]<br>Gate-Drain Capacitance [F]                                                                                                                                                                                                                                                     |

| C <sub>ds</sub><br>C <sub>gd</sub><br>C <sub>ge</sub>                                                          | Drain-Source Capacitance [F]<br>Gate-Drain Capacitance [F]<br>Gate-Emitter Capacitance [F]                                                                                                                                                                                                                     |

| C <sub>ds</sub><br>C <sub>gd</sub><br>C <sub>ge</sub>                                                          | Drain-Source Capacitance [F]<br>Gate-Drain Capacitance [F]<br>Gate-Emitter Capacitance [F]<br>Gate-Emitter Capacitance [F]                                                                                                                                                                                     |

| C <sub>ds</sub><br>C <sub>gd</sub><br>C <sub>ge</sub><br>C <sub>gs</sub>                                       | Drain-Source Capacitance [F]<br>Gate-Drain Capacitance [F]<br>Gate-Emitter Capacitance [F]<br>Gate-Emitter Capacitance [F]<br>Gate-Source Capacitance [F]                                                                                                                                                      |

| $C_{ds}$<br>$C_{gd}$<br>$C_{ge}$<br>$C_{gs}$<br>$C_{H0}$                                                       | Drain-Source Capacitance [F]<br>Gate-Drain Capacitance [F]<br>Gate-Emitter Capacitance [F]<br>Gate-Emitter Capacitance [F]<br>Gate-Source Capacitance [F]<br>Heatsink-Zero-Volt-Plane Capacitance [F]                                                                                                          |

| C <sub>ds</sub><br>C <sub>gd</sub><br>C <sub>ge</sub><br>C <sub>gs</sub><br>C <sub>H0</sub><br>C <sub>HC</sub> | Drain-Source Capacitance [F]<br>Gate-Drain Capacitance [F]<br>Gate-Emitter Capacitance [F]<br>Gate-Emitter Capacitance [F]<br>Gate-Source Capacitance [F]<br>Heatsink-Zero-Volt-Plane Capacitance [F]<br>Heatsink-Chassis Capacitance [F]                                                                      |

| C <sub>ds</sub><br>C <sub>gd</sub><br>C <sub>ge</sub><br>C <sub>gs</sub><br>C <sub>H0</sub><br>C <sub>HC</sub> | Drain-Source Capacitance [F]<br>Gate-Drain Capacitance [F]<br>Gate-Emitter Capacitance [F]<br>Gate-Emitter Capacitance [F]<br>Gate-Source Capacitance [F]<br>Heatsink-Zero-Volt-Plane Capacitance [F]<br>Heatsink-Chassis Capacitance [F]<br>Heatsink-Diode Capacitance [F]                                    |

| Cds<br>Cgd<br>Cge<br>Cgs<br>CH0<br>CHC<br>CHD<br>CHD                                                           | Drain-Source Capacitance [F]<br>Gate-Drain Capacitance [F]<br>Gate-Emitter Capacitance [F]<br>Gate-Emitter Capacitance [F]<br>Gate-Source Capacitance [F]<br>Heatsink-Zero-Volt-Plane Capacitance [F]<br>Heatsink-Chassis Capacitance [F]<br>Heatsink-Diode Capacitance [F]<br>Heatsink-MOSFET Capacitance [F] |

| C <sub>iss</sub>   | Input Transfer Capacitance [F]                      |

|--------------------|-----------------------------------------------------|

| C <sub>j</sub>     | Junction Capacitance [F]                            |

| C <sub>LEAD</sub>  | Power Lead Capacitance [F]                          |

| C <sub>M</sub>     | Miller E ffect Capacitance [F]                      |

| C <sub>MD</sub>    | MOSFET-Diode Capacitance [F]                        |

| C <sub>n</sub>     | Complex Fourier Expression                          |

| C <sub>oss</sub>   | Output Transfer Capacitance [F]                     |

| Cout               | Output Capacitance [F]                              |

| C <sub>PCB</sub>   | PCB Capacitance to Ground [F]                       |

| C <sub>rss</sub>   | Reverse Transfer Capacitance [F]                    |

| C <sub>P</sub>     | Parallel Capacitance [F]                            |

| C <sub>p</sub>     | Package Capacitance [F]                             |

| C <sub>Plate</sub> | Parallel Plate Capacitance [F]                      |

| D                  | Duty Cycle [%]                                      |

| D1                 | Component Identification: Diode                     |

| $D_{\mathrm{H}}$   | Diameter Helmholtz Coil                             |

| D <sub>M</sub>     | Density of conducted material [g.cm <sup>-3</sup> ] |

| d                  | Diameter of Wire [m]                                |

| di                 | Insulator Thickness [m]                             |

| δ                  | Unit Impulse Function                               |

| e                  | Percentage winding eddy current loss                |

| 60                 | Permittivity of air, 8.854 x $10^{-12}$ [F/m]       |

| ٤ <sub>r</sub>     | Relative Permittivity                               |

| F                  | Short Circuit Current Factor                        |

| $\mathbf{f}_{prf}$ | Parallel Resonant Frequency [Hz]                    |

| $\mathbf{f}_{s}$   | Switching Frequency [Hz]                        |

|--------------------|-------------------------------------------------|

| $\mathbf{f}_{srf}$ | Series Resonant Frequency [Hz]                  |

| φ                  | Magnetic Flux [Wb]                              |

| Н                  | Magnetic Field [A/m]                            |

| $H_X$              | Magnetic Field in X-Direction [A/m]             |

| h                  | Distance / Height [m]                           |

| h <sub>s</sub>     | Specific Heat of Conductor Material [J/gK]      |

| θ                  | Angle [°]                                       |

| $\theta_{T}$       | Temperature rise [K]                            |

| Ι                  | Current [A]                                     |

| i <sub>D</sub>     | Diode Current [A]                               |

| I <sub>CM</sub>    | Common Mode Current [dBµA]                      |

| I <sub>DM</sub>    | Differential Mode Current [dBµA]                |

| J                  | Winding current density in [A/m <sup>2</sup> ]  |

| j                  | Complex Notation $\sqrt{-1}$                    |

| k                  | Heat Transfer Coefficient [W/m <sup>2</sup> -K] |

| L                  | Inductance [H]                                  |

| L1                 | Component Identification: Inductor              |

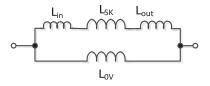

| L <sub>0V</sub>    | Zero-volt Trace Inductance [H]                  |

| L <sub>ce</sub>    | Collector-Emitter Inductance [H]                |

| L <sub>PCB</sub>   | PCB Trace Inductance [H]                        |

| L <sub>d</sub>     | Drain Inductance [H]                            |

| L <sub>Diode</sub> | Diode Inductance [H]                            |

| Le                 | Emitter Inductance [H]                          |

| L <sub>ESL</sub>   | Equivalent Series Inductance [H]                |

| Lg                | Gate Inductance [H]                            |

|-------------------|------------------------------------------------|

| L <sub>ge</sub>   | Gate-Emitter Inductance [H]                    |

| L <sub>GND</sub>  | Ground Lead Inductance [H]                     |

| L <sub>IN</sub>   | Input PCB Inductance [H]                       |

| L <sub>Lead</sub> | Power Lead Inductance [H]                      |

| L <sub>OUT</sub>  | Output PCB Inductance [H]                      |

| L <sub>p</sub>    | Package Inductance [H]                         |

| Ls                | Source Inductance [H]                          |

| L <sub>SK</sub>   | Source to Cathode Trace Inductance [H]         |

| l                 | Length [m]                                     |

| l <sub>cu</sub>   | Copper Wire Length [m]                         |

| le                | Magnetic Path Length [m]                       |

| λ                 | Wavelength [m]                                 |

| m, n              | Real Values                                    |

| Ν                 | Turns                                          |

| р                 | Arbitrary Point                                |

| $p_n$             | n <sup>th</sup> Pole                           |

| ρ                 | Resistivity of conducted material $[\Omega.m]$ |

| Q                 | Quality Factor                                 |

| Q1                | Component Identification: MOSFET               |

| q                 | Heat Flux [W/m <sup>2</sup> ]                  |

| r <sub>d</sub>    | Diode Resistance[ $\Omega$ ]                   |

| R                 | Resistance $[\Omega]$                          |

| R <sub>ESR</sub>  | Equivalent Series Resistance $[\Omega]$        |

| $R_0$             | On Resistance[ $\Omega$ ]                      |

| 10                |                                                |

| R <sub>gd</sub>   | Gate-Drain Resistance[ $\Omega$ ]      |

|-------------------|----------------------------------------|

| R <sub>gs</sub>   | Gate-Source Resistance[ $\Omega$ ]     |

| R <sub>H</sub>    | Radius Helmholtz Coil [m]              |

| R <sub>Load</sub> | Load resistor $[\Omega]$               |

| R <sub>P</sub>    | Parallel Resistance $[\Omega]$         |

| R <sub>s</sub>    | Series Resistance $[\Omega]$           |

| ρ                 | Resistivity [Ω-m]                      |

| $ ho_{cu}$        | Resistivity of Copper $[\Omega-m]$     |

| r                 | Radius [m]                             |

| r <sub>n</sub>    | n <sup>th</sup> Residue                |

| S                 | Surface Area [m <sup>2</sup> ]         |

| $S_L$             | Surface Area of Loop [m <sup>2</sup> ] |

| S                 | Distance [m]                           |

| s11               | Return-loss Scattering Parameters      |

| s21               | Transfer Scattering Parameters         |

| σ                 | Conductivity [S/m]                     |

| $\sigma_{cu}$     | Conductivity of Copper [S/m]           |

| T <sub>S</sub>    | Switching Period [s]                   |

| t <sub>f</sub>    | Fall Time [s]                          |

| t <sub>r</sub>    | Rise Time [s]                          |

| τ                 | On-Time [s]                            |

| U                 | Coil Wire Bundle Diameter [m]          |

| μ <sub>r</sub>    | Relative Permeability                  |

| $V_0$             | Output Voltage [V]                     |

| V <sub>b</sub>    | Battery Voltage [V]                    |

| V <sub>CM</sub>   | Common Mode Voltage [V]                |

| V <sub>D</sub>   | Diode Switching Voltage [V]              |

|------------------|------------------------------------------|

| V <sub>DM</sub>  | Differential Mode Voltage [V]            |

| V <sub>IN</sub>  | Converter Input Voltage [V]              |

| V <sub>M</sub>   | MOSFET Switching Voltage [V]             |

| V <sub>OUT</sub> | Converter Output Voltage [V]             |

| V <sub>P</sub>   | Peak Voltage [V]                         |

| $V_{PP}$         | Peak-to-Peak Voltage [V]                 |

| Vov              | Zero Line Voltage [V]                    |

| V <sub>X</sub>   | LISN Port 1 Voltage [dBµV]               |

| $V_{Y}$          | LISN Port 2 Voltage [dBµV]               |

| W                | Width [m]                                |

| ω <sub>r</sub>   | Ringing Angular Frequency [rad/s]        |

| $\Delta \omega$  | Delta Angular Frequency [rad/s]          |

| X <sub>C</sub>   | Impedance Real $[\Omega]$                |

| Z <sub>CM</sub>  | Common-Mode Impedance $[\Omega]$         |

| Z <sub>D</sub>   | Diode Impedance $[\Omega]$               |

| Z <sub>DM</sub>  | Differential-Mode Impedance [ $\Omega$ ] |

| Z <sub>C</sub>   | Capacitor Impedance $[\Omega]$           |

| Z <sub>L</sub>   | Inductor Impedance $[\Omega]$            |

| Ζ                | Impedance $[\Omega]$                     |

| Z <sub>0</sub>   | Characteristic Impedance $[\Omega]$      |

| ΔZ               | Delta Impedance [ $\Omega$ ]             |

# **TABLE OF CONTENTS**

| CHAP         | FER 1   INTRODUCTION                     | 1               |

|--------------|------------------------------------------|-----------------|

| 1.1          | PROBLEM STATEMENT                        | 1               |

|              | 1.1.1 Context of the problem             | 1               |

|              | 1.1.2 Research gap                       | 3               |

| 1.2          | RESEARCH OBJECTIVE AND QUESTIONS         | 4               |

| 1.3          | HYPOTHESIS AND APPROACH                  | 5               |

| 1.4          | RESEARCH GOALS                           | 6               |

| 1.5          | RESEARCH CONTRIBUTION                    | 6               |

| 1.6          | OVERVIEW OF STUDY                        | 8               |

| 1.7          | THESIS STRUCTURE                         | 9               |

| CHAP         | FER 2 LITERATURE STUDY                   | 10              |

| 2.1          | BACKGROUND                               | 10              |

|              | 2.1.1 Overview of current literature     | 10              |

|              | 2.1.2 What has been done before          | 13              |

|              | 2.1.3 EMI noise research                 | 14              |

| 2.2          | ELECTROMAGNETIC INTERFERENCE ISSUES      | 16              |

| 23           |                                          |                 |

| 2.3          | COMPONENT PROXIMITY EFFECTS              | 20              |

| CHAP         |                                          |                 |

| 2.0          |                                          | 21              |

| CHAP:<br>3.1 | FER 3       MODELLING – NOISE GENERATION | <b>21</b><br>21 |

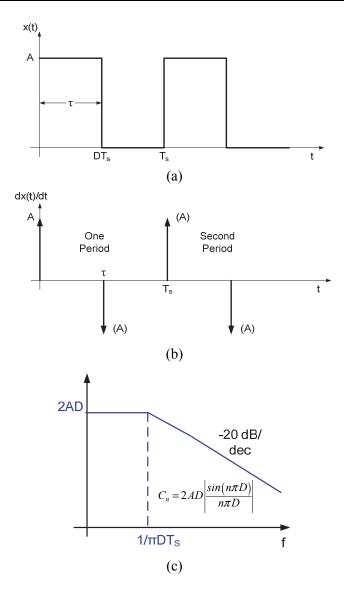

| 3.4  | THE    | EMI NOISE SOURCE                                   | 27 |

|------|--------|----------------------------------------------------|----|

|      | 3.4.1  | Square wave expansion coefficients                 | 27 |

|      | 3.4.2  | Trapezoidal wave expansion coefficients            | 31 |

|      | 3.4.3  | Trapezoidal wave with superimposed ringing         | 35 |

| 3.5  | SUM    | MARY                                               | 37 |

| CHAP | FER 4  | MODELLING – NOISE PROPAGATION                      | 39 |

| 4.1  | INTR   | ODUCTION                                           | 39 |

| 4.2  | NOIS   | E PATH MODELLING                                   | 39 |

|      | 4.2.1  | Practical complex impedance measurement – Method 1 | 40 |

|      | 4.2.2  | The impedance analyser – Method 2                  | 43 |

|      | 4.2.3  | The network analyser – Method 3                    | 44 |

|      | 4.2.4  | Characterising the power circuit noise path        | 46 |

|      | 4.2.5  | Converter capacitor modelling                      | 46 |

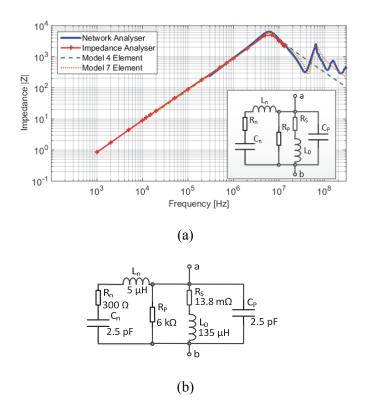

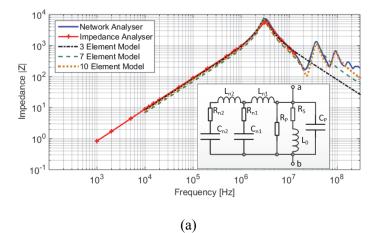

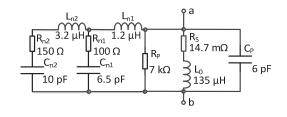

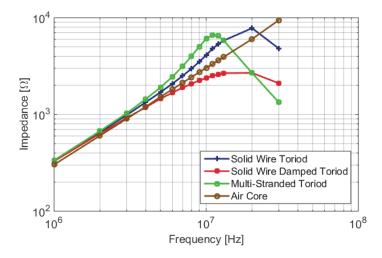

|      | 4.2.6  | Power inductor modelling                           | 51 |

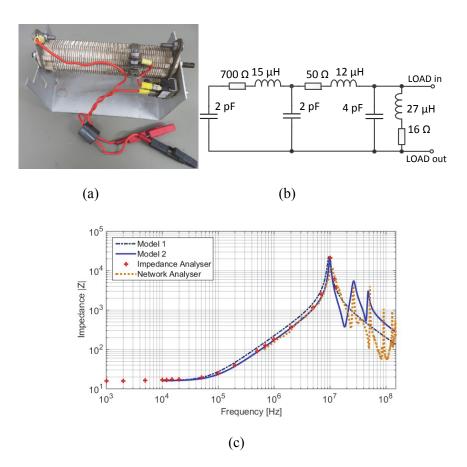

|      | 4.2.7  | Wirewound resistive load                           | 57 |

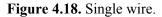

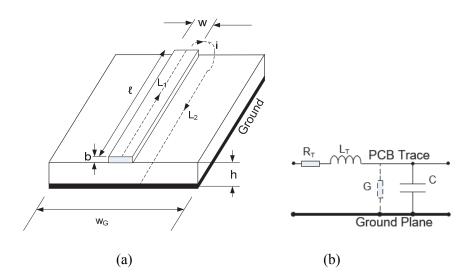

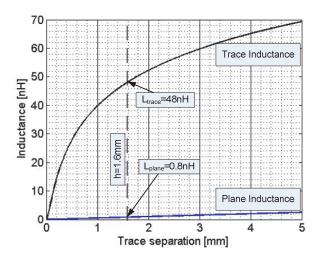

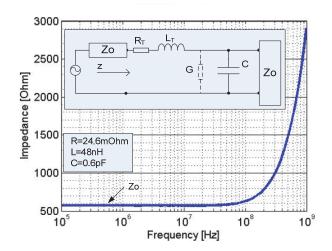

|      | 4.2.8  | PCB traces and wires                               | 57 |

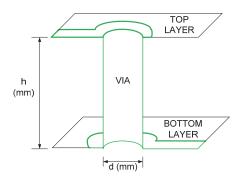

|      | 4.2.9  | PCB via inductance                                 | 65 |

|      | 4.2.10 | ) The skin and proximity effect                    | 66 |

|      | 4.2.11 | Magnetic loops                                     | 69 |

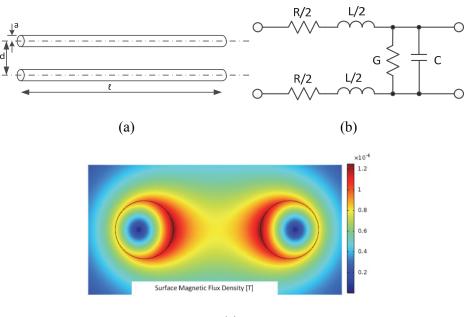

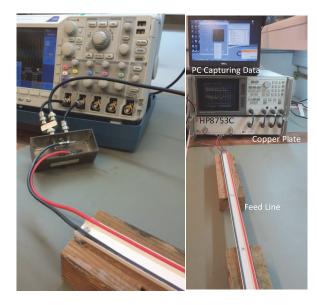

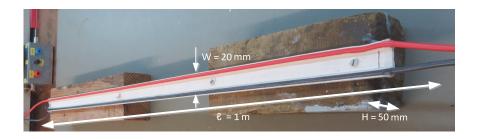

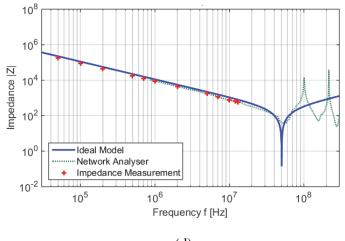

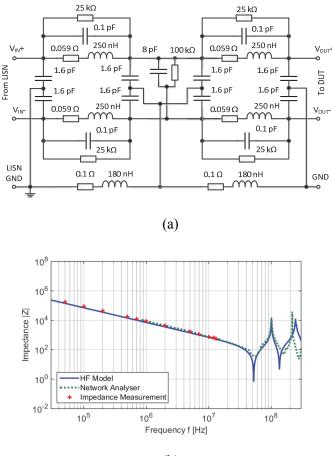

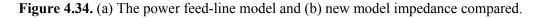

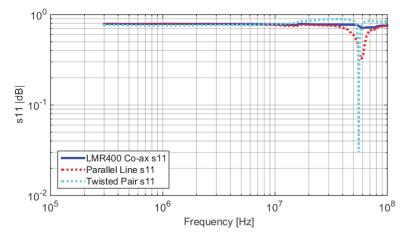

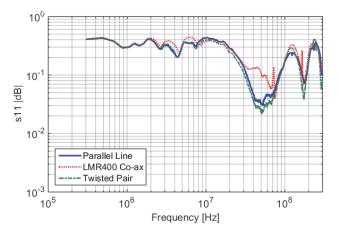

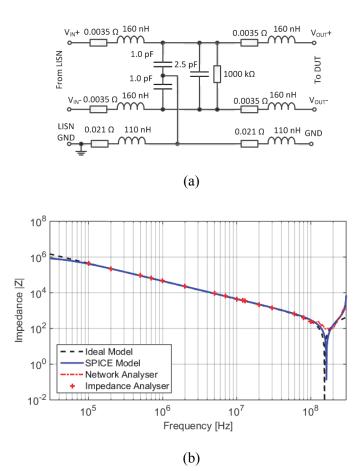

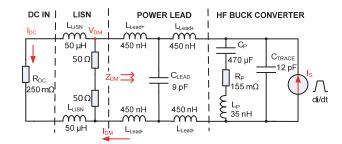

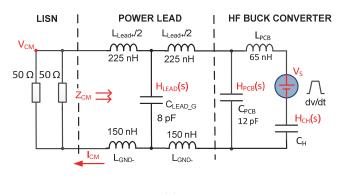

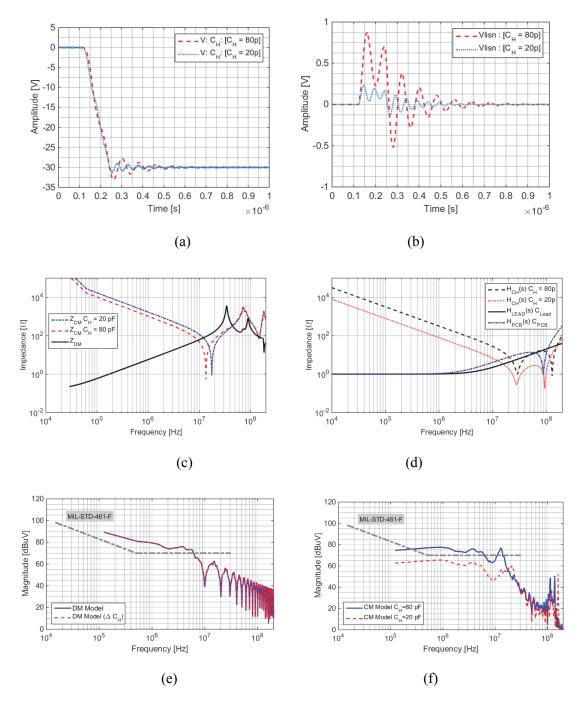

|      | 4.2.12 | 2 Power feed-line model                            | 70 |

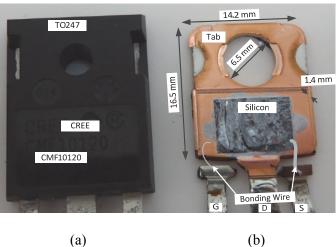

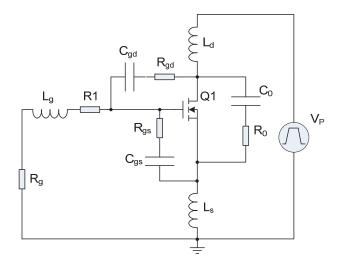

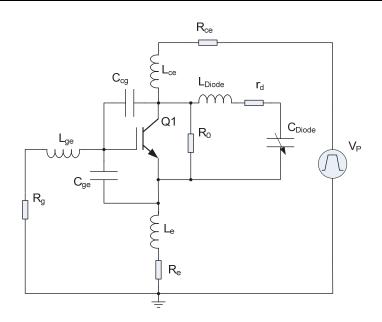

|      | 4.2.13 | 3 Active devices                                   | 78 |

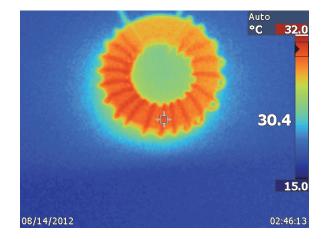

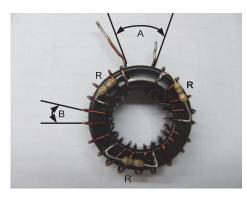

|      | 4.2.14 | 4 Aluminium and polymer heatsink                   | 82 |

| 4.3   | COM   | PONENT PROXIMITY                             | 95  |

|-------|-------|----------------------------------------------|-----|

|       | 4.3.1 | Enclosure effects                            | 96  |

|       | 4.3.2 | Trace coupling                               | 99  |

|       | 4.3.3 | Component coupling – Helmholtz Coil test bed | 101 |

| 4.4   | CHAI  | PTER SUMMARY                                 | 107 |

| СНАРТ | TER 5 | DESIGN AND SIMULATION                        | 108 |

| 5.1   | MEAS  | SUREMENT BENCH DESIGN                        | 108 |

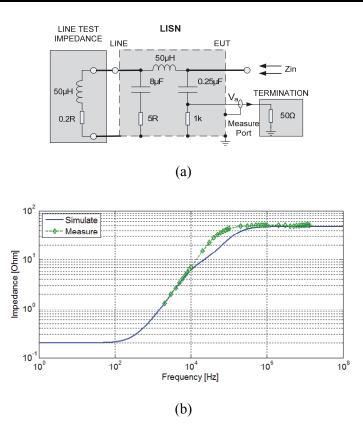

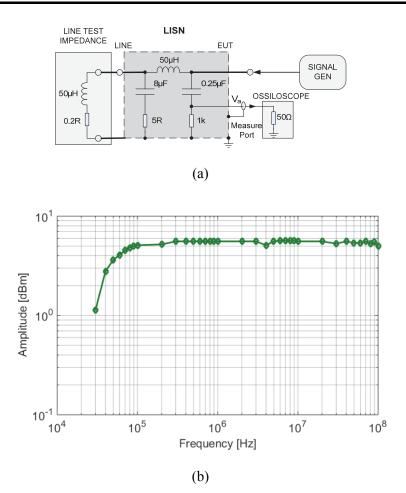

|       | 5.1.1 | LISN design                                  | 109 |

|       | 5.1.2 | LISN manufacturing                           | 111 |

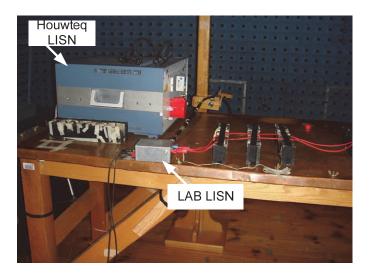

| 5.2   | LISN  | AND MEASUREMENT BENCH VALIDATION             | 120 |

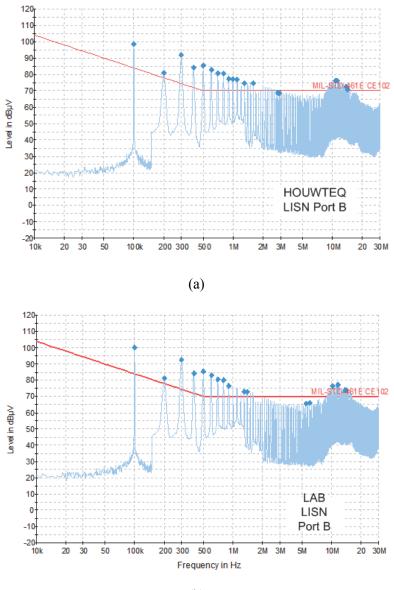

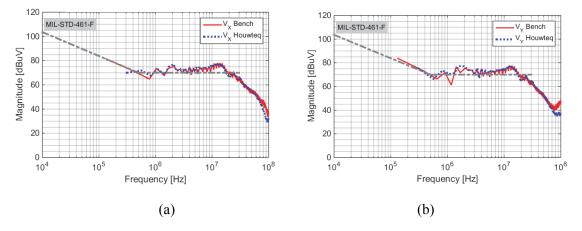

|       | 5.2.1 | Houwteq accredited measurements              | 120 |

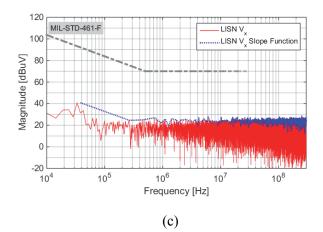

|       | 5.2.2 | LISN Results                                 | 120 |

| 5.3   | LAB   | COMPARISON                                   | 122 |

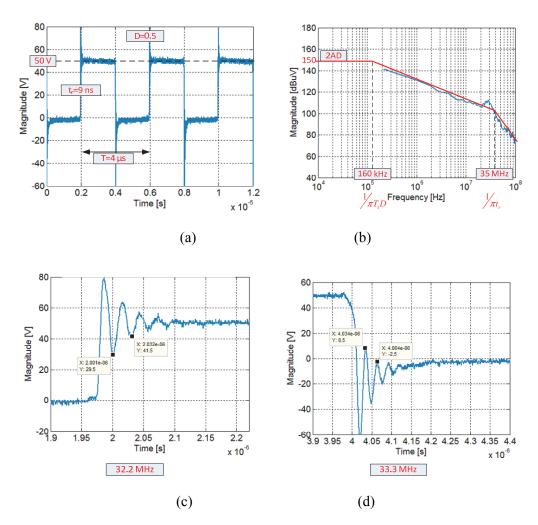

|       | 5.3.1 | EMC measurements in the time-domain          | 122 |

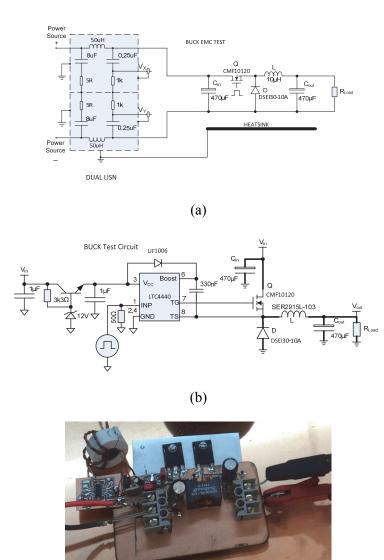

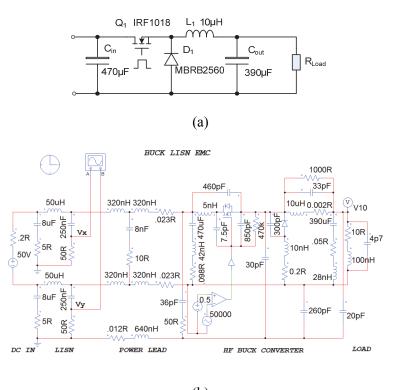

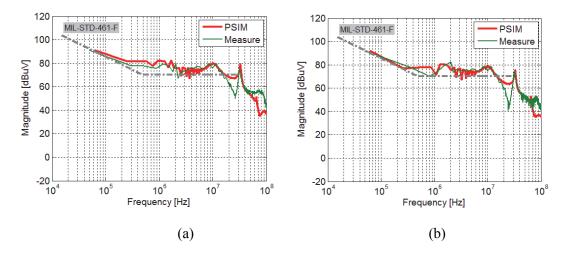

|       | 5.3.2 | Step-Down DC-DC compliance comparison        | 124 |

| 5.4   | COM   | MON-MODE AND DIFFERENTIAL-MODE EXTRACTION    | 127 |

| 5.5   | ACCU  | URATE HIGH FREQUENCY MODELLING               | 128 |

|       | 5.5.1 | Conducted EMC modelling software             | 129 |

|       | 5.5.2 | Modelling process                            | 131 |

| 5.6   | CHAI  | PTER SUMMARY                                 | 137 |

| СНАРТ | TER 6 | SIMULATED AND EXPERIMENTAL WORK              | 139 |

| 6.1   | MEAS  | SUREMENT PLATFORMS                           | 139 |

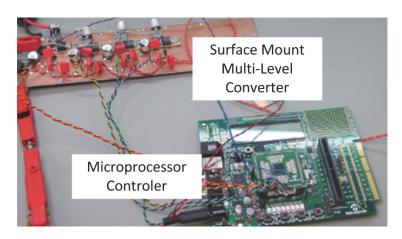

| 6.2   | SURFACE MOUNT TECHNOLOGIES                       | 139 |

|-------|--------------------------------------------------|-----|

| 6.3   | COMPONENT PROXIMITY EFFECT                       | 143 |

| 6.4   | DISCRETE POWER CONVERTER TECHNOLOGY              | 144 |

| 6.5   | REDUCING COMMON-MODE NOISE WITH POLYMER HEATSINK | 149 |

| 6.6   | SHORTER FEED-LINE EFFECT                         | 159 |

| 6.7   | MULTIPHASE ANALYSIS                              | 160 |

| 6.8   | CHAPTER SUMMARY                                  | 163 |

| СНАРТ | TER 7 DISCUSSION AND CONCLUSION                  | 164 |

| СНАРТ | TER 8 SUGGESTION FOR FUTURE WORK                 | 170 |

| APPEN | DIX A EMC REGULATION                             | 184 |

| A.1   | PURPOSE                                          | 184 |

| A.2   | BACKGROUND                                       | 184 |

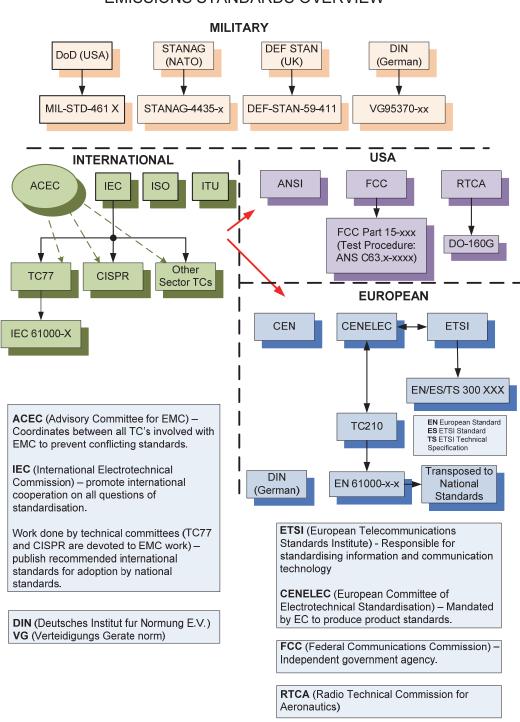

| A.3   | CONDUCTED EMC STANDARDS                          | 185 |

|       | A.3.1 Standards background                       | 185 |

|       | A.3.2 Regulating bodies overview                 | 186 |

|       | A.3.3 Regulating bodies summary                  | 188 |

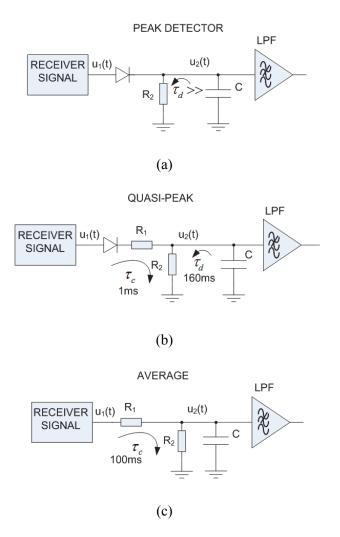

| A.4   | MEASUREMENT DIFFERENCES                          | 191 |

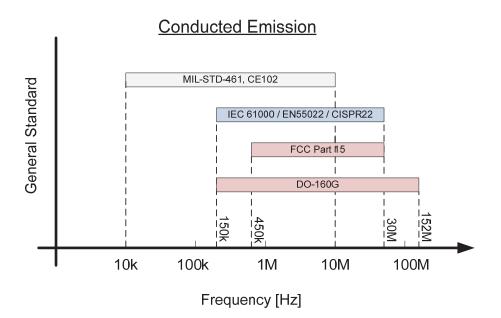

|       | A.4.1 Conducted emission frequency coverage      | 191 |

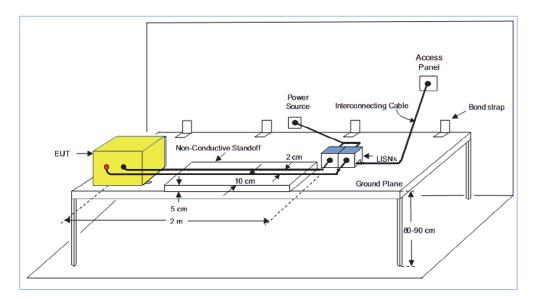

|       | A.4.2 Setup Differences between standards        | 192 |

| A.5   | CONCLUSION                                       | 198 |

| A.6   | REFERENCES                                       | 199 |

# CHAPTER 1 INTRODUCTION

#### **1.1 PROBLEM STATEMENT**

#### **1.1.1** Context of the problem

Electromagnetic interference (EMI) can be described as any unwanted electromagnetic energy that interferes with the operation of a device either generated by the device itself or received by other devices nearby. The electrical or electronic device or system needs to be able to operate without interfering with other systems, and must have the ability to operate as intended within a specific electromagnetic environment. We can quantify the electromagnetic noise of a device as conducted and radiated emissions from the device as well as conducted and radiated susceptibility to the device. International standards and regulations govern these levels to be within certain limits, and is a requirement to conform to in the open marketplace.

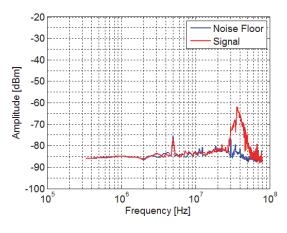

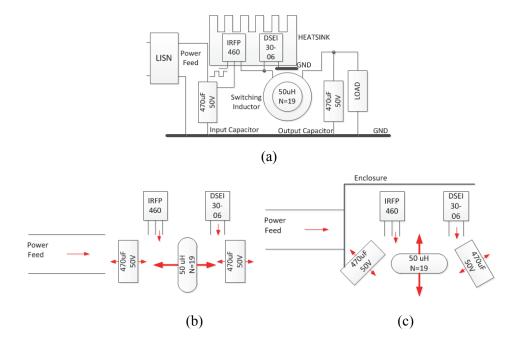

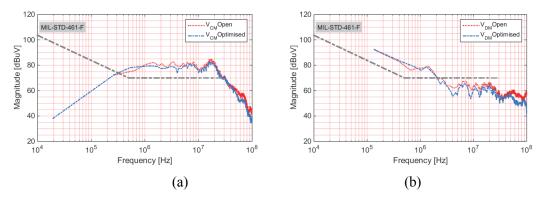

The current publications on conducted Electromagnetic compatibility (EMC) analysis mostly simplifies converter circuits and thus can achieve only accurate results below about 1 MHz, as typically seen in [1]. Better accuracies are seen with simplified noise path circuit models considering switching transient modelling [2], but accurate switching waveforms are only available when measured on the end-product. Some references use a trapezoidal waveform with simplified noise path models, but high frequency accuracy is then compromised. It will be desirable to perform conducted emission modelling and measurement up to 100 MHz. This can easily be achieved by careful design of parasitic circuit models and by the measuring equipment normally found in a power electronics laboratory, to analyse conducted EMC with lumped element SPICE circuit analysis, spectral results are usually not presented over the entire conducted band due to inaccuracies and the difficulty to obtain. Results of only a small portion of the band are presented in [3]. In [4] a common-mode model is offered as well as high frequency impedance measurements up to 100 MHz, whereas the actual model results are fairly

accurate compared to the measurements up to 1 MHz, thereafter large discrepancies appear of more than 20- 30 dBµV. Furthermore, the predicted common-mode follows the measurement values only up to 300 kHz, thereafter fails to follow any measured result. Accurate high frequency models, up to 100 MHz are not available. The decomposition into the common- and differential-mode currents, necessary for optimal filter design, is normally done by complex analog radio frequency (RF) circuitry splitting and combining techniques, providing inaccurate results due to the handling of sensitive high frequency signals as well as impedance issues [5]. Setting up high frequency EMI current coils provides very good results, as in [6], but these instruments are not always readily available in the laboratory. Digital splitting by signal processing should be possible when simultaneous digital recordings of the LISN noise currents are made. Some equations found in literature for the decomposition in common-mode and differential-mode noise, mostly sited from an early publication in [7], provide inaccurate results. Performing accurate measurements, supplemented with first principle equation extraction, a 6 dB discrepancy was found, that highlights the need to clarify these equations. Although in [8], a current probe was used enabling the correct splitting of common- and differential-mode noise, but no comparative simulation results were presented. Furthermore, splitting the common- and differential-mode noise digitally by using the LISN, verifying the equations thereof, is not seen in literature. The measurement of conducted EMI noise with a wideband digital acquisition technique, (e.g. GHz digital Oscilloscope) and consequent signal processing as described in [9] is rarely seen. In most measurements, EMI receivers are used, and due to the dwell-time and frequency binning principle, is a very timeconsuming exercise. The conducted EMC environment is in urgent need to clarify the modelling environment and provide an instinctive modelling mechanism to design for EMC, and rid itself from the 'black art' principle as well as trial-and-error [4] filter design.

The EMI management of a power converter should be an integral part of the converter design process. As the EMI verification is normally done when the product is at its final stage and qualification tests are underway, redesign at this stage can extend the crucial time-to-market date. For this reason proper modelling, of both EMI noise generation and propagation in power converters is of absolute importance right from the start of the design

#### CHAPTER 1

phase. Numerical predictions of the electromagnetic behaviour prior to prototyping help reduce post prototyping electromagnetic compliance risk, costly redesigns and subsequent modifications [10]. It is thus of utmost importance to try and model the electromagnetic compatibility concurrently with the power processor design stage.

Power electronic designers are in need of an accurate and practical EMI modelling and prediction method suitable for use as a design tool [11]. The complexities of electromagnetic noise generation and propagation mechanisms make modelling prediction difficult. It depends on many variables, for example, component density, placement position, lead length, track layout, and the subsequent interaction with the environment under which the converter is to operate. An understanding of the converter behavior can assist in eliminating the EMI problems at the design stage rather than by excessive filtering. Understanding conducted EMI behavior will also substantially influence packaging density and cost as low frequency conducted noise requires large filter components. These large filter components are not only physically large but have enormous parasitics and consequently poor high frequency performance [12].

The project proposed here is to analyse and model the mechanisms of conducted electromagnetic noise originating from densely packaged components in DC-DC converters. The proposal also includes the identification of typical EMI sources, and a study of their coupling mechanisms. A case study of a selected power converter will illustrate the typical techniques for dealing with conducted noise. The study will further show how an iterative process between the theoretical and practical results will improve the accuracy and understanding of the conducted EM noise mechanisms, and in this way manage, as well as suppress EMI noise in a systematic way.

#### 1.1.2 Research gap

The approach to conducted EMC modelling is usually to simplify the circuit so as to provide for an easier analysis method. These simplifications make it difficult to predict high frequency effects. When SPICE circuit modelling is used, the extraction of the parasitic elements does not receive the proper attention, as the switching elements do play a large role in the conducted EMC levels [13]. Recently, in [14], equivalent parasitic model extraction by vector fitting is taken to the extreme, creating complex equivalent noise circuit models from the end-product, accurately modelled to 10 MHz. These complex equivalent circuit models seem not to relate to the functionality of the power circuit, or to the switching waveform slope information and high frequency effects that is crucial in high frequency modelling.

Power converter designers are in need of an EMC modelling and design methodology at reasonable cost. So often, power converters are designed without proper attention being given to EMC related issues. Standard recipes are normally followed during the design process, and the EMC tests are only done when the design is complete. Failing this test, modifications need to be performed and in a worst case, redesign. In a market where time and cost is of utmost importance, this is seen as a high risk. By designing for EMC at the initial design stages, optimal components can be selected, layout can be optimised and by accurate modelling and design, the accredited EMC tests can be executed with confidence

#### **1.2 RESEARCH OBJECTIVE AND QUESTIONS**

It would be useful to develop an EMC design methodology suited for the power electronics designer, knowing that through design, the applicable conducted EMC levels can be achieved. A conducted emission test bench will be designed, tested and calibrated up to at least 100 MHz, so as to see if radiated emissions start to emerge. The conducted test is a much easier test to perform in a laboratory.

Power converter designers very often see EMC design as a burden, as it can in some cases be very difficult and frustrating. Currently, the EMC modelling should form part of the converter design, so the method should be intuitive, easy to perform and provide accurate results. Questions that need to be answered are:

• Is it possible to accurately model conducted EMC without using expensive and complex EMC modelling packages?

- Is it possible to construct a LISN and consequently a test bed to be able to accurately measure conducted emissions up to 100 MHz?

- Is it possible to accurately measure conducted EMC in a development laboratory with commonly available instruments, such as a digital oscilloscope and signal generator?

- What is the accuracy in digital recording of the noise levels compared to measurement by a traditional EMC spectrum analyser?

- Can conducted emissions be split digitally by recording data from the LISN ports, into common-mode and differential-mode noise signals so as to provide inputs for optimal filter design?

- What are the effects of the required EMC measurement setup prescribed by the accreditation organisations on conducted emission; for example the power feed-line from the LISN to the power converter under test?

- What is the effect of the physical structures such as the heatsink, the enclosure, component and PCB fasteners on common-mode emissions?

- How do power components in close proximity influence conducted emissions?

- Closing the complete modelling and measurement cycle is needed. The modelling

as well as measurement results in the power electronics laboratory is to be

compared to accredited noise measurements. This provides confidence that the

modelling as well as measurement techniques can be used in a pre-compliance test.

This improves the assurance that the power unit under test will pass the accredited

conducted EMC measurement qualification test performed at the final design stage

before the unit can be released into the marketplace.

#### **1.3 HYPOTHESIS AND APPROACH**

A conducted EMC design philosophy will be developed and tested. The test and implementation environment will be the general power converter lab. Modelling, test and measurement techniques will be developed, up to a frequency of at least 100 MHz to be able to show radiating effects starting to emerge. The end result of this design methodology will be that if the converter design is completed, the designer will have the

confidence that the converter will adhere to the applicable EMC standard imposed on the converter.

The EMI noise source analysis will firstly consider the idealised square wave switching signal. The noise path consists of components, traces and structures. The high frequency models of these devices and structures are part of the noise path. High frequency circuit models of the passive components and circuit traces are generated and where applicable, verified with an impedance analyser or network analyser. As these expensive instruments are not readily available in a power development laboratory, a practical scheme is presented to accurately determine the high frequency impedance of components. The measurements will be verified with an impedance analyser (lower frequency) as well as a network analyser (higher frequency).

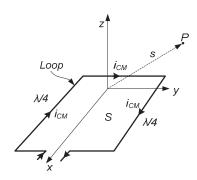

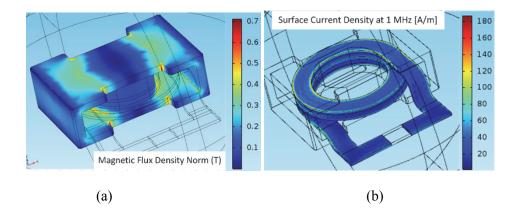

Where applicable, component and environment modelling is supplemented with finite element electromagnetic analysis. Mostly COMSOL Multiphysics will be used, but for larger structures, such as enclosure modelling, the electromagnetic analysis package FEKO will be used. This analyses the broader effects of parasitic inductance and capacitance as well as the component effects on the circuit board and the environment.

#### 1.4 RESEARCH GOALS

Modelling and design for high frequency conducted EMC and all the aspects around it such as the noise source, the noise path and component interactions are the primary design goal. Accurate test, verification and validation should be performed. Pushing the limit of conducted EMC measurement frequencies beyond the required frequency limit so as to investigate radiated phenomena in an easier conducted EMC measurement setup.

#### **1.5 RESEARCH CONTRIBUTION**

The research goals were met. The main contributions were the accurate intuitive modelling of conducted EMC up to 100 MHz, accurate bench design and measurements, the accurate digital splitting of common-mode and differential-mode signals by means of the LISN voltages. Additional contributions included identifying a practical way of determining the

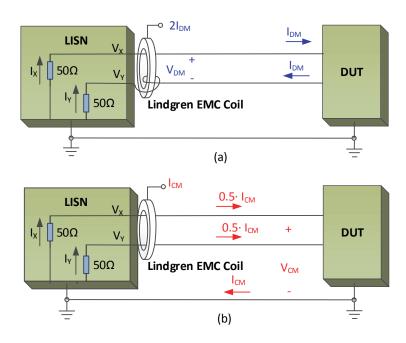

most and least susceptible side of the component as design input to a printed circuit board component placement and optimal orientation. Spinoffs achieved were a calibrated measurement technique that can be used in a development laboratory environment. Due to the noise mechanism an in-depth analysis was performed on the heatsink contributing towards common-mode noise, lowering common mode noise by using a polymer composite heatsink and the further advantages thereof, creating accurate EMC SPICE models as well as structural COMSOL FEA models applicable for a wide range of converter types. Various conducted EMC lowering techniques were tested, for example PWM jittering and slope compensation. The equations for deriving common-mode and differential-mode signals from the LISN voltage ports found in literature were not always correct. Although a simple derivation, most references to the differential-mode equation and to a lesser extent, the common-mode equation, were found not to be valid.

During the course of the EMC studies, seven conference papers were delivered and also published in conference proceedings. Three journal articles were submitted of which one has been provisionally accepted and two are undergoing revisions. These publications do provide practical solutions to the power converter designer in looking for solutions to EMC problems in converters:

- I. I. Grobler and M. N. Gitau, "Common-mode noise in three-level DC-DC converters," in *Proc. IEEE AFRICON*, Nairobi, Sept. 23-25, 2009, pp. 1-6.

- II. I. Grobler and M. N. Gitau, "Low cost power lead extended pre-compliance conducted EMI measurement setup and diagnostics with compact LISN," in *Proc. IEEE ECCE*, Melbourne, June 3-6, 2013, pp. 1144-1149.

- III. I. Grobler and M. N. Gitau, "Characterising and modelling extended conducted electromagnetic emission," in *Proc. IEEE ECCE*, Melbourne, June 3-6, 2013, pp. 1131-1136.

- IV. I. Grobler and M. N. Gitau, "Characterising and modelling extended conducted electromagnetic interference in densely packed DC-DC converter," *in Proc. IEEE ECCE*, Denver, Sept. 15-19, 2013, pp. 1676-1681.

- V. I. Grobler and M. N. Gitau, "Component proximity effects in high density and high switching speed power converters," in *Proc. Energy Conversion Congress* and Exposition (ECCE), Denver, Sept. 15-19, 2013, pp. 1251-1258.

- VI. I. Grobler and M. N. Gitau, "Modelling and Measurement of High Switching Frequency Conducted EMI," in *Proc. IEEE IECON2013*, Vienna, Nov. 10-13, 2013, pp. 1029-1034.

- VII. I. Grobler and M. N. Gitau, "Conducted EMC modelling for accreditation in DC-DC converters," in *Proc. IEEE IECON 2015*, Yokohama, Japan, Nov. 9-12, 2015, pp. 2329-2335.

Three journal papers have been prepared and are in review process /accepted in IET Journal of Science, Measurement & Technology:

- SMT-2016-0188: "Modelling and Measurement of High-Frequency Conducted EMI in DC-DC Converters," reviewers comments have been incorporated and final submission was on 3 February 2017.

- I. Grobler and M. N. Gitau, "Analysis, Modelling and Measurement of the Effects of Aluminium and Polymer Heatsinks on Conducted EMC in DC-DC Converters," *IET Science and Measurement Technology*, Online ISSN 1751-8830, Available online: 20 January 2017.

- In preparation for re-submission: "Component Placement Effects in High Density and High Switching Speed Power Converters", that will incorporate up to 300 MHz conducted emission model and measurements with a CISPR 15 CDN.

#### **1.6 OVERVIEW OF STUDY**

The noise source and the noise path has been analysed in detail. The noise mode equations were derived and tested. A conducted EMC design method has been implemented and component as well as enclosure interaction scrutinised. The heatsink capacitances were

modelled in detail, as this is a prominent common-mode conduction path. The test bench has been designed and consistent and accurate calibrated measurements could be performed on the test devices. EMC design solutions were presented.

### **1.7 THESIS STRUCTURE**

Chapter 2 starts off with a background and literature study on EMI noise research. Chapter 3 gives a theoretical noise generation concept. Chapter 4 deals with the noise propagation concept, component proximity effects and coupling mechanisms. Chapter 5 presents the design and simulation method for conducted EMC. Chapter 6 provides results from experimental work and Chapter 7 presents the discussion and conclusion. Chapter 8 closes down indicating suggestions for future work. Appendix A gives an EMC regulative summary, the different regulatory bodies and applicable standards.

# CHAPTER 2 LITERATURE STUDY

# 2.1 BACKGROUND

A detailed literature review will be carried out in this chapter to establish the current status in EMI modelling. Research gaps will be identified and based on these, research goals will be determined.

# 2.1.1 Overview of current literature

# 2.1.1.1 High density packaging

The first generation converters were implemented using only discrete components [15] populated with a low component packaging density. The main switching devices and diodes were typically mounted directly onto a heatsink. The power devices were connected to one or more printed circuit boards that housed the gate drive circuitry, as well as all the protection and control circuitry. Depending on the power rating, magnetic components could also be mounted on the PCB. Larger components for higher power ratings were mounted on a separate bracket or even directly onto the heatsink.

The next power packaging technologies on the market called brick and half brick hybrids are still very popular and provide fair packaging densities at affordable costs. These are complete packaged converter structures built with discrete components that have been packed into smaller volumes than the equivalent first generation converters. This was possible due to higher switching frequencies and improved thermal management that allowed more energy to be processed with smaller components. The components are then partially or fully encapsulated into a brick-like structure. The power substrates take up the most of the volume, about 12.5%, followed by the magnetic components with about 11 %. Next the capacitors and control components with each about 3% of the total volume. It further shows that between 30% to 50% of the total volume is still not used by components in this technology [15].

To further improve packaging, power modules called Direct Copper Bonded (DCB) substrate are used to pack multiple semi-conductor power devices on a single substrate and therefore replace the old discrete power devices. It is then possible to implement the converter switching functions with a single power module with increased thermal performance. Fewer external interconnections are required due to the already made internal connections. Depending on the power rating, the magnetic components, driver, and control circuitry are normally mounted on a PCB.

# 2.1.1.2 Integrated electromagnetics

The new generation power converters, known as power processors, contain distributed structures or integrated Electromagnetics [12], [15]. Integrated Electromagnetics is the three dimensional integration of the functions of conduction, inductance, resistance, and capacitance in one component, namely the integrated power module. This is the electromagnetic integration of multiple passive components into a single integrated structure, also called a planar power passive module. The structure normally consists of the combination of alternative layers of conductors, dielectrics, and magnetic materials. These alternative layers realise components such as inductors, capacitors, and transformers in a series and/or parallel configuration, normally configured for a specific converter topology.

# 2.1.1.3 Electromagnetic environment

From the foregoing paragraphs one can conclude that in the new generation power converters, passive as well as active devices, are in closer proximity to each other now more so than ever before. This close proximity enhances parasitic capacitance and inductive coupling, creating a complex electromagnetic environment. Furthermore, switching frequencies have been dramatically increased leading to reduced passive component sizes, but also generating greater EMI levels at higher frequencies, resulting in high conducted common-mode disturbance [10]. Component parasitics, magnetic or electrostatic coupling effects can therefore not be neglected.

Currently, external to most power converters, is a modern environment consisting of sensitive electronic devices, such as communications and Information Technology. These

IT equipment are usually sensitive to electromagnetic interference levels. It is thus very important that power processors comply with the electromagnetic limits and even in some cases, that they generate less noise than proposed by the compliance authorities.

Typical power processors may have multiple converters, and although they might be synchronised, they still produce an array of broad-band EMI emissions of up to several hundred mega Hertz. The low frequency range can extend down to several Hertz and conventional methods such as shielding and typical filtering techniques do not adequately contain this noise. The space and boundary conditions necessary for the EMC design are also very complex.

The belief is that if conducted EMI can be contained by firstly, understanding the mechanism thereof, and secondly, by designing for minimum conducted emissions with this knowledge, the radiated emissions that are more difficult to analyse, could also be effectively lowered in the process [16]. The conducted EMI is considered as the source of the radiated EMI.

# 2.1.1.4 Modelling criteria

Due to the switching operation of power converters, enabling reduced size and weight and increased efficiency, large dv/dt and di/dt currents exist, generating unwanted noise. Placing any power product into the marketplace, it needs to adhere to stringent international EMI requirements. If a power converter does not pass the EMI qualification test, its use become limited and will be unable to enter the marketplace. Traditionally, EMI is known to many power electronics designers as a 'black art', implementing recipes and hope the power product will eventually pass its EMI qualification test. If not, expensive rework is performed; adding more filtering etc. and this process can be disastrous, missing deadlines and at worst, enter a re-design phase. This is why most power engineers will overdesign filters and add extra measures that might not be necessary. Designing for EMI is becoming extremely important, especially in lieu of factors even more detrimental to EMI noise, such as converters constantly evolving into better efficiencies, moving to higher frequencies and smaller packaging.

In many situations, EMI modelling is not being performed with all the required starting data. EMI models are often based on estimates and on cases where component tolerances and environment variations can be extensive. EMI modelling should be approached with the idea of bounding the problem region to reduce the uncertainty to a minimum [17].

The three basic criteria for comparing different EMI modelling methodologies can include accuracy, feasibility, and generalization [11], [18].

Both frequency and magnitude levels of the predicted EMI need to be accurate as to address the different aspects of EMI mechanisms. Most models are only accurate in the lower frequency region (below 5 MHz [11] or below 8 MHz [10]. The modern high density packaging of components introduces an increase in parasitics and creates an easier conduction path for the unwanted high frequency electromagnetic noise. It is thus very important to model these higher frequencies more accurately.

Feasibility is important as some EMI models are complicated to use, while others sacrifice accuracy to achieve simplicity. The need for less complex and practical models accessible to the power designer is becoming a valuable necessity. Generalisation is important as some models are only valid for specific applications and topologies. Even in larger converter systems or power processors, as well as in the design of different converters, a generic modelling methodology is indispensable.

# 2.1.2 What has been done before

From the results of reviewing the existing literature, it is obvious that conducted EMI modelling research is still not adequate and in most cases, addressing only specific topologies. Due to simplification and as a result of the techniques used, most EMI models deal only with the lower 15% of the frequency range. To incorporate the high frequency part of the conducted EMI noise, a more accurate modelling methodology is required.

In the converter design process, the EMI management tends to be included in the last step, leading to expensive rework if the EMI levels fail compliance testing. Failure of EMI management in the early design process is mostly because of lack of EMI noise source models.

The present EMI modelling research is still at the converter level. Specific topologies have specific EMI models, but in a power processor system where multiple converters are in close proximity, system level EMI is often inefficient and ineffective. This inefficiency is due to a lack of proper consideration of the appropriate interactions and inter-modulation phenomena induced by the system. This is due to the fact that a general modelling approach for the power processor system is not available and thus not implemented in the early stages of the design.

Some important EMI phenomena, such as common-mode and differential-mode noise interaction are not fully explored [12]. This type of noise interaction is not easily controlled and subsequently not suppressed by traditional EMI management. It is thus important to develop modelling technologies that take them into account.

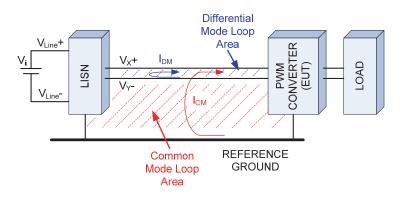

# 2.1.3 EMI noise research

The objective of the conducted EMI research proposal is to understand the primary causes of EMI and how to manage and suppress EMI in a systematic, methodical yet practical manner. The basic conducted EMI modelling process includes 2 steps, namely: the EMI noise source [16] and the EMI noise propagation [10], [11]. The purpose of modelling the propagation path and noise source separately is to try to understand the EMI noise methodology. All links between the noise source and noise coupling effects are considered possible noise propagation paths. The noise paths consist of cables, wires, PCB traces, magnetic components, capacitors and their parasitics. The noise source and noise path need to be addressed simultaneously.

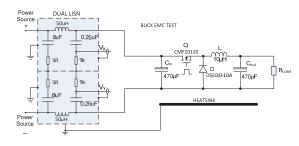

An important aspect of conducted EMI noise research is the verification of the simulated models. Verifying the models for accuracy needs a well-designed EMI bench to be able to take measurements of the intended noise. Unwanted noise paths, for example the DUT auxiliary power or the load interface to the test bench, has to be screened if not part of the model. Similarly for the measurement cables, it needs to terminate into 50  $\Omega$  because the LISN is a 50  $\Omega$  measurement device. The test bench needs a proper ground and care must also be taken with regards to external noise interference

Regardless of which simulation approach is taken, the key to successful EMI performance prediction is accurate noise source and path information [16], [19]. This information could also reveal the significant roles of parasitic elements combined with device switching processes in EMI.

Many EM noise simulators have not considered skin and proximity effect, non-linear characteristics, intermodulation and hysteresis. The influence of enclosures, bulky structures such as heatsinks and the effects that nuts, bolts and washers have on EMI are not considered in the present literature. Furthermore, EMC modelling on high-density packaging and power passive structures is not well researched. The PWM effects on EMI performance are also not well documented. In conclusion it seems that the requirement for further research in the above mentioned field would be of great value to the affiliated industries.

# 2.1.3.1 Problem and objectives

As is the case with any power converter, where current changes rapidly i.e. large di/dt and dv/dt, EM radiation will take place. This radiation needs to be limited or contained so as not to interfere with other nearby sensitive electronic equipment, by meeting internationally accepted test standards.

Most designers use the basic EMC recipes and make use of good EMC design practices when designing power processors. This design process may contain the EMI sufficiently in most cases, but poses a huge financial risk when the initial EMC qualification tests are performed for the first time on the prototyped unit. If this unit fails the initial qualification test as often happens, minor changes to the design might not solve the problem completely. This can lead to very expensive modifications, adding bulky filters or may even lead to the redesigning of a part of the converter, and extending the critical time to market deadline in a competitive marketplace.

The design goal is to develop a practical model for accurate broadband conducted EMC analysis for high density power processor packaging that could well be expanded to different structures and components. This will enable the designer to accurately predict the

EMC parameters in the early design stage and thus through the model understand the mechanisms that create EMI and solve the EMC aspects early in the design stage. The ultimate goal would be a modeling technique that would guarantee test compliance by yielding noise characteristics that are as accurate as those from an accredited test facility.

# 2.1.3.2 Design methodology

At this point, the proposal presents a broad research methodology. Firstly, a comprehensive literature study will be performed on the subject of conducted EMI, mathematically assessing how it relates to high density power processors and integrated power passive components. The outflow will be a model or models to do a prediction on simple packaging, verifying the accuracy of these models against practical measurements. This process will also enable a wider understanding of the mechanisms involved in EMC with regard to the close proximity of components and should lead to a substantial contribution towards more effective techniques and ideas with regards to the design of high density packaging and ultimately better EMC compliance.

# 2.2 ELECTROMAGNETIC INTERFERENCE ISSUES

The physical sizes of the passive energy storage elements such as transformers, inductors and capacitors in power converters decrease in size as well as in component values with an increase of the switching frequency [20]. Therefore, high-density power supplies generally demand high switching frequency and fast semiconductor devices. However, the increased switching frequency, together with the increased current and voltage slew rates, dv/dt and di/dt, has negative effects on the electromagnetic compatibility (EMC) performance of the power converter.

Decreasing the EMI to acceptable levels as dictated by the applicable EMI regulatory body for the application is of utmost importance. Switch-mode power supplies were known in the past for their overwhelming electromagnetic noise interference, causing disruption to especially communication equipment such as AM/FM receivers and microprocessors. Recently, care needs to be taken to comply with the applicable regulation as power converters are more and more utilized near sensitive radio frequency circuitry and microprocessors.

Different countries call for different EMI standards, depending on their internal regulatory bodies. The major standards are normally slightly adjusted or in some cases such as in South Africa, adopted a given standard as is. The four major bodies implementing standards are the International Electrotechnical Commission (IEC), the Federal Communications Commission (FCC) in the United States, the European Committee for Electrotechnical Standardization (CENELEC) and the European Telecommunications Standards Institute (ETSI) in European countries. Two IEC technical committees are devoted full time to EMC work, namely the TC77, who study electromagnetic compatibility between equipment, including networks, and the International Special Committee on Radio Interference (CISPR). The major output of TC77 is printed in various parts of IEC Publication 61000. CISPR publications deal with the limits and measurement of radio interference characteristics or potentially disturbing sources. CISPR publications co-exist with IEC 61000.

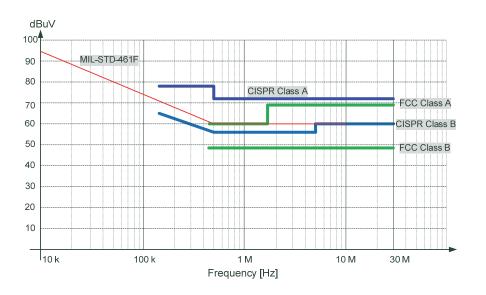

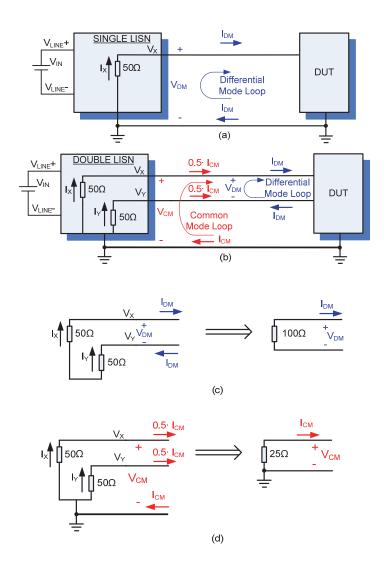

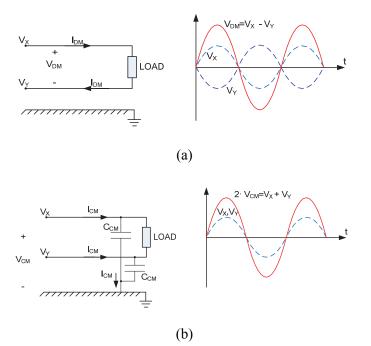

For military applications, a different requirement exists, explained in the DOD document MIL-STD-461F [21]. Conducted emissions are applicable down to 30 Hz for submarine applications and regulated up to 10 MHz for all equipment. Table 2.1 provides more detail pertaining the popular limits. Figure 2.1 shows a graphical representation. The MIL-STD-461F limits are standard values and guidance for relaxation of these limits is given. The basic limits are for system source voltage of lower than 28 V. Up to 115 V, a 6 dB relaxation is applicable, and for 220 V systems, 9 dB is given. Furthermore, if equipment is housed in less sensitive areas, relaxation can be negotiated.

| CLASS A              |                       |           |           |                 |             |         |              |           |  |

|----------------------|-----------------------|-----------|-----------|-----------------|-------------|---------|--------------|-----------|--|

| FCC Part 15 CISPR 22 |                       |           |           |                 |             |         |              |           |  |

| Frequency            | Quasi Peak            |           |           | Quasi Peak      |             |         | Average      |           |  |

| [MHz]                | [dBµV]                | [mV]      | [dBµV]    |                 | μV] [mV     |         | [dBµV]       | [mV]      |  |

| 0.15 - 0.45          | _                     | _         | 7         | 79              | 9           |         | 66           | 2         |  |

| 0.45 - 0.5           | 60                    | 1         | 7         | 79              | 9           |         | 66           | 2         |  |

| 0.5 - 1.705          | 60                    | 1         | 7         | 73              | 4.5         |         | 60           | 1         |  |

| 1.705 - 30           | 69.5                  | 3         | 7         | 73              | 4.5         |         | 60           | 1         |  |

|                      |                       |           | CLAS      | SS B            |             |         |              |           |  |

|                      | FCC Part 15 CISPR 22  |           |           |                 |             |         |              |           |  |

| Frequency            | Quasi Peak            |           |           | Quasi Peak      |             | Average |              |           |  |

| [MHz]                | [dBµV]                | [mV]      | [dB       | βμV] [mV]       |             | 7]      | [dBµV]       | [mV]      |  |

| 0.15 - 0.45          | _                     | _         | 66-       | -56.9 2.0-0     |             | ).7     | 56-46.9      | 0.63-0.22 |  |

| 0.45 - 0.5           | 48                    | 0.25      | 56.       | 9-56 0.7-0      |             | .63     | 46.9-46      | 0.22-0.2  |  |

| 0.5 - 1.705          | 48                    | 0.25      | 4         | 56              | 0.6         | 3       | 46           | 0.2       |  |

| 1.705 - 30           | 48                    | 0.25      | 6         | 60 1.0          |             | )       | 50           | 0.32      |  |

|                      | MIL-STD-461F          |           |           |                 |             |         |              |           |  |

| Subma                | Submarine Application |           |           | Other Platforms |             |         |              |           |  |

| Frequency            | Quasi Peak            |           | Frequency |                 | Quasi Peak  |         |              |           |  |

| [Hz]                 | [                     | dBµA]     |           |                 | [Hz]        |         | [dBµV]       |           |  |

| 30 - 2.6 k           | 95                    | 5 (<3 A)  | 10        |                 | 10k – 500 k |         | 94–60 (28 V) |           |  |

| 2.6 k to 10 k        | 95 -                  | 76 (< 3A) | .) 50     |                 | с – 10 М    |         | 60 (28       | V)        |  |

| Table 2.1 | Popular | conducted | emission l | limits. |

|-----------|---------|-----------|------------|---------|

|-----------|---------|-----------|------------|---------|

Figure 2.1. Applicable limits for conducted emissions.

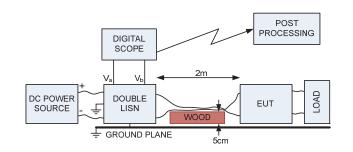

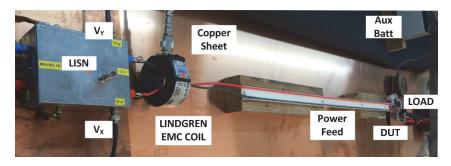

The EMC bench setup as explained in MIL-STD-461E is shown in Appendix A, Figure A.3. The bench consists of a double LISN, a 2 m power feed-line suspended 50 mm above the conducting surface with wooden blocks, as well as the test equipment.

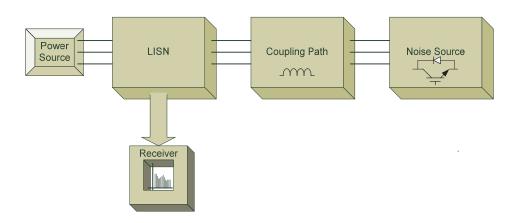

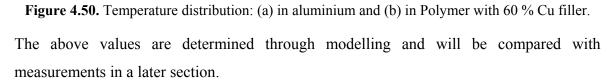

Figure 2.2 shows the conducted EMI emission path as from the noise source, a coupling path to the power source matched with a Line Impedance Stabilising Circuit (LISN). The noise source generates the EMI noise, a coupling path transfers the noise to the LISN through cables or wires. The LISN creates a standardized means to measure the EMI noise into a 50  $\Omega$  impedance and to isolate the power source noise from the converter noise.

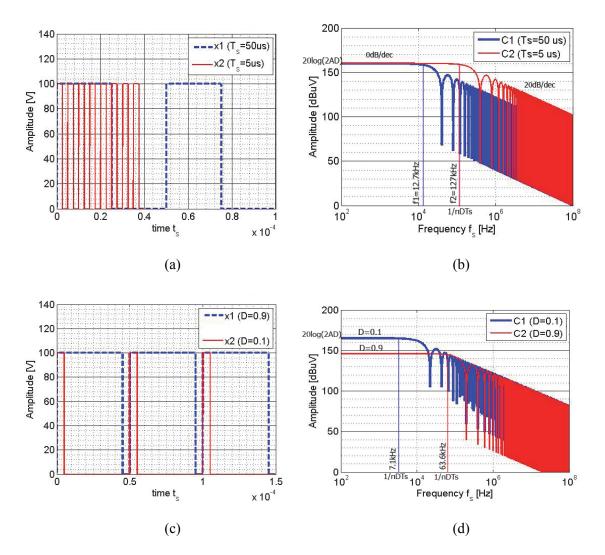

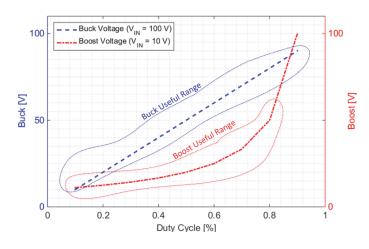

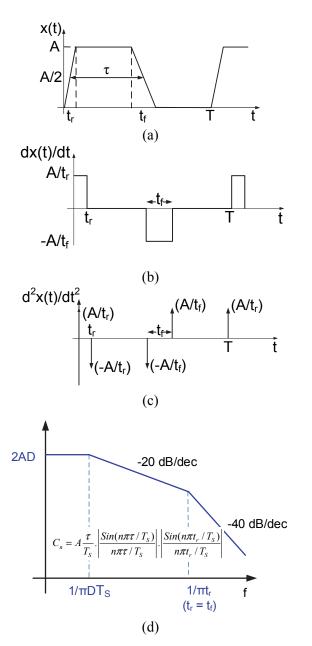

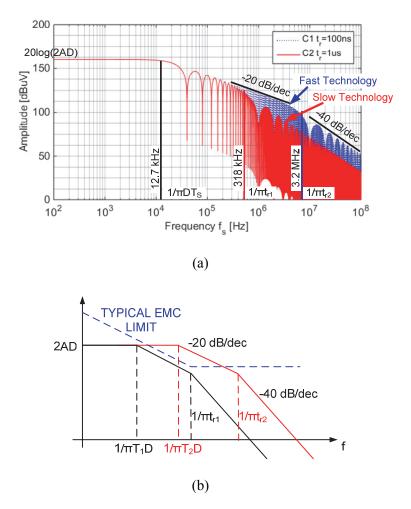

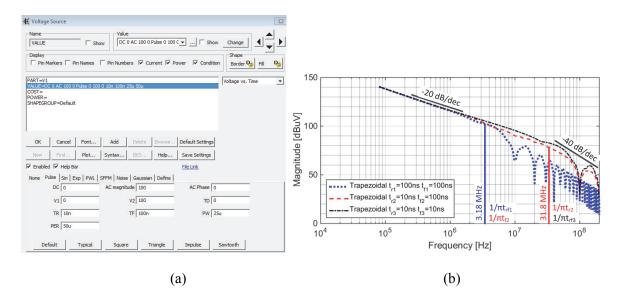

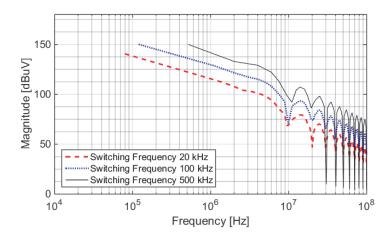

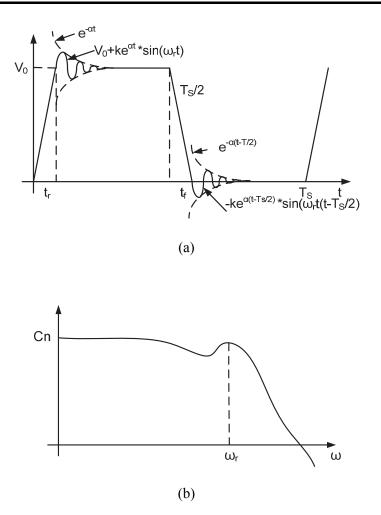

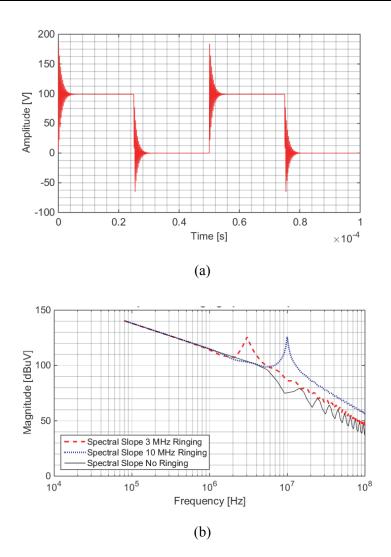

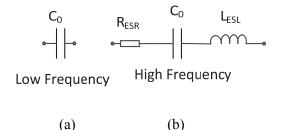

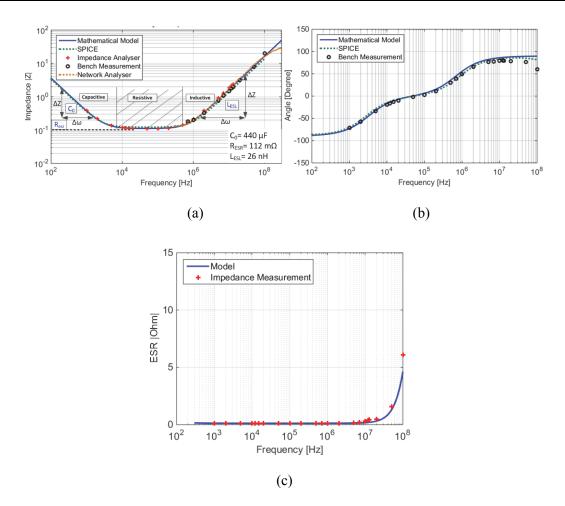

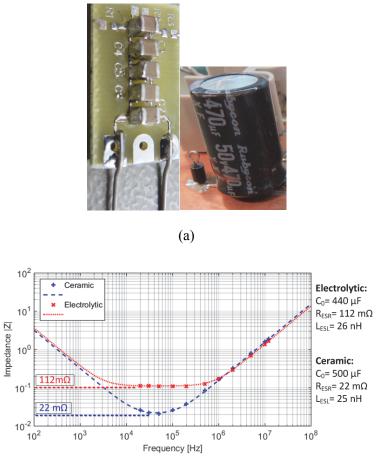

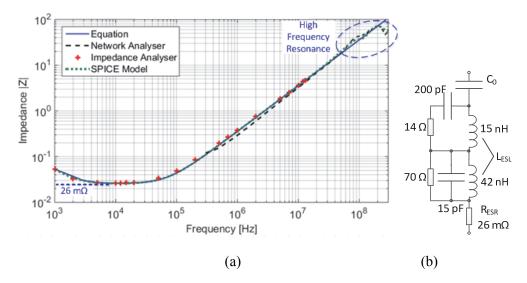

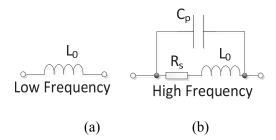

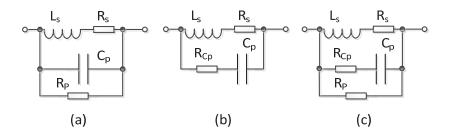

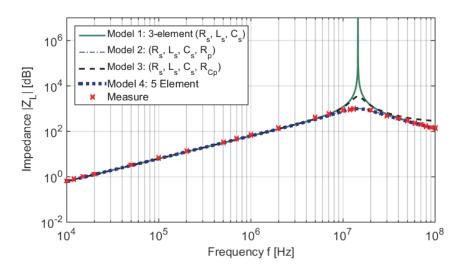

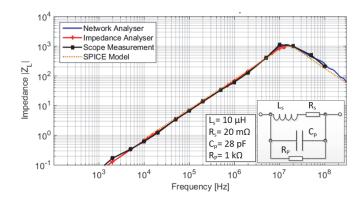

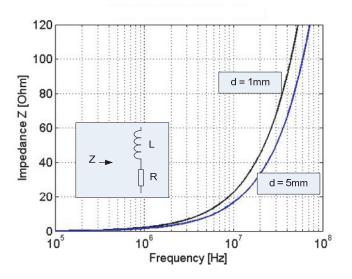

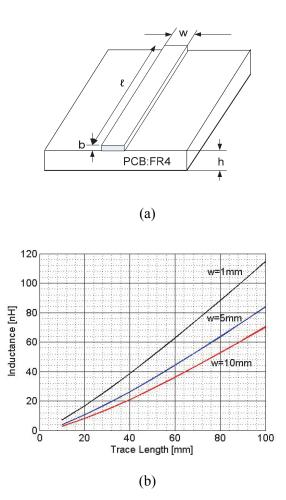

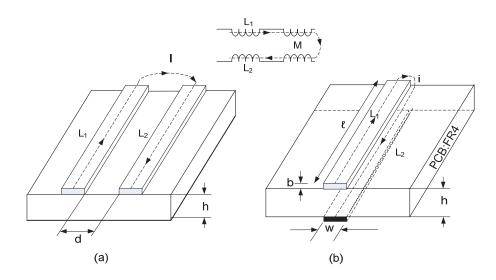

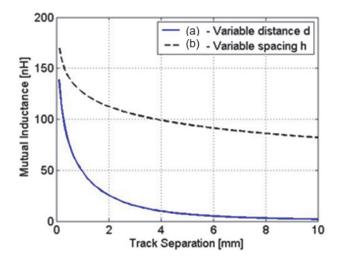

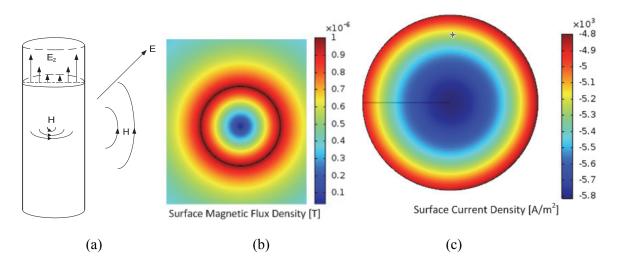

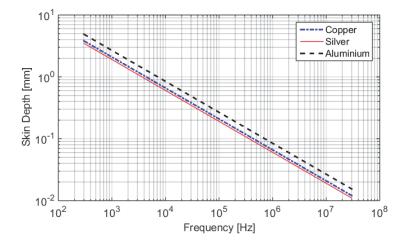

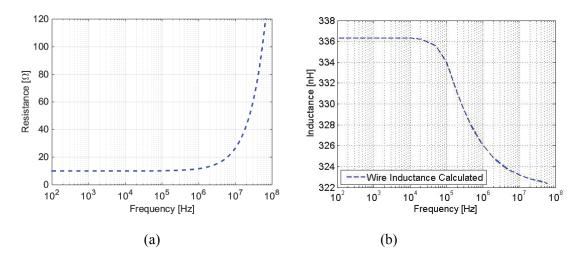

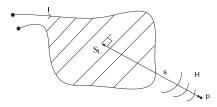

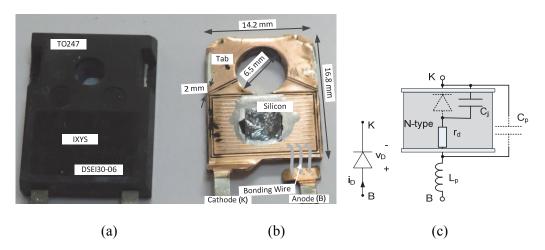

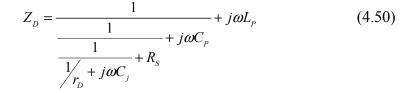

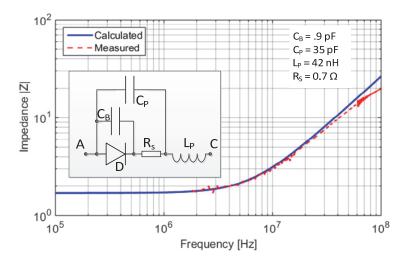

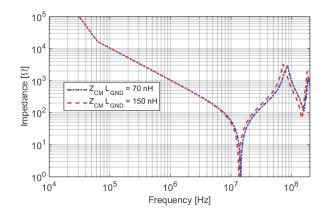

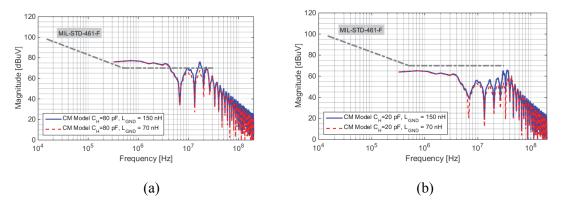

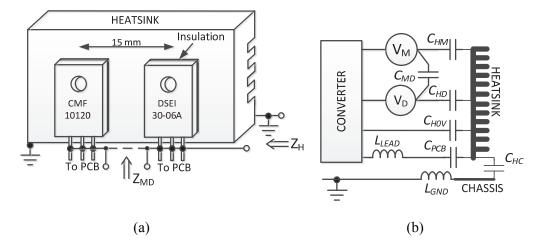

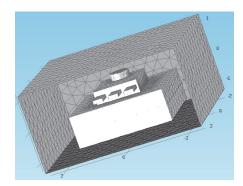

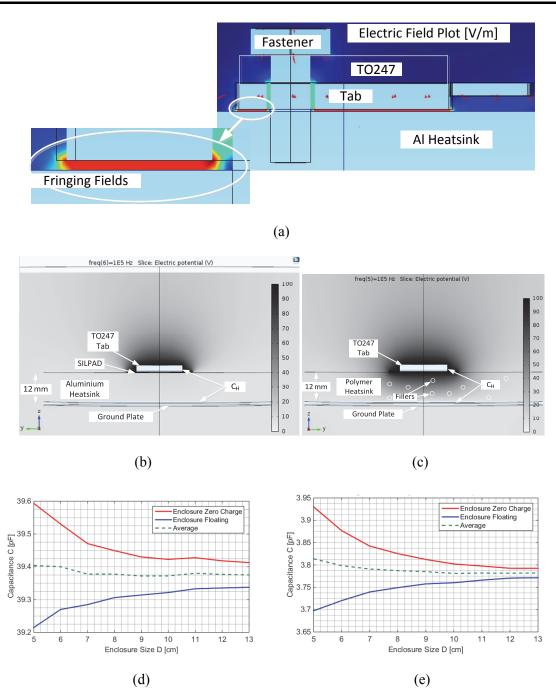

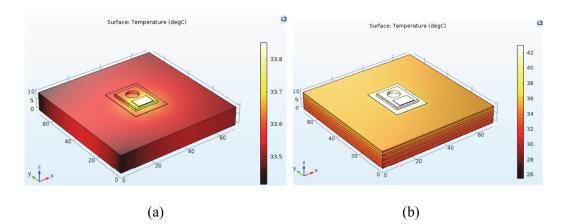

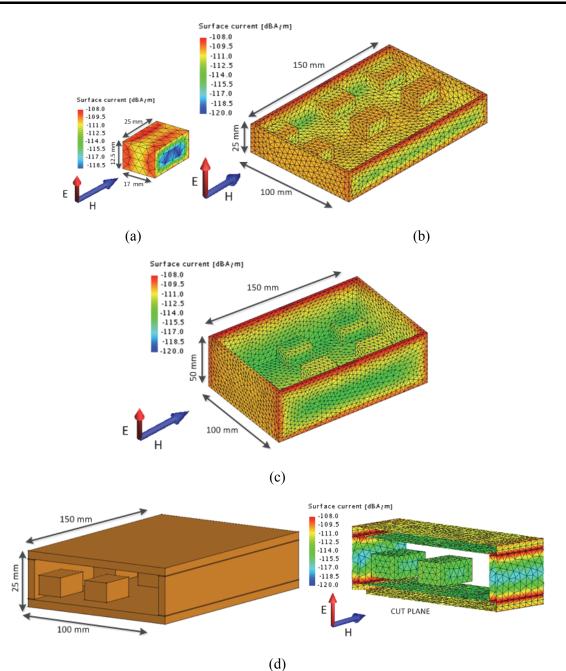

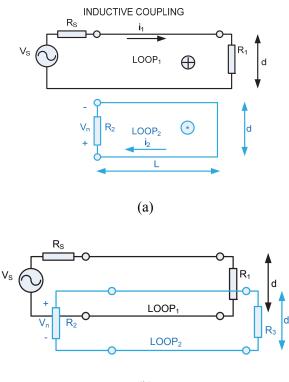

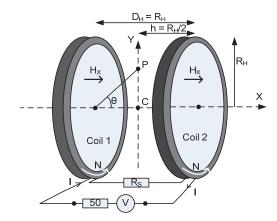

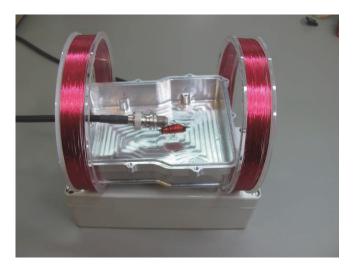

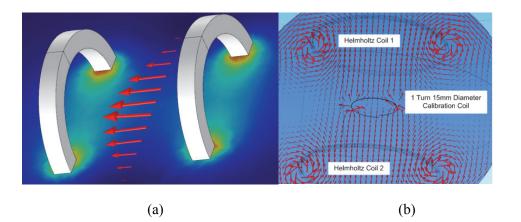

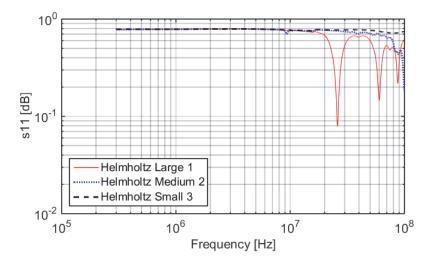

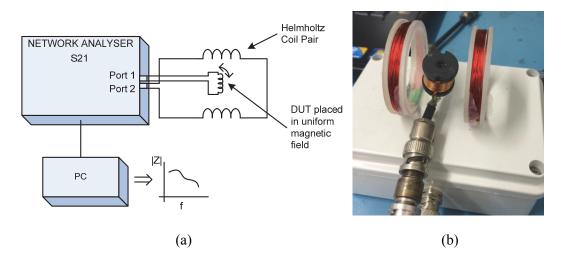

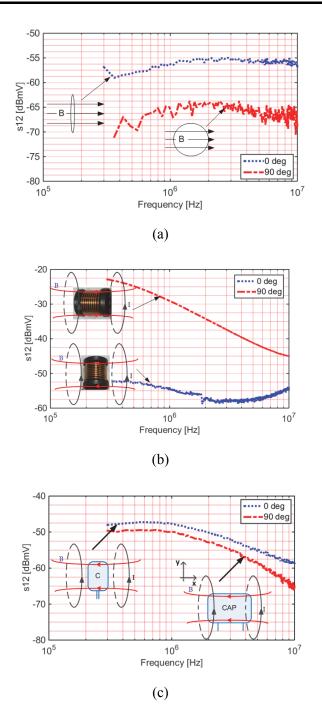

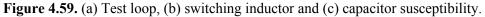

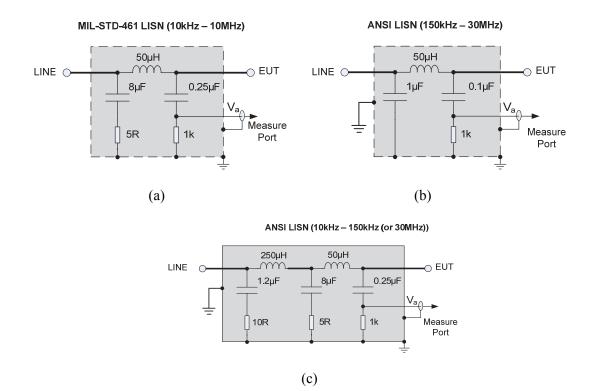

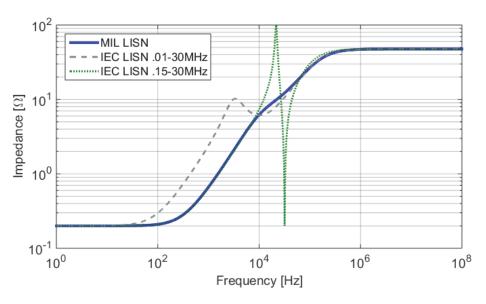

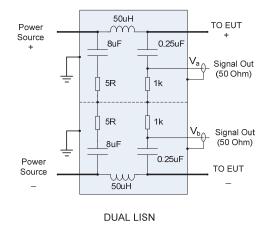

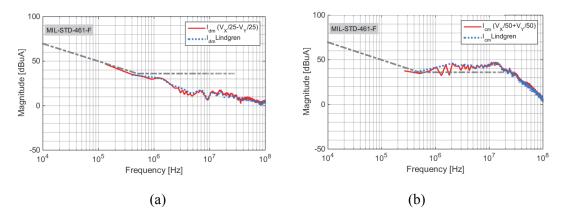

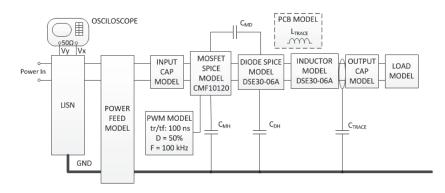

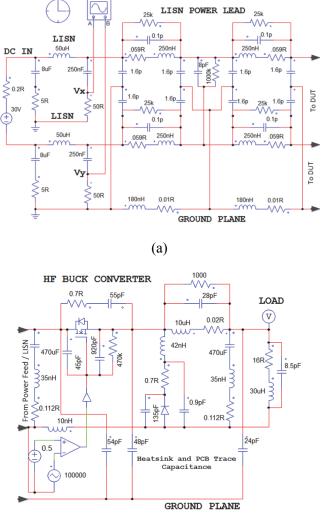

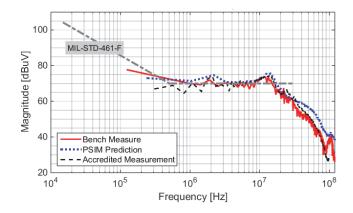

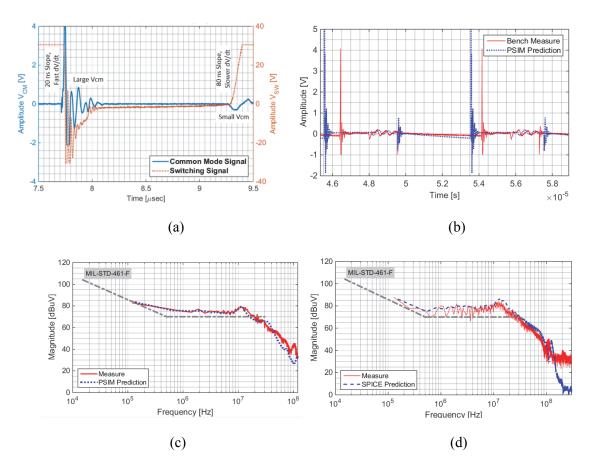

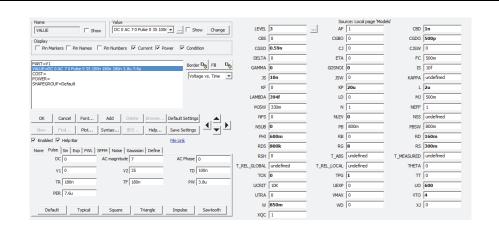

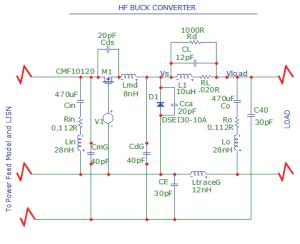

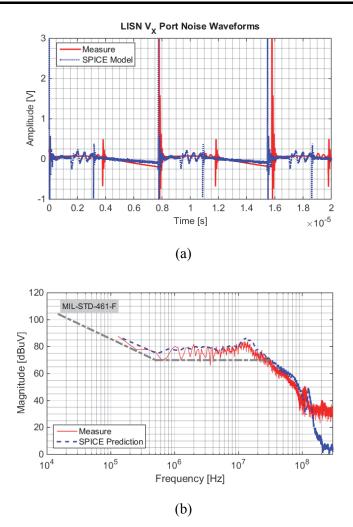

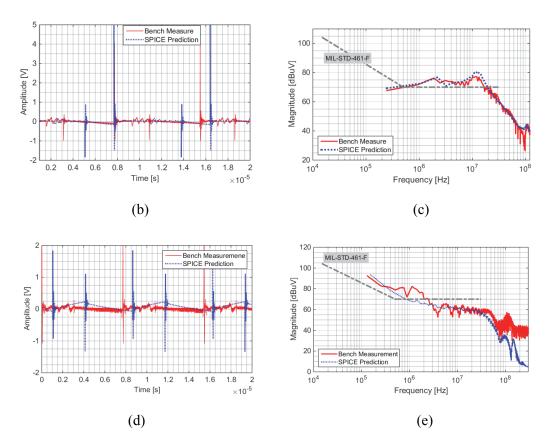

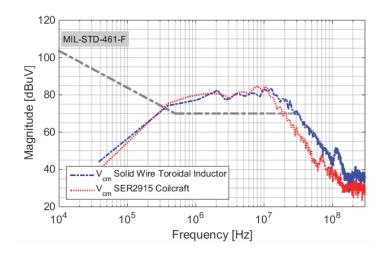

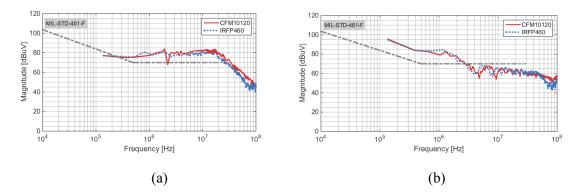

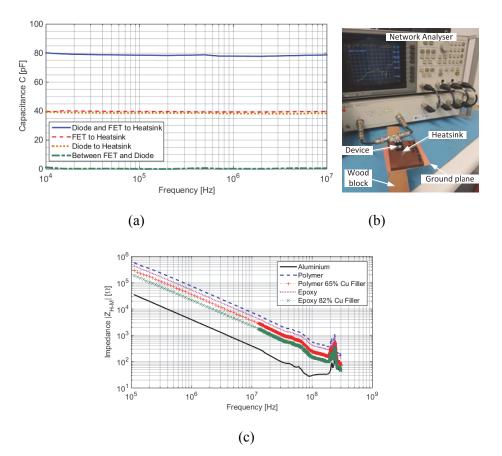

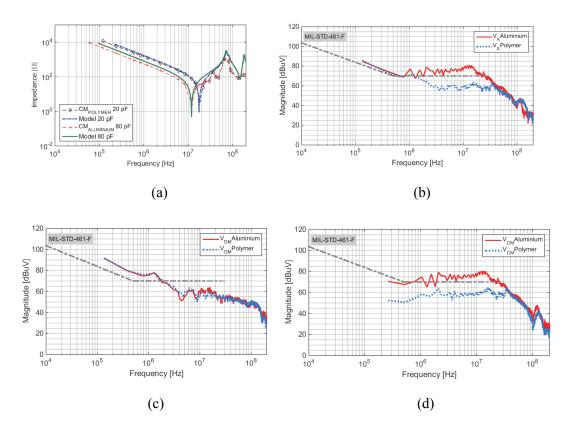

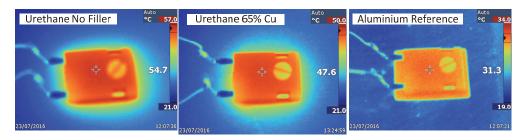

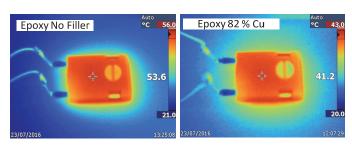

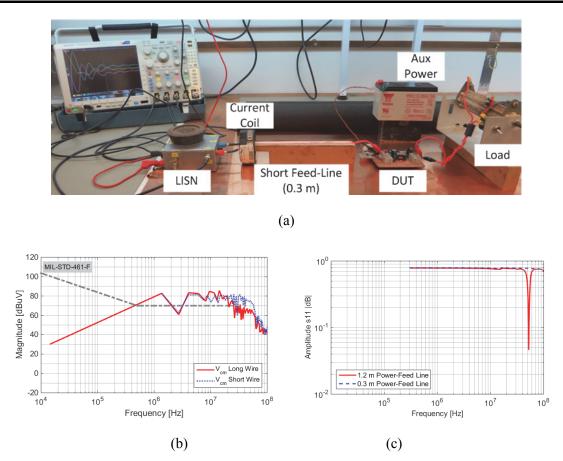

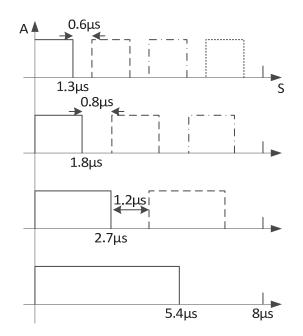

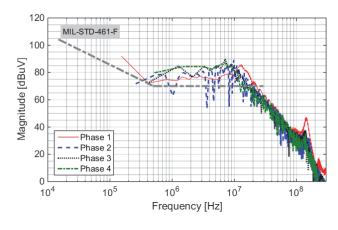

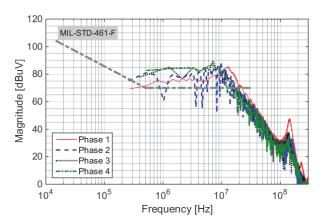

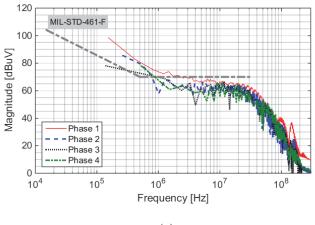

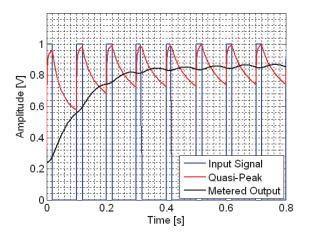

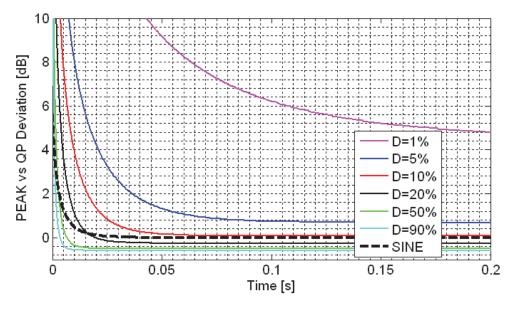

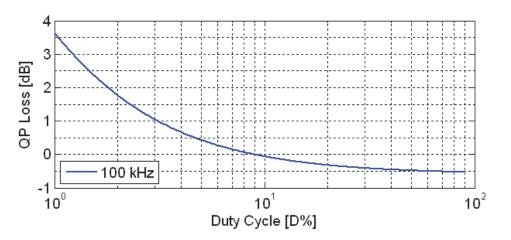

Figure 2.2. Conducted EMI emission concept.