Pretoria, South Africa Paper number: KJ1

# IDENTIFICATION OF THE ENCLOSED ELECTRO-THERMAL SYSTEM WITH USING DYNAMIC THERMAL RESPONSE

## **ABSTRACT**

A methodology for modeling and simulating electro-thermal system in an enclosed electronic package is presented. The electro-thermal model was constructed by using system dynamics, particularly the bond graph methodology. The system model, in which the electrical domain and the thermal domain are coupled, is presented. The system model described its dynamic thermal behaviour of the system caused by heat generation from the electronic package which in located in the test enclosure chamber. The system model included the timevariant thermal parameters such as environment variation and with incoming heat flow variation. In detail, an effective way to identify the time-variant thermal parameters of the system with considering transient thermal behaviour using temperature difference between nodes was suggested. The system model contains the variation of heat flow derived by resistance change of resistive heater in electronic device increasing with temperature rise of heater, and the variation of ambient air temperature. The electro-thermal system model was validated when the system has time-variant thermal parameters such as variation of convection and contact resistance. The proposed system model shows good agreement with measured temperature response in the transient state corresponding to the variance of environment.

## INTRODUCTION

Modeling and simulating electronic packaging systems has long been a popular issue, especially when the electronic package is enclosed [1]. One problem with this subject has to do with the identification of the complex structure with variations in the transient state. Most network simulation programs using FEM and FDM require a great deal of computing time for compute the system in a transient state; especially the model is composed of time-invariant system

parameters. In this paper, an approach is proposed to develop an electro-thermal model of an enclosed electronic package that takes into account time-variant parameters under the dynamic variations of the environment.

Bond graph modeling [2] is an attraction means of modeling dynamic physical systems. It is a language based on power exchanges within a system model where the structure of the system model is shown graphically [3]. One of its most interesting advantages is that it is an efficient method to represent analytical models graphically in complicated cases in which multiple energy domains (i.e. mechanical, electrical, hydraulic, thermal, magnetic) are coupled [4].

The main purpose of this paper is to build a model that describes the thermal response of enclosed electronic devices or package systems in a control box. Using the proposed electrothermal model, it is possible to predict the thermal response according to the operating conditions, the thermal deformation of components, and the reliability of component bonding in an effort to provide a guideline for designing an electronic package system. This model was tested and validated by comparing with measured data in the transient sate accompanying with dynamic variations of the environment.

# **NOMENCLATURE**

| T                | [K]   | Temperature                            |

|------------------|-------|----------------------------------------|

| $\Delta T_{A-B}$ | [K]   | Temperature difference between A and B |

| C                | [J/K] | Thermal capacitance                    |

| R                | [K/W] | Thermal resistance                     |

| Q                | [W]   | Heat flow rate                         |

| I                | [A]   | Current input on the electronic device |

| V                | [V]   | Voltage input on the electronic device |

|                  |       |                                        |

Subscripts Amb Ambient air Heater Electronic device heater Chip Chip surface  $Test\_air$  Test chamber air

Insulation chamber air Electro-thermal heater resistance External pressure loading part

#### **TEST SET UP**

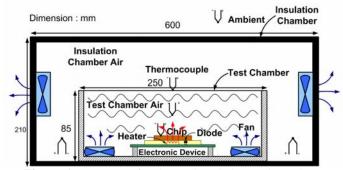

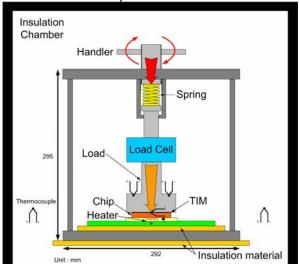

The test set-up for the modeling of an enclosed electronic package system is shown in Fig. 1. The electronic device is placed inside the test chamber. In the electronic package, heat resistance was implanted, as was a diode near this material to monitor its temperature. Several cooling fans were placed inside the wall to ensure uniformity of air temperature inside the chamber. The fans provide variation of heat transfer rate of the air through the speed changes. The test chamber was placed inside an insulation chamber to minimize the influence of any fluctuation of the surrounding air. In particular, cooling fans were placed on the wall of the insulation chamber to exhaust insulation chamber air continually to ambient. The temperatures of the chip surface, test chamber air, test chamber case surface, and insulation chamber air were measured using thermocouples.

Figure 1 Test set up for the enclosed electronic package

## **SYSTEM MODELING**

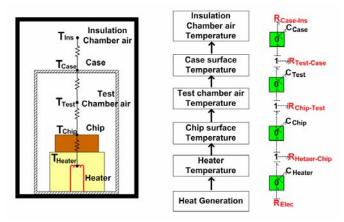

A model for the enclosed electronic package system is presented using a bond graph model. The overall heat flow in the electronic package system, including the heat generation of the electronic device heater through chip surface, the test chamber air, the test chamber case surface, and the insulation chamber air is illustrated in Fig. 2. The left side of the diagram corresponds to a bond graph model of the total amount of heat transfer in the system. Here, the '0' component represents the thermal node point and the '1' component represents the heat flow path connected to the thermal resistance. Each node has a thermal capacitance component 'C', and the thermal resistance component, 'R', exists between each node.

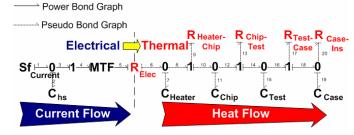

Fig. 3(a) describes the entire system in which the thermal model is coupled with the electrical model. The electronic device heater generates heat flow via 'Joule heating' with a constant current input and converts electrical energy input to thermal output. The conversion of electrical power dissipation into heat in the electro-thermal heater is modeled in bond graph by a 2-port R-field with one electrical port and one thermal port. Fig. 4 shows the electro-thermal model for a heater as a switch bond graph R-filed and its constitutive relations. In the modeling, the solid lines show the power bond graph in the electrical domain, in which the effort variable and the flow

variable represent the voltage and current respectively. On the other hand, the dotted lines show pseudo bond graph in the thermal domain, in which the effort variable and the flow variable represent the temperature and the heat flow rate respectively [5].

Figure 2 Heat flow and bond graph model

Figure 3 Bond graph model of electro-thermal system

Figure 4 Switch bond graph R-filed and its constitutive relations

# **IDENTIFICATION OF THERMAL PARAMETERS**

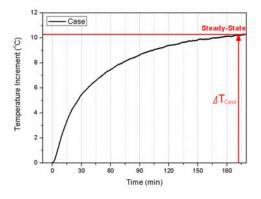

For design purposes, at this point it is now necessary to find the numerical values of the thermal components of the thermal network. Conventionally, by measuring the steady state value of the temperature response on the node point, it is possible to determine the values of the thermal resistances. From Fig. 5, the incremental value of the temperature on the surface of the test chamber case. The relationship regarding the temperature increment with the thermal resistance between the test chamber case surface and the insulation chamber air is expressed by Eq. (1).

$$\Delta T_{Case} = R_{Case-Ins} \cdot Q \tag{1}$$

It is necessary to determine the value of the heat flow rate (Q) first. The heat rate can be found using the known values of the current input on the electronic device heater and the electrothermal heater resistance. This is expressed in Eq. (2). Thus, the

value of the thermal resistance (  $R_{\text{Case-Ins}}$  ) can be obtained easily.

$$R_{Case-Ins} = \frac{\Delta T_{Case}}{I^2 \cdot R_{Flec}} \tag{2}$$

In the same way, other thermal resistance (  $R_{\it Test-Case}$  ,  $R_{\it Chip-Test}$  ,  $R_{\it Heater-Chip}$  ) values can be obtained using Eqs. (3) to (8) consecutively.

$$\Delta T_{Test} = (R_{Test-Case} + R_{Case-Inc}) \cdot Q \tag{3}$$

$$R_{Test-Case} = \frac{\Delta T_{Test}}{I^2 \cdot R_{Elec}} - R_{Case-Ins} \tag{4}$$

$$\Delta T_{Chip} = (R_{Chip-Test} + R_{Test-Case} + R_{Case-Ins}) \cdot Q \tag{5}$$

$$R_{Chip-Test} = \frac{\Delta T_{Case}}{I^2 \cdot R_{Flec}} - R_{Test-Case} - R_{Case-Ins}$$

(6)

$$\Delta T_{Heater} = (R_{Heater-Chip} + R_{Chip-Test} + R_{Test-Case} + R_{Case-Ins}) \cdot Q$$

(7)

$$R_{Heater-Chip} = \frac{\Delta T_{Heater}}{I^2 \cdot R_{Elec}} - R_{Chip-Test} - R_{Test-Case} - R_{Case-Ins}$$

(8)

**Figure 5** Temperature rise of test chamber enclosure surface (step response)

Nonetheless, it is difficult to define a specific steady state of temperature response because the temperature of the elements inside the chamber continues to increase slightly when the temperature is measured over an extended time. Therefore, a new idea is needed to identify the thermal parameters on the basis of transient behavior. Fig. 6 illustrates a part of a bond graph model that is connected with the thermal resistance (R) component in the thermal domain. In the figure, the dashed arrows with the number 1, 2, and 3 represent identical bonds,

and e and f with identical bond subscripts denote the flow and effort values. The constitution equation of the flow variable on the second bond, notified as '2', is expressed as in the Fig.

Figure 6 Thermal resistance bond graph R-element and its constitutive relations

Here,  $e_2=e_1-e_3$ ,  $f_2=Q$ , and  $T_1$  and  $T_3$  are the temperature increment values. The effort variable ( $e_2$ ) on that bond is the difference of the nearest effort variable. In the thermal domain, the flow variable and the effort variable represent the heat flow rate and the temperature, respectively. In a similar manner, through the known value of the heat flow rate and the temperature difference between each node, it is possible to identify the thermal resistances.

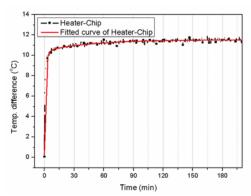

The new method for thermal resistance identification is based on the temperature difference between each node. Fig. 7 shows temperature difference between the electronic device heater and the chip surface. The temperature difference between the heater and the chip reaches a steady state very early while the temperature difference continues to increase as shown in Fig. 7. During the initial stage, the curve fitting of the temperature difference curve was conducted using an exponential decay function or polynomial function. It is possible to identify the value of the thermal resistances in a transient state using the temperature difference fitting curve.

The relationship of the temperature difference with the thermal resistance between the electronic device heater and the chip surface is expressed in Eq. (9). All temperatures are relative to the initial state temperature ( $T_{Amb}$ ), i.e.

$$\Delta T_{Heater} = T_{Heater} - T_{Amb}.$$

$$\Delta T_{Heater} - \Delta T_{Chip} = R_{Heater-Chip} \cdot Q \tag{9}$$

The heat flow rate can be found through the known values of the current input on the electronic device heater and the electro-thermal heater resistance as expressed in Eq. (10). Thus, the thermal resistance ( $R_{Heater-Chip}$ ) can be obtained easily.

$$R_{Heater-Chip} = \frac{\Delta T_{Heater} - \Delta T_{Chip}}{I^2 \cdot R_{Elec}}$$

(10)

**Figure 7** Temperature difference between the electronic device heater and the chip surface and its fitted curve

In the same way, other thermal resistance ( $R_{Case-Ins}$ ,  $R_{Test-Case}$ , and  $R_{Chip-Test}$ ) values can be obtained using Eq.s (11) to (16) consecutively.

$$\Delta T_{Case} - \Delta T_{Ins} = R_{Case-Ins} \cdot Q \tag{11}$$

$$R_{Case-Ins} = \frac{\Delta T_{Case} - \Delta T_{Ins}}{I^2 \cdot R_{Elec}}$$

(12)

$$\Delta T_{Chip} - \Delta T_{Test} = R_{Chip-Test} \cdot Q \tag{13}$$

$$R_{Chip-Test} = \frac{\Delta T_{Chip} - \Delta T_{Test}}{I^2 \cdot R_{Eleo}}$$

(14)

$$\Delta T_{Test} - \Delta T_{Case} = R_{Test-Case} \cdot Q \tag{15}$$

$$R_{Test-Case} = \frac{\Delta T_{Test} - \Delta T_{Case}}{I^2 \cdot R_{Flec}}$$

(16)

The thermal capacitance of each component can be identified from the value of the transient slope (S) at t=0 from the temperature rise curve [6].

## SIMULATION RESULTS

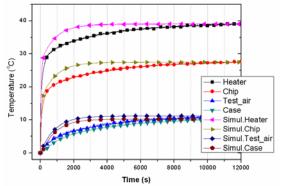

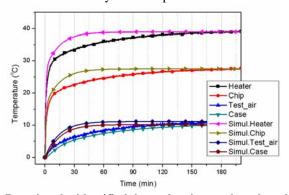

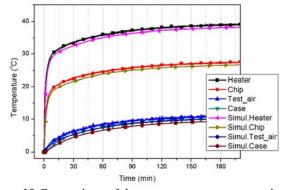

In this section, simulation results are presented with a comparison of the experimented data. The CAMP/G (Computer aided Modeling Program) with graphical editor was used to simulate the developed modeling. The software derives the equations in some code form and submits them to a simulator such as MATLAB. The source code generated by CAMP/G was modified to implement the time-variant thermal parameters. The simulation was then executed with the solver of an explicit Runge-Kutta (2, 3) pair of Bogacki and Shampine [7]. Fig. 8(a) shows the temperature rise at the constant current 150mA (I) input on the electronic device heater. In this case, the thermal resistance was identified using the temperature change from an initial state to a steady state. As is shown, the simulation results are fairly different from the measured data in the transient state. These discrepancies are caused by the identification of the thermal resistance, which is determined from the steady state temperature with a constant heat input.

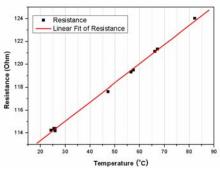

However, since the heater resistance varies with its temperature. Heat input on the electronic device continuously change with the resistance of heater even applying constant current input. It is necessary to identify the resistance variation of heater with temperature for considering the heat input variation on simulation. The relationship between resistance of heater and temperature is identified as per EIA/JEDEC standard No. 51-1 [8]. Fig. 9 shows the calibration curve of electronic package heater resistance with temperature and the relationship is expressed by Eq. (17) at this experiment. The resistance of electronic package heater resistance is  $114.20\Omega$  at the ambient temperature,  $25\,^{\circ}\mathrm{C}$ . Fig. 8(b) shows the results with consideration of the heat input variation. There still exist some discrepancies at the inflection zone.

$$R_{Elec} = 110.003 + 0.1678 \cdot T_{Heater} \tag{17}$$

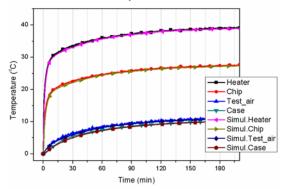

Thus, by adapting the suggested identification method using Eqs. (10) to (16), simulation results are shown in Fig. 10. The results are in good agreement, and less temperature differences between the simulated and the measured temperature response is shown. Through the comparison of the inflection zone in Fig. 8 with that in Fig. 10, the new identification method is a better approach for measuring the temperature. The temperature response of this improved identification method follows the pattern of upward trend temperature well; however, it has a temperature deviation of less than 0.8 degree for the as final instance.

(a) By using the identified thermal resistance based on the steady state temperature

(b) By using the identified thermal resistance based on the steady state temperature and the heat input variationFigure 8 Comparison of the temperature response between simulation and experiment

For a more accurate simulation, it is necessary to consider the temperature variation of the insulation chamber air. As the new method for thermal resistance identification uses the temperature difference between each node, the temperature of the insulation chamber air is a basis for all other nodes, as the ground is a basis for other node point voltages in an electrical analogy. The temperature variation of the insulation chamber air shows a downward or an upward trend following the trend of the ambient air. Using a polynomial fit through the measured temperature curve, the variation of the insulation chamber air temperature can be included in the model, and comparisons between the measurement and the simulation results are shown in Fig. 11. As it can be seen, the results are in good agreement with the measured temperature response in the transient state without temperature deviations.

**Figure 9** Calibration curve of electronic package heater resistance with temperature

**Figure 10** Comparison of the temperature response using the thermal resistance based on the temperature difference and the heat input variance

Figure 11 Comparison of the temperature response

## **VALIDATION OF THE SYSTEM MODELING**

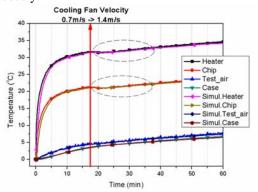

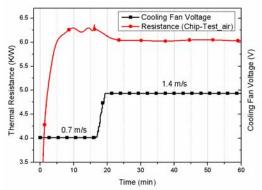

In this section, the electro-thermal bond graph model was validated when the system has time-variant thermal parameters such as heat convection and thermal contact resistance. Fig. 12 shows a case the effect of a convection change. An electronic device was operated at a constant current input, and cooling fan speed inside test chamber was switched from 0.7m/s to 1.5m/s. Fig. 12(a) shows effects on the temperature response of each node in the existence of variations in the convection condition with cooling fan air speed. Fig. 12(b) shows a comparison of input voltage on fan and fan air speed, measured by anemometer and the simulated thermal resistance between the test chamber air and the case surface. With increases in the velocity of the fan cooler speed, the thermal resistance between the chip surface and the test chamber internal air, calculated from simulation results, decreases from 6.3K/W to 6.0K/W.

Validation of the contact pressure variation was also performed. Fig. 13 shows the experimental set up with an electronic device and external pressure variation apparatus. Applying pressure on the electronic device was regulated using a bolt screw-type handler and was measured using a load cell simultaneously.

(a) Simulation results and measured temperature curves

(b) Thermal resistance from simulation results and the input voltage on fan and air velocity from measurements

**Figure 12** Simulation results and validation curves with variations of the internal air flow

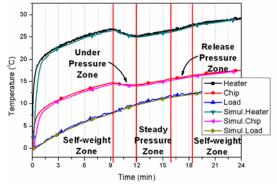

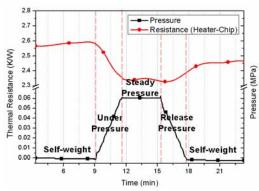

With a constant current input on the electronic device heater, the temperature of each node point (electronic device heater, chip surface, and pressure loading part) was measured when applying a pressure change. The electronic device was operated at a constant 150mA current input and the applied pressure varied from a self-weight value to 0.06MPa. Fig. 14(a) shows the comparison of the temperature response while changing the pressure. All practical surfaces have microscopic irregularities such as roughness and frequently macroscopic irregularities

such as waviness and deviation from flatness, therefore, a contact formed by pressing two surfaces together is never perfect. The irregularity of real surface is therefore a primary caused of thermal contact resistance. The area of contact spots can be increased by applying pressure that will flatten the peaks of the micro roughness and deflecting the mating surface to reduce any non-flatness. As external pressure is applied to the surface of electronic device, the thermal contact resistance between the electronic package heater and the chip decreases, therefore, it makes temperature decrease of heater and chip surface. This phenomenon can be verified by comparing with external pressure variation along with the thermal resistance between the electronic device heater and the chip surface, as shown in Fig. 14(b). The thermal resistance between the electronic package heater and the chip surface, calculated from simulation results decreases from 2.55K/W to 2.35K/W while the thermal resistance increases from 2.35K/W to 2.5K/W after

the release of the external pressure.

Figure 13 Experimental set up of external pressure variation

It is possible to estimate the variation of the thermal resistance on the system from the dynamic temperature response induced by the variation of the convection condition or the contact pressure.

(a) Simulation results and measured temperature curves

(b) Thermal resistance from simulation results and external pressure variation curve

**Figure 14** Simulation results and validation curves with variations of the applied external pressure

## **CONCLUSIONS**

A new method of modeling and simulating the electrothermal behavior of enclosed electronic packages is proposed and validated. An electrical model was coupled with a thermal model in a complete system model such that the joule heat caused by the operation of the device changes directly according to the device temperature. Thermal resistance identification using the temperature difference between each node in the transient state is presented and verified by comparisons of the temperature response between the measurement data and the simulation results.

The simulated temperature response based on the proposed method well agreed with the measured one. This model also can be extended to estimate the variation of the thermal resistance of the system induced by thermal boundary conditions such as environment or contact pressure.

# **REFERENCES**

- V. Szekely, A new evaluation method of thermal transient measurement results, Microelectronics Journal, Vol. 28, 1997, pp. 277-292.

- [2] H. M. Paynter, Analysis and Design of Engineering Systems, MIT Press, Cambridge, MA, USA, 1961.

- [3] J. Garcia, G. Dauphin-Tanguy, C. Rombaut., Electrothermal Bond Graph Model for Semiconductor Switching Devices, In Proceedings of the APEC'96 Conference. San Jose, 1996, pp. 258-263.

- [4] J.J. Granda, Shaoqing Tang, Computer Simulation of Heat Transfer Models Using a Pseudo Bond Graph Network, Trans. of the Society for Computer Simulation, Vol. 5, Num. 4, 1988, pp. 265-283.

- [5] P. J. Gawthrop, Thermal modelling using mixed energy and pseudo bond graphs, Proceedings of the Institution of Mechanical Engineers Part I-Journal of Systems and Control Engineering, Vol. 213, 1999, pp. 201-216.

- [6] C. Sueur and G. Dauphintanguy, BOND GRAPH APPROACH TO MULTITIME SCALE SYSTEMS-ANALYSIS, Journal of the Franklin Institute-Engineering and Applied Mathematics, Vol. 328, 1991, pp. 1005-1026.

- [7] Bogachi, P. and L. F. Shampine, A 3(2) pair of Runge-Kutta formulas, Appl. Math. Letters, Vol. 2, 1989, pp. 1-9

- [8] EIA/JESD 51-1, Integrated Circuits Thermal Measurement Method

Electrical Test Method (Single Semiconductor Device)