# SiGe BASED MULTIPLE-PHASE VCO OPERATING FOR MM-WAVE FREQUENCIES

by

#### Deepa George

Submitted in partial fulfilment of the requirements for the degree

Philosophiae Doctor (Electronics)

in the

Department of Electrical, Electronic and Computer Engineering Faculty of Engineering, Built Environment and Information Technology

UNIVERSITY OF PRETORIA

April 2013

#### **SUMMARY**

# SiGe BASED MULTIPLE-PHASE VCO OPERATING FOR MM-WAVE FREQUENCIES

by

#### Deepa George

Supervisor: Prof. S. Sinha

Department: Electrical, Electronic and Computer Engineering

University: University of Pretoria

Degree: PhD (Electronics)

Keywords: Voltage-controlled oscillator (VCO), millimetre-wave (mm-wave),

silicon germanium (SiGe), heterojunction bipolar transistor (HBT), Colpitts oscillator, phase noise, impulse sensitivity function, phased arrays, vector sum, hybrid coupler, variable gain amplifier (VGA),

Gilbert mixer, integrated circuit (IC)

The ever-increasing demand for higher speed in wireless consumer applications has increased the interest in the unlicensed spectrum of 7 GHz around 60 GHz. The high atmospheric oxygen absorption at 60 GHz and small size of the antennas at this frequency requires the use of integrated phased-array systems to overcome the deficiencies of lossy channels at these frequencies. The phased arrays combine signals from multiple paths to obtain higher receiver sensitivity and directivity. The system thus requires phase-shifted voltage-controlled oscillator (VCO) signals to implement phase shifting in the local-oscillator (LO) path.

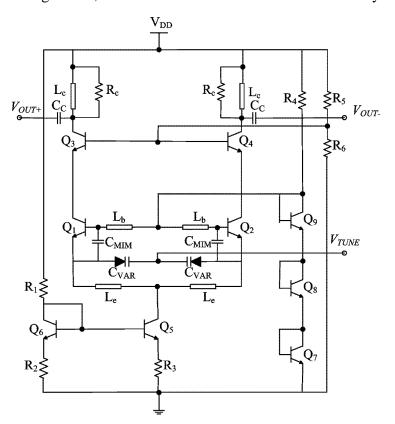

In this research, the vector sum method to generate various phases of the signal at 60 GHz was investigated for its suitability in phased-array systems. The main focus was on improving the phase noise performance of the VCO. The VCO was implemented using a fully differential common-collector Colpitts oscillator in the cascode configuration, which

was found to be the VCO configuration with acceptable phase noise performance and stability in the millimetre-wave range.

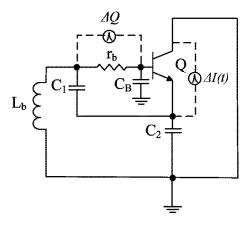

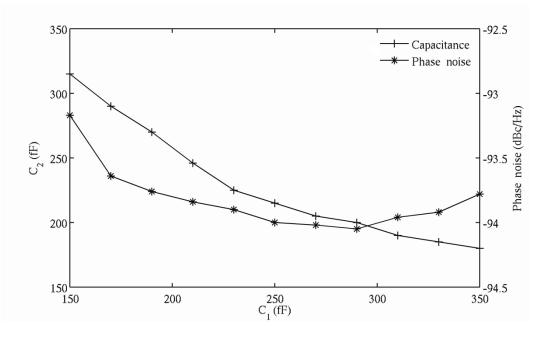

The research focus was on modelling the phase noise of the VCO, and was performed by identifying the impulse sensitivity function for various noise sources, followed by analysing its effect on the linear time varying (LTV) model of the oscillators. The analysis led to a closed-form expression for the phase noise of the oscillator in terms of process and design parameters. The design was then optimised in terms of identified parameters to attain minimum phase noise. The phase noise expression using LTV theory and SpectreRF simulations reported the same optimum value for the design parameter, of around 0.3 for the capacitor ratio.

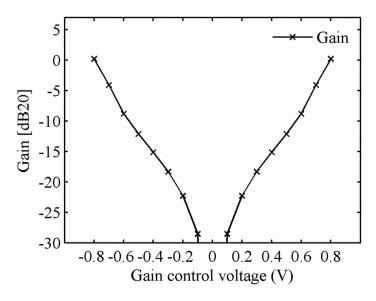

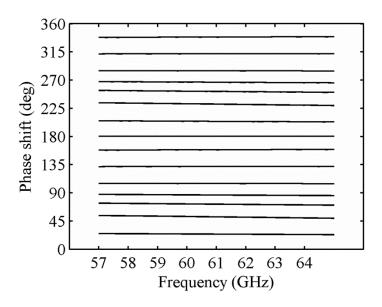

The simulation results utilising the vector sum phase shifting method to generate multiple phase oscillator signals suggest its suitability in implementing phased-array systems in the millimetre-wave range. The vector sum was realised by generating quadrature signals from the oscillator using hybrid couplers. Variable gain amplifiers (VGAs) based on Gilbert mixer topology were used to combine the in-phase and quadrature phase signals to generate the phase-shifted oscillator signal. The gains of the VGAs were linearised by using a pre-distortion circuit, which was an inverse tanh cell.

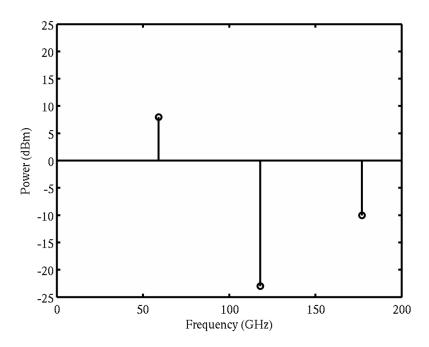

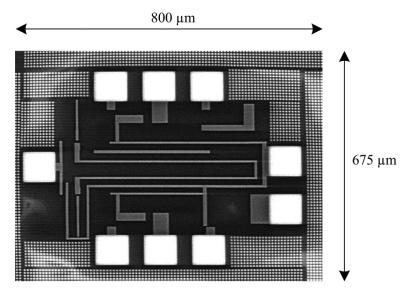

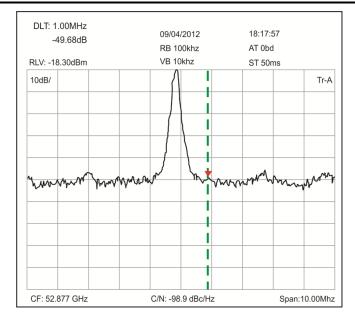

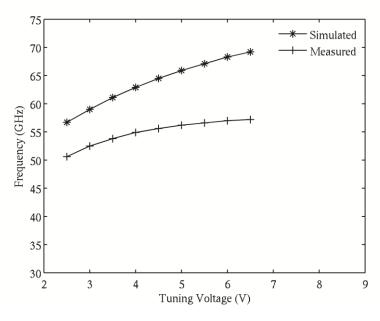

A fully differential 60 GHz VCO was fabricated using a SiGe process with a  $f_T$  of 200 GHz. The fabricated integrated circuit (IC) measured at the wafer level had a centre frequency of 52.8 GHz and a tuning range of 7 GHz. It demonstrated a phase noise performance of -98.9 dBc/Hz at 1 MHz offset and a power dissipation of 140 mW, thus providing a VCO figure of merit of 172 dBc/Hz. It delivered a differential output power of 8 dBm and the IC occupied an area of 0.54 mm<sup>2</sup>, including the bondpads. It was thus concluded that a 10% design margin for the tuning range is required while using SiGe BiCMOS technology.

The simulation results demonstrate that the VCO, along with an active interpolator, provides a range of phase-shifted signals from 0° to 360° in steps of 22.5° for various gain settings of the VGAs. The power dissipation of the active interpolator is around 60 mW and the system could thus be employed in LO path shifting architecture of the phased arrays with increased power consumption.

#### **OPSOMMING**

# SiGe-GEBASEERDE VEELVULDIGEFASE-VCO WAT FUNKSIONEER VIR MM-GOLFFREKWENSIES

deur

#### Deepa George

Studieleier: Prof. S. Sinha

Departement: Elektriese, Elektroniese en Rekenaaringenieurswese

Universiteit Universiteit van Pretoria

Graad: PhD (Elektronies)

Sleutelwoorde: Spanningsbeheerde ossillator (VCO), millimetergolf (mm-golf),

silikon-germanium (SiGe), heterovoegvlak bipolêre transistor, Colpitts-ossillator, faseruis, impulssensitiwiteitsfunksie, gefaseerde rangskikking, vektorsom, hibried-koppelaars, verstelbare wins

versterker (VGA), Gilbert-menger, geïntegreerde stroombaan

Die steeds toenemende vraag na hoër spoed in draadlose verbruikerstoepassings het die belangstelling in die ongelisensieerde 7 GHz spektrum rondom 60 GHz verhoog. Die hoë atmosferiese suurstof absorpsie by 60 GHz en klein dimensies van die antennas by hierdie frekwensie benodig die gebruik van geïntegreerde gefaseerde rangskikkingsisteme om die tekortkomings van verliesige kanale by hierdie frekwensies die hoof te bied. Die gefaseerde rangskikkingsisteme kombineer seine van veelvuldige kanale om beter ontvangersensitiwiteit en -gerigtheid te verkry. Die sisteem vereis dus faseverskuifde spanningsgekontroleerde ossillatorseine om faseverskuiwing in die plaaslike ossillator te implementeer.

In hierdie navorsing is die vektorsommetode geïmplementeer om verskeie fases van die sein by 60 GHz op te wek en te ondersoek, om die geskiktheid daarvan vir gefaseerde rangskikkingsisteme te bepaal. Die hoofklem was op die verbetering van die faseruiswerksverrigting van die spanningsbeheerde ossillator (VCO). Die VCO is geïmplementeer deur gebruik te maak van 'n ten volle differensiële gemene kollektor

Colpitts-ossillator in die kaskodekonfigurasie, wat geblyk het om die VCO-konfigurasie met aanvaarbare faseruiswerkverrigting en stabiliteit in die millimetergolfbereik te wees.

Die fokus van die navorsing was op die modellering van die faseruis van die VCO en dit is uitgevoer deur die impulssensitiwiteitsfunksie van verskeie ruisbronne te identifiseer, waarna die effek daarvan op die liniêre tydwisselende model van die ossillators geanaliseer is. Die ontleding het gelei tot 'n geslotevormuitdrukking vir die faseruis van die ossillator ingevolge proses- en ontwerpsparameters. Die ontwerp is daarna geoptimeer kragtens geïdentifiseerde parameters om die minimum faseruis te behaal. Die faseruisuitdrukking wat liniêre tydwisselingsteorie en SpectreRF simulasies gebruik het, het dieselfde optimumwaarde van ongeveer 0.3 vir die kapasitorverhouding bevestig.

Die simulasieresultate tydens die gebruik van die vektorsomfaseverskuiwingsmetode om veelvuldigefase-ossillatorseine te genereer, dui die geskiktheid daarvan aan vir gebruik in gefaseerde rangskikkingsisteme in die millimetergolfbereik. Die vektorsom is bereik deur die opwekking van kwadratuurseine van die ossillator deur die gebruik van hibried-koppelaars. Verstelbare wins versterkers (VGAs) gebaseer op Gilbert-mengertopologie is gebruik om die infase- en kwadratuurfaseseine te kombineer om die faseverskuifde ossillatorsein op te wek. Die versterking van die VGAs is gelineariseer deur die gebruik van 'n opsetlike vervormingsbaan, naamlik 'n omgekeerde tanh-sel.

'n Ten volle gedifferensieerde 60 GHz VCO is vervaardig deur gebruik te maak van 'n SiGe BiCMOS-proses met 'n  $f_T$  van 200 GHz. Die geïntegreerde stroombaan wat vervaardig is, gemeet op vlokkie-vlak, het 'n sentrale frekwensie van 52.8 GHz asook 'n instem-omvang van 7 GHz gehad. Dit het 'n faseruiswerksverrigting van -98.9 dBc/Hz gespesifiseerd by 1 MHz afwyking en kragverbruik van 140 mW gelewer, en dus 'n VCO-gevoeligheidskonstante van 172 dBc/Hz. Dit het 'n differensiële uitsetkrag van 8 dBm gelewer en die geïntegreerde stroombaan het 'n oppervlakte van 0.54 mm² op die vlokkie beslaan, insluitende die verbindingstukke. Daar is dus tot die gevolgtrekking gekom dat 'n 10 %-ontwerpstoleransie vir die instemgebied vereis word as SiGe BiCMOS-tegnologie gebruik word.

Die simulasie resultate toon dat die VCO, saam met 'n aktiewe interpoleerder, 'n omvang van faseverskuifde seine van 0° tot 360° lewer in stappe van 22.5° vir verskeie versterkerstellings van die VGAs. Die kragverlies van die aktiewe interpolator is ongeveer

60 mW en die stelsel kan dus met verhoogde drywingsgebruik in die plaaslike ossillatorbaanverskuiwingsargitektuur van die gefaseerde rangskikkings aangewend word.

### ACKNOWLEDGMENT

First and foremost, I thank the Almighty God for his grace and granting me the strength to complete this journey.

This work would not have happened if not for the support and motivation of my mentor, Prof. Saurabh Sinha. His enthusiasm and interest in the research work has been a great encouragement to me. I also appreciate his patience and constant feedback on the work, which has helped me in finishing it.

I am thankful to Mr Jannes Venter at Carl and Emily Fuchs Institute for Microelectronics (CEFIM), for providing the software support and for resolving any issue that came up during the work.

I have enjoyed working with my colleagues, Bongani Mabuza and Christo Janse van Rensburg, during our joint multi-project wafer (MPW) run. I also express my sincere gratitude to other colleagues at CEFIM, Dr Marnus Weststrate, Wynand Lambrechts, Johny Sebastian, Joe Valliarampath, Antonie Alberts and Marius Goosen, for the interesting discussions we have had.

Thanks to MOSIS educational programme for providing me with the MPW run. Special thanks to SAAB Electronic Defence Systems for the support and manufacture of the PCBs. I am very grateful to Erik-Jan Moes, Dr Alexandru Müller, Prof. Dan Neculoiu, Dr Valentine Buiculescu, Dr Alina Cismaru, Dr Alexandra Stefanescu and Alina Bunea for their valuable guidance and willingness to help at various stages of the work.

I am grateful to Ms Tilla Nel, the departmental administrator (CEFIM), for her support at various stages and for providing a comfortable atmosphere to pursue the work.

I thank the National Research Foundation (NRF) of South Africa for sponsoring my trip to National Institute for Microtechnologies (IMT-Bucharest) in Romania for measurement purposes. The trip was funded resulting from an international bilateral agreement

facilitated by the NRF and it's counterpart in Romania (Autoritatea Nationala pentru Cercetare Stiintifica). The research group at CEFIM was beneficiary to this funding by way of a competitive research grant proposal in the area of "mm-Wave Radio System Design" (NRF UID# 67949). Another funding instrument supporting this work was through the NRF "Competitive Support for Rated Researcher" - "The design and realization of MOS UHF power transistors," NRF UID# 73666. I remain thankful to CEFIM and it's research management structure that compete for research grants enabling for funding of international research-oriented trips for students and emerging researchers.

I also express my sincere gratitude to my parents, M. X. George and Philo George, and my brother, Dejo George, who have encouraged me all my life to pursue my dreams and for their unwavering support and encouragement to help me reach my goal.

Last, but not least I cannot thank my husband, Jibin Francis, and my lovely daughter, Misha Francis, enough for their support and understanding during my research work.

#### LIST OF ABBREVIATIONS

ADE Analog Design Environment

BEOL Back-end-of-line

BiCMOS Bipolar and CMOS

BJT Bipolar junction transistor

CMOS Complementary metal oxide semiconductor

CBE Collector-base-emitter

CBEBC Collector-base-emitter-base-collector

DAC Digital-to-analogue converter

DC Direct current

DUT Device under test

EM Electromagnetic

FET Field effect transistor

FOM Figure of merit

GaAs Gallium arsenide

GBP Gain-bandwidth product

GSG Ground-signal-ground

HBT Heterojunction bipolar transistor

IC Integrated circuit

IF Image frequency

InP Indium phosphate

I/O Input / output

ISF Impulse sensitivity function

LO Local oscillator

LVS Layout versus schematic

LTI Linear time-invariant

LTV Linear time-varying

MEP MOSIS educational program

MIM Metal-insulator-metal

MMIC Monolithic microwave integrated circuit

MOS Metal-oxide-semiconductor

MOSIS MOS implementation service

MPW Multi-project wafer

NDA Non-disclosure agreement

NF Noise figure

PCB Printed circuit board

PDK Process design kit

PLL Phase locked loop

RBW Resolution bandwidth

RF Radio frequency

SiGe Silicon germanium

SPICE Simulation program with integrated circuit emphasis

VCO Voltage-controlled oscillator

WPAN Wireless personal area network

## TABLE OF CONTENTS

| CHAPTER 1: INTRODUCTION                        | 1  |

|------------------------------------------------|----|

| 1.1 BACKGROUND TO THE RESEARCH                 | 1  |

| 1.1.1 Phased-array systems                     | 2  |

| 1.1.2 Vector-sum phase-shifting method         | 4  |

| 1.2 MOTIVATION FOR THE RESEARCH                | 6  |

| 1.3 RESEARCH PROBLEM AND HYPOTHESIS            | 7  |

| 1.4 JUSTIFICATION FOR THE RESEARCH             | 8  |

| 1.5 METHODOLOGY                                | 8  |

| 1.6 DELIMITATIONS OF SCOPE AND KEY ASSUMPTIONS | 9  |

| 1.7 CONTRIBUTIONS TO THE FIELD                 | 9  |

| 1.8 PUBLICATIONS DERIVED FROM THE RESEARCH     | 12 |

| 1.9 OUTLINE OF THE THESIS                      | 12 |

| 1.10 CONCLUSION                                | 14 |

|                                                |    |

| CHAPTER 2: LITERATURE REVIEW                   | 15 |

| 2.1 INTRODUCTION                               |    |

| 2.2 SiGe TECHNOLOGY FOR MM-WAVE APPLICATIONS   |    |

| 2.3 INTEGRATED PHASED-ARRAY IMPLEMENTATIONS    | 20 |

| 2.4 PHASE SHIFTERS                             |    |

| 2.5 MULTIPLE-PHASE VCO                         |    |

| 2.6 PHASE NOISE IN OSCILLATORS                 |    |

| 2.6.1 Leeson's LTI approach                    | 22 |

| 2.6.2 Hajmiri and Lee's LTV approach           | 25 |

| 2.7 DESIGN OF VCO CORE                         | 30 |

| 2.7.1 Design considerations                    | 32 |

| 2.8 IMPLEMENTATION OF VECTOR-SUM INTERPOLATOR  | 34 |

| 2.8.1 Lange couplers                           | 34 |

| 2.8.2 Design of VGA                            | 35 |

| 2.9 MILLIMETRE-WAVE DESIGN CHALLENGES          |    |

| 2.9.1 Substrate effects                        | 37 |

| 2.9.2 Packages and module design               | 38 |

| 2.10 CONCLUSION                                                 | 38         |

|-----------------------------------------------------------------|------------|

| CHAPTER 3: RESEARCH METHODOLOGY                                 | 40         |

| 3.1 INTRODUCTION                                                | 40         |

| 3.2 INTEGRATED CIRCUIT PROCESS                                  | 40         |

| 3.2.1 SiGe HBT characteristics                                  | 40         |

| 3.2.2 Inductors                                                 | 42         |

| 3.2.3 Capacitors                                                |            |

| 3.2.4 Resistors                                                 |            |

| 3.3 PHASE NOISE MODELLING IN THE 1/f² REGION USING THE IS       |            |

| 3.4 OSCILLATOR SIMULATIONS IN CADENCE (PSS, PNOISE)             |            |

| 3.5 MEASUREMENT SETUP AND EQUIPMENT                             | 46         |

| 3.6 CONCLUSION                                                  | 48         |

| CHAPTER 4: ANALYTICAL MODELLING                                 | 49         |

| 4.1 INTRODUCTION                                                | 49         |

| 4.2 OSCILLATION AMPLITUDE                                       | 49         |

| 4.2.1 Analytical expression for fundamental current $i_{fund}$  | 51         |

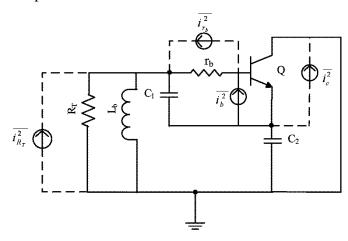

| 4.3 PHASE NOISE CONTRIBUTION FROM ACTIVE DEVICE NOISE           | SOURCES 52 |

| 4.3.1 Phase noise contribution of collector current shot noise  | 54         |

| 4.3.2 Phase noise contribution of base resistance thermal noise | 56         |

| 4.4 CONCLUSION                                                  | 59         |

| CHAPTER 5: CIRCUIT DESIGN AND SIMULATION                        | 60         |

| 5.1 INTRODUCTION                                                | 60         |

| 5.2 DIFFERENTIAL COLPITTS OSCILLATOR                            | 60         |

| 5.3 DESIGN OF THE PASSIVE COMPONENTS                            | 62         |

| 5.3.1 Inductors in the circuit                                  | 62         |

| 5.3.2 Design of capacitors                                      | 62         |

| 5.3.3 Q and C-V characteristics of the varactors                | 63         |

| 5.4 QUADRATURE SIGNAL GENERATION                                |            |

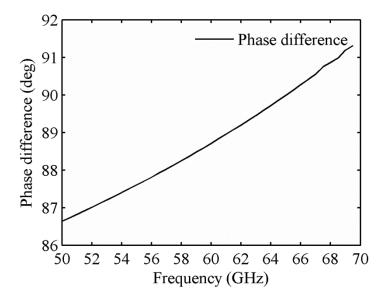

| 5.4.1 Lange coupler                                             | 65         |

| 5.5 VGA                                                         | 67         |

| 5.6 CONCLUSION                                                  | 69         |

| CHAPTER 6: LAYOUT, FABRICATION AND MEASUREMENT | 70 |

|------------------------------------------------|----|

| 6.1 INTRODUCTION                               | 70 |

| 6.2 IC LAYOUT AND FABRICATION                  | 70 |

| 6.3 PCB LAYOUT AND FABRICATION                 | 72 |

| 6.4 MEASUREMENT RESULTS                        | 73 |

| 6.5 CONCLUSION                                 | 75 |

| CHAPTER 7: CONCLUSION                          | 76 |

| 7.1 INTRODUCTION                               | 76 |

| 7.2 CRITICAL EVALUATION OF THE WORK            | 76 |

| 7.3 SUGGESTIONS FOR FUTURE WORK                | 78 |

### **CHAPTER 1: INTRODUCTION**

#### 1.1 BACKGROUND TO THE RESEARCH

The millimetre-wave (mm-wave) band has been attracting world-wide attention because of the high speed data communication that can be achieved with the wide band of unlicensed spectrum available at 60 GHz [1]. The IEEE 802.15.3 Task Group 3c (TG3c) has developed a mm-wave based physical layer for the wireless personal area network (WPAN) standard, which operates in the 57-64 GHz unlicensed band and can provide high data rates over 2 Gbps [2]. The channel frequencies allocated in the IEEE 802.15.3c standard are 58.32 GHz, 60.48 GHz, 62.64 GHz and 64.8 GHz, which are similar to other standards, such as ECMA, WiGig, WirelessHD etc. The advancement in silicon integrated circuits (ICs) [3] [4] have also driven the development activity in the mm-wave consumer and commercial market, namely in WPANs at 60 GHz [5] [6] and also in automotive radars at 24 GHz and 77 GHz [7] [8] [9]. In addition to achieving higher communication speeds and improved radar detection, higher imaging resolution is another applications that is being explored in the mm-wave range [10].

The 57-64 GHz band is in the mm-wave portion of the electromagnetic (EM) spectrum, where the wavelength ranges from ten millimetres (30 GHz) to one millimetre (300 GHz). The specific attenuation characteristics of 10 to 15 dB/km due to atmospheric oxygen absorption at 60 GHz makes this band suitable for short-range (<1 km) communications. The high attenuation factor also helps in frequency re-use, as one 60 GHz radio link is attenuated enough not to interfere with another 60 GHz link operating in its geographic vicinity [1].

In addition to obtaining high-speed systems, the added advantage of moving to higher frequencies is the reduction in the size of the antennas ( $\lambda$  of about 2.4 mm in silicon dioxide at mm-wave), which can create compact systems. The small size of the antennas necessitates highly directional beams for communication, which could be obtained using

techniques such as phased arrays. This is also suitable as the behaviour at V-band is more line-of-sight and there is less diffraction compared to lower frequencies [11].

#### 1.1.1 Phased-array systems

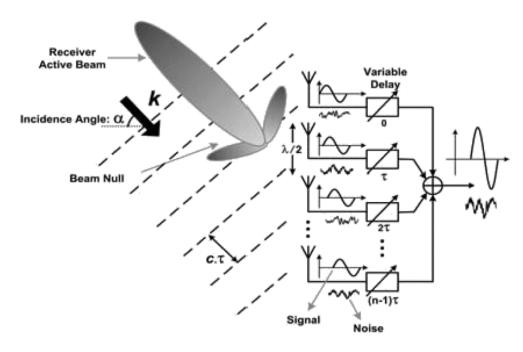

A complete integrated phased-array system consists of several antenna elements arranged in one or two dimensions, with each element having its own signal path. A phased-array receiver and transmitter implementation is shown in Figure 1.1 and Figure 1.2 respectively.

Figure 1.1. Phased-array receiver [11] (Copyright © [2008] IEICE)

In a phased-array receiver as in Figure 1.1, the signal reaches each of the spatially separated antennas at different times, depending on the angle of incidence and the spacing between the antennas. The time delay between the signals at different antenna elements are compensated for and the signals are coherently combined by the receiver to enhance the reception from the desired direction [12]. This helps in rejecting any interference that does not originate from the direction of the intended signal.

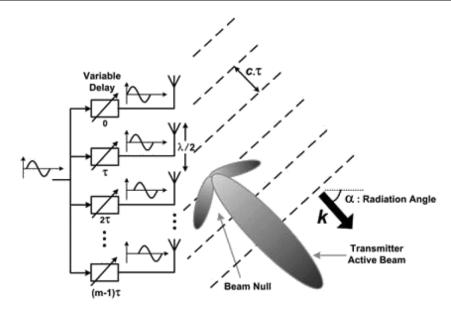

Figure 1.2. Phased-array transmitter [11] (Copyright © [2008] IEICE)

In a phased-array transmitter as in Figure 1.2, the signals radiating from each element are delayed such that they add up coherently and thus transmit in the intended direction. In a transmitter with n antenna elements, the total power radiated is  $n^2$  times that of the power radiated by a single antenna element. Thus the power-handling requirement of each of the active devices is also alleviated, while migrating to a newer technology node, which has higher performance but a lower breakdown voltage.

Better sensitivity and improved rejection capability to interference are the main attributes of a phased-array receiver. The directivity of a transceiver also results in improving the frequency reuse ratio, thus increasing the capacity of the network.

In narrow-band systems, the required time delay in the signals at each element of the phased array can be obtained by a phase-shift. A phase shifter with a phase control range of 360° and a phase resolution of 22.5° is the typical requirement for phased-array systems [13].

The phase-shift can be applied at radio frequency (RF), baseband/IF or the local oscillator (LO) path. The RF path phase-shifting approach has the lowest power consumption, and

hence is the architecture implemented most often in phased-array implementations [6] [13]. The advantage of LO path phase-shifting is that the phase-shifter loss does not directly deteriorate the receiver sensitivity [7] [8]. The various phases required at the antenna elements can be obtained in a centralised or decentralised method. In the centralised approach, all the necessary phases are generated in one place [7], while in the decentralised approach, the LO signal is distributed and the remaining phases are generated locally using a phase rotator in each LO path [8]. In a centralised LO-path approach, the phase resolution is limited by the number of phases generated by the voltage controlled oscillator (VCO). Also, the phase distribution network becomes quite complex as the number of antenna elements is increased and they tend to perform less efficiently at mm-wave frequencies. Therefore, the decentralised option or *local* LO-path phase-shifting system is preferred in phased-array systems where the phase resolution will depend on the resolution of interpolator weights, employed as part of the phase rotator, and can be generated by using high-resolution digital-to-analogue converters (DACs).

The phase-shifted signals for implementing phased-array transceivers could be achieved using passive architecture such as a reflection-type phase shifter [14]. The disadvantage of implementation with passives is the high insertion loss of about 4.2 dB – 7.5 dB at 60 GHz. An active interpolator for the RF-path phase shifting approach at 60 GHz [15] is reported to achieve 360° phase variation, -2 dB gain, 12 GHz 3 dB bandwidth and a 16.5 dB noise figure.

#### 1.1.2 Vector-sum phase-shifting method

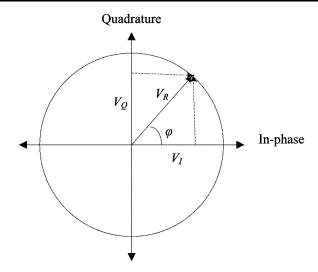

The vector-sum phase-shifting method could be employed to generate a random phase signal from an in-phase and a quadrature phase signal [16] [17] [18]. As the amplitudes of both signals are varied independently, the resulting phase and amplitude will vary accordingly, as shown in Figure 1.3, and are given by (1.1)

$$V_R = \sqrt{V_I^2 + V_Q^2}$$

;  $\varphi = \tan^{-1} \frac{V_Q}{V_I}$  (1.1)

Figure 1.3. Vector sum phase-shifting method

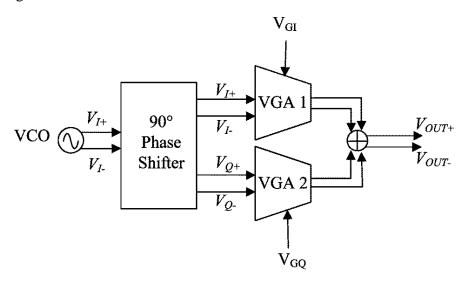

As shown in Figure 1.3, the quadrature-phased signals are combined to obtain the signal whose magnitude and phase depends on the magnitudes of the in-phase and quadrature signals. The LO phase-shifting approach for phased-array systems requires a phase-shifted oscillator signal to be applied to the mixers in each signal path. Such a linearly varying phase signal generator could be conceptualised as an integrated phase-shifted VCO, as shown in Figure 1.4.

Figure 1.4. Block diagram of the integrated phase-shifted VCO

According to Figure 1.4, the essential components of the integrated phase-shifted VCO are the VCO, the 90° phase shifter to generate  $V_I, V_Q$  and variable gain amplifiers (VGAs) whose gain could be controlled by current-steering DACs. In a phased-array system with multiple antenna elements, a single VCO along with buffers and transmission lines in the distribution network could channel the signals to the phase shifter circuits. The phase shifter circuits could then generate the required phase shifts locally by using quadrature generators and VGAs in each signal path of the phased arrays as in a decentralised approach.

#### 1.2 MOTIVATION FOR THE RESEARCH

Traditionally, the III-V compound semiconductors technology, which has a relatively high  $f_T$ , high breakdown voltage and lower passive losses, has been used for RF design, but its commercialisation is not viable owing to the associated higher cost. The technology advances have pushed the  $f_T$  of silicon germanium (SiGe) and metal-oxide-semiconductor (MOS) transistors to as high as 500 GHz [19], thus making high performance systems based on these technologies commercially viable.

The objective of this research was to test the feasibility and accuracy of a SiGe production technology based integrated phase shifted VCO for implementing a phased-array system. The objective was to minimise the rms phase error in the output of the integrated phase-shifted VCO to reduce the jitter in the output transmitter beam of phased arrays [8]. In addition, the particular requirement of an oscillator in any communication system (especially for ones with narrow channel spacing) is the low phase noise of the oscillator, as the channel spacing is constrained by the phase noise. Hence this research also targeted the improvement of phase noise performance of VCOs, particularly at 60 GHz, by studying the phenomenon of phase noise generation. It focused on analytically modelling the phase noise to optimise the design performance by identifying the high-impact process or design parameters. This helped in generalising a design procedure for optimum phase noise performance at any mm-wave frequency.

#### 1.3 RESEARCH PROBLEM AND HYPOTHESIS

This research aimed to investigate the performance of an integrated phase shifter system at 60 GHz, which could be used to implement the *local* LO-path phase shifting for phased-array systems. To minimise the rms phase error in the output of an integrated phase-shifted VCO, the focus was placed on improving the performance of the VCO. The following research hypothesis was proposed to improve that aspect of the research problem.

• If a linear time varying (LTV) model could be used to analyse a mm-wave VCO configuration, then an analytical expression for phase noise in terms of process and design parameters could be derived and optimised to improve the phase noise performance of the VCO.

In the mm-wave spectrum, phase noise primarily depends on the quality factor of the varactor and hence, instead of researching the improvement of the inductor quality factor at mm-wave frequency, the focus will be on studying the effect of the varactor performance and thus on optimising its value during the design.

To validate the hypothesis, a mm-wave VCO was prototyped using a production-ready IC process, namely the IBM 8HP 130 nm SiGe BiCMOS process with the devices including the passives and the heterojunction bipolar transistors (HBTs) using their process design kits (PDKs).

The performance improvement of the VCO was then quantified by calculating the VCO figure of merit (FOM) [20] defined as in (1.2),

$$FOM = -L(f_c, \Delta f) + 10\log\left(\left(\frac{f_c}{\Delta f}\right)^2 \frac{1 \, mW}{P_{supply}}\right) \tag{1.2}$$

where  $L(f_c, \Delta f)$  is the phase noise at offset  $\Delta f$  in dBc/Hz;  $P_{\text{supply}}$  is the power consumption in mW;  $f_c$  and  $\Delta f$  are the carrier and offset frequency.

Another research problem investigated was the feasibility of implementing an integrated phase shifter using the vector-sum phase-shifting method in the IBM 130 nm process.

#### 1.4 JUSTIFICATION FOR THE RESEARCH

The demands for higher speeds in communication systems and the channel allocation by IEEE 802.15.3c have accelerated the research activity in the mm-wave spectrum, where phased arrays are implemented to achieve the necessary directivity. These phased arrays require LO signals at multiple phases to steer the direction of the beam. These signals could be generated from the VCO using vector interpolation and this would mean that its performance would depend on the performance of the VCO.

In general, a wireless transceiver requiring a VCO to perform RF to baseband conversion needs good phase noise performance for the VCO, as it determines the system sensitivity. To design a VCO with good phase noise performance, it is imperative to model the effects of various noise sources in the circuit on the final phase noise, and thus decide on the design choices. The linear time-varying (LTV) model of oscillator was thus studied and the effect of various noise sources was quantified by using their impulse sensitivity function (ISF). This eventually led to an expression, which was then optimised and thus the design choices were developed. These design choices serve as a reference for any mm-wave VCO design that would require optimum phase noise performance.

The hypothesis was validated by a VCO prototype using the IBM 130 nm SiGe BiCMOS process, which is a production-ready process for mm-wave applications. This would mean that the design could be performed without the need for any time-consuming EM simulations, which is mostly used to design passives for the mm-wave circuit design arena [21].

#### 1.5 METHODOLOGY

As a 60 GHz VCO was prototyped to validate the hypothesis, the design methodology consisted of literature study performed on the various mm-wave VCO configurations that have been implemented to date. The most popular VCO configuration was identified as the

differential Colpitts oscillator with a cascode buffer. As proposed, phase noise modelling using the ISF was performed on the LTV model of the oscillator. This would lead to an analytical expression, which would help in optimising the phase noise.

The design choices leading from the above analysis were used in designing a mm-wave VCO. The simulations were performed using the PDK supplied by IBM for the 130nm process. Numerical simulations on the design using SpectreRF also led to the same conclusion as the analytical modelling. Simulations were performed to verify the proposed vector interpolation scheme to generate various phases from the VCO output.

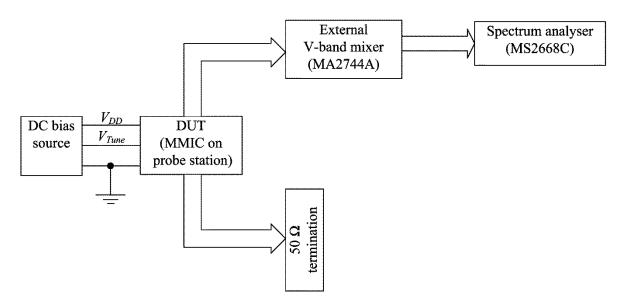

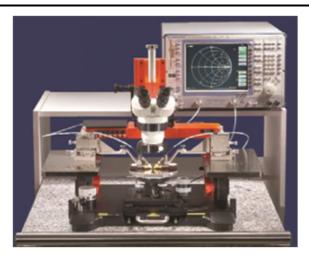

Finally, the layout of the designed 60 GHz VCO was submitted for fabrication in the IBM 8HP 130 nm SiGe BiCMOS process. A PCB was then designed and fabricated to characterise the monolithic microwave integrated circuit (MMIC) on the wafer level. The measurements were then performed using a spectrum analyser, MS2668C, and the VCO characteristics were recorded.

#### 1.6 DELIMITATIONS OF SCOPE AND KEY ASSUMPTIONS

A mm-wave design methodology usually encompasses interconnect modelling, where the 'electrically long' interconnects need to be treated as transmission lines rather than shorts. This would mean that after the layout, interconnects have to be characterised in EM simulation software and incorporated back into the schematic design for proper simulation of the circuits. This approach was not followed in the research and this decision is justified, as care was taken during the layout to keep the interconnect length as short as possible.

#### 1.7 CONTRIBUTIONS TO THE FIELD

Phase noise analysis has been performed on a mm-wave VCO configuration, and an analytical expression for phase noise in terms of process and design parameters has been derived. A detailed list of the resulting contributions to the body of knowledge is given here.

• The major contribution of the research has been the modelling of phase noise of a mm-wave VCO configuration, using the ISF of various noise sources on the LTV model of oscillators. This led to an analytical expression for phase noise in terms of process and design parameters for the specific circuit configuration, followed by minimisation of its value by optimisation of these parameters.

- A common collector Colpitts oscillator in the cascode configuration has been analytically modelled for its phase noise performance. The phase noise contributions from the noise sources associated with active devices in the circuit have been quantified using their impulse sensitivity function. The resulting analytical expression for phase noise provides an explanation for the design choices made by the designer.

- The lumped element approach to mm-wave design followed in this work used the PDK provided by the foundry and no EM simulations were performed to characterise the components.

- A mm-wave VCO was fabricated based on the analysis and was measured to demonstrate a phase noise performance of -98.9 dBc/Hz at 1 MHz offset, from a centre frequency of 52.8 GHz. The power consumption of the MMIC was around 140 mW and it occupied an area of 0.64 mm<sup>2</sup>, including the bondpads.

Oscillator designs can be widely varied in design criteria and include optimisation in area or any design specification such as phase noise or power consumption, the technology used etc. Generally the parameter FOM given by (1.2), which includes the design specifications such as oscillating frequency, phase noise and power consumption, is reported for benchmarking the design. A summary of the performance of state-of-the-art SiGe VCOs is given in Table 1.1.

Table 1.1. Comparison with state-of-the-art SiGe VCOs in the mm-wave range

| References                         | [22]                   | [23]                      | [24] [25]                 |                        | This work [26]            |

|------------------------------------|------------------------|---------------------------|---------------------------|------------------------|---------------------------|

| Impact Factor (2011)               | 3.226                  | 3.226                     | 1.853                     | 3.226                  | 0.618                     |

| Cited Half-life (2011)             | 7.1                    | 7.1                       | 9.0                       | 7.1                    | 5.0                       |

| Technology                         | 0.35 μm<br>SiGe<br>HBT | 0.18 μm<br>SiGe<br>BiCMOS | 0.13 μm<br>SiGe<br>BiCMOS | 0.35 μm<br>SiGe<br>HBT | 0.13 µm<br>SiGe<br>BiCMOS |

| Frequency (GHz)                    | 41                     | 52.5                      | 70.5                      | 80                     | 52.8                      |

| Freq Tuning Range (%)              | 26                     | 26.5                      | 5                         | 30                     | 13.5                      |

| Phase Noise at 1 MHz               | -110                   | -108                      | -93                       | -97                    | -98.9                     |

| Differential Output<br>Power (dBm) | 6.5                    | 1.5                       | 0                         | 12                     | 8                         |

| Power Consumption (mW)             | 280                    | 132                       | 73                        | 240                    | 140                       |

| Area (mm²)                         | 0.5 (with pads         | 0.168                     | Not Given                 | Not<br>Given           | 0.28                      |

| FoM (dBc/Hz)                       | 178                    | 181                       | 171                       | 171                    | 172                       |

From Table 1.1, it is evident that the VCO in this work presents an FOM comparable to the state-of-the-art VCOs. [22] presents a higher FOM, but is achieved at twice the power dissipation than that of this work. The output power is not taken into account in the presented FOM, and that is the reason for the high FOM of [23]; as can be noted, it

provides very low output power. The reason for the low output power is that it is a push-push VCO, in which the second harmonic is combined at the output to provide a higher frequency of oscillation. A push-push topology is advantageous in achieving a wide tuning range and low phase noise with low power consumption, as the tank operates at half the frequency [27]. The disadvantage is that the power output at the second harmonic, which is the useful one, is very low.

• The suitability of a vector interpolator in phased-array systems to steer the beam direction was demonstrated through simulations. The interpolator provided VCO signals from 0° to 360° in steps of 22.5° with a total power consumption of about 60 mW. This could be successfully implemented in a *local* LO-path shifting architecture to provide phase-shifted VCO signals to mixers in the signal path of a transceiver.

#### 1.8 PUBLICATIONS DERIVED FROM THE RESEARCH

The following peer-reviewed journal (listed by the Thomson Reuters Web of Knowledge) article has been published:

• D. George and S. Sinha, "Phase noise analysis for a mm-wave VCO configuration", *Microwave and Optical Technology Letters*, vol. 55, no. 2, pp. 290-295, February 2013.

A second article on the research work has been submitted for publication to a journal (also listed by the Thomson Reuters Web of Knowledge):

D. George and S. Sinha, "Vector-sum method for multiple-phase generation in mmwave phased array systems using BiCMOS technology", Analog Integrated Circuits and Signal Processing.

#### 1.9 OUTLINE OF THE THESIS

Chapter 1 provides the background and context of the research that was undertaken. The research problem and hypothesis are stated. A summary of the research methodology that

was adopted and the contribution of the research to the body of knowledge are discussed, followed by the publication derived from the research.

Chapter 2 provides the details of the literature that was reviewed to validate the proposed research hypothesis. The choice of SiGe technology and the way in which the noise sources in the technology are converted into phase noise in the oscillators are discussed briefly. The VCO implementations in the mm-wave range and current circuit techniques used to improve the phase noise performance have been thoroughly studied.

Chapter 3 describes the research methodology in detail. It provides a study of the process to be used in designing the prototype mm-wave VCO. It also discusses the details of the measurement setup that to be used, so that the layout of the MMIC can be finalised according to any equipment setup requirements.

Chapter 4 discusses the analytical model for phase noise developed in the research. An analytical expression for phase noise was derived for a mm-wave VCO configuration, so that any design optimisation could be performed. The design and process parameters that influence the phase noise performance were identified in this process. This helped in providing a solution to the design choices that are crucial to circuit performance.

Chapter 5 describes the design and simulation of the VCO and the vector interpolator using components available in the IBM 130 nm SiGe BiCMOS process. Numerical simulations have been performed to verify the optimum value of the design parameter capacitors' ratio, n, as indicated by the analytical model derived in Chapter 4.

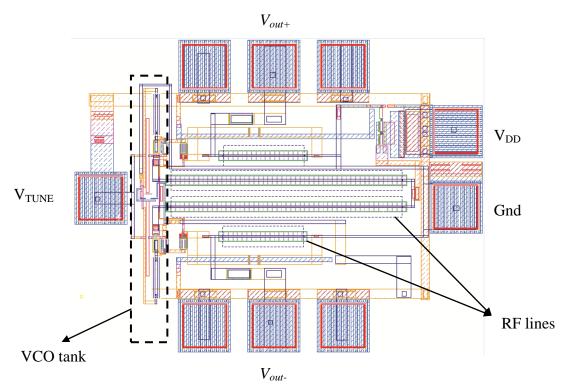

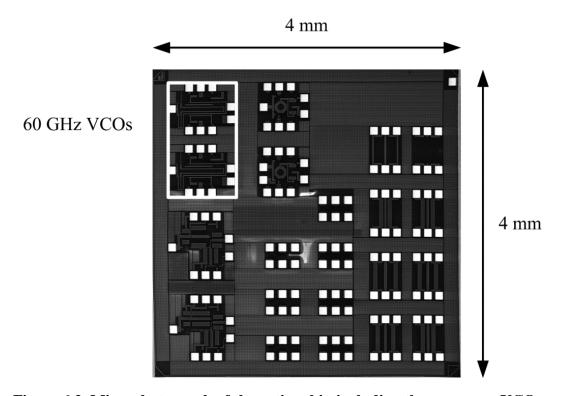

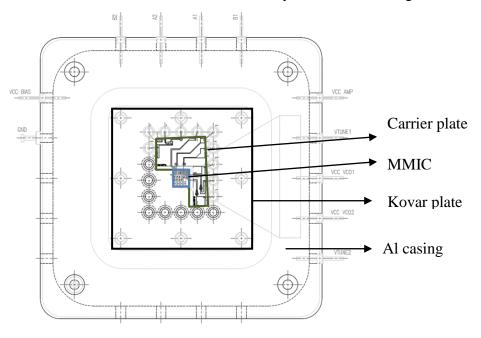

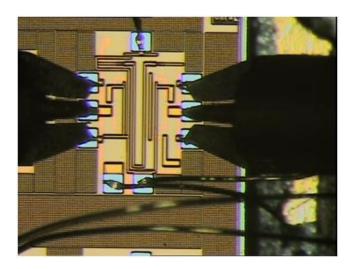

Chapter 6 details the layout of the MMIC, and provides microphotographs of the chip. It also describes the PCB and its components. The measurement setup for characterising the VCO is described and the results are presented. The measurement results are compared with the simulation and reasons for discrepancies are identified.

Chapter 7 provides a critical evaluation of the work, along with suggestions for future work.

Due to a non-disclosure agreement (NDA) between the author and the foundry through the University of Pretoria, certain process parameters have been excluded from this thesis.

#### 1.10 CONCLUSION

This chapter provided background and motivation to the research work. The hypothesis and research questions were developed. A brief research methodology followed in the work and limitations to the research were stated. The contributions from the research were also provided and finally, the outline of the thesis was given.

### **CHAPTER 2: LITERATURE REVIEW**

#### 2.1 INTRODUCTION

This chapter details the literature study performed for the research work. It provides a background study of the SiGe semiconductor technology and the targeted system implementation, which includes the VCO. The study describes how the noise sources in the technology would manifest as phase noise of the oscillator, in turn determining the random phase error in the phase shifter system.

#### 2.2 SIGE TECHNOLOGY FOR MM-WAVE APPLICATIONS

The intrinsic device characteristics are dependent on the constituent material systems and device physics underlying a transistor's operation [4]. Table 2.1 shows the properties of several semiconductor materials that determine the preferred constituent material for the deployment of an RF transceiver system.

**Table 2.1. Electron properties of several materials [4]**

| Property                                         | Si    | Ge    | GaAs  | InP   | GaN       |

|--------------------------------------------------|-------|-------|-------|-------|-----------|

| Bandgap (eV)                                     | 1.12  | 0.66  | 1.42  | 1.35  | 3.26      |

| Lattice constant (Å)                             | 5.431 | 5.646 | 5.653 | 5.869 | 5.189     |

| Breakdown field (× 10 <sup>6</sup> V/cm)         | 0.3   | 0.1   | 0.4   | 0.5   | 2         |

| Electron mobility at 300 K (cm <sup>2</sup> /Vs) | 1450  | 3900  | 8500  | 4600  | 1000-2000 |

| Saturation velocity (× 10 <sup>6</sup> cm/s)     | 9     | -     | 6     | 9     | 25        |

| Thermal conductivity (W/cm-K)                    | 1.3   | 0.58  | 0.3   | 0.68  | 1.3       |

In Table 2.1, the semiconductor bandgap and the breakdown field determine the maximum device operating voltage of any device technology. The drift velocity and carrier mobility influence the device speed. The thermal resistance of a semiconductor substrate limits the device's power-handling capability. The lattice constant determines whether high-quality

single-crystal growth of certain materials is possible on a substrate without any introduction of strain layers. It is evident from Table 2.1 that Si has a relatively high thermal conductivity; however, the lack of a semi-insulating substrate and low mobility (resulting in a low drift velocity) stalled the development of low-cost Si-based RF systems. Historically, compound semiconductors such as GaAs, InP, etc have been deployed in RF applications because of their high mobility and the ease of preparation of semi-insulating substrates. The associated high cost has limited their success in commercial applications, and has led to an increased focus on SiGe HBTs.

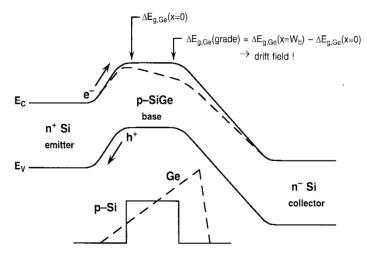

SiGe HBT is a modification over the standard silicon bipolar junction transistor (BJT), in which the bandgap energy of the base is lowered by introducing Ge atoms to its base. The graded concentration of Ge reaches its maximum in the base-collector junction, as shown in Figure 2.1.

Figure 2.1. The energy bandgap diagram of the Si/SiGe HBT [28] (© [1998] IEEE)

The lowered bandgap in the base, as seen from Figure 2.1, improves the emitter injection efficiency  $\gamma$  of the transistor, as the potential barrier for the holes injected back into the emitter is increased. The high emitter injection efficiency enables one to increase the doping concentration in the base and thus to lower the physical base resistance  $r_B$ . The graded Ge profile in the base also results in a *drift field*, which accelerates the electrons from the emitter to the collector, thus lowering the base transit time  $\tau_b$ . Hence, SiGe HBT offers higher performance transistors with high  $f_T$  given by (2.1)

$$f_T = \frac{1}{2} \left[ \frac{1}{g_m} (C_{eb} + C_{cb}) + \tau_b + \tau_e + \tau_{bc} \right]^{-1}$$

(2.1)

where  $C_{eb}$  (also known as  $C_{\pi}$ ) is the parasitic emitter-base junction capacitance,  $C_{cb}$  (or  $C_{\mu}$ ) is the parasitic collector-base junction capacitance,  $g_m$  is the device transconductance,  $\tau_b$  is the base transmit time,  $\tau_e$  is the emitter delay time and  $\tau_{bc}$  is the base-collector junction depletion layer time.

Another FOM of an active device is the maximum oscillation frequency  $f_{max}$  given by (2.2),

$$f_{\text{max}} = \sqrt{\frac{f_T}{8\pi r_h C_{ch}}} \tag{2.2}$$

where  $r_b$  is the parasitic base resistance.

Thus SiGe HBT offers bandgap engineering with the cost of fabrication and process reliability similar to that of the Si BJTs. However, SiGe HBT has poorer device ruggedness in wireless applications owing to its relatively low open-base collector-to-emitter breakdown voltage ( $BV_{CEO}$ ). This is one of the key parameters limiting the power output from oscillators, thus controlling its phase noise [29].

It has been reported that bipolar MMIC design is relatively easier and has a better chance of first-pass silicon success than CMOS design. One of the main reasons is that the bipolar model is simpler and models the physical processes in the transistor quite accurately. The layout effects of wiring parasitics, substrate contacts and proximity effects to adjacent devices have much less impact on the device performance in bipolar design than in CMOS. As device parasitics play a major role in the close matching of simulated and measured results, this also influences the choice of one technology over another for efficient circuit implementation. 60 GHz transceiver circuits implemented in SiGe technology have shown good model-to-hardware correlation [30]. Also, SiGe VCOs have better phase noise performance and a better tuning range than their MOS counterparts [31], but at the expense of higher power consumption.

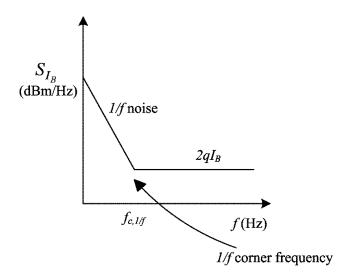

The low 1/f noise of SiGe makes it the preferred choice over MOS technology for VCO design. The reason is that 1/f noise is up-converted and shows up as the phase noise of the

oscillator (see section 2.6). The low-frequency (1/f or flicker) noise has a power spectral density inversely proportional to f as shown in Figure 2.2.

Figure 2.2. A typical low-noise frequency spectrum of SiGe HBTs [20] (Reproduced by permission from J. Rogers and C. Plett, *Radio Frequency Integrated Circuit Design*, Norwood, MA: Artech House, Inc., 2003. © 2003 by Artech House, Inc.)

As shown in Figure 2.2, a typical low-frequency noise spectrum of the base current has an 1/f component which intercepts the  $2qI_B$  shot noise level at the 1/f corner frequency given by  $f_{c,1/f}$ . The polysilicon-to-crystal silicon interfacial oxide and the oxide spacers around the emitter perimeter are responsible for 1/f noise in SiGe HBTs [32].

In general,  $S_{I_R}$  is related to the DC component of the base current,  $I_B$  by

$$S_{I_B} = K_F \frac{I_B^{\alpha}}{f} \tag{2.3}$$

where  $K_F$  and  $\alpha$  correspond to the flicker noise coefficient (KF) and flicker noise exponent (AF) model parameters in SPICE. The value of  $\alpha$  is close to 2 for typical SiGe HBTs.

For a certain value of the collector current,  $S_{I_B}$  is lower in SiGe HBTs than in Si BJTs. This is because of the lower base current due to higher  $\beta$ . The 1/f noise factor  $K_F$  is

inversely proportional to the emitter area  $A_E$  and thus substituting for the base current in (2.3) gives (2.4)

$$S_{I_B} = \frac{K}{A_E} \frac{I_B^2}{f} = \frac{K}{\beta^2} \frac{1}{A_E} \frac{I_C^2}{f}$$

(2.4)

Hence, a higher  $\beta$  and a larger device reduce  $S_{I_B}$ , but this reduces the  $f_T$  of the device owing to lower collector current density  $J_C$ . The 1/f corner frequency is obtained by equating the two noise spectral densities as shown

$$\frac{K}{A_E} \frac{I_B^2}{f_{c, 1/f}} = 2qI_B \tag{2.5}$$

$$f_{c, \gamma_f} = \frac{KI_B}{2qA_E} = \frac{KJ_C}{2q\beta}$$

(2.6)

The 1/f noise factor K is seen to increase with technology scaling, but this is usually offset by the increase in  $\beta$  due to scaling. However, the phase noise corner frequency in an oscillator is seen to be much lower than the 1/f noise corner frequency given by  $f_{c,1/f}$  (see section 2.6.2)

The added advantage of integrating SiGe and CMOS technology into BiCMOS processes is that it helps in the development of system-on-chip mm-wave systems where analogue, RF and digital circuitry can reside on a single chip. In the IBM 8HP process, SiGe HBTs with  $f_T = 200$  GHz have been integrated into a 130 nm BiCMOS technology while fully retaining the field effect transistor (FET) device and interconnect properties of IBM's standard 130 nm CMOS technology.

The quality of the passive devices is also important in high-frequency designs. Though the III-V materials have low-loss dielectric properties, the RF-enhanced processes offer Si passives whose Q-factor is approaching that of III-Vs [3]. The Q of the inductors in the mm-wave range is much higher compared to the varactors [31], and this holds true for the IBM 8HP process as well.

#### 2.3 INTEGRATED PHASED-ARRAY IMPLEMENTATIONS

Phased-array implementations have been demonstrated in SiGe [5] [6] [7] [8] [9] [17] and CMOS [33] [34]. A phased-array receiver with an LO-path-based approach is implemented in [9] and [33], while the phased-array transmitter implementation in Q-band [17] has the phase shift implemented in the RF path. Reported simulations in [17] show that an on-chip phased array with 0-360° phase shifters can drive  $4 \times 4$  elements with virtually no penalty for a system with up to 10% bandwidth.

The integral module in any phased-array implementation is the phase shifter circuitry, which is incorporated in the RF path for an RF-based approach, or after the VCO in the LO path-based approach.

#### 2.4 PHASE SHIFTERS

The phase shifters could be implemented using passive elements, as by using a quadrature coupler with a C-L-C load as in a reflection-type phase shifter [14] or by using vector-interpolation scheme. As discussed earlier, the disadvantage with the passive phase shifters is the high insertion loss. The phase shifters for the LO path shifting architecture in [8] have been implemented using phase rotators, where a  $\lambda/4$  t-line has been used to generate a quadrature LO signal which is then provided to an analog phase rotator. The quadrature signal for vector-interpolation could also be obtained using a quadrature all-pass filter, and an I/Q phase error of less than 5° is reported at 30-46.5 GHz band [17].

#### 2.5 MULTIPLE-PHASE VCO

The LO-path phase-shifting architecture for phased arrays requires multiple phases of the LO signal. This can be obtained by using a VCO and a phase shifter circuitry to implement the vector-sum method [8].

The resolution of an LO path-based phase shifting transmitter system depends on the resolution of the interpolator weights generated by the DACs and the phase-noise of the LO signal, which translates to jitter in the beam direction [8]. As the output is obtained by

interpolating the in-phase and quadrature-phase (delayed version) signals, the rms jitter in the phase setting is given in radians by (2.7)

$$\left\langle \theta^{2}(t)\right\rangle = 2\int_{f_{\min}}^{\infty} 10^{L(f)/10} df$$

(2.7)

where L(f) is the phase noise of the oscillator in dBc/Hz.

It was noted that the resolution of the phase-shift is not the same as that of the DAC weights. There would be an error in some phase settings if a phase shift from 0° to 360° is generated with a step size of  $360^{\circ}/_{2n+1}$  using a *n*-bit DAC.

#### 2.6 PHASE NOISE IN OSCILLATORS

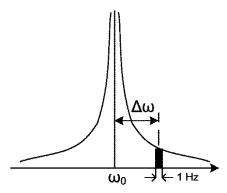

Phase noise in oscillators is given by (2.8),

$$L_{total}\{\Delta\omega\} = 10.\log\left[\frac{P_{sideband}(\omega_0 + \Delta\omega, 1 \text{ Hz})}{P_{carrier}}\right]$$

(2.8)

where  $P_{sideband}(\omega_0 + \Delta\omega, 1\,\text{Hz})$  represents the single sideband power at a frequency offset  $\Delta\omega$  from the carrier in a measurement bandwidth of 1 Hz and  $P_{carrier}$  is the total power under the spectrum in Figure 2.3.

Figure 2.3. The phase noise per unit bandwidth at offset  $\Delta \omega$

The phase noise is an undesirable feature in any communication system, as it leads to "reciprocal mixing" and thus a significant degradation of the wanted signal [35]. This also affects the channel spacing, especially in narrow band systems.

The increasing demand for bandwidth thus places a stringent requirement on the phase noise of the oscillators, and low phase noise oscillators have become a requirement for attaining good communication system characteristics. Also, the phase noise of the LO signal is a critical performance measure of the VCO in an LO-path phase-shifting transmitter architecture, as it translates to jitter of the beam [8]. These requirements emphasise the need to model phase noise accurately.

The noise in the circuit undergoes various frequency translations before ultimately contributing to the phase noise. These translations, caused by non-linearities in the oscillator, should be properly modelled to optimise the circuit performance. The pioneering work on modelling the phase noise was done by Leeson in 1966 and was based on a linear time-invariant (LTI) approach [36]. Though the LTI approach was successful in providing qualitative design insights, it failed to predict the phase noise quantitatively. In 1998, Hajmiri and Lee described oscillators as an LTV system, which could be characterised by an ISF [37]. The two approaches to phase noise modelling are discussed in the following subsections.

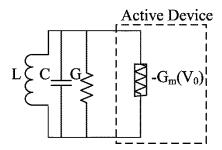

#### 2.6.1 Leeson's LTI approach

Leeson's model was the first one to provide an approximation for the phase noise of an oscillator. In an ideal oscillator the only noise source is the loss of the tank G, as shown in Figure 2.4.

Figure 2.4. The one-port model of an LC oscillator

The average thermal current noise spectral density of a resistor with conductance G is given by (2.9),

$$\frac{\overline{i_n^2}}{\Delta f} = 4kTG \tag{2.9}$$

where k is the Boltzmann's constant  $(8.617 \times 10^{-5} \text{ eV/K})$  and T is the absolute temperature in K.

The spectral density of the mean-square voltage is obtained by multiplying the current noise spectral density by the square of impedance of the tank.

$$\frac{\overline{v_n^2}}{\Delta f} = \frac{\overline{i_n^2}}{\Delta f} \bullet |Z|^2 \tag{2.10}$$

For a relatively small offset frequency ( $\Delta\omega$ ) from the centre frequency  $\omega_0$ , the impedance of the tank Z can be approximated by (2.11).

$$Z(\omega_0 + \Delta\omega) \approx \frac{j.\omega_0 L}{2\frac{\Delta\omega}{\omega_0}}$$

(2.11)

Substituting for L from the expression of loaded quality tank factor Q in the equation for Z, as in (2.12)

$$Q = \frac{R}{\omega_0 L} = \frac{1}{\omega_0 GL} \tag{2.12}$$

$$Z(\omega_0 + \Delta\omega) \approx \frac{1}{G} \bullet \frac{\omega_0}{2Q\Delta\omega}$$

(2.13)

Thus the mean-square noise voltage spectral density is given by (2.14):

$$\frac{\overline{v_n^2}}{\Delta f} = \frac{\overline{i_n^2}}{\Delta f} \bullet |Z|^2 = 4kTR \left(\frac{\omega_0}{2Q\Delta\omega}\right)^2$$

(2.14)

Thus the power spectral density of the output noise varies as  $^1/_{f^2}$  at an offset frequency  $\Delta f$  from the centre frequency and contains the combined effect of both amplitude and phase variations. The equipartition theorem of thermodynamics states that, in equilibrium, the amplitude and phase-noise power are equal. The inherent amplitude-limiting mechanism present in an oscillator limits the amplitude noise and hence the phase noise will be half of that given in (2.14)

Phase-noise, defined as the ratio of noise spectral density to the carrier power  $P_{sig}$ , will thus be given by (2.15):

$$L\{\Delta\omega\} = 10 \bullet \log \left[ \frac{2kT}{P_{sig}} \bullet \left( \frac{\omega_0}{2Q\Delta\omega} \right)^2 \right]$$

(2.15)

It is evident from the equation that increasing the signal power and Q of the tank improves the phase noise of the system. It also seems logical, as increasing the signal power improves the ratio as thermal noise is fixed and increasing Q improves the ratio quadratically as tank impedance falls off as  $I/Q\Delta\omega$ . However, in a practical oscillator there are additional noise sources to be accounted for, namely the noise sources from the active devices that form the energy-restorer element [38]. The modified model known as the Leeson-Cutler phase noise model includes the noise from the active devices as well and is given by (2.16).

$$L(\Delta\omega) = 10 \bullet \log \left\{ \frac{2FkT}{P_{sig}} \left[ 1 + \left( \frac{\omega_0}{2Q\Delta\omega} \right)^2 \right] \bullet \left[ 1 + \frac{\Delta\omega_{1/f^3}}{\Delta\omega} \right] \right\}$$

(2.16)

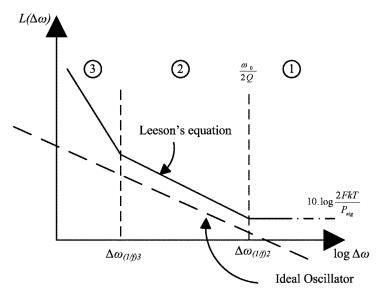

The features of (2.16) are that it has an additive factor F, which is an empirical fitting parameter to account for the increased noise in the  $^1/_{(\Delta\omega)^2}$  region, an additive factor of unity with the term  $\left(\frac{\omega_0}{2Q\Delta Q}\right)^2$ , to account for the noise floor, and a multiplicative factor (the term in the second set of brackets) to provide  $^1/_{(\Delta\omega)^3}$  behaviour at sufficiently small offset frequencies. The phase noise could be plotted as in Figure 2.5.

Figure 2.5. Oscillator phase noise spectrum [29](© [2000] IEEE)

In Figure 2.5, region 1 is the thermal noise floor that arises because of both active devices as well as the resistive loss of the RLC tank and is given by (2.17).

$$L(\Delta\omega) = 10.\log\frac{2FkT}{P_{sip}}$$

(2.17)

Region 2 has the -20 dB/decade slope described by the original Leeson's equation for an ideal oscillator; however, the value is shifted up because of the factor F. This then flattens off into Region 1 around the resonator 3 dB bandwidth given by  ${}^{\omega_0}/_{2Q}$ . Region 3 begins at a corner frequency  $\Delta\omega_{(1/f)^3}$  and is dependent on the  ${}^{1}/_{f}$  noise corner of the device.

The inadequacy of Leeson's model was that though it was successful in predicting the dependence of the tank Q and signal power on phase noise performance, there was no indication of the factors on which F was dependent. Thus good oscillator designs could not be developed, as designers could not control the factor F. The inability to predict the phase noise quantitatively has necessitated revision of the assumptions made in the derivation.

#### 2.6.2 Hajmiri and Lee's LTV approach

The concept of linearity and the time-invariance of oscillators in Leeson's model were reexamined by Hajmiri and Lee [39]. They demonstrated that oscillators are time-varying systems [29], though linearity appeared to be a reasonable assumption as far as the noiseto-phase transfer function is concerned.

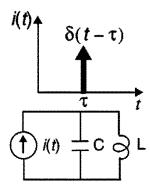

To prove that oscillators are fundamentally time-varying systems, they considered an impulse at the input of a lossless LC tank oscillating with constant amplitude until the instance of the impulse, as in Figure 2.6.

Figure 2.6. LC oscillator excited by current pulse [29](© [2000] IEEE)

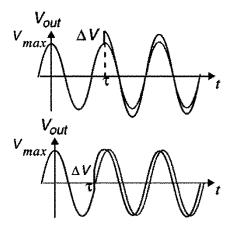

They analysed the system's response to an impulse occurring at two different time instances. Each noise source may cause both amplitude and phase variations as in Figure 2.7.

Figure 2.7. Impulse response of LC tank [29](© [2000] IEEE)

According to Figure 2.7, it was observed that if the impulse coincides with the maximum of the voltage, the amplitude increases abruptly, but the phase superimposes with the pre-existing oscillation and thus the timing of the zero crossings does not change. An impulse occurring at any other instance is seen to cause a change in both amplitude and zero crossings in the oscillations. Therefore, an oscillator is basically an LTV system with periodicity.

The impulse response for the phase is a function of two arguments, the observation time t and the excitation time  $\tau$ , and can be written as in (2.18):

$$h_{\phi}(t,\tau) = \frac{\Gamma(\omega_0 \tau)}{q_{\text{max}}} u(t-\tau)$$

(2.18)

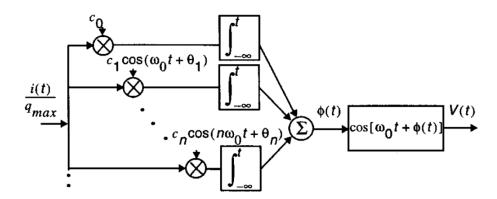

$\Gamma(x)$  is called the ISF and is a dimensionless, frequency-and amplitude-independent function periodic in  $2\pi$  that describes the amount of phase shift from applying a unit impulse at any point in time. The shape of the ISF depends on the oscillator waveform. Once the ISF of an oscillator has been determined through simulation or analytical methods, the excess phase may be determined using the superposition integral (2.19):

$$\phi(t) = \int_{-\infty}^{+\infty} h_{\phi}(t,\tau)i(\tau)d\tau = \frac{1}{q_{\text{max}}} \int_{-\infty}^{t} \Gamma(\omega_0 \tau)i(\tau)d\tau$$

(2.19)

ISF is a periodic function with a period related to the oscillator frequency and hence can be expressed as a Fourier series (2.20),

$$\Gamma(\omega_0 \tau) = \frac{c_0}{2} + \sum_{n=1}^{\infty} c_n \bullet \cos(n\omega_0 \tau + \phi_n)$$

(2.20)

where coefficient  $c_n$  is real and  $\phi_n$  is the  $n^{\text{th}}$  harmonic phase.  $\phi_n$  could be ignored if the noise sources are uncorrelated, hence their relative phase is insignificant.

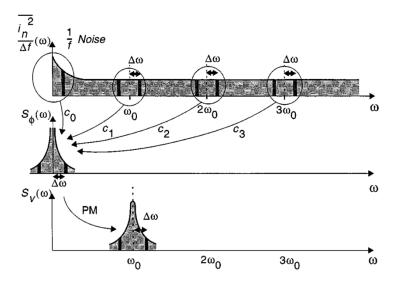

Substituting the Fourier expansion into the integral (2.19), the excess phase is given by (2.21) and shown graphically in Figure 2.8.

$$\phi(t) = \frac{1}{q_{\text{max}}} \left[ \frac{c_0}{2} \int_{-\infty}^{t} i(\tau) d\tau + \sum_{n=1}^{\infty} c_n \int_{-\infty}^{t} i(\tau) \cos(n\omega_0 \tau) d\tau \right]$$

(2.21)

Figure 2.8. Equivalent system for ISF decomposition [29](© [2000] IEEE)

This system in Figure 2.8 is analogous to a superheterodyne receiver, where the normalised noise current, which can be considered as a "broadband RF signal", is undergoing down-conversions by "local-oscillator signals" at all harmonics of the oscillating frequency.

If a sinusoidal current i(t) as in (2.22), whose frequency is near an integer multiple m of the oscillation frequency, is injected into the system,

$$i(t) = I_m \cos[(m\omega_0 + \Delta\omega)t]$$

(2.22)

where  $\Delta \omega \ll \omega_0$ .

Substituting in (2.21) and noting that there is a negligible component from the terms other than n=m, one obtains the following approximation (2.23):

$$\phi(t) \approx \frac{I_m c_m \sin(\Delta \omega t)}{2q_{\text{max}} \Delta \omega}$$

(2.23)

Therefore, the spectrum of  $\phi(t)$  contains two sidebands at  $\pm \Delta \omega$ , even though the injection occurs near some integer multiple of  $\omega_0$ , as seen in Figure 2.9.

Figure 2.9. Evolution of circuit noise into phase noise [29](© [2000] IEEE)

As seen in Figure 2.9, the spectrum of the output voltage of the oscillator could be evaluated from the phase spectrum by considering the output sinusoid, given by (2.24),

$$v_{out}(t) = \cos[\omega_0 t + \phi(t)] \approx \cos(\omega_0 t) - \phi(t)\sin(\omega_0 t)$$

(2.24)

where it is assumed that  $\cos(\phi(t)) \approx 1$  and  $\sin(\phi(t)) \approx \phi(t)$  for small values of  $\phi(t)$ . Using this narrowband tone modulation approximation, an injected current at  $m\omega_0 + \Delta\omega$  is seen to result in a pair of equal sidebands at  $\omega_0 + \Delta\omega$ , with single sideband carrier power given by (2.25):

$$P_{SBC}(\Delta\omega) \approx 10 \bullet \log \left(\frac{I_m c_m}{4q_{\text{max}} \Delta\omega}\right)^2$$

(2.25)

It may be extended to the general case of a white noise source:

$$P_{SBC}(\Delta\omega) \approx 10 \bullet \log \left( \frac{\overline{i_n^2}}{\frac{\Delta f}{4q^2 \Delta \omega^2}} \sum_{m=0}^{\infty} c_m^2 \right)$$

(2.26)

From (2.26), it is implied that noise components near the integer multiple of  $\omega_0$  fold into noise near the carrier itself, as shown in Figure 2.9; thus  $^1/_f$  noise of the device becomes  $^1/_{f^3}$  noise near  $\omega_0$  and white noise near the higher integer multiple of  $\omega_0$  undergoes down-conversion into the noise in the  $^1/_{f^2}$  region. It can be understood from the expressions that minimising the various coefficients of ISF  $(c_m)$  will minimise the phase noise of the system.

Using Parseval's theorem (2.27),

$$\sum_{n=0}^{\infty} c_n^2 = \frac{1}{\Pi} \int_{0}^{2\Pi} |\Gamma(x)|^2 dx = 2\Gamma_{rms}^2$$

(2.27)

the spectrum in the  $\frac{1}{f^2}$  region can be expressed as in (2.28),

$$L(\Delta\omega) = 10 \bullet \log \left( \frac{\frac{\overline{i_n^2}}{\Delta f} \Gamma_{rms}^2}{2q_{\max}^2 \Delta\omega^2} \right)$$

(2.28)

where  $\Gamma_{rms}$  is the rms value of the ISF.

The spectrum in the  $\frac{1}{f^3}$  region can be evaluated by assuming that the current noise behaves as in (2.29) in the  $\frac{1}{f}$  region.

$$i_{n, \frac{1}{f}}^{2} = i_{n}^{2} \bullet \frac{\omega_{\frac{1}{f}}}{\Delta \omega}$$

(2.29)

where  $\omega_{1/f}$  is the corner frequency.

Using (2.28), the spectrum in the  $\frac{1}{f^3}$  region can be written as in (2.30):

$$L(\Delta\omega) = 10 \bullet \log \left( \frac{\frac{\overline{i_n^2}}{\Delta f} c_0^2}{8q_{\text{max}}^2 \Delta\omega^2} \bullet \frac{\omega_{\frac{1}{f}}}{\Delta\omega} \right)$$

(2.30)

The  $^{1}/_{f^{3}}$  corner frequency is then given by (2.31)

$$\Delta \omega_{1/f^3} = \omega_{1/f} \bullet \left(\frac{\Gamma_{dc}}{\Gamma_{rms}}\right)^2 \tag{2.31}$$

Thus the phase noise theory explains why the  $^1/_{f^3}$  noise corner frequency is lower than the  $^1/_f$  noise corner frequency and also demonstrates that it could be controlled by  $\Gamma_{dc}$  and  $\Gamma_{rms}$  of the ISF. The ISF is determined by the oscillator waveform's shape whose rise-time and fall-time symmetry can be controlled by the designer.

In addition to the phase noise improvement techniques derived from the LTI model, namely improving the tank Q and signal power, the LTV model suggests that the phase noise contribution from active devices, which act as the energy-restorer, should be minimised. From the ISF theory, it is quite obvious that there are sensitive and in-sensitive instances in an oscillation cycle. Hence the transistor (active element) should deliver the energy *all at once* to the LC tank, i.e. the transistor would remain off almost all the time and wake up periodically to deliver the current impulse at the signal's peak in each cycle. The oscillators should also be designed to possess symmetry properties (rise-time and fall-time) so as to reduce  $\Gamma_{dc}$  for minimum up-conversion of 1/f noise.

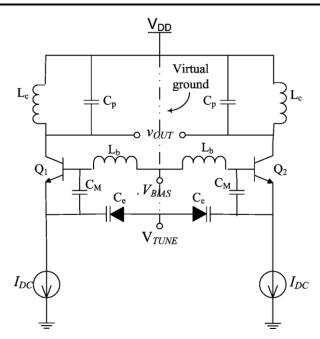

#### 2.7 DESIGN OF VCO CORE

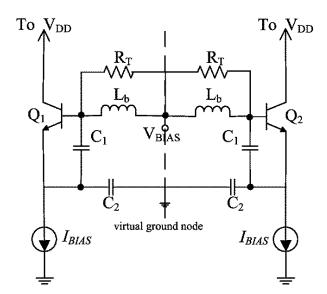

In the mm-wave range, LC oscillators are preferred to ring oscillators because of better phase-noise performance [39]. The most popular VCO topology in the mm-wave region is the differential Colpitts oscillator [25] [40], as shown in Figure 2.10. A differential configuration is preferred, especially at high frequencies, to minimise the generation and coupling of high-frequency signals. It also has the advantage of less criticality to on- and off-chip decoupling of supply and bias voltages due to the virtual ground node [41]. The differential architecture also minimises the substrate noise and power supply variation effects by rejecting common mode noise. The physical design process is also made simpler because of the virtual grounds in differential circuits.

Figure 2.10. Differential Colpitts oscillator topology [20] (Reproduced by permission from J. Rogers and C. Plett, *Radio Frequency Integrated Circuit Design*, Norwood, MA: Artech House, Inc., 2003. © 2003 by Artech House, Inc.)

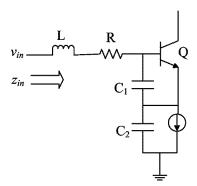

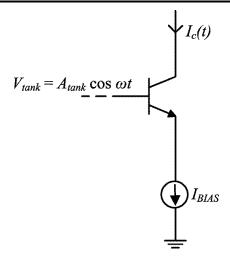

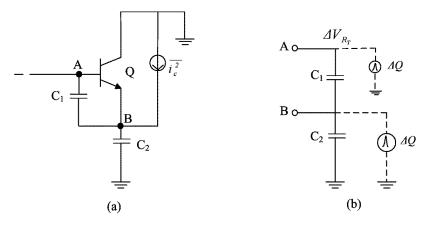

The impedance between the base of transistor  $Q_1$  in Figure 2.10 and the virtual ground shows a capacitive reactance, which resonates when an inductor  $(L_b)$  is connected across it. This could be seen from the analysis of the basic Colpitts oscillator core, as in Figure 2.11.

Figure 2.11. Oscillator core analysis

$$z_{in} = j\omega L + R + \frac{1}{j\omega C_1} + \frac{1}{j\omega C_2} - \frac{g_m}{\omega^2 C_1 C_2}$$

(2.32)

Therefore, the condition for oscillations is given by

$$\frac{g_m}{\omega^2 C_1 C_2} > R_B \tag{2.33}$$

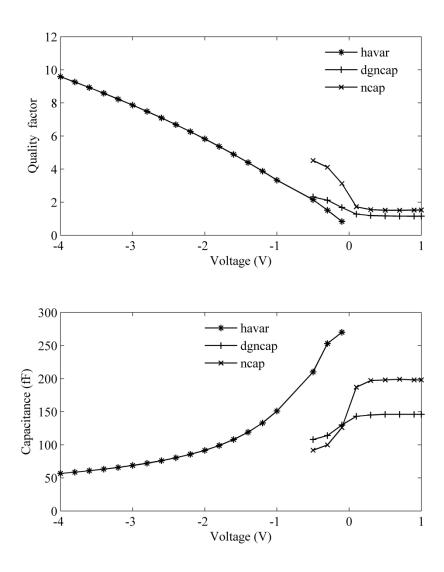

The varactor ( $C_e$ ) in Figure 2.10, which forms  $C_2$  in Figure 2.11, helps in tuning the VCO, using the bias voltage  $V_{TUNE}$ . The B-E capacitance of the transistor usually forms  $C_I$  and an additional capacitance in parallel could be placed if required by the design. The VCO core should be followed by a buffer for decoupling the load from the core [42], and a cascode buffer would be advantageous in terms of lower power consumption.

#### 2.7.1 Design considerations

In this section, the design considerations identified in the literature study undertaken for a high-performance VCO are discussed.

As phase noise decreases with the quality factor, a high Q LC tank is the primary requirement for a low-noise design. In the mm-wave frequency range, the Q of the tank is limited by the varactor Q, unlike in the case of low-frequency designs where the tank Q is dominated by the inductor Q [43]. This is because high quality inductors with superior isolation could be realised using transmission lines in the mm-wave range. This was true for the IBM 130 nm process, where high Q inductors were realised using microstrip lines but varactor Q was just around 6 (see Chapter 5).

Varactors available in the process need to be carefully studied to know their suitability for the design. It has been demonstrated that minimum gate width (to reduce gate resistance) and minimum gate length (to reduce channel resistance) for MOS varactors and minimum anode size for junction varactors are required to attain a high Q. It has also been observed that increasing the varactor size tends to increase the total Q of the tank, though not that of the varactor Q [40].

The VCO core consists of the LC tank and a negative resistance applied as feedback to compensate for the losses in the LC tank. A tapped capacitor and an amplifier form the feedback in a Colpitts oscillator. A summary of the design methodology followed in VCO design in the literature is given on the next page.

i. The voltage swing across the tank is set to the maximum allowed for the safe operation area of the transistor and the smallest inductor size is chosen for the tank (for low phase noise)

- ii. The transistors are biased at optimum noise current density [44]. (In the W-band, optimum noise current density is seen to shift towards the peak  $f_T$  current density because of the correlation between base and collector noise currents [40])

- iii. The transistor and the varactor size, and the capacitance ratio  $C_1$ :  $C_2$ , should be scaled for minimum phase noise.

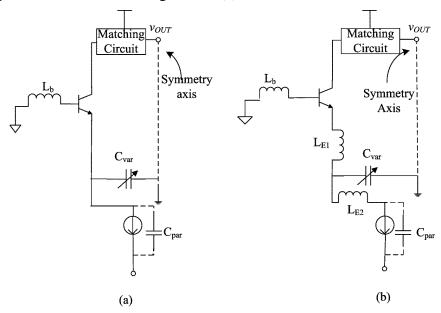

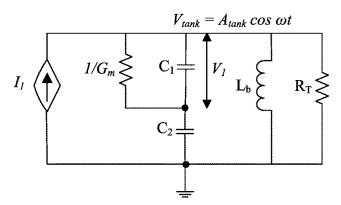

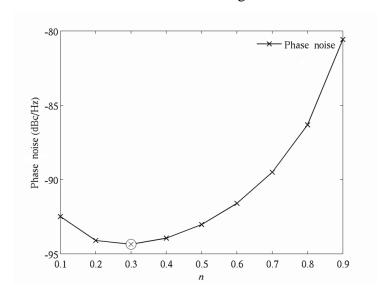

The normal VCO topology has low phase noise performance and a narrow tuning range due to parasitics interfering with the core. The high-frequency noise generated by the current source adds to the noise of the VCO core. The tuning range is also reduced, because of the parasitic capacitance  $C_{par}$  of the output current source, which shunts the varactor capacitance, as shown in Figure 2.12(a).

Figure 2.12. (a) Normal VCO topology showing the current source parasitic and (b) LC filtering technique to improve phase noise and tuning range [22] (© [2003] IEEE)

To improve the phase noise performance of the VCO, an LC filtering technique [22] could be used. The LC filtering technique using inductors at the emitter, as shown in Figure 2.12(a), can improve the phase noise performance and tuning range of the VCO.  $L_{E2}$  forms

a low-pass LC filter and thus helps in decoupling the high-frequency noise generated by the current source from the core of the oscillator. It also prevents  $C_{par}$  from shunting the varactor capacitance.  $L_{EI}$  is said to increase the loaded quality factor of the tank and thus improves the phase noise. A VCO with the LC filtering technique is seen to demonstrate a relatively high FOM [22]. An output buffer added to decouple the oscillator core from the external load is also reported to demonstrate better phase noise performance [45]. It also helps in obtaining large output power. HBT cascode, common source amplifier and MOS-HBT cascade are the possible options for the implementation of a buffer [40].

#### 2.8 IMPLEMENTATION OF VECTOR-SUM INTERPOLATOR

The vector-sum interpolator requires I and Q signals to be interpolated to generate the necessary phase shift. The quadrature generation could be performed using passive devices to reduce power consumption and the interpolation could be performed with active devices.

The quadrature signal for the vector sum phase-shifting method could be generated from the VCO output. The I/Q phase accuracy of the generated quadrature phase signal is important, though the amplitude variations could be adjusted with the gain of the VGAs following the phase shifters.

#### 2.8.1 Lange couplers

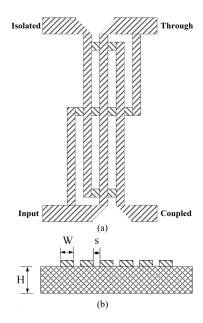

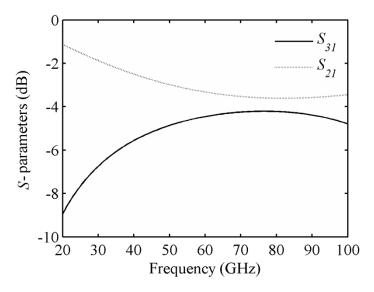

Lange couplers as shown in Figure 2.13 are passive devices that could be used for quadrature signal generation [46]. They are popular in the mm-wave region because of their low insertion loss. A D-band Lange coupler in a 0.13  $\mu$ m SiGe BiCMOS technology is reported to have an insertion loss of 0.7 dB at the centre frequency of 140 GHz [47]. A Lange coupler implemented in the IBM 0.13  $\mu$ m SiGe process using the top thick AM layer has a 42  $\Omega$  characteristic impedance and an insertion loss of 1.8 dB [14].

The design parameters of a Lange coupler, are the voltage coupling coefficient (c) and the even and odd mode characteristic impedances ( $Z_{o,even}$  and  $Z_{o,odd}$ ).

$$Z_{0,even} = Z_0 \sqrt{\frac{(1+c)}{(1-c)}}$$

(2.34)

$$Z_{0,odd} = Z_0 \sqrt{\frac{(1-c)}{(1+c)}}$$

(2.35)

Figure 2.13. (a) Lange coupler (b) Cross-section of Lange coupler [48] ( $\bigcirc$  [2009] IEEE)

As observed in Figure 2.13, the Lange coupler consists of four interconnected metal lines. There is a  $90^{\circ}$  phase difference between the through and coupled ports, and hence it is a quadrature hybrid [46].

#### 2.8.2 Design of VGA

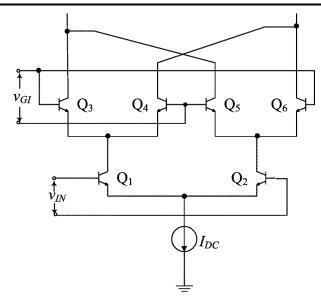

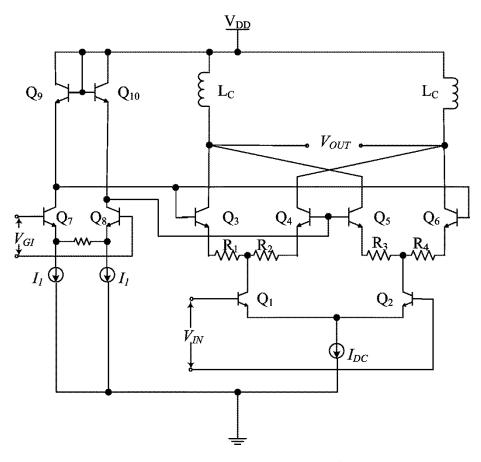

The vector interpolation requires a VGA to interpolate the I and Q signals. A VGA could be implemented using a Gilbert mixer topology as in Figure 2.14 [20]. The gain control voltage is applied to transistors  $Q_{3-6}$  to steer the currents in the branches, which are then passed through the loads to provide an output voltage.

**Figure 2.14. Variable gain amplifier** [20] (Reproduced by permission from J. Rogers and C. Plett, *Radio Frequency Integrated Circuit Design*, Norwood, MA: Artech House, Inc., 2003. © 2003 by Artech House, Inc.)

The currents  $i_3$ ,  $i_4$ ,  $i_5$ ,  $i_6$  in transistors  $Q_3$ ,  $Q_4$ ,  $Q_5$ ,  $Q_6$  respectively in Figure 2.14 are given by (2.36)

$$i_{3} = \frac{i_{1}}{-v_{GI}/v_{T}}$$

$$1 + e^{\frac{i_{1}}{v_{GI}/v_{T}}}$$

$$i_{4} = \frac{i_{1}}{\frac{v_{GI}/v_{T}}{1 + e^{\frac{i_{2}}{v_{T}}}}}$$

$$i_{5} = \frac{i_{2}}{\frac{v_{GI}/v_{T}}{1 + e^{\frac{i_{2}}{v_{T}}}}}$$

$$1 + e^{\frac{i_{2}}{v_{T}}}$$

Assuming symmetrical collector resistors  $R_C$ , the output voltage is given by (2.37)

$$v_o = (i_1 - i_2)R_C = ((i_3 + i_4) - (i_5 + i_6))R_C = -2R_C I_{DC} \tanh\left(\frac{V_{GI}}{2v_T}\right) \tanh\left(\frac{v_{IN}}{2v_T}\right)$$

(2.37)

#### 2.9 MILLIMETRE-WAVE DESIGN CHALLENGES

In the mm-wave range, the chip dimensions are in the order of the wavelength, hence MMIC designers need to account for distributed effects in the interconnects. The approach has been that the individual blocks, such as amplifiers, mixers, oscillators etc, are designed as lumped circuits and are interconnected to one other using transmission lines, which have a distributed nature. This traditional approach is said to give way to a new class of holistic circuit design technique combining device physics, circuits, and electromagnetics [11]. However, The author of this thesis feels that the modular approach helps to analyse and efficiently design the individual circuit blocks that can be employed in a wide range of applications. Hence, the traditional approach will be followed in this thesis, thus optimising the VCO design and its associated phase shifter circuitry, which could be incorporated as a module in phased-array systems.

The challenges faced in such a modular design approach are discussed in the following subsections.

#### 2.9.1 Substrate effects