# THE DESIGN OF AN ELECTRO-OPTIC CONTROL INTERFACE FOR PHOTONIC PACKET SWITCHING APPLICATIONS WITH CONTENTION RESOLUTION CAPABILITIES

by

# Jacobus Stefanus van der Merwe

Submitted in partial fulfilment of the requirements for the degree

Master of Engineering (Electronic Engineering)

in the

Faculty of Engineering, Built Environment and Information Technology

UNIVERSITY OF PRETORIA

October 2006

#### **SUMMARY**

# THE DESIGN OF AN ELECTRO-OPTIC CONTROL INTERFACE FOR PHOTONIC PACKET SWITCHING APPLICATIONS WITH CONTENTION RESOLUTION CAPABILITIES

By: Jacobus Stefanus van der Merwe Supervisor: Ms R. Geldenhuys

Department of Electrical, Electronic and Computer Engineering, University of Pretoria

Degree: M. Eng. (Electronic Engineering)

Keywords: Contention Resolution, Complex Programmable Logic Device, Electronic Header Processing, Optical Cross-point Switch, Optical Switch, Photonic Packet Switching, Recirculating Buffer, Transparency, Variable Length Packets and Vertical Active Coupler.

The objective of the research is to design an electro-optic control for the Active Vertical Coupler-based Optical Cross-point Switch (OXS). The electronic control should be implemented on Printed Circuit Board (PCB) and therefore the design will include the PCB design as well. The aim of the electronic control board is to process the headers of the packets prior to entering the OXS to be switched and from the information in the headers, determine the state that the OXS should be configured in. It should then configure the optical cross-point accordingly. The electronic control board should show flexibility in the sense that it can handle different types of traffic and resolve possible contention that may occur.

The research seeks to understand the problems associated with Photonic Packet Switching (PPS) networks. Two of the main problems identified in a PPS network are contention resolution and the lack of variable delays for storing optical packets. The OXS was analyzed and found to meet the requirements for future ultra-high speed PPS network technology with its high extinction ratio, wide optical bandwidth, ultra-fast switching speed and low crosstalk levels.

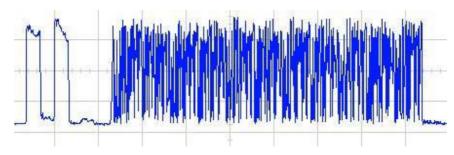

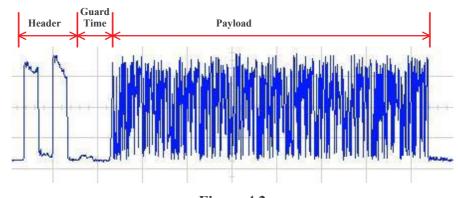

Photonic packets were generated with 4-bit, 8-bit or 16-bit headers at a bit rate of 155 Mbit/s followed by a PRBS (Pseudo Random Bit Sequence) payload at 10 Gbit/s. Different scenarios were created with these types of packets and the electro-optic control and OXS were subjected

to these scenarios with the aim of testing the flexibility of the electro-optic control to control the OXS. These scenarios include:

- Fixed length packets arriving synchronously at one input of the OXS. Some packets are destined for output 1, some are destined for output 2 and some are destined for output 3, therefore realizing a 1-to-3 optical switch.

- Eight variable length packets arriving synchronously at the OXS at one input, all of them destined for one output. The electro-optic control should open the switch cell for the correct amount of time

- Three variable length packets arriving synchronously and asynchronously at one input of the OXS. Some packets are destined for output 1 while other packets are destined for output 2. The electro-optic control should open the correct switch cell for the correct amount of time.

- Two fixed length packets arriving at the OXS synchronously on different input ports at

the same time, both destined for the same output port. The electro-optic control should

detect the contention and switch the packets in such a way as to resolve the contention.

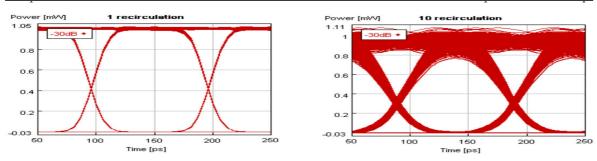

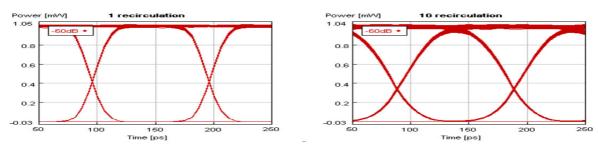

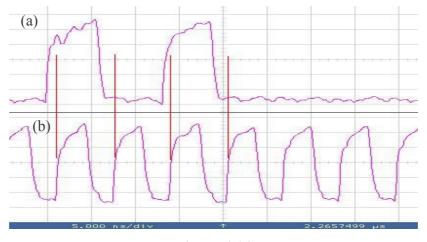

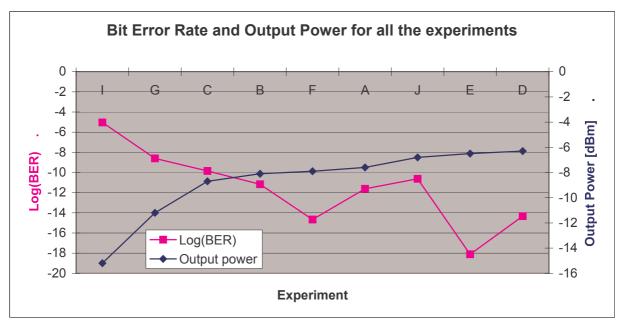

The electro-optic control and OXS managed to switch all these types of data traffic (scenarios) successfully and resolve the contention with an optical delay buffer. The success of the results was measured in two ways. Firstly it was deemed successful if the expected output sequence was measured at the corresponding output ports. Secondly it was successful if the degradation in quality of the packet was not drastic, meaning the output packets should have an BER (Bit Error Rate) of less than 10<sup>-9</sup>. The quality of the packets was measured in the form of eye diagrams before and after the switching and then compared.

The research resulted in the design and implementation of a flexible electro-optic control for the OXS. The problem of contention was resolved for fixed length synchronous packets and a proposal is discussed to store packets for variable lengths of time by using the OXS. This electro-optic control has the potential to control the OXS for traffic with higher complexities and make the OXS compatible with future developments.

#### **SAMEVATTING**

# DIE ONTWERP VAN 'n ELEKTRO-OPTIESE BEHEERSTELSEL VIR FOTONIESEPAKKIE-SKAKELINGDOELEINDES MET KONTENSIE-OPLOSSINGSVERMOË

Deur: Jacobus Stefanus van der Merwe

Studieleier: Me R. Geldenhuys

Departement Elektriese, Elektroniese en Rekenaar-ingenieurswese, Universiteit van Pretoria Graad: M.Ing. (Elektroniese Ingenieurswese)

Sleutelwoorde: Deursigtigheid, Elektroniese Hoofprosessering, Hersirkulerende Buffer, Kontensie-oplossing, Komplekse Programmeerbare Logiese Toestel, Optiesekruispuntskakelaar, Optiese Skakelaar, Fotoniesepakkie-skakeling, Verskeielengte-pakkies, Vertikale Aktiewe Koppelaar

Die doel van die navorsing is om 'n elektro-optiese beheerstelsel te ontwerp vir die aktiewe vetikale koppelaar-gebaseerde Optiese-Kruispunt-Skakelaar (OKS). The elektro-optiese beheer moet op 'n stroombaanbord gebou word en dus sluit die ontwerp ook dié van 'n stroombaanbord in. Die doel van die elektro-optiese beheer is om die hoofde van die pakkies te prosesseer net voordat hulle in die OKS ingaan om geskakel te word, sodat die staat waarin die OKS gestel moet word, bepaal kan word. Die elektro-optiese beheer moet dan die OKS soos volg skakel: die elektroniese beheer moet buigsaamheid toon in die sin dat dit verskeie tipes verkeer kan hanteer en ook kontensie oplos wat mag opduik.

Die navorsing probeer vasstel wat die probleme met Fotoniesepakkieskakeling- (PPS) netwerke is. Twee van die belangrikste probleme is kontensie en die realisering van verskeie lengte vertragings om fotoniese pakkies te stoor. Die OKS is geanaliseer en daar is bevind dat dit aan die vereistes voldoen van toekomstige ultra-hoë PPS netwerktegnologie met sy hoë ekstinksieverhouding, wye optiese bandwydte, ultra-vinnnige skakelingspoed en lae kruisspraakvlakke.

Fotoniese pakkies word gegenereer met hoofde van 4 bisse, 8 bisse of 16 bisse teen 'n bistempo van 155 Mbis/s, wat gevolg word deur 'n PRBS vrag teen 10 Gbis/s. Verskillende

scenarios word beplan en die elektro-optiese beheer en OKS word dan blootgestel aan die scenarios met die doel om die doeltreffendheid van die elektro-optiese beheer en OKS te toets. Die schenarios sluit in:

- Vastelengte-pakkies wat sinchronies by inset 1 van die OKS aankom. Sekere van die pakkies moet na uitset 1 gaan, ander moet na uitset 2 gaan en sekere pakkies moet na uitset 3 gaan. Dus word 'n 1-tot-3 optiese skakelaar gerealiseer.

- Agt verskilende lengte pakkies wat sinchronies by inset 1 van die OKS aankom. Almal word na uitset 1 geskakel. Die elektro-optiese beheer moet dan die skakelsel oopskakel vir die regte hoeveelheid tyd.

- Drie verskilende lengte pakkies wat sinchronies en asinchronies by inset 1 van die OKS aankom. Sekere pakkies moet na uitset 1 gaan en die ander pakkies moet na uitset 2 gaan. Die elektro-optiese beheer moet dan die regte skakelsel oopskakel vir die regte hoeveelheid tyd.

- Twee vastelengte-pakkies kom gelyktydig by die OKS aan op twee verskillende insette. Beide van hulle moet na uitset 1 geskakel word. Die elektro-optiese beheer moet dan die kontensie waarneem en die pakkies so skakel dat die kontensie opgelos word.

Die elektro-optiese beheer en OKS het suksesvol al die tipes scenarios hanteer en die kontensie opgelos met 'n verlengde vessel. Sukses word op grond van twee aspekte gemeet. Eerstens is die eksperimentele resultate suksesvol as die uitsetstroom-pakkies dieselfde is as wat verwag is. Tweedens is die resultate suksesvol as die kwaliteit van die sein nie noemenswaardig versleg nie, wat beteken dat die BFT (Bis Fout Tempo) vir die pakkies minder as 10<sup>-9</sup> moet wees. Die oogdiagram van die pakkies word geneem, voor en na die OKS, om die kwaliteit van die pakkies te meet voor en na skakeling en dit dan te vergelyk.

Die navorsing het gelei tot die ontwerp van 'n doeltreffende elektro-optiese beheerstelsel vir die OKS. Die kontensieprobleem is opgelos vir vastelengte-pakkies wat sinchronies vervoer word en 'n voorstel om pakkies vir verskilende lengtes te stoor, word bespreek. Die elektro-optiese beheer het die potensiaal om die OKS vir meer ingewikkelde verkeer ook te beheer en sal dus die OKS verenigbaar maak met toekomstige ontwikkelinge.

#### LIST OF ABBREVIATIONS

ATM Asynchronous Transfer Mode

AVC Active Vertical Coupler

AWG Arrayed Waveguide Grating

BER Bit Error Rate

BPF Band Pass Filter

CPLD Complex Programmable Logic Device

EDFA Erbium Doped Fibre Amplifier

FTTH Fibre To The Home

GEPON Gigabit Ethernet Passive Optical Network

InGaAs Indium Gallium Arsenide

MOD Modulator

MOSFET Metal-oxide-semiconductor Field-effect Transistor

OOK On-off Keying

OXS Optical Cross-point Switch

PC Polarization Controller

PON Passive Optical Network

PPG Pulse Packet Generator

PPS Photonic Packet Switching

PRBS Pseudo Random Bit Sequence

SDH Synchronous Digital Hierarchy

SLALOM Semiconductor Laser Amplifier in Loop Optical Mirror

SOA Semi-conductor Optical Amplifier

SONET Synchronous Optical Network

TTL Transistor-transistor Logic

VOA Variable Optical Attenuator

# TABLE OF CONTENTS

| CHAPTER 1: INTRODUCTION                                         | 1  |

|-----------------------------------------------------------------|----|

| 1.1 Background                                                  | 1  |

| 1.2 Motivation                                                  | 2  |

| 1.3 Nature of problem                                           | 3  |

| 1.4 The aim of the research                                     | 4  |

| CHAPTER 2: LITERATURE STUDY                                     | 5  |

| 2.1 Introduction                                                | 5  |

| 2.2 Elements of a photonic packet switching node                | 6  |

| 2.3 The Active Vertical Coupler Based Optical Crosspoint Switch | 10 |

| 2.4 Contention-resolving techniques                             | 15 |

| 2.5 Buffering variable length packets                           | 18 |

| 2.6 The nature of data traffic                                  | 18 |

| 2.7 Header-processing techniques                                | 19 |

| 2.8 Transparency in optical networks vs. all-optical networks   | 21 |

| 2.9 Ultra-high speed optical packet switching                   | 21 |

| CHAPTER 3: ELECTRONIC CONTROL DESIGN                            | 22 |

| 3.1 Introduction                                                | 22 |

| 3.2 Aims of the electro-optic control interface                 | 22 |

| 3.3 The existing current control circuitry                      | 23 |

| 3.4 Circuit diagram for the new electronic control              | 25 |

| 3.4.1 The PINFETs                                               | 25 |

| 3.4.2 The voltage comparators                                   | 27 |

| 3.4.3 The CPLD                                                  | 28 |

| 3.4.4 Power supply                                              | 29 |

| 3.4.5 The SMA output ports                                      | 30 |

| 3.5 Printed circuit board design                                | 30 |

| 3.5.1 The layer stacks                                          | 31 |

| 3.5.2 Component layout and packaging                            | 32 |

| 3.5.3 The analog and digital ground                             | 33 |

| 3.5.4 Track impedance calculation                               | 34 |

|                                                                 |    |

| 3.6 The electronic control's response to a packet with a 155 Mbit/s header and 10 Gbit/s |    |

|------------------------------------------------------------------------------------------|----|

| payload                                                                                  | 35 |

| CHAPTER 4: EXPERIMENTAL SET-UP                                                           | 38 |

| 4.1 Introduction                                                                         | 38 |

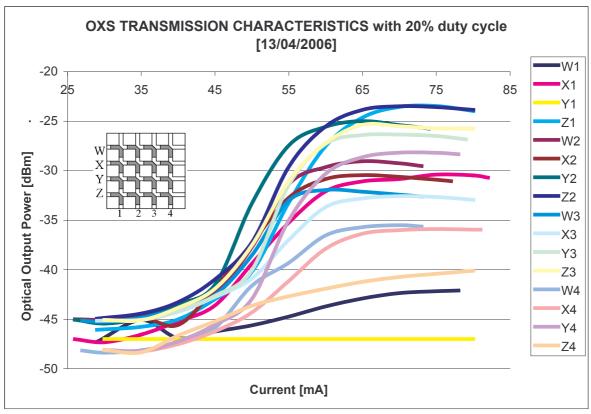

| 4.2 Characteristics of the VAC OXS                                                       | 38 |

| 4.3 A typical packet                                                                     | 40 |

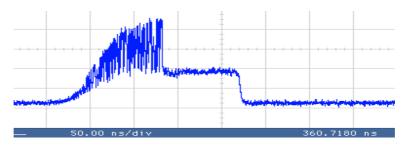

| 4.4 Determining the rise and fall time of the OXS                                        | 40 |

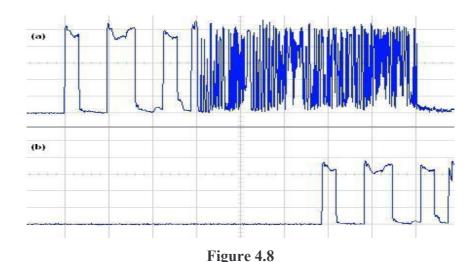

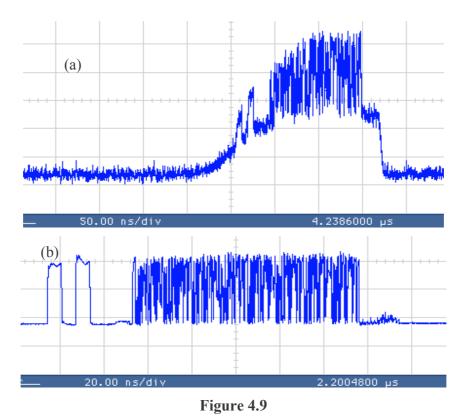

| 4.5 Packet generation                                                                    | 42 |

| 4.6 Input buffer length calculation                                                      | 45 |

| 4.7 The band pass filter                                                                 | 46 |

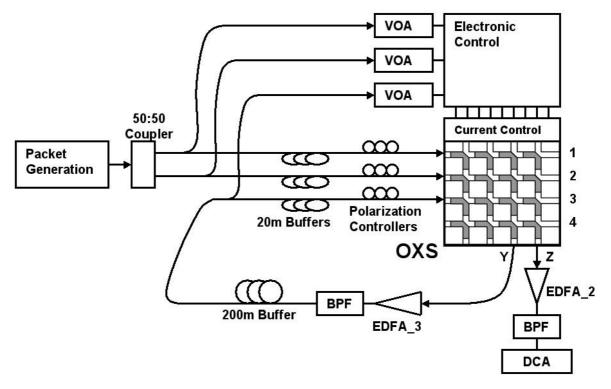

| 4.8 The experimental set-up for the contention resolution experiment.                    | 47 |

| 4.9 The delay buffer                                                                     | 49 |

| 4.10 The influence of crosstalk in the OXS                                               | 49 |

| 4.11 Synchronization with clock                                                          | 51 |

| 4.12 Discussion of experiments                                                           | 52 |

| CHAPTER 5: EXPERIMENTAL RESULTS                                                          | 54 |

| 5.1 Introduction                                                                         | 54 |

| 5.2 The clock signal                                                                     | 54 |

| 5.3 The PRBS payload                                                                     | 55 |

| 5.4 Measuring Q-factor and bit error rate                                                | 56 |

| 5.5 Experiment 1A: Using 4-bit header packets for photonic packet switching from one     |    |

| input to three outputs                                                                   | 57 |

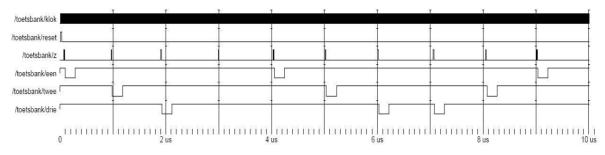

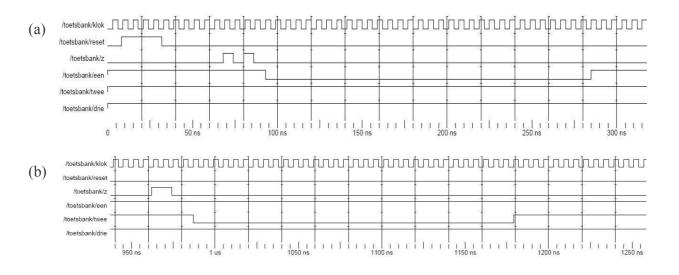

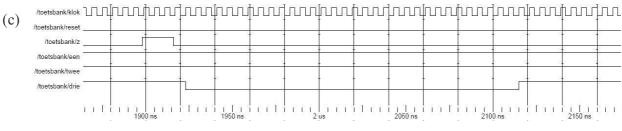

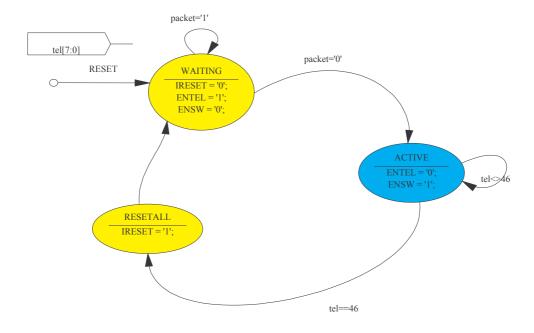

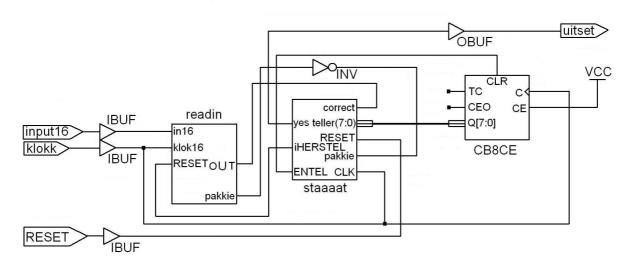

| 5.5.1 The logic design and simulation results                                            | 57 |

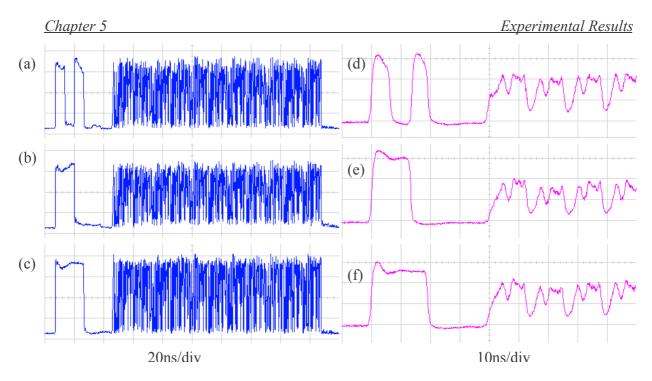

| 5.5.2 The experimental results                                                           | 60 |

| 5.6 Experiment 1B: Using 4-bit header packets for eight variable length photonic packet  | S  |

| switching from one input to one output                                                   | 65 |

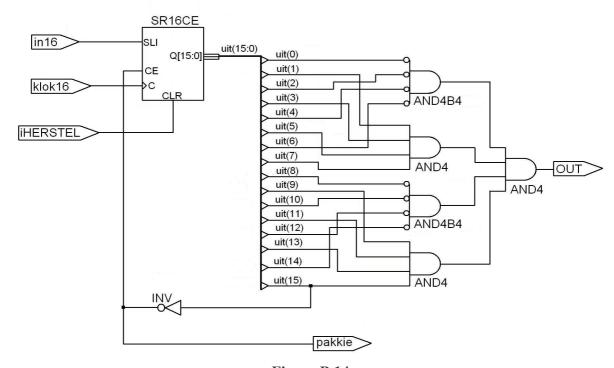

| 5.6.1 The logic design and simulation results                                            | 65 |

| 5.6.2 The experimental results                                                           | 67 |

| 5.7 Experiment 2: Using an 8-bit header packet for photonic packet switching of three    |    |

| variable length packets from one input to two outputs.                                   | 70 |

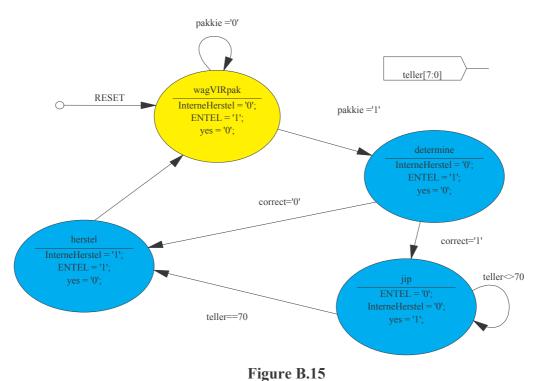

| 5.7.1 The logic design and simulation results                                            | 70 |

| 5.7.2 The experimental results                                                           | 74 |

| 5.7.3 Asynchronous packet stream                                                         | 77 |

| 5.8 Experiment 3: Using a 4-bit header packet to demonstrate contention resolution | in a |

|------------------------------------------------------------------------------------|------|

| photonic packet switching network from two inputs to one output.                   | 77   |

| 5.8.1 The logic design and simulation results                                      | 77   |

| 5.8.2 The experimental results                                                     | 81   |

| 5.9 Experiment 4: Using a 16-bit header for 1-to-1 photonic packet switching       | 84   |

| 5.9.1 The logic design and simulation results                                      | 84   |

| 5.9.2 The experimental results                                                     | 85   |

| 5.10 Discussion of experimental results                                            | 87   |

| CHAPTER 6: DISCUSSION AND CONCLUSION                                               | 91   |

| 6.1 Discussion of research results                                                 | 91   |

| 6.2 Recommendations for future work                                                | 92   |

| 6.2.1 Label/header swapping                                                        | 92   |

| 6.2.2 Header content                                                               | 92   |

| 6.2.3 Technology interfacing                                                       | 93   |

| 6.2.4 Asynchronous operation                                                       | 93   |

| 6.2.5 Storing variable length packets                                              | 93   |

| REFERENCES                                                                         | 95   |

| ADDENDUM A:                                                                        | 102  |

| ADDENDUM B:                                                                        | 106  |

#### **CHAPTER 1: INTRODUCTION**

## 1.1 Background

Today's optical networks offer many types of services. These services are connection orientated in the sense that data is being transported across an underlying network between two or more parties. The bandwidth of the connection as well as the type of network with which this connection is supported has a significant impact on the quality of the service offered [1]. The three types of networks include circuit switched, packet switched and burst switching networks.

In a circuit switched network the connection has a guaranteed amount of bandwidth all the time. Circuit switching networks lack the ability to handle bursty data traffic efficiently [2]. Packet switching was invented to increase the efficiency of transporting bursty traffic across the network. In packet switching networks, the data are broken up into packets. Packets from all sources share the network at the same time. A packet consists of a header and payload. The header carries information about the destination of the payload and is used to route the packet through the network. Burst switching is very similar to packet switching in the sense that many packets with the same destination are grouped together, forming a burst, and are sent across the network at one time. An example of a packet based switching network is the Internet with Internet Protocol (IP) based packets being routed across the telecommunication network.

Optical fibre technologies are widely used in telecommunication networks today and have the ability to manage and support all three these types of connections. SONET/SDH networks deploy optical interfaces and play a major part in metro and long-haul transport networks. The role of optics today is only limited to the realization of transport functions. The overhead, control and management functions are performed in the electronic domain. Next generation networks might perform switching and control functions directly in the optical domain [3]. In order to exploit the tremendous capacity provided by optical fibre, the switching functions must be implemented in the optical domain [4]. Photonic packet switching technologies are still in the experimental stage in research laboratories and require maturity before prototypes

Chapter 1 Introduction

will become commercially available. In an optical packet switching network, also known as a photonic packet switching network, packets are switched across the network while in the optical domain without any optical-electrical-optical conversion.

#### 1.2 Motivation

With the telecommunication network's bandwidth increasing at a very fast rate, the future telecommunication network should be able to handle and manage this traffic load efficiently, fast and without error and to be compatible with future development and a further increase in the telecommunication network's traffic. Optical fibre networks most certainly have this capability, with technologies such as DWDM (Dense Wavelength Division Multiplexing), PPS (Photonic Packet Switching), Optical Burst Switching and OTDM (Optical Time Division Multiplexing). Photonic packet switched networks combine the high capacity of optical technology with the flexibility of packet switching and are regarded as a promising future solution for all-optical networks [2], [5]-[6]. Owing to the high bandwidth demand, bandwidth efficiency is of the utmost importance in optical fibre networks and photonic packet/burst switching networks manages high bandwidth more efficiently.

In the last 20 years, novel optical technologies, such as distributed feedback lasers, advanced designs of passive and active optical fibres, erbium-doped and Raman optical amplifiers, high-speed optical modulators and wavelength division multiplexing have revolutionized the transport of information by moving data transport from the electronic domain to the optical domain. With the advent of reconfigurable optical add-drop multiplexers, the need for optical-electrical-optical conversion and electronic processing was pushed further away from the network core towards the edge of an increasingly all-optical network.

The full potential of optical communication networks is compromised (not utilized to its full potential) in networks that convert the data to the electronic domain. If information is converted to the electronic domain, an electronic bottleneck is formed owing to the limitation of electronic processing and high bandwidth capabilities (+40Gbits/s per channel) of optical fibre networks. Currently optical networks still depend on the electronic domain to assist in data transport. In photonic packet switching networks the packets can be kept in the optical domain but by tapping off some optical power, the header can be processed electronically to

Chapter 1 Introduction

perform control functions. Therefore the need for fast and flexible control circuitry is of the utmost importance in PPS networks. While the processing is being done, the packet needs to be buffered in a fibre delay line and therefore transparency is preserved. Transparency can easily be implemented in circuit switching networks but is more complex in packet and burst switching networks.

Because photonic packet switching technology is being developed in research laboratories [2], problems and difficulties can be identified at this stage and be dealt with before the product becomes commercially available.

## 1.3 Nature of problem

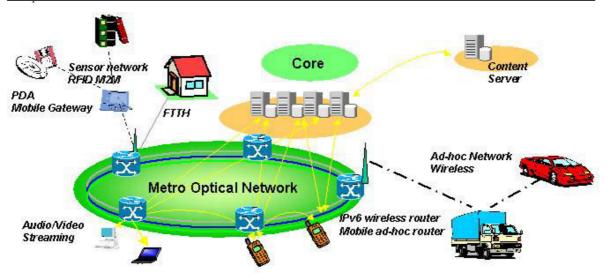

A typical optical fibre network is shown in Figure 1.1. The access networks for example, audio/video streaming, PDA mobile gateway, sensor networks, FTTH networks and wireless networks, all connect to the metro optical network. All the different metro networks are connected to a core or backbone network over which optical packets must be routed. Optical packets arrive at the input of the node and need to be switched to a specific output of the node in order to reach their destination.

It is at these nodes that some problems with photonic packet switching are identified. The first problem is the need for a fast and flexible control mechanism and optical switch to route optical packets from the input of these nodes to the outputs. The second problem occurs when two or more packets on the same wavelength enter the node from different input ports and are destined for the same output port at the same time and in the same space. If this contention of input packets is not resolved, it will result in loss of data due to interference of light with these two packets. This is a problem in photonic packet switching networks and needs to be taken into account when designing optical fibre networks, otherwise it will result in a dramatic decrease in quality of service.

According to [7] contention resolution belongs to a realm of higher-level routing control and should be dealt with by more complicated control and according to [8], contention resolution is a fundamental difficulty with all optical packet switch designs due to a lack of optical memory.

Chapter 1 Introduction

Figure 1.1

An overview of an optical network from [9]. The access networks connect to the metro optical network. The core optical network connects different metro optical networks.

Because of the processing that needs to be done or contention that needs to be resolved, a third problem arises: these optical packets need to be "stored" for some time while the processing is being done or contention is being resolved. No optical RAM is available and therefore fibre delay lines are used to "store" the optical packets for a fixed duration of time. Sometimes there is a need for variable length delay and this requires more complicated buffering strategies.

### 1.4 The aim of the research

The objective of this research is to identify a potential optical switch to be used in photonic packet switching networks. The aim is then to develop an electro-optic control interface to manage and control this optical switch very fast (in the order of 10 ns) in order to demonstrate errorless photonic packet switching with the capability to detect when contention occurs as well as to resolve it successfully. The electronic control should show flexibility in the sense that various types of data traffic can be switched.

#### **CHAPTER 2: LITERATURE STUDY**

#### 2.1 Introduction

The research will focus mainly on photonic packet switching functionality. The technologies within optical networks that need to be studied include

- photonic packet switching,

- optical switches,

- contention resolution techniques,

- optical buffering of packets (fixed and variable length),

- optical and electronic header processing, and

- the nature of data traffic in these types of networks.

Photonic packet switching has emerged as an attractive way to overcome the electronic bottleneck in today's fast-growing communication network. Identifying the needs and requirements for photonic packet switching networks will give insight into the design of the electro-optic control interface. As more bandwidth is provided in these systems, issues such as processing, optical buffering, scalability and contention remain the key design challenges for the switching networks. The goal of photonic packet switching networks is to provide the same services as those of electronic packet switched networks but at much higher speeds. Although optical packet switching networks offer extremely high data rates, transparency and high switching speed, their performance depends strongly on optical device technology [10].

A typical optical fibre network is shown in Figure 2.1. The network consists of three main interconnected networks: the core network, the metropolitan network and the access network. The core or long-haul network carries the highest amount of data and basically connects all the metropolitan networks. The access network is the connection point of all the clients to the optical network. The dominating optical network for the access network is the PON (Passive Optical Network) or GEPON (Gigabit Ethernet Passive Optical Network). The metropolitan and core networks basically consist of nodes interconnected by fibre cables. These nodes and fibres are connected in a ring, star or mesh topology. It is at these nodes that data need to be

switched from one specific input fibre to another specific output fibre. This switching is done with a photonic switching element.

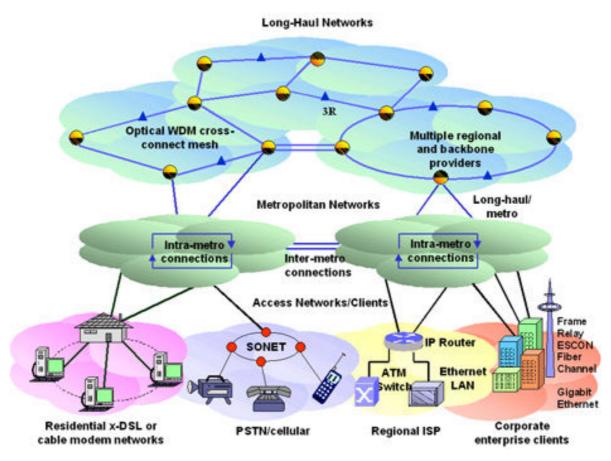

Figure 2.1

Diagram illustrating how different optical network layers are interconnected. Access network such as x-DSL, cellular, ISP and Gigabit Ethernet are connected to the metropolitan network. Long-haul networks connect all the metropolitan networks to form the backbone optical network. Picture taken from [11].

The basic building blocks of such a switching node will be studied and various problems that may occur at these photonic packet switching nodes will be addressed. Recent experimental results from different sources will also be investigated.

# 2.2 Elements of a photonic packet switching node

The function of the node is to make and break connections between inputs and outputs. A

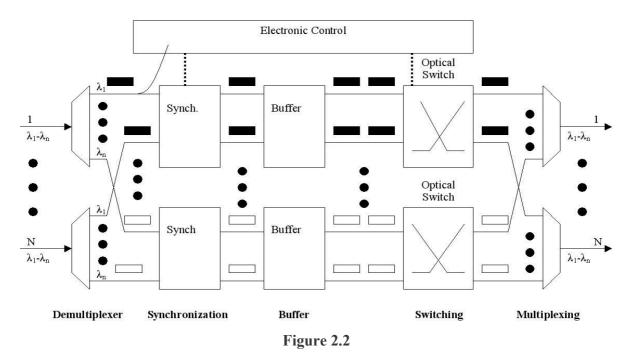

typical node will have 4-16 input fibres with about 16 channels (different wavelengths) carried on each input. The data entering the node must be switched optically to the correct output port, depending on the information in the header. Figure 2.2 shows such a generic node with N input fibres and n wavelength channels in each fibre. The first function is to demultiplex the wavelengths from the different inputs so that only one specific wavelength, from the N different inputs, travels through a synchronization, buffer and optical switching block. Synchronization is done to align packets in time before entering the optical switch because packets arrive at the node out of synchronization due to different routes travelled. The buffer stores the packet for a fixed amount of time in order for the processing to be done and optical switch to be set up correctly. The optical switch will be an N×N switch. There are different blocks for each wavelength since different information is carried on different wavelengths and is destined for different outputs. All the packets from these different blocks are then again multiplexed onto one fibre at each output port. Although a wavelength routing technique also exist to implement a generic node, this dissertation will focus on the generic node structure from Figure 2.2.

A generic node found in the core and metro optical networks. It has N input and output fibres each with *n* wavelengths. The packets need to be synchronized and buffered before they can be switched. Each optical switch handles only one specific wavelength [2], [5].

Packet switching structures are compared on a number of parameters; one such figure of merit is the loss probability or blocking probability [12]. The functioning of such a generic node is strongly dependent on the type of data. One of the most important components in photonic packet switching networks is the optical switch. This component should be able to route optical packets within a few nanoseconds from the input to the correct output port.

Switching is an essential operation in communication networks [13]. A switch is a device that establishes and releases connections among transmission paths in a communication network. Fibre-optic communication networks can transport data at a rate of 2.5 Terabits/s on one fibre. This rate is achieved by WDM and OTDM. At these high data rates, very fast photonic switches are essential. Types of optical switches include: Optical MEMS (Micro-Electro-Mechanical System), thermo-optical, electro-optical, opto-optical, acousto-optical and magneto-optical [13], [14]. Optical MEMS are miniature devices with optical, electrical and mechanical functionalities at the same time. Thermal optical switches are based on waveguide thermo-optic effect or thermal phenomena of materials. Electro-optical switches realize optical switching by using the electro-optic effect. Opto-optical switches realize switching functions relying on the intensity-dependent nonlinear optic effect in optical waveguides. The efficiency and performance of these optical switches depend on the following characteristics:

- Size This is the number of inputs and outputs that the switch supports.

- Direction The ability to transfer light across the switch in one or two directions.

- Switching speed The time it takes to be reconfigured from one state to another.

- Propagation delay time The time it takes the light from the input to the output.

- Throughput The maximum data rate that can flow through the switch when it is connected.

- Switching energy The energy needed to activate and deactivate the switch.

- Power dissipation The energy dissipated per second in the process of switching.

- Insertion loss The loss in optical power introduced by the connection.

- Crosstalk The undesired power leakage to other ports.

- Physical dimensions The size of the switch architecture.

- Bandwidth The band of wavelengths that the optical switch supports.

- Transparency The independence of the switch from the bit-rate or protocol of the data.

The different types of optical switches are compared on the basis of these characteristics and the comparisons are given in [14]. One important characteristic that needs to be pointed out is that the fastest optical switch is the SOA based switch that is an electro-optic switch with switching speed in the order of 200 ps.

Another optical switch that is being developed in the research laboratories is the SLOB (Switch with Large Optical Buffers) [10]. The SLOB has a very simple architecture and very large buffer depth, ideally for bursty traffic. This switch is limited by optical power loss, noise and crosstalk when the number of input and output ports is high. The ALCATEL ATM switch [10] is limited by the splitting and combining losses. Optical amplifiers can increase the performance by increasing the optical power but also introduce more noise. The ALCATEL ATM switch is limited to 16 inputs. The ULPHA (Ultra-Fast Photonic ATM) switch is similar to the ALCATEL ATM but utilizes ultra-short optical pulses. It has many electronic devices that result in the electronic bottleneck effect. The ULPHA is a very large architecture but with a relatively simple routing algorithm.

The most common limitation in optical switches is the optical splitting and combining losses. To solve this problem, an AWG (Arrayed Waveguide Grating) is used. The AWG switch takes the optical input power, consisting of a number of wavelengths, and switches the specific wavelengths to specific output ports by interference. Owing to the wavelength dependence of the AWG, it is also very popular in resolving contention in the wavelength domain. The AWG has a typical power penalty in the order of 1.54dB for 32 inputs.

The European Keys to Optical Packet Switching project (KEOPS), described in [8], [15] focuses on the development and assessment of optical packet switching and routing networks capable of providing transparency to the payload bit rate. They seek to combine packet switching with WDM transmission techniques to yield WDM optical packet switching. They use a WRS (Wavelength Routing Switch) that relies on dynamic wavelength conversion at the packet level to perform the routing of packets. The WRS includes demultiplexers based on the AWG. The switch is under the control of an electronic unit.

Fewer components result in less noise and crosstalk and therefore it is desirable to build such a photonic packet switching node with as few components as possible. These will also reduce

the cost of the network. A very attractive optical switch is the AVC (Active Vertical Coupler-Based) OXS (Optical Crosspoint Switch), an electro-optical switch, which will be discussed in greater detail in the next section.

# 2.3 The Active Vertical Coupler Based Optical Crosspoint Switch

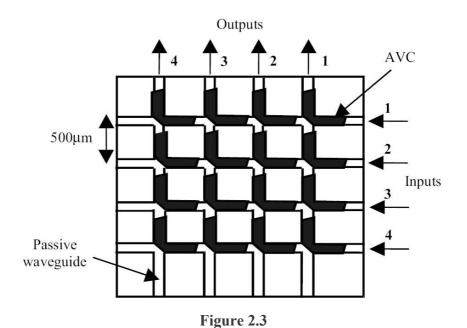

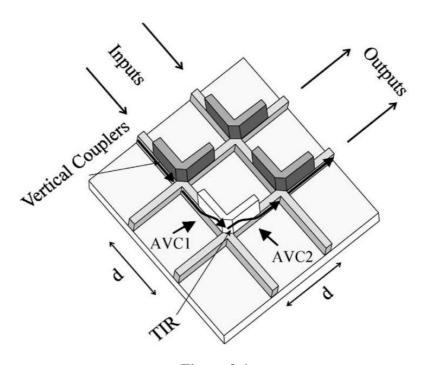

The AVC OXS was developed and built by researchers in the Department of Electrical and Electronic Engineering at the University of Bristol in the United Kingdom. The OXS has four optical inputs and four optical outputs. The top view of the OXS can be seen in Figure 2.3. Each of the four inputs consists of a passive waveguide separated by  $500 \, \mu m$  from one another to guide the light into the OXS.

The 4x4 AVC OXS seen from the top. Four passive input and output waveguides intersect at the 16 cross points. Sixteen AVCs are grown at these cross points [4].

The four outputs also consist of passive waveguides separated by  $500\,\mu m$  that intersect perpendicularly with the input waveguides. These passive waveguides are made from InGaAsP. These four input and output waveguides are deposited on top of an InP substrate and intersect in 16 places.

A three-dimensional picture of a 2x2 OXS is shown in Figure 2.4. On top of each of these waveguide crosses, an active layer is deposited that together with the passive lower waveguide forms an active vertical coupler. Active refers to the fact that the waveguide has either a significant loss or gain of the optical signal concerned. External power is required to perform the coupling operation. This loss or gain and refractive index can be modulated by current injection. Two of these active vertical couplers are made, one with the input passive waveguide and the other one with the output passive waveguide. A total internal reflection mirror vertically penetrates the active waveguide at an angle of 45° with respect to the two couplers' directions. This intersection, or crosspoint, is called a switch cell.

Figure 2.4

A 3D view of a 2x2 OXS. The arrows indicate the direction and how light travels through the OXS when in the ON state. TIR: Total Internal Reflection, AVC: Active Vertical Coupler [16].

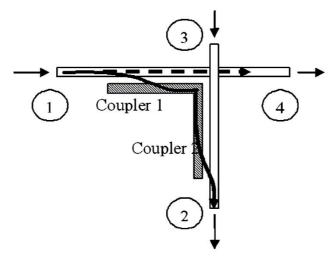

A single switch cell is shown in Figure 2.5. The switch cell can be operated in one of two states. The injection of carriers into the active region turns the device to the "ON" state. Applying current to the active region causes the injection of carriers into this region. It generates gain and reduces the refractive index of the active upper waveguide to match the corresponding refractive index value of the bottom passive waveguide. Therefore in the "ON"

state, the travelling input light signal, injected into the input passive lower waveguide, couples with the active upper waveguide at the first active vertical coupler and is steered by the total internal reflection mirror into the second active vertical coupler waveguide. The light is then coupled down to the bottom passive waveguide to exit the OXS via the specific passive output waveguide.

Figure 2.5

One of the switch cells is shown here. In the OFF state light travels in the passive waveguide from 1 to 4, in the ON state light travels from 1 to 2 via the AVC [17].

When in the "OFF" state the OXS is not biased and therefore the input optical signal only travels along the input lower passive waveguide. The optical signal in the passive waveguide does not interact with the active layer and travels straight through to the next switch cell. Any residual coupling into the active layer is absorbed by its high loss and therefore very little of the signal (leakage) appears on the output. When operated in a point-to-point switching application, up to four input signals can be simultaneously switched through the matrix if they are not contending with each other. The electronic control will control the states of these switch cells by supplying current to the corresponding switch cell.

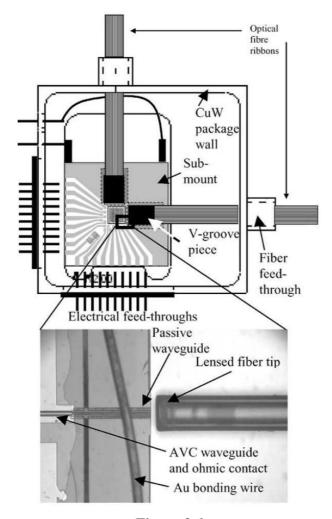

One of the main problems with the OXS is to package it or connect the OXS chip, Figure 2.6, with optical fibres and electrical connections. Four input and four output optical fibres are needed as well as 16 electrical connections, one for each switch cell. The coupling strategy, to connect optical fibres to the waveguides or OXS chip, is discussed in [18]. The fibres need to

be coupled with minimum optical coupling loss. Since the OXS chip is an active device, heat will be generated and thermal management is required to keep the chip operating at environmental temperatures. The packaged case has dimensions of 30 x 30 x 9 mm (L x D x H). Two sides are used for optical fibre access. The other two sides are used for electrical connections. Refer to Figure 2.6 that demonstrates this packaging.

Figure 2.6

Diagram illustrating the packaged OXS chip [18].

Fibre array alignment and fixation are the two most critical issues in the packaging process. The fibre ends need to be micro-machined into lenses with the proper shape to achieve high coupling efficiency. Wedge lenses are used instead of conical lenses because of limitations in the micro-machining process. The fibre tips are machined by a high-powered laser beam into wedge-shaped fibre lenses with a focal distance of about  $9 \mu m$ .

Various experiments have been done with the AVC OXS to demonstrate the flexibility of the OXS as optical switching mechanism. A continuous data stream was sent into the OXS and short packet type control signals were sent to the switch cell, resulting in packets being generated [4], [17]. The ON-OFF extinction ratio was 70 dB and crosstalk levels of smaller than –65 dB were achieved. Each switch cell was tested and experimented with separately. A power penalty of less than 1 dB at a BER of 10<sup>-11</sup> was measured between the longest and shortest path. The longer paths suffered higher power penalties.

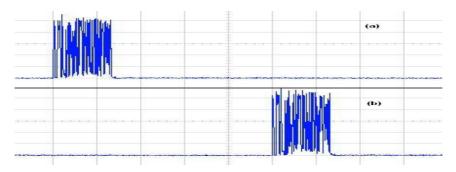

All experiments above use the OOK external modulation scheme. By using a DPSK (Differential Phase Shift Keying) payload, the pattern effect was reduced and this is demonstrated in [19]. Timeslot interchange was demonstrated through which the order of the arriving packets is rearranged into a more desirable order for specific applications such as time division multiplexing [20]. A re-circulating buffer of one timeslot was used to store packets for a fixed time. Multiple re-circulations through the optical buffer were demonstrated. The packets are 60 ns long and consist of a PRBS at 10 Gbit/s.

Optical multicasting experiments have also been done with the OXS and results are discussed in [21], [22]. In optical multicasting experiments one packet is sent into the input port and exits all four output ports. Switching the switch cell on with a higher current than that used in normal packet switching operations can achieve this multicasting. In [23] packets with different optical powers are sent to the OXS and switched to the output at equal power levels. To achieve this power equalization, processing is needed to determine the power level and make a decision on how much current to use to switch on the switch cells, since the current is proportional to the optical power loss across the switch cell.

In all these experiments the current is controlled (switch cell being switched ON and OFF) by a signal from the PPG. This signal is deterministic, meaning that before the experiment is conducted, a plan is set up to determine which switch cells should be opened and for how long they should be opened. The signal from the PPG is a 16-bit code that includes a header detection code and the address of the switch cell to open. In a more realistic situation, this approach will not work because of the undetermined nature of data traffic, and therefore a header signal is needed before the payload that carries information about the packet.

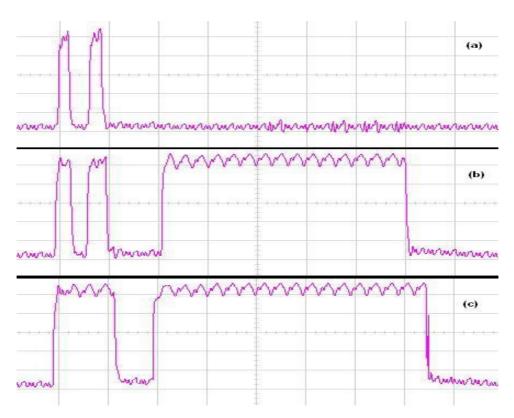

The experiments in [7], [23] have this form of header or optical label. A guard time of 103 ns is used between the header and payload to allow time for processing and switching the switch cell from the OFF state to the ON state. No input buffer is therefore needed. In [7] the header is sent on  $\lambda_1$  and the packet's payload is sent on  $\lambda_2$ , 103 ns later. The optical header is converted to the electronic domain, processed and the corresponding switch cell is opened. When the payload arrives at the OXS it can be switched directly without being buffered. Variable length packets are generated and switched across the OXS. The label or header is a 14-bit sequence at 155 Mbit/s, indicating which switch cell needs to be switched open for its packet and for how long the switch cell must be opened. This approach of transmitting the switch cell's address to be used in the header is not very good. It does not take into account what happens on the other input ports of the same OXS. A better approach is to indicate the desired output port of the packet in the header. The electronic control should detect from which input the packets are coming, which output port they are destined for and then compare this information with the current status of the OXS. The electronic control then decides which switch cell to switch open for the packets. In PPS or OBS networks that run synchronously or in a slotted approach, the status can be determined at the beginning of each timeslot, but with packets arriving asynchronously at the switch, real time status needs to be used.

#### 2.4 Contention-resolving techniques

A fundamental issue in packet switching networks is contention resolution [24], [25]. Contention occurs at a switching node whenever two or more packets try to leave the switch fabric on the same output port, on the same wavelength and at the same time. When designing a photonic packet switching network with contention resolution capabilities the nature of the data traffic is of the utmost importance. These characteristics include fixed length packets versus variable length packets or bursts and whether the data arrive at the optical switch synchronously or asynchronously.

The three main solutions used to resolve contention include:

1. In the time domain by using a fibre delay line as a buffer to store the contending packet for a fixed amount of time.

2. In the space domain by deflection routing whereby the contending packet is switch via another route to its destination to resolve the contention.

3. In the wavelength domain by converting the contending packet to another wavelength that is available.

The type of contention-resolving technique is dependent on the characteristics of the data being sent across the network. All three these solutions have been demonstrated and results were all successful [24], [26]-[34]. Both wavelength conversion and optical buffering require extra hardware. This includes wavelength converters, lasers and demultiplexers. Optical fibres and extra switching ports are needed when implementing buffering to resolve the contention. Deflection routing requires extra control software and can cause latency, packets arriving in the wrong order at the destination.

The main aim is not to select one contention resolution technique to implement in the network, but rather to try integrating all three techniques, resulting in much more depth of the network's ability to handle contention. For example, the authors from [27] simulate and investigate the effect of combining the three contention resolution schemes. Their rule of which scheme to use is as follows: A packet that loses the contention will first seek a vacant wavelength on the preferred output port. If no such wavelength exists, it seeks a vacant delay line. If no delay line is available it seeks a vacant wavelength on the deflection port. If all three schemes fail, the packet is dropped.

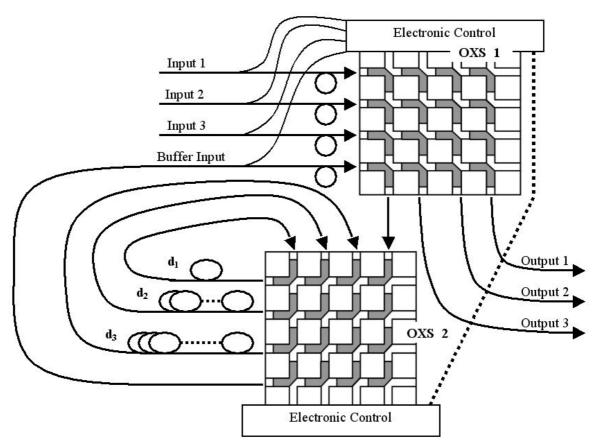

In [12] the authors suggest using the staggering switch. It assumes all packets are of fixed length, time is slotted and the arrival of packets is synchronized. The system has n inputs and n outputs and consists of two stages, the scheduling and switching stage. The scheduling stage is connected to the switching stage by m delay lines,  $d_i$  (i=1to m). The delay of the  $d_i$  delay line equals i packets. The scheduling stage distributes packets to the delay lines in such a way that, in any timeslot, no two packets arrive at the switching stage destined for the same output. In other words, the output collisions that occur at the inputs are resolved by delaying the colliding packets by different numbers of timeslots, so that when they arrive at the switch's output there are no output collisions. The scheduling and switching are done by electronic control. The control receives header information from all arriving packets and allocates them

to the delay lines. Therefore the electronic control should have knowledge of the content of the delay lines at any time. This requires quite a lot of electronic processing. The performance of the staggering switch is measured in terms of packet loss probability.

Contention is mainly found in the core and metropolitan networks since that is where optical switching is implemented. In [35] the authors suggest moving away from the core and focussing more on the edge or access part of the network in order to resolve, or in this case, reduce contention. They propose enhanced edge routers with a traffic-shaping function. This means that packets are sent from the edge nodes in such a way as to avoid contention occurring at the core routers. A similar scheme is proposed in [24] and is called contention aware slot shifting. In this scheme core switches collect slot information and calculate possible contending slots during a period T, then notify the edge nodes, which are responsible for the computationally intensive task of slot shifting. Therefore, the core node processing time for each slot is not affected (header processing and forwarding are not changed) and no extra hardware is required at the core switch. A time slot interchange system is also demonstrated in [20] by using the VAC OXS. This approach changes the order of packets to avoid contention.

$N\times1$  contention resolution is demonstrated in [36] by using a  $N\times1$  (multi-stage) buffer for asynchronous variable length packets. The system consists of N fibre delay lines with different lengths. The outputs of all these fibre delay lines are coupled into one fibre. Therefore any input (N) could be switched to the output with a specific delay, by allowing it to pass through the corresponding fibre delay line. This is very similar to the staggering switch.

How contention is resolved has a great influence on network performance [26]. The network's performance is based on packet loss probability and quality of service. Packets are only dropped if all possible contention-resolving techniques are being used and no other contention resolution technique is available.

When one looks at Figure 2.2, the generic photonic packet switching node, one notices that at a single optical switch, the N inputs all carry the same wavelength. Other wavelengths are switched at other optical switches. Therefore, contention should first be resolved in the wavelength by using buffering and secondly (if a buffer is full) the contention can be resolved using a second wavelength.

In [37] the authors demonstrate an all-optical sub-system performing on-the-fly contention resolution in both space and wavelength domains. Error-free operation was obtained for 10 Gb/s NRZ and 40 Gb/s RZ packets but the system lacks a header in the packets, uses a 2x1 network and is very bulky and therefore not flexible at all.

The next problem occurs because variable length packets need to be stored while in the optical domain. No optical RAM is available and some solutions to store variable length optical data are discussed next.

# 2.5 Buffering variable length packets

Switching and buffering of variable length packets optically is a demanding task [33]. The use of a re-circulating buffer serves as a variable delay in [38]. A fixed delay length, T, is chosen and by passing the packet x times through this buffer, a delay of xT can be realized. The variable delay is set up by all-optical processing technology using an optical threshold function and a wavelength converter. This buffering concept is good for fixed length packets but suffers some problems when using variable length packets. With a combination of switches and different fixed length fibres between the switches, a more flexible variable optical buffer can be realized [1]. The VAC OXS can also be set up to deliver variable delays as discussed in [19].

A totally different method is slowing light down in the optical fibre. This can be realized by using a vertical cavity surface-emitting laser [39]. By varying the bias current around the lasing threshold researchers achieve variable delay of intensity-modulated signal input. In [40] the authors also propose building a variable optical buffer by slowing light down. The buffering effect is achieved by slowing down the optical signal using an external control light source to vary the dispersion characteristics of the medium via an electro-magnetically induced transparency effect.

#### 2.6 The nature of data traffic

The packet starts with a header. The header is usually at a lower bit rate than the payload for electronic processing purposes. In some cases the header and payload has the same data rate.

The header has information about the destination of the packet, the length of the payload and some recognition bits to identify the header. The payload follows the header. They are usually separated by some guard time. The payload contains the data and is at very high bit rates. The payload can be either a fixed length for all packets on the network or of variable lengths for different types of data. Packets are sent across a network either synchronously or asynchronously.

Synchronously means that the timescale is divided into fixed length timeslots within which packets can be sent (slotted). In slotted networks all packets usually have the same length. Asynchronously means that the packets, usually of variable length, arrive at the optical switch randomly (un-slotted). Un-slotted networks have lower overall throughput than slotted networks because of the increased packet contention probability [28].

# 2.7 Header-processing techniques

The most common approach is to transmit the header in front of the payload at a bit rate that the photodiodes and processing electronics can support. By tapping optical power from the input fibres, the header is converted to the electronic domain to be processed to configure the optical switch as required. The header is normally a NRZ (Non Return to Zero) OOK modulated signal but according to [19], [41] when using a DPSK decoding scheme for the header or payload, enhanced performance with respect to extinction ratio and alleviation of the pattern effect is observed. In DPSK modulation the header information is encoded on the phase of a pulsed optical level. Higher header processing rates are possible when using DPSK modulated headers because of higher header extraction efficiency [41]. Higher header bit rates can also be achieved if optical header processing is implemented.

It is important to realize that electronic control does not imply an e-bottleneck, since the data (payload) are kept in the optical domain. In electronic processing the header is 4-16 bits long at speeds ranging from 155 Mbit/s to 622 Mbit/s. In optical header processing the header is only 2 or 4 bits long at a bit rate of 10 Gbit/s. More bits in the header mean more information can be stored but this also occupies more time. In optical header processing the header occupies much less time but the experimental set-ups are bulky and network and protocol

specific. In both cases the packet is optically stored in a buffer while the header is being processed.

The authors from [5] demonstrate a 1x2 all-optical packet switch. The header processing is done in the optical domain by employing the two-pulse correlation principle in a semiconductor laser amplifier in loop optical mirror (SLALOM). This process does not require optical clock recovery and therefore reduces the complexity of the header recognition system. A disadvantage is that the structure only works for well-chosen header patterns and Manchester encoding is required for the payload to ensure that the header's bits do not repeat in the packets payload. However, the system is bit rate transparent for both header and payload. The system is based on wavelength routing principles and can only handle one packet at any given time. If two packets arrive, one of them needs to be buffered to avoid packet contention. Although the header is processed optically, the packet still needs to be delayed to compensate for the time taken to carry out the optical header processing functions. The header is at 2.5 Gbit/s and the payload at 10 Gbit/s.

A demonstration of a 4-bit optical header processing system using a wavelength label switch based on optical digital to analogue conversion is discussed in [6]. In the wavelength label switch the digital optical header is converted to a single analogue pulse with different amplitude to discriminate the header pattern difference. This amplitude is used to select a wavelength of an electronically tunable laser. Depending on the header, the packet is then converted to a specific wavelength and switched accordingly. If the header is 1111 it exits on wavelength 1552.8 nm, if the header is 1010 it exits on wavelength 1553.6 nm and if the header is 1110 it exits on wavelength 1558.9 nm. These three wavelengths then exit the optical switch via an arrayed waveguide grating, each one on a separate output port. The electronic domain is used to control the tunable laser, but no processing is done in the electronic domain. The disadvantage of such a system is the limit (four) in the number of bits in the header and also that there are no contention resolution capabilities.

A unique all-optical 1×2 self-routed optical switch is discussed in [42]. The header bits (three) are optically processed in parallel to route optical packets from one input to one of two possible outputs. This parallel processing increases the switching speed.

# 2.8 Transparency in optical networks vs. all-optical networks

Transparency can be realized in optical networks and has far-reaching consequences for expanding and upgrading the future optical network [12]. Transparency and "all-optical networks" are not synonyms [43]. Transparency refers to the fact that the network is bit rate and protocol independent. This means that many different types of data can be sent across the network without any concern about meeting specific speeds or network protocols. For transparency to be realized the data have to remain in the optical domain all the time from source to destination because if the data are converted to the electronic domain, processing and control functions are required, which require the data to be in a specific protocol and bit rate. To route the data across the network, a header at a specific speed and protocol is used, converted to the electronic domain to perform the control and switching functions at the nodes.

'All-optical networks' means that everything happens in the optical domain. Signal processing, packet switching and other control function are all realized in the optical domain. There is no need for the electronic domain in an all-optical network.

# 2.9 Ultra-high speed optical packet switching

Very high and fast (160 Gb/s up to 320 Gb/s) all-optical switching is demonstrated in [44] [45]. These high rates are achieved by WDM and ultra-fast modulation techniques. The principle of the system is very similar to general photonic packet switching, as has been discussed. The packets are generated, split (with coupler) and one part is delayed while the other part is processed to control the optical switch. At this high speed optical flip-flop memory is used to assist in the switching function. These systems do not have a very high number of input and output ports, typically one or two input and output ports.

#### **CHAPTER 3: ELECTRONIC CONTROL DESIGN**

#### 3.1 Introduction

The VAC OXS has an electronic control circuit consisting of a XC9572XL Complex Programmable Logic Device (CPLD) and 16 separate current control circuits. This electronic circuit forms part of the OXS package and therefore if one wants to control the OXS electronically, it needs to be done via this current control circuitry. Each one of these current control circuits controls the flow of current through the corresponding switch cell. In the previous experiments on the OXS, it was electronically controlled by control signals sent directly from the PPG to this current control circuitry. Optical packets are sent to the OXS and at the same time, pre-determined control signals are sent to the electronic control to open the correct switch cells for these packets. This approach to controlling the OXS can be seen as pre-determined switch cell operation and cannot be implemented in a realistic photonic packet switching network because of the random nature of data on the network.

A new approach is needed through which the OXS is electronically controlled depending on the input packets arriving at the OXS. In order to control the OXS without any knowledge about the sequence or occurrence of the data, an electronic control is needed that can determine the state of the PPS network at the OXS and make a decision on how to configure the OXS, for example which switch cells to switch open and how long to keep the corresponding switch cell open. In order to determine the state of the PPS network, processing is needed, and therefore the optical packets need to be converted to the electronic domain. In the electronic domain the headers of these packets are processed and the current state of the PPS network is determined. The header of the optical packets should have information on the length and desired output port of the packet.

#### 3.2 Aims of the electro-optic control interface

The aim is to design a new electronic control circuit that monitors the packets just before entering the OXS in order to determine the state that the OXS should be in. This new electronic control should interface with the existing current control electronics. Tapping some of the optical power from the input optical fibres and converting the packets from the optical

domain to the electronic domain should be done just before the packets enter the OXS. Only the header part of the packet is used for the processing. Depending on the input received and information processed, control signals are sent to the OXS's current control electronics to configure the OXS's switch cells.

The requirements and specifications for the new electronic control circuit include:

- It must have four photodiodes, one for each input, to convert the packets from the optical to the electronic domain.

- Conversion of the packets from the optical to the electronic domain at a bit rate of 155Mbit/s.

- The design of an interface from the photodiode's output to the CPLD's input port. The CPLD requires digital signals with transistor-transistor logic standard voltage signals. This is 0 V for low and 3.3 V for high.

- A fast CPLD to do the processing. It should have a clock input at 155MHz, be able to receive, process and send signals at 155 Mbit/s. It should have enough input and output ports. It should also have enough memory (macrocells) so that it can be programmed to control the OXS.

- A packet format or protocol will be established and processing will be done based on the information in the packet's header.

- The electronic circuit must be implemented on a printed circuit board (PCB).

- The control signals from the new electronic control must be sent via PCB mounted SMA connectors to the existing electronic control of the OXS. The existing electronic control also has PCB mounted SMA connectors and therefore the two circuits' boards will be connected with an SMA cable.

- The CPLD on the new electronic control board must be programmed using the JTAG connector.

- The PCB must be supplied with sufficient power for all the components.

#### 3.3 The existing current control circuitry

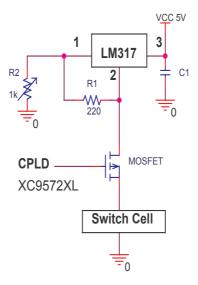

A switch cell on the OXS is switched on by a flow of current through the active coupler. There are 16 separate switch cells, each with its own electronic circuit to switch it on or off. The

current control circuit for one switch cell is shown in Figure 3.1. The current through the switch cell can be controlled manually or electronically. Variable resistor R2 can be manually selected to control the flow of current supplied by the LM317. In the off state (R2 = 0  $\Omega$ ) no current is supplied to the switch cell irrespective of the control signal from the CPLD. In the on state (R2 = 1 k $\Omega$ ) current is supplied to the switch cell only if the control signal from the CPLD is low. If the control signal from the CPLD is high, the p-channel MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor) is off and no current flows through the switch cell.

Figure 3.1

The existing current control circuit for one switch cell. The switch cell can be manually switched on or off with resistor R2 or electronically via the CPLD input.

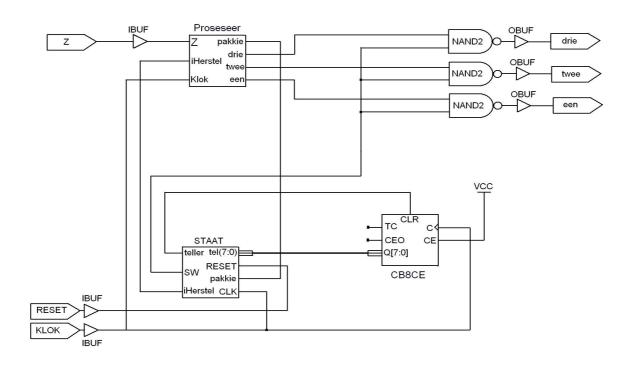

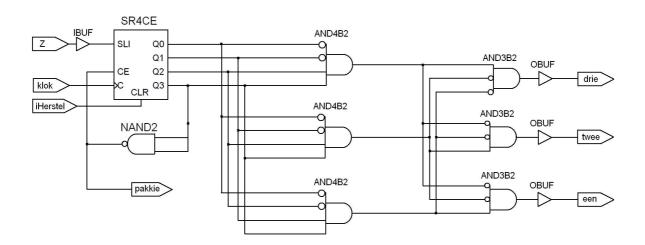

All 16 switch cells are controlled with control signals from the XC9572XL CPLD via its specific current controlled circuit. Sixteen output ports forming the XC9572XL CPLD are connected to the 16 control circuits. The XC9572XL CPLD has four inputs; one is for a clock input and in previous experiments, the other inputs were used for control signals from the PPG. With this new electronic circuit board, three of these inputs will be used as interfaces from the new electronic control board. The clock signal is supplied by the PPG to the new electronic control board. The clock signal is then also sent to the existing electronic circuit from the new control circuit board.

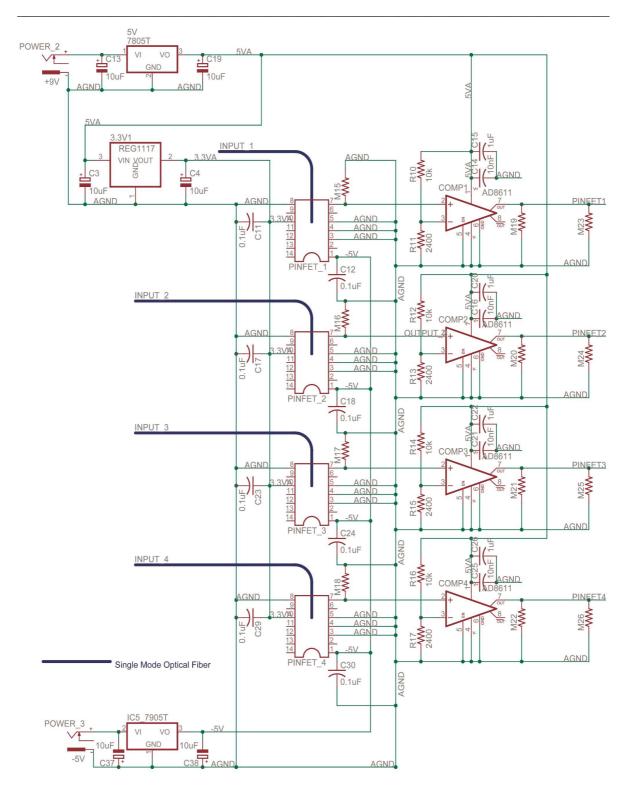

# 3.4 Circuit diagram for the new electronic control

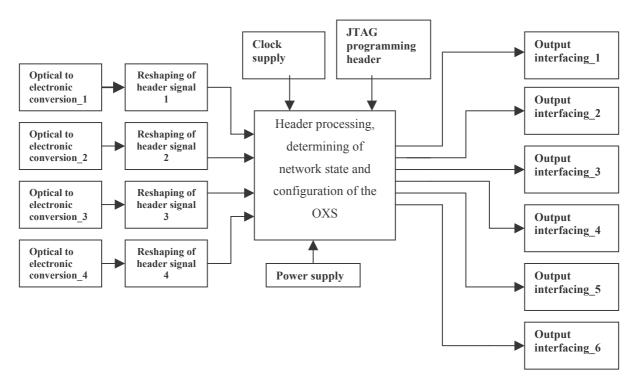

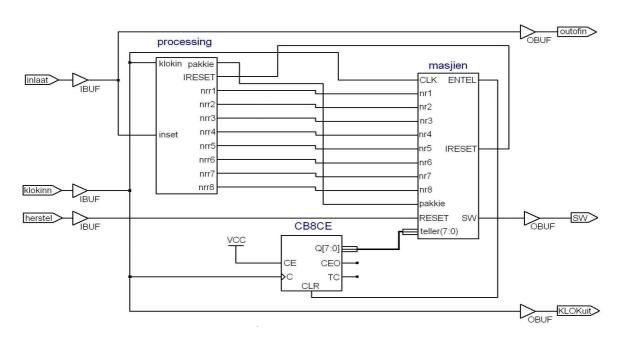

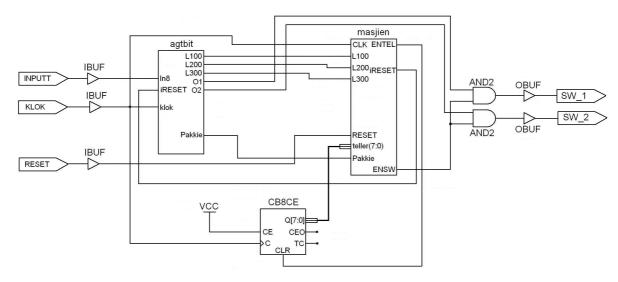

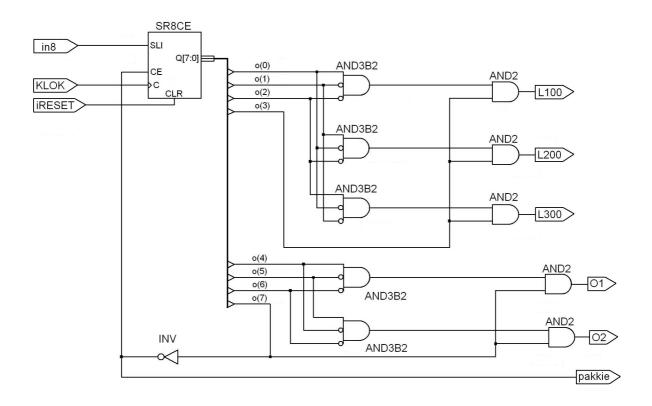

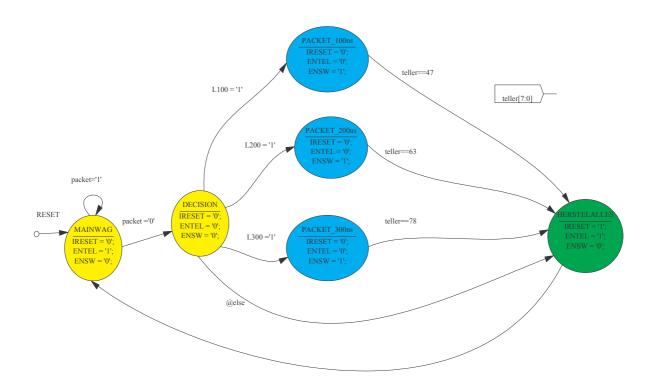

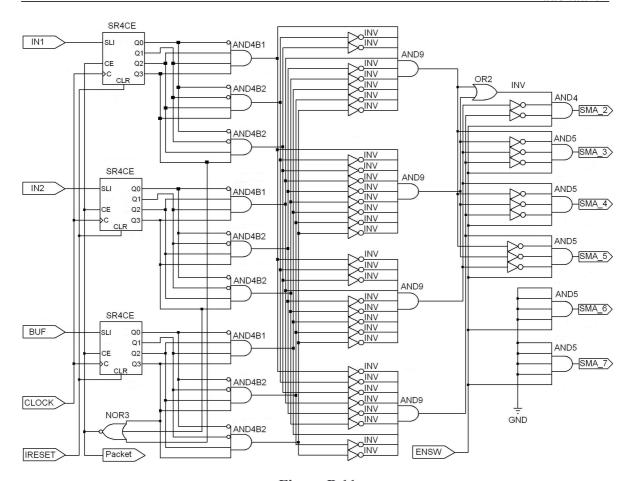

The functional block diagram is given in Figure 3.2. Firstly the four optical inputs are converted to the electronic domain. These four inputs represent the four inputs to the OXS and will carry the header signals of the packets. When converted to the electronic domain, they need to be reshaped before entering the processing unit. The processing is done and will require some DC power levels, a clock signal and a communication link to be programmed with. After the processing has been done, six output interfaces are required to send control signals to the OXS.

Figure 3.2

Functional block diagram of the electro-optic control interface

#### 3.4.1 The PINFETs

The term PINFET (p-intrinsic-n Field-Effect Transistor) indicates the integration of a PIN photodiode with a high-performance trans-impedance amplifier. The PINFET is constructed of InGaAs (Indium Gallium Arsenide) with a high responsivity in the 1100 nm to 1600 nm wavelength range. Light is coupled into the detector through a single mode optical fibre

pigtail. The fibre pigtail is actively aligned with the detector and soldered in place to provide a stable coupling mechanism.

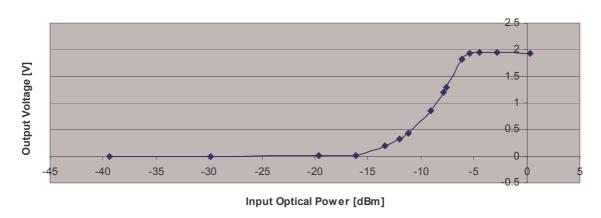

The PINFET photodiode was chosen over the PIN photodiode because of its low sensitivity of -35 dBm, high bandwidth of 350 Mbits/s, responsivity of 0.95 A/W at 1550 nm and typical output voltage level of 2.5V, DC coupled. The PIN, on the other hand, has similar specifications, can support a bandwidth up to 2.5 Gbits/s and with typical output voltage levels of 0.5V, AC coupled. The main reason for choosing the PINFET was its high output DC coupled voltage level. Although the PIN photodiode has a bandwidth of 2.5 Gbit/s, its output voltage is too low and electronic processing of signals at this high data rate is not required. The output voltage characteristic of the PINFET photodiode was tested at a reverse detector bias of -5 V and supplying the trans-impedance amplifier with only +3.3 V. The results are shown in Figure 3.3. The PINFETs are supplied in a 14-pin dual in-line package offering high reliability.

#### Output Voltage vs. Input Optical Power

Figure 3.3

The output voltage characteristics of the PINFET [46]

The experiment was done by increasing the current through a 1550 nm laser diode and connecting the output of the laser to a 3 dB coupler. One of the coupler's outputs was connected to the optical power meter while the other output was connected to the PINFET. The results clearly show that if an optical input power level of about –5 dBm (for high) and optical input power of –20 dBm (for low) enter the PINFET, the resulting output voltage is 1.95 V for a high or '1' and 0 V for a low or '0'.

Chapter 3

By supplying the trans-impedance amplifier with a negative supply voltage, the output voltage's low level was measured at -0.7 V. This signal needs to be processed by a CPLD whose minimum input voltage is -0.3 V and therefore the negative supply of the trans-impedance amplifier was grounded. Four PINFETs were chosen, one for each input to the OXS. Figure A.1 shows the schematic diagram of the biasing of the four PINFETs and the electronic circuit for interfacing the PINFET's output to the CPLD.

Pin 1 of the PINFET is the detector bias input and is supplied with -5 V. Pin 10 is the transimpedance amplifier's positive supply and is connected to the 3.3 V DC supply. A 0.1  $\mu$ F bypass capacitor is connected between pin 1 and ground and also pin 10 and ground to reduce any potential voltage ripples from the power supplies. Pin 7 is the output from the transimpedance amplifier and is fed to the positive input of the voltage comparator. This output is seen as an analogue signal and is converted to a digital signal by the comparators. Pins 3, 4, 5 and 8 are grounded. The name of the ground is AGND, referring to the analog ground plane. A 110  $\Omega$  (refer to section 3.5.4 for the calculations) resistor matches the PINFET's output to the PCB's track impedance. These resistors are named M15, M16, M17 and M18. Pins 2, 6, 9, 11-14 are not connected. The blue lines on Figure A.1 represent the single mode optical fibres entering the PINFETs.

# 3.4.2 The voltage comparators

The output from the PINFET needs to be converted/interfaced to the input port of a CPLD so the signal can be processed. The CPLD accepts inputs with a low voltage level at 0 V and a high voltage level at 3.3 V. Therefore the 0 V to 1.95 V signal from the PINFET needs to be converted to a 0 V to 3.3 V signal. The two ways of doing this at 155 Mbits/s include the use of an ultra-fast voltage comparator or voltage amplifier with high gain causing saturation at 3.3 V. The output from the PINFETS, although it is digital information, is regarded as an analog signal. Therefore analog-to-digital conversion, or to be more precise, reshaping of the analog signal, should also be done to ensure the input to the CPLD is a high-quality digital signal. The best-suited component for this job was defined as the AD8611 – ultra-fast single supply voltage comparator. The AD8611 has a rise time of 2.5 ns and a fall time of 1.1 ns and is therefore capable of supporting digital signals at a bandwidth of 155 Mbits/s. The schematic diagram of these four AD8611 microchips interfacing with the PINFETS is shown in Figure

Chapter 3

Electronic Control Design

A.1. The input from the PINFET is connected to pin 2 (+IN) of the AD8611. The negative input (-IN) of the AD8611 is biased with a reference voltage of 0.97 V. A simple voltage division circuit created this 0.97 V. A 10 k $\Omega$  resistor, connected to 5 V, in series with a 2400  $\Omega$  resistor, connected to ground, results in 0.97 V between the two resistors and is supplied to (-IN). The 0.97 V was chosen as the reference since it is halfway between the minimum and maximum voltage that will enter the AD8611 from the PINFET. Pins 4, 5 and 6 are grounded. Pin 1 is connected to the positive power supply of 5 V.

A 1  $\mu F$  bypass capacitor is placed between the positive power supply pin and ground. Another 10 nF ceramic capacitor is placed as close as possible to the device in parallel with the 1  $\mu F$  bypass capacitor. The 1  $\mu F$  capacitor will reduce any potential voltage ripples from the power supply and the 10 nF capacitor acts as a charge reservoir for the comparator during high frequency switching. Pin 8, an inverse of the output, is left unconnected. Pin 7 is the output with a voltage level of 0 V for a low and 3.3 V for a high. This output is connected to the CPLD as input. Two 100  $\Omega$  resistors, one at the AD8611 side and one at the CPLD side, provide matching to the PCB track of 110  $\Omega$ .

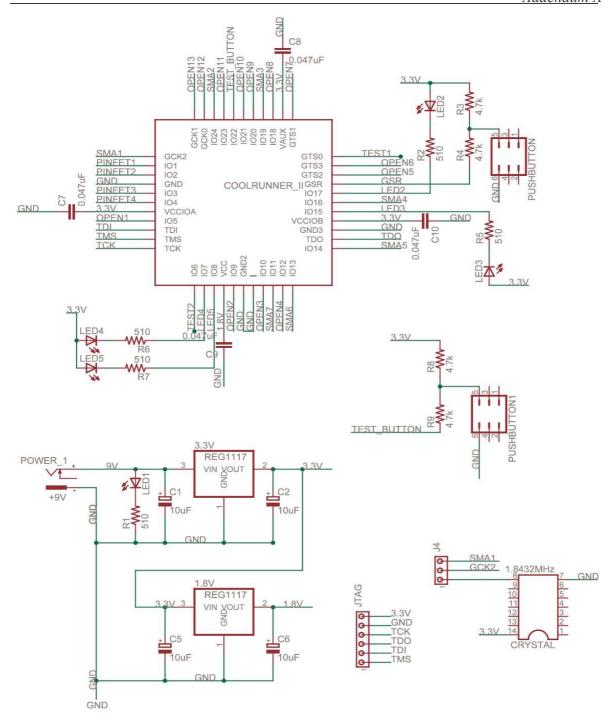

#### **3.4.3 The CPLD**

A CPLD was chosen to do the processing. It is defined as the industry's best and fastest CMOS CPLD. The Xilinx CoolRunner-II CPLDs are fabricated on 0.18 micron process technology. CoolRunner-II CPLDs employ a design technique that makes use of CMOS technology in both the fabrication and design methodology. This design technology, also known as RealDigital, employs a cascade of CMOS gates to implement the sum of products instead of traditional sense amplifier methodology.

A Xilinx CoolRunner-II XC2C32 CPLD in a VQ44 package has a 3 ns pin-to-pin logic delay and can support system frequencies up to 333 MHz. It has 33 input/output pins and was identified as the best CPLD for the design. The other two types of packages included the PC44 and CP56. The VQ44 with its surface mount pins promised to be the best solution. The schematic diagram of the CPLD with its connections to the rest of the schematic diagram is show in Figure A.2.

The CPLD is clocked in one of two ways. The user can select the option by selecting the correct configuration for header J4. Refer to the schematic diagram in Addendum B, Figure B.1. The first option is the on-board 1.8432 MHz clock mostly used for testing the board and low-speed applications. The second option is an external clock via the SMA1 connector that uses pin GCK2 of the CPLD. This option will be used to connect an external 155 MHz clock signal to the circuit.

The main power supply to the CPLD is the 1.8V supplied to pin VCC. The VCCOIA and VCCOIB power pins are supplied with 3.3 V and define the input and output voltage levels for the CPLD. The VAUX pin is also supplied with 3.3 V and is also known as the JTAG supply voltage. Each of these four power pins is supplied with a 0.047 µF capacitor that serves as a charge reservoir for the CPLD during high-frequency switching. The reset pin (GSR) is connected to a push button. It is always high but when pressed, makes pin GSR low, resulting in a reset. Four LEDs and one other push button are also connected to the CPLD to assist in debugging and testing of the CPLD. The JTAG programming header also connects to the CPLD on the corresponding pins. The CPLD is programmed from a computer. The computer needs a parallel port. The JTAG programming cable acts as the interface between the computer and the circuit with its parallel connector and 6-pin header connector.

# 3.4.4 Power supply

The CPLD is supplied with a different power source than the PINFETs and comparators. The reason is that different voltage levels are required and it is necessary to reduce the noise from different parts of the circuit (analogue and digital side). For the CPLD an LM-1117-3.3 V regulator is used together with an LM-1117-1.8 V regulator. The PINFETs and comparator are supplied with 5 V from an LM7805CT, with 3.3 V from an LM-1117-3.3 V and with -5 V from an LM7905CV regulator. All the regulators have 10  $\mu$ F bypass capacitors connected just before the input of the regulator to reduce any potential voltage ripples from the main power supplies. A 10  $\mu$ F tantalum capacitor on the output port of the regulator is for proper operation and to improve high frequency load regulation. A high-quality tantalum capacitor was used to ensure that the ESR (effective series resistance) is less than 0.5  $\Omega$ .

# 3.4.5 The SMA output ports

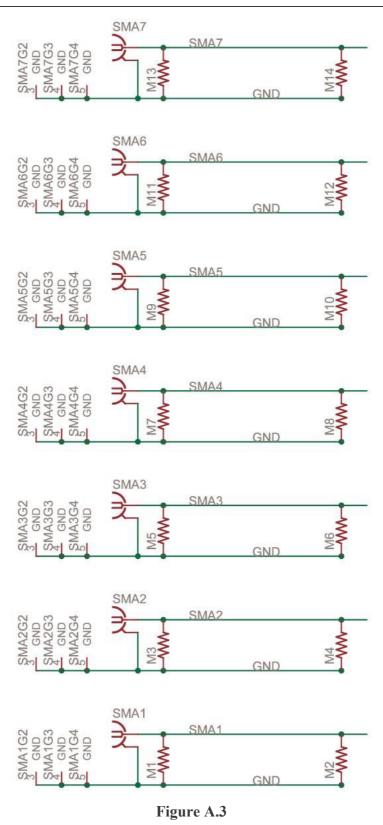

The circuit has seven SMA connector outputs connected directly from six of the CPLD's output ports. The seventh one is used for the 155 MHz clock and is connected to the CPLD's GCK2 port. Space is reserved for two matching resistors, one on the CPLD's side and one on the SMA's side. These are to ensure the circuit is matched to the transmission line. The circuit diagram of the SMA outputs is shown in Figure A.3.

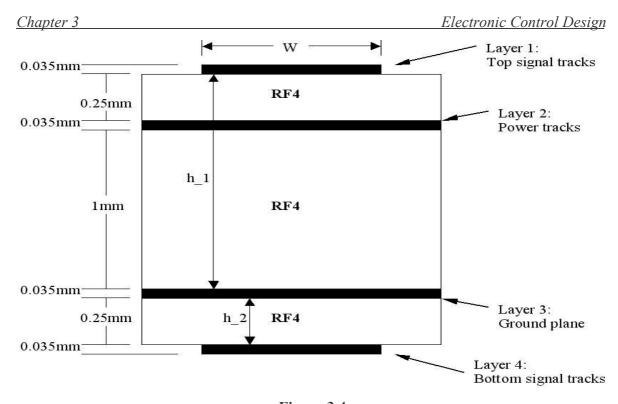

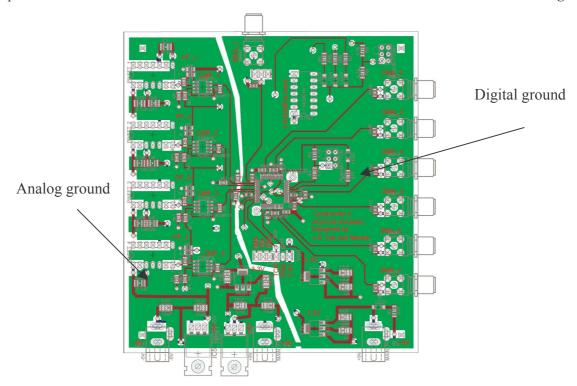

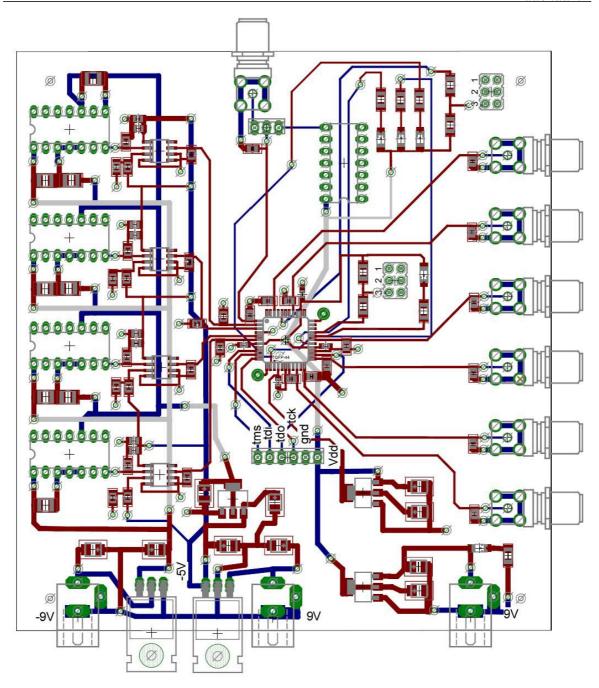

# 3.5 Printed circuit board design

The schematic diagram of the electronic circuit was physically implemented onto a PCB. Owing to the high-speed (155 Mbit/s) requirement of the control electronics, the physical characteristics of implementing the design onto the PCB contributes to the behaviour of the circuit just as much as the parts of the electrical design that are included in the schematics. Physical characteristics such as impedance matching, transmission line propagation, delay, characteristic impedance ( $Z_0$ ), PCB material, relative permittivity or dielectric constant ( $\varepsilon_T$ ), size, stack-up, placement of components, packaging and grounding are not all included in the schematic diagram and must be taken care of when designing the PCB from the schematic diagram. If not seriously considered they will lead to problems with signal integrity. The main concern in PCB design is the characteristic impedance of the high-speed signal tracks, how many layers will be used in the PCB and how will they be stacked on top of one another.

The two losses of greatest concern are caused by signal reflections, due to impedance mismatch or impedance changes and the loss of signal energy into the dielectric of the material. The loss tangent (tan  $(\delta)$ ) is a measure of how much of the signal pulse (electromagnetic wave) propagating down the PCB transmission line will be lost in the dielectric region (insulating material between copper layers). Relative permittivity ( $\epsilon_r$ ) is a measure of the effect an insulating material has on the capacitance of a conductor embedded in the material or surrounded by it. It is also a measure of the degree to which an electromagnetic wave is slowed down as it travels through the insulating material. The higher the relative permittivity, the slower a signal travels on a trace. The amount of signal loss in a circuit is not only a function of material type but is also a function of frequency and line length in or on the PCB.

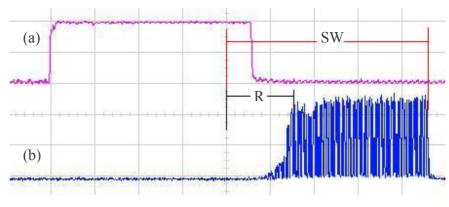

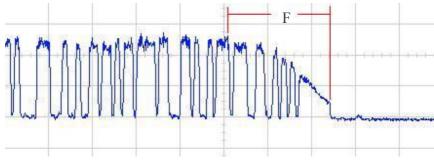

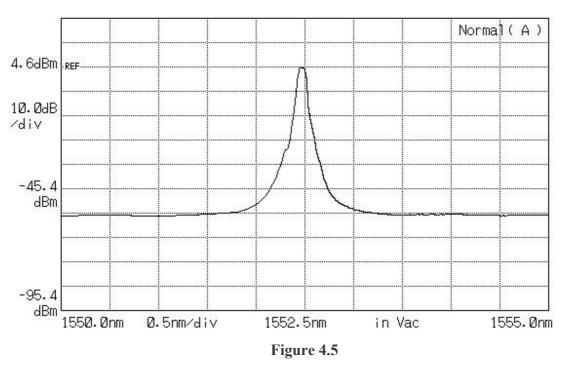

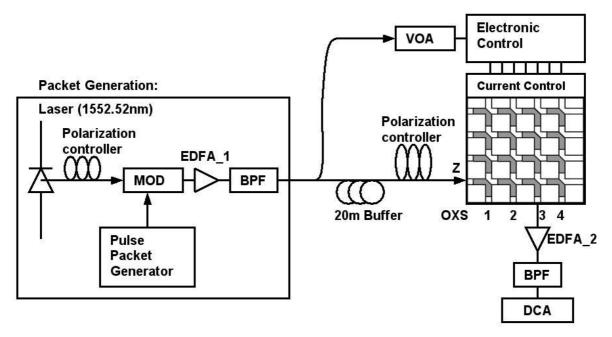

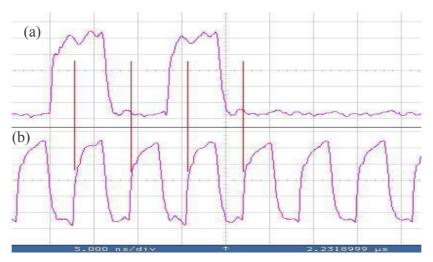

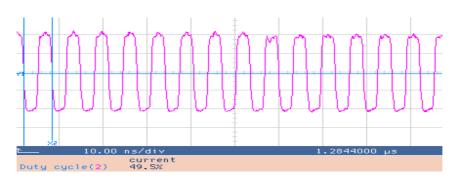

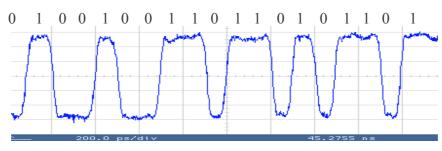

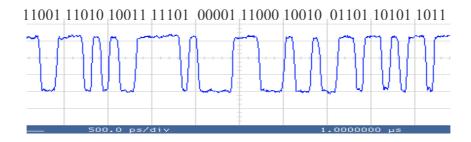

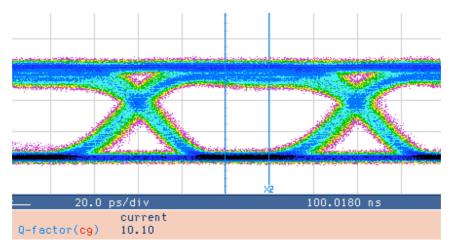

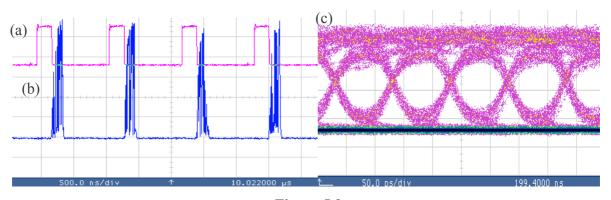

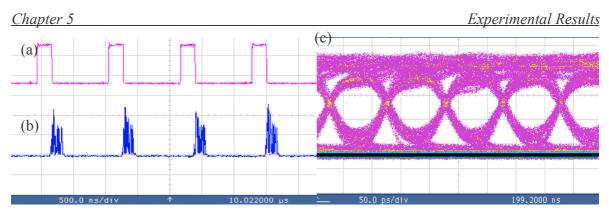

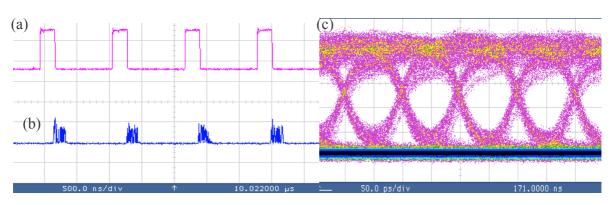

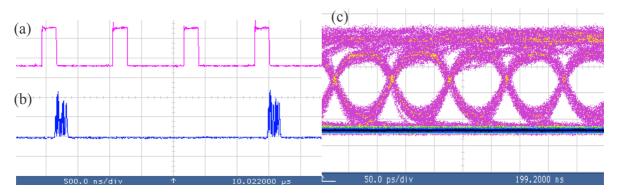

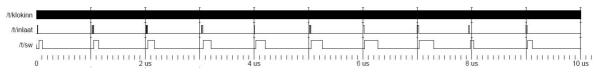

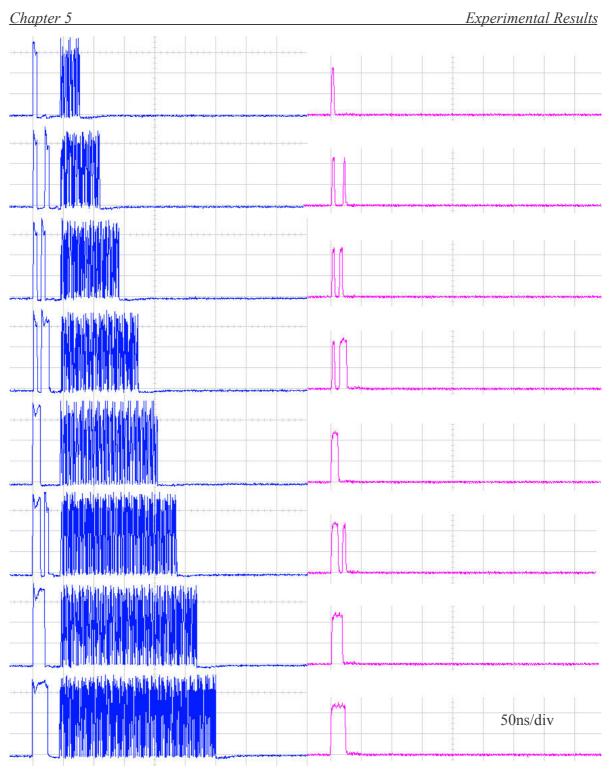

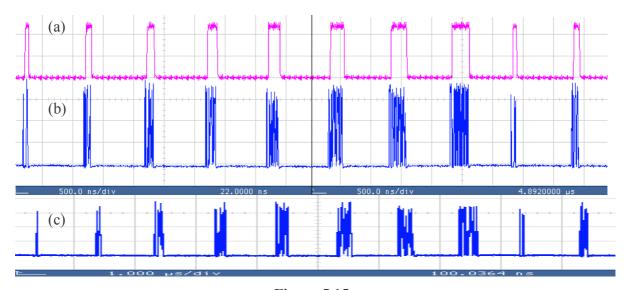

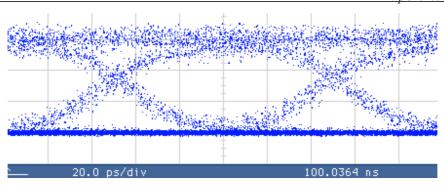

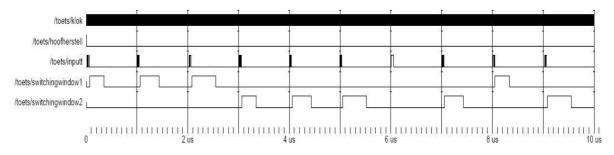

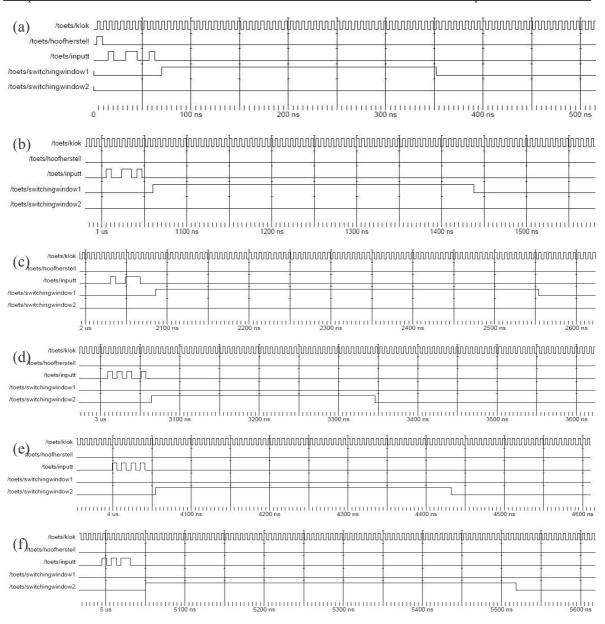

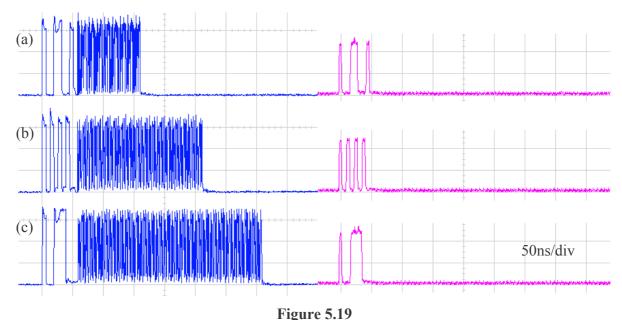

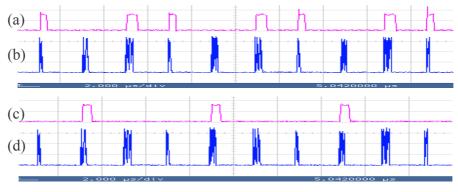

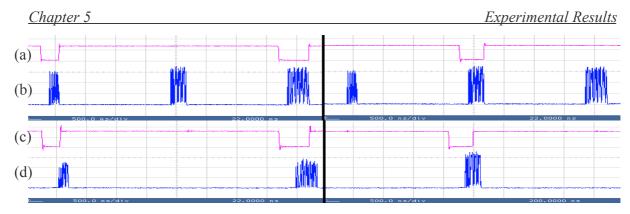

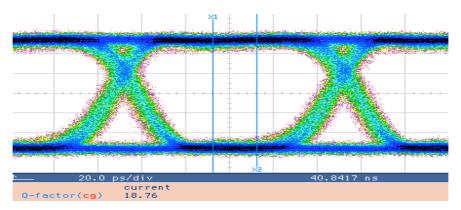

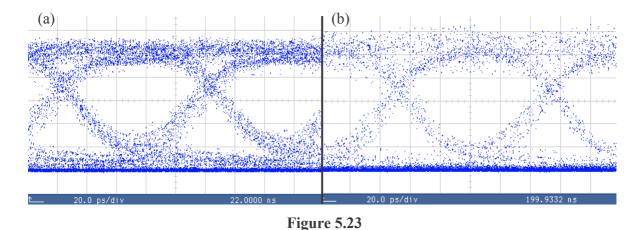

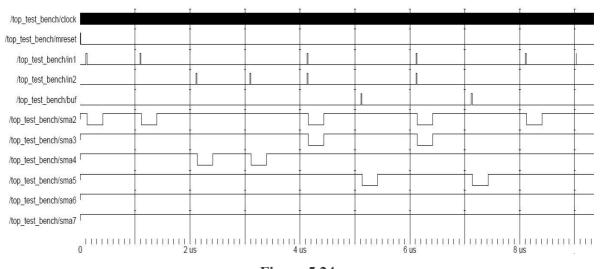

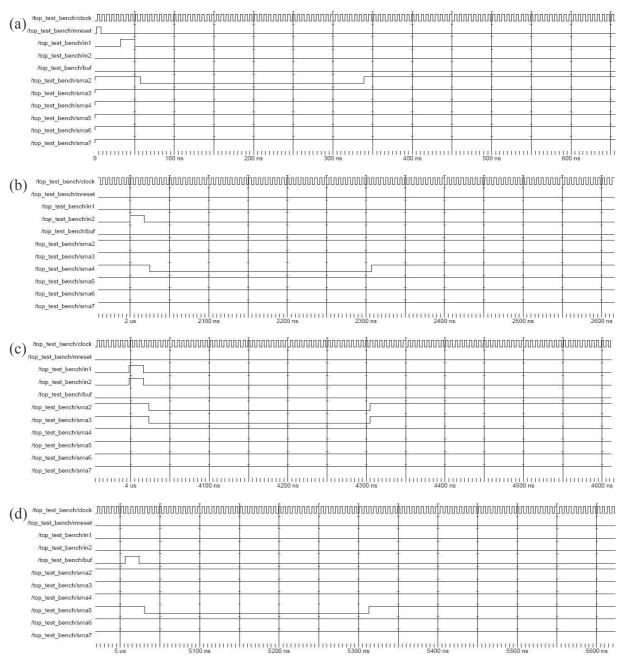

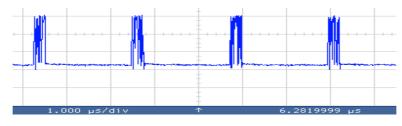

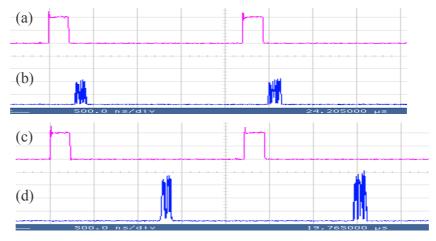

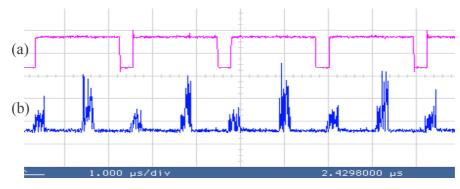

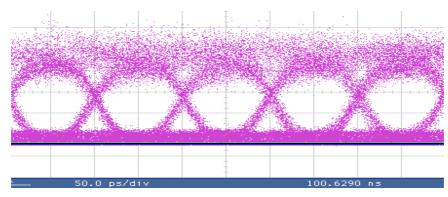

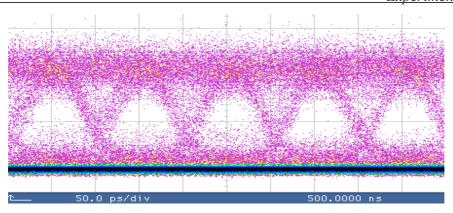

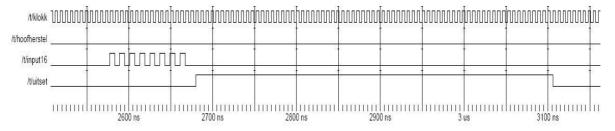

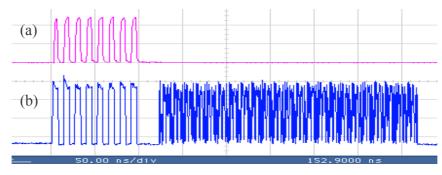

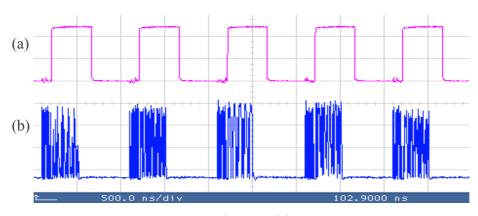

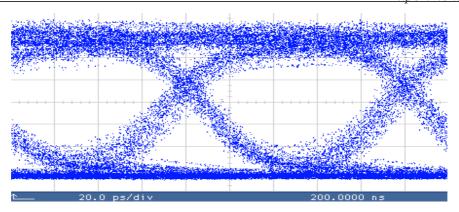

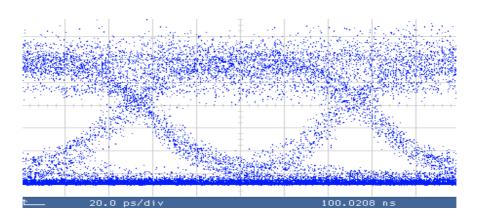

# Chapter 3