## REFERENCES

[1] A. Collins, "Solid State Solutions for Electricity Metrology", IEE Metering and Tariffs for Energy Supply, no. 462, pp. 1, May 1999.

[2] W. Koon, "New Developments in Current Sensors in Solid State Meters", Metering. International Magazine, Issue 3, pp. 50 – 52, 2001.

[3] http://www.loadcontrols.com/application\_notes/pdfs/power\_sensors&\_load\_control.pdf

[4] A. Bilotti, "Monolithic Magnetic Hall Sensor Using Dynamic Quadrature Offset Cancellation", IEEE journal of solid-state circuits, vol. 32, no. 6, pp. 829-836, June 1997.

[5] G. Bjorklund, "Improved Design of Hall Plates for Integrated Circuits", IEEE Transactions on Electron Devices, Vol. ED-25, No. 5, May 1978.

[6] Y. Kanda and M. Migitaka, "Effect of mechanical stress on the offset voltage of Hall devices in Si IC", Phys. Status Solidi (a), vol. 35, pp. K115-K118, 1976.

[7] M. Ai and M. Shimazoe, "Cantilever-type Displacement Sensor using Diffused Silicon Strain Gauges", Sensors and Actuators, 2, pp. 207-307, 1982.

[8] R.S. Popović (B.E. Jones), "Hall Effect Devices, Magnetic Sensors and Characterization of Semiconductors", Adam Hilger, Bristol, England, 1991.

[9] R.S. Popovic, "Hall-Effect Devices", Sensors and Actuators, 17, pp. 39-45, 1989.

[10] G.S. Randhawa, "Monolithic Integrated Hall Devices in Silicon Circuits", Microelectronics Journal, vol. 12, no. 6, pp. 24 – 25, 1981.

[11] W. Göpel, J. Hesse and J.N. Zemel, "Sensors, Volume 5, Magnetic Sensors", VCH Publishers Inc., New York, USA, 1989.

[12] B. Drafts, "A Tutorial on Hall Sensors", http://fwbell.com/Cataglogs/Sesnors/Hall\_Sensors/Hall\_sensor\_Tutorial/hall\_sensor\_tutorial. html, pp1 - 6, 2001.

[13] "Hall Effect Sensing and Application", Honeywell Inc, Illinois.

[14] J. Gilbert, "Technical Advances in Hall-Effect Sensing", Sensors EXPO, Technical Paper STP 00-1, Anaheim, pp. 1 – 6, May 2000.

[15] P. Emerald, "'Non-Intrusive' Hall-Effect Current-Sensing Techniques Provide Safe,

Reliable Detection and Protection for Power Electronics", International Appliance Technical

Conference, Ohio State University, Technical Paper STP 98-1, pp. 1 – 18, May 1998.

[16] J. Gilbert, "Hall-Effect IC Applications Guide", Allegro MicroSystems, Inc., Application Note 27701B, pp. 1 – 34.

[17] P.M. Drljaca, V. Schlageter, F. Vincent and R.S. Popović, "High Sensitivity Hall Magnetic Sensors Using Planar Micro and Macro Flux Concentrators", The 11<sup>th</sup> International Conference on Solid-State Sensors and Actuators, Munich, Germany, June 2001.

[18] CEI/IEC International Standard 1036, "Alternating current static watt-hour meters for active energy (classes 1 and 2)", Edition 2, 1996.

[19] D. Ebel, "Modern measurement techniques for verifying electricity meters and measuring loads on site", Metering International Magazine, Issue 4, pp. 15 – 19, 1997.

[20] S. Kasap, "Hall Effect in Semiconductors", Special Custom Published e-Booklet, pp. 1 –5, November 2001.

[21] C. Scott, "High accuracy magnetic field measurement using silicon Hall sensors", Swiss Institute of Technology Lausanne, 1995.

[22] R.F. Wick, "Solution of the field problem of the Germanium gyrator", Journal of Applied Physics, Vol. 25, pp. 741 – 756, 1954.

[23] A. Bakker, S. Bellekom and S. Middelhoek, "Low-Offset Low-noise 3.5 mW CMOS Spinning-Current Hall Effect Sensor with Integrated Chopper Amplifier", Physical Sensor Applications, 28C2, pp. 1045-1048, September 1999.

[24] S. Bellekom, S. Yin and A. Bakker, "Spinning-current Hall plate with integrated switches", Proceedings of the ProRISC Workshop Circuits, Systems and Signal Processing, pp. 37-42, 1997.

[25] A. Bakker, K Thiele and J.H. Huijsing, "A CMOS Nested-Chopper Instrumentation Amplifier with 100-nV Offset", IEEE Journal of Solid-State Circuits, Vol. 35, no. 12, December 2000.

[26] T. Hara, N. Mihara, N. Toyoda and M. Zama, "Highly linear GaAs Hall devices fabricated by ion implantation", IEEE Trans. Electron Devices, Vol. ED-29, pp. 78-82, 1982.

[27] J.W.A. von Kluge, "Analysis of split-current magnetic field sensitive resistors", Sensors and Actuators, A 3054, pp. 5, 2001.

[28] B. Razavi (W. Stephen), "Design of Analog CMOS Integrated Circuits", McGraw-Hill, New York, pp. 100 – 369, 377 – 397 and 418 – 422, 2001.

[29] P.E. Allen and D.R. Holberg, "CMOS Analog Circuit Design", Saunders College Publishing, Orlando, Florida, pp. 197 - 240 and 365 - 387, 1987.

[30] A. Bakker and J.H. Huijsing, "A CMOS Chopper Opamp with Integrated Low-Pass Filter", Proceedings of the ProRISC Workshop on Circuits, Systems and Signal Processing, pp. 25 – 28, 1997.

[31] M. Degrauwe, E. Vittoz and I. Verbauwhede, "A Micropower CMOS-Instrumentation Amplifier", IEEE Journal of Solid-State Circuits, Vol. SC-20, no. 3, June 1985.

[32] R.C. Yen and P.R. Gray, " A MOS Switched-Capacitor Instrumentation Amplifier", IEEE Journal of Solid-State Circuits, Vol. SC-17, no. 6, December 1982.

[33] South African Micro-Electronic Systems, "Single Phase Bi-directional Power / Energy Metering IC with Instantaneous Pulse Output", <u>http://www.sames.co.za/energy/sa2002h.pdf</u>, pp. 1 – 12, 2002.

[34] Analog Devices, "Energy Metering IC with Pulse Output", http://www.analog.com/productSelection/pdf/ADE7755\_0.pdf, pp. 1 – 16, 2002.

# ADDENDUM A: 1.2µM CMOS PROCESS PARAMETERS

## CMOS1.2 Process

2.0µ 2.0µ 1.2µ 1.8µ 3.0µ 2.0µ 2.0µ 7µ 9µ

|                   | Physical Cl           | naracteristics    | cs |  |  |

|-------------------|-----------------------|-------------------|----|--|--|

| Process Geometry  | 1.2 Micron            | Metal II Width    |    |  |  |

| Process Number    | C1201(S.M)/C1202(D.M) | Metal II Space    |    |  |  |

| Operating Voltage | 5v                    | Gate Poly Width   |    |  |  |

| Well Doping       | N-WELL                | Gate Poly Space   |    |  |  |

| Metal Layers      | 2                     | Bottom Poly Width |    |  |  |

| Poly Layers       | 2                     | Bottom Poly Space |    |  |  |

| Contact           | 1.5µ                  | N+/P+Space        |    |  |  |

| Via               | 1.5µ                  | N+ to N-WELL      |    |  |  |

| Metal I Width     | 2.0µ                  | N+ to P+          |    |  |  |

| Metal I Space     | 2.0µ                  |                   |    |  |  |

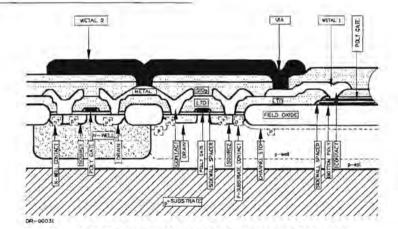

#### CROSS SECTIONAL VIEW OF THE CMOS1.2 PROCESS

# CMOS1.2 Process

### **Electrical Characteristics**

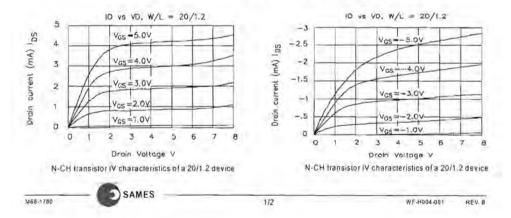

| n-ch transistor<br>Parameters              | Sym                 | Min  | Тур   | Max  | Unit              | otherwise noted)<br>Comments |

|--------------------------------------------|---------------------|------|-------|------|-------------------|------------------------------|

| Threshold Voltage (linear                  | VTON                | 0.55 | 0.75  | 0.95 | V                 | 100/1.2 device               |

| extrapolated)                              | . N                 |      |       |      |                   |                              |

| Body Factor                                | 9                   |      | 0.35  |      | V 1/2             | 100/1.2 device               |

| Conduction factor (normalized)             | b <sub>N</sub>      | 60   | 75    | 90   | µA/V²             | 100/100 device               |

| Effective Channel Length                   | Leff <sub>N</sub>   | 0.7  | 0.9   | 1.1  | μm                | 100/1.2 device               |

| Width Encroachment                         | DWN                 |      | 0.6   |      | μm                | perside                      |

| Punch Through Voltage                      | BVDSSN              | 9    |       | 1    | V                 | 100/1.2 device               |

| Poly Field Threshold                       | VTF <sub>P(N)</sub> | 10   |       |      | V                 |                              |

| Threshold Voltage Offset<br>(two sigmas)   | DVT <sub>N</sub>    |      | 5     |      | mV                | 100/10 device                |

| p-ch transistor                            |                     |      |       |      |                   | No                           |

| Threshold Voltage (linear<br>extrapolated) | VTO <sub>P</sub>    | -1.1 | -0.9  | -0.7 | V                 | 100/1.2 device               |

| Body Factor                                | g.                  |      | 0.4   |      | V 1/2             | 100/1.2 device               |

| Conduction Factor (normalized)             | D <sub>p</sub>      | 20   | 25    | 30   | µA/V <sup>2</sup> | 100/100 device               |

| Effective Channel Length                   | Leffp               | 0.8  | 1.0   | 1.2  | μm                | 100/1.2 device               |

| Width Encroachment                         | DWp                 |      | 0.6   |      | μm                | per side                     |

| Punch Through Voltage                      | BVDSS <sub>P</sub>  |      |       | -9   | V                 | 100/1.2 device               |

| Poly Field Threshold                       | VTF                 |      |       | -10  | V                 |                              |

| Threshold Voltage Offset<br>(two sigmas)   | DVTp                |      | 5     | 11.2 | mV                | 100/10 device                |

| diffusion & thin films                     |                     |      |       |      |                   |                              |

| Well (field) Sheet Resistance              | R <sub>w(+1)</sub>  | 0.5  | 1     | 1.5  | k₩□               | n-well                       |

| N+ Sheet Resistance                        | R <sub>N+</sub>     | 20   | 30    | 40   | W/ 🗆              |                              |

| N+ Junction Depth                          | X <sub>IN</sub> ,   |      | 0.3   | 1    | μm                |                              |

| P+ Sheet Resistance                        | R <sub>p</sub> ,    | 60   | 80    | 100  | W/D               |                              |

| P+ Junction Depth                          | X                   |      | 0.3   |      | μm                |                              |

| Gate Poly Sheet<br>Resistance (n-ch)       | RPOLYN              | 15   | 25    | 35   | WD                |                              |

| Gate Poly Sheet<br>Resistance (p-ch)       | RPOLYP              | 15   | 25    | 35   | ₩□                |                              |

| Bottom Poly Sheet Resistance               | RPOLYB              | 15   | 25    | 35   | W/D               |                              |

| Metal 1 Sheet Resistance (SLM)             | R <sub>M1</sub>     |      | 30    |      | mW/D              |                              |

| Metal 1 Sheet Resistance (DLM)             | R <sub>M2</sub>     |      | 50    |      | mW/□              |                              |

| Metal 2 Sheet Resistance (DLM)             | R <sub>M2</sub>     |      | 30    | 11   | m W/🗆             |                              |

| capacitance                                |                     |      |       |      |                   |                              |

| Gate Oxide                                 | C <sub>ox</sub>     | 1.28 | 1.38  | 1.58 | fF/µm²            |                              |

| Poly Gate To Bottom Poly                   | C <sub>PP</sub>     | -    | 0.86  |      | fF/µm²            | interpoly capacito           |

| Metal 1 to Poly                            | CMIP                |      | 0.057 | 1    | fF/µm²            |                              |

| Metal 2 to Metal 1                         | C <sub>MM</sub>     |      | 0.035 |      | fF/µm²            |                              |

M68-1780

SAMES -

-212-

Electrical, Electronic and Computer Engineering

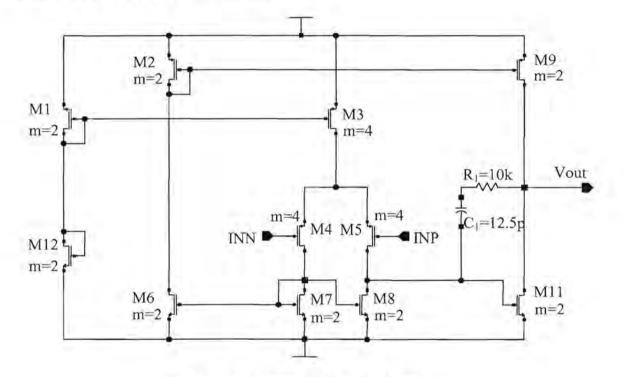

# **ADDENDUM B: OPERATIONAL AMPLIFIER DESIGN**

Specifications:

- $V_{DD} = 5 \text{ V}$

- $A_{V(opoen-loop)} > 80 \text{ dB}$

- UGBW prod = 1 MHz (stable)

- Slew-rate =  $2V/\mu s$

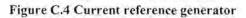

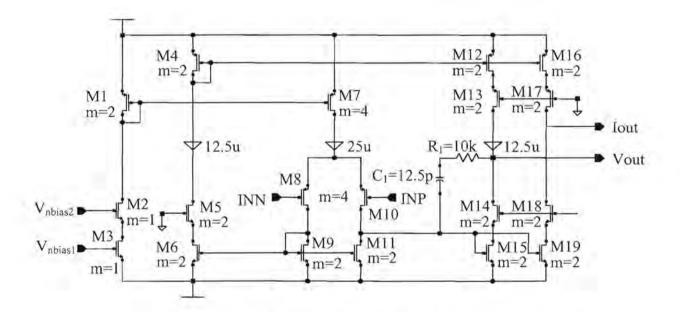

Figure B.6.1 shows the proposed circuit.

Design equations:

$$\frac{SR}{UGBW} = 2\pi \left( V_{GS} - V_t \right) \tag{B.1}$$

$$V_{GS} = \frac{SR}{\left(2\pi \left(UGBW\right)\right)} + V_i \tag{B.2}$$

$$A_{\nu} = (A_{\nu_1})(A_{\nu_2})(1) \tag{B.3}$$

#### Addendum B

The input stage's gate-source voltage can thus be calculated from equation B.3 as

UNIVERSIT

UNIVERSITY OF PRETORIA YUNIBESITHI YA PRETORIA

$$V_{GS5} = \frac{2}{2\pi} + 1.0 \tag{B.4}$$

= 1.318V

but, we know that

$$A_{\nu_1} = g_{m5}(r_{o5} || r_{o8})$$

=  $\frac{g_{m8}}{g_{o8} + g_{o5}}$  (B.5)

where,

$$g_{m5} = \sqrt{\left(2I_{D5}k_{p}.\frac{W_{5}}{L_{5}}\right)}$$

(B.6)

$$g_{o5} = \frac{I_{D5}}{V_{AP}} \tag{B.7}$$

$$g_{o8} = \frac{I_{D8}}{V_{AN}}$$

(B.8)

$$I_{D8} = I_{D5}$$

(B.9)

$$A_{\nu 1} = \frac{\sqrt{\left(2I_{D5}k_{p}\frac{W_{5}}{L_{5}}\right)}}{\left(\frac{2I_{D5}}{V_{AP}}\right)}$$

(B. 10)

$$A_{P2} = \frac{\sqrt{\left(2I_{D11}k_{n}\frac{W_{11}}{L_{11}}\right)}}{\left(\frac{2I_{D11}}{V_{dN}}\right)}$$

(B.11)

and so too,

thus,

where,

$$I_{D11} = I_{D5} = \frac{I_3}{2} = 12.5 \,\mu\mu$$

(B. 12)

But we know that  $\frac{W_{11}}{L_{11}} = 7$ , from the bias ratios and thus from equation B.3,

$$A_{\nu} = 95dB \approx 56000$$

=  $A_{\nu 1}A_{\nu 2}$

=  $\frac{\sqrt{\left(2I_{D5}k_{p}\frac{W_{5}}{L_{5}}\right)}}{\left(\frac{2I_{D5}}{V_{AP}}\right)} \times \frac{\sqrt{\left(2I_{D11}k_{n}\frac{W_{11}}{L_{11}}\right)}}{\left(\frac{2I_{D11}}{V_{AN}}\right)}$  (B. 13)

From this we can calculate  $\frac{W_5}{L_5}$  < 46.1. A width/length ratio of approximately  $\frac{W_5}{L_5}$  = 38,

was chosen such as to accommodate for the 1.2  $\mu$ m process. This will assist in the matching of the devices within the operational amplifier. M<sub>4</sub> is biased the same as M<sub>5</sub> and symmetry is required in the differential stage such that the inverting and non-inverting input transistors amplify symmetrically.

$$I_{D11} = \frac{\mu C_{OX}}{2} \frac{W_{11}}{L_{11}} (V_{GS11} - V_{t})^{2}$$

(B. 14)

$$12.5 = \left(\frac{75}{2}\right) (7) (V_{GS11} - 0.7)^2$$

(B. 15)

and thus,

$$V_{GS11} = 0.92 V$$

(B. 16)

As M<sub>8</sub> is biased under the same conditions as M<sub>7</sub>,  $V_{DG} = 0$  and thus M<sub>8</sub> will remain in saturation.

Addendum B

## Compensation

The compensation capacitor needed is calculated from

$$C_{m} = \frac{I_{T}}{SR}$$

$$= \frac{25\mu A}{2V/\mu/}$$

$$= 12.5 nF$$

(B. 17)

The resultant pole positions are thus as follows;

$$p_{1} = \frac{1}{((C_{m} + C_{2})R_{2} + (C_{1} + C_{m})R_{1} + g_{2}R_{2}R_{1}C_{m})}$$

(B. 18)

But the DC gain of the second stage is high and thus

$$p_1 \approx \frac{1}{(g_2 R_1 R_2 C_m)}$$

(B. 19)

And so;

$$g_{8} = \sqrt{2I_{D5}k_{n}\frac{W_{5}}{L_{5}}}$$

$$= \sqrt{(2)(12.5\mu)(75\mu)(7)}$$

$$= 114.56 \ \mu A/V$$

(B. 20)

$$R_{I} = R_{2} = r_{OP} || r_{ON}$$

$$= \left(\frac{V_{AP}}{I_{D8}}\right) || \left(\frac{V_{AN}}{I_{D8}}\right)$$

$$= \left(\frac{30}{12.5\mu A}\right) || \left(\frac{60}{12.5\mu A}\right)$$

$$= 1.6 M\Omega$$

(B. 21)

$$p_{1} \approx \frac{1}{g_{2}R_{2}R_{1}C_{m}}$$

$$= \frac{1}{(14.56 \ e-6)(1.6 \ e6)(1.6 \ e6)(12.5 \ e-12)}$$

$$= 273 \ Hz$$

(B. 22)

Electrical, Electronic and Computer Engineering

The second pole is given by

$$p_2 \approx \frac{g_8 C_m}{C_1 C_2 + (C_1 + C_2) C_m}$$

(B. 23)

It was given that  $\mu C_{OX}$  for PMOS and NMOS transistors were 25  $\mu$ A/V<sup>2</sup> and 75  $\mu$ A/V<sup>2</sup> respectively. From addendum A the gate capacitance is seen to be 1.4 fF/ $\mu$ m<sup>2</sup> and thus the mobility constants are calculated as  $\mu_e = 536 \text{ cm}^2/\text{Vs}$  and  $\mu_h = 179 \text{ cm}^2/\text{Vs}$ .

Now,

$$C_1 = 112 x 3 x 1.4 e-15$$

(B. 24)

= 470 fF

$$C_2 = 28 x 4 x 1.4 e-15$$

(B. 25)

= 160 fF

$$p_2 = \frac{114.56\,\mu A/V \times 12.5\,pF}{470\,fF \times 160\,fF} + 470\,fF + 160\,fF \times 12.5\,pF \qquad (B.26)$$

$$= 180.1\,MHz$$

As was mentioned before, the zero introduced by the compensation capacitor does influence CMOS operational amplifiers, thus:

$$z = \frac{g_8}{C_m}$$

(B. 27)

$$= \frac{114.56 \ e{-}6}{12.5 \ e{-}12}$$

$$= 9.2 \ MHz$$

This is not to say that the zero will not affect the stability, as more phase is introduced. To ensure this will be the case, a compensation resistor will be implemented with the value of

$$z = \frac{1}{C_m \left(\frac{1}{g_{m2}} - R_z\right)}$$

(B. 28)

Electrical, Electronic and Computer Engineering

Choosing  $R_z > 1/g_{m2}$ , will result in moving the zero from the right half plane to the left half plane close to the second dominant pole, where stability can once again be achieved. Here, the zero contributes to positive phase shift. Thus choosing  $R_z = 10k\Omega$ , results in the zero frequency to be at approximately 10 MHz. This will also affect the UGBW to move as the zero now occurs after the uncompensated RHP zero.

## ADDENDUM C: SYSTEM SCHEMATICS

System Simulation

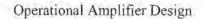

Figure C.1 Schematic illustrating simulation test bench

Figure C.1 illustrates the simulation setup used to simulate the sensor. The voltage divider network can be clearly seen. An external resistor of 50 k $\Omega$  is used for calibrating the current bias circuit. The output of the circuit was loaded with a 2 k $\Omega$  resistance for simpler result calculations.

Addendum C

#### **Power Sensor**

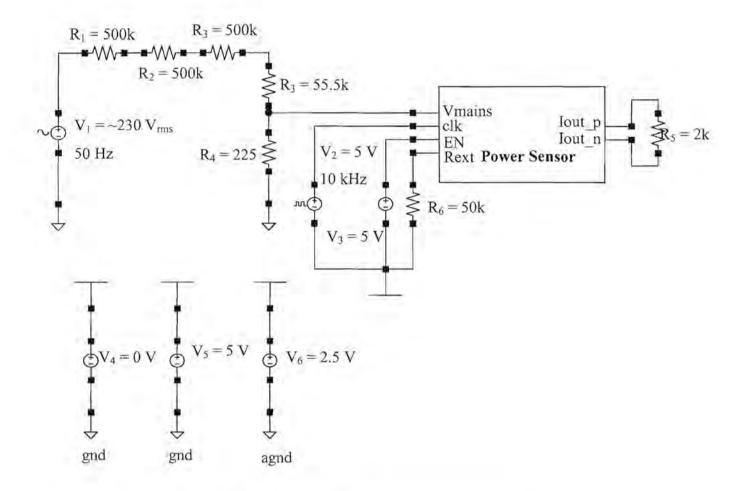

Figure C.2 Schematic of the power sensor system

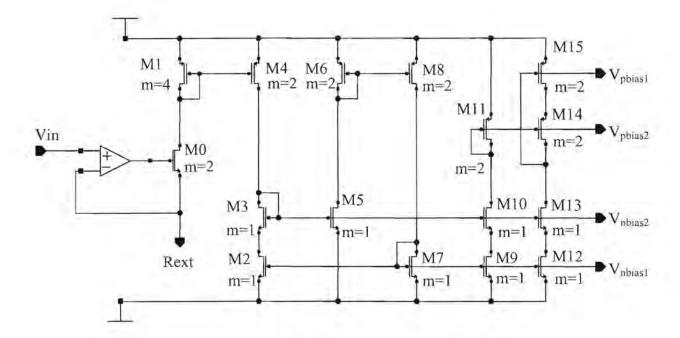

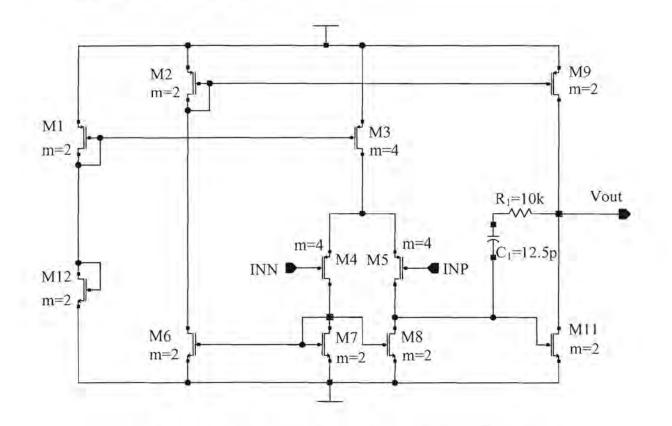

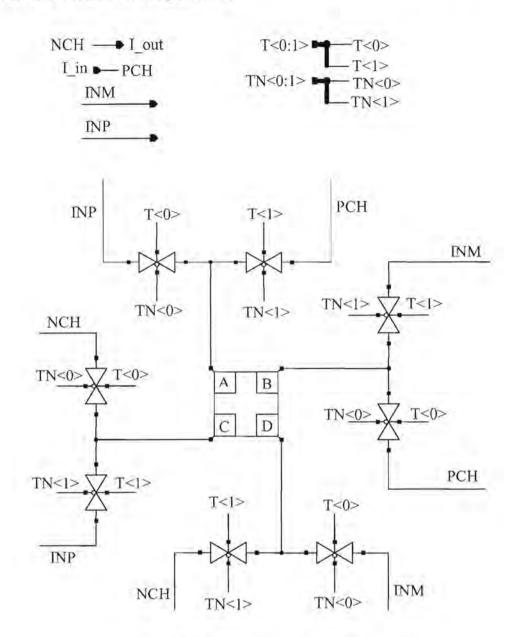

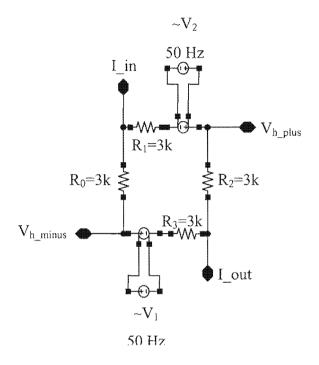

Figure C.2 shows the entire system schematic of the power sensor. The inputs and outputs are indicated in figure C.1. The amplifier biasing circuits comprises of the bandgap generator (figure C.3) and the current reference generator (figure C.4). The current reference generator uses a self-biased amplifier shown in figure C.5. The biasing amplifier (figure C.6) drives the

Hall generator via the transmission gate switches (figure C.8). The switches are configured such that quadrature rotation is implemented on the Hall generator (figure C.9). This amplifier uses two operational amplifiers shown in figure C.7. The Hall output is low passed filtered (figure C.10) and finally amplified by the final output stage (figure C.6). The 4 inverters generate the clock cycles required by the transmission gates.

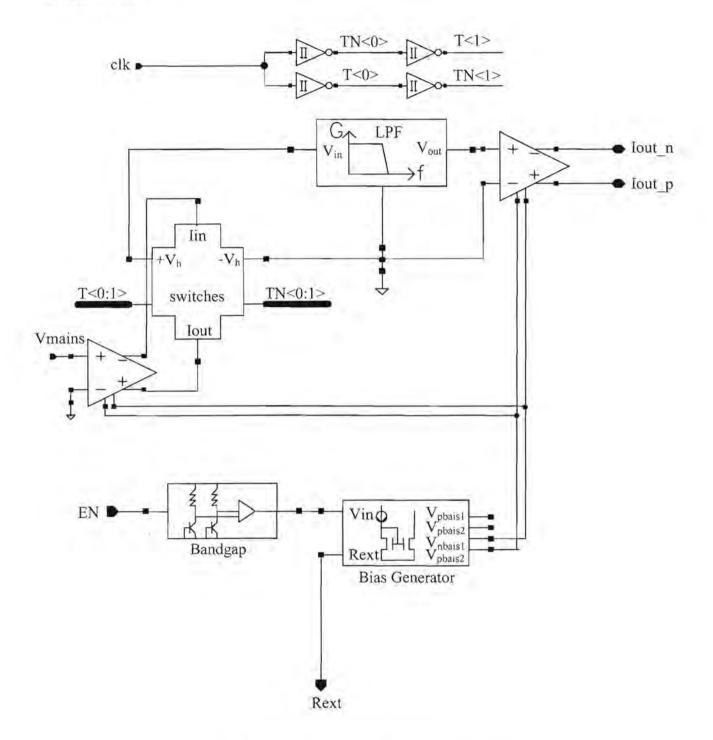

#### **Bandgap** reference

Figure C.3 Bandgap reference schematic

### Current bias generator

### Self biased operational amplifier

Figure C.5 Operational amplifier used in current reference circuit

Addendum C

### Instrumentation amplifier

#### Voltage-to-current converting operational amplifier

#### Figure C.7 Operational amplifier implemented in instrumentation amplifiers

#### Quadrature rotation switching circuitry

Figure C.8 Transmission gate switching circuitry

Addendum C

### Hall generator simulation model

Figure C.9 Hall generator simulation model

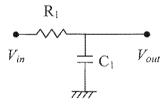

Low pass filter

Figure C.10 Passive low-pass filter

. ..

-----

# ADDENDUM D: LAYOUT LEGEND

N-Well

N-Active

P-Active

Poly 1

Contact

Metal 1

Via

Metal 2