## 1. INTRODUCTION

Generally, solid-state energy meters are based on two types of signal processing, namely analog and digital [1]. This signal processing refers to multiplication and filtering for the extraction of the information required by an energy meter and includes kWhrs, VARS etc. Typical trends are that companies with newer generation technologies can process most signals in the digital domain where older technologies have to utilize analog signal processing techniques to minimize digital circuitry. This is due to the fact that digital circuitry in older technologies tends to dominate final chip size thus making it extremely difficult for companies using these technologies to be competitive within the solid-state energy metering market. Although processing signals digitally assists easier reconfiguration to meet specific local requirements or upgrades, digital signal processing (DSP) comes at a large overhead in circuitry and is unsuitable for companies with older, larger Complementary Metal Oxide Semiconductor (CMOS) processes. For such companies to remain competitive, it is necessary to find a balance between analog and digital signal processing such that integrated circuit area is utilized cost effectively. Hall effect sensors have recently played a major role in finding a balance between the analog and digital domain. Their inherent multiplication properties can be used to calculate the product of the line voltage and current. This directly yields the power vector, which can subsequently be digitized and processed, eliminating the need for large digital multipliers and filters. Multiplication is ultimately executed "free of charge" within the Hall generator through simple signal manipulation.

#### 1.1.1. Current Sensing Techniques

Modern solid-state power meters contain elements for sensing both voltage and current. Voltage sensing is typically achieved by dividing down the line voltage using a resistor divider or a potential transformer when isolation from the line is required. Current sensing however, poses a much more difficult problem. Due to the rich harmonic content in the current waveform, current sensors not only require a much wider measurement dynamic range, but also need to handle a much wider frequency range. There are three common current sensing technologies currently deployed in the market and these include the low resistance current shunt, the current transformer (CT), and the Hall effect sensor [2].

#### Low Resistance Current Shunt

The low resistance current shunt is the lowest cost solution available today and it offers simple current measurement with high accuracy. One disadvantage of the shunt resistor is that high precision current measurement is affected by the parasitic inductance of the shunt. Although this affects only the magnitude of the impedance at relatively high frequency, its affect on the phase at line frequency causes a noticeable error at a low power factor. A phase mismatch of 0.1° will lead to about 0.3% error at a power factor of 0.5.

The low cost and high reliability make the low resistance current shunt a very popular choice for energy metering. The major disadvantage to using the shunt is that fundamentally a shunt is a resistive element, the power loss is thus proportional to the square of the current passing through it and consequently it is a rarity amongst high current energy meters.

#### **Current Transformer**

The CT is based on the principle of a transformer and converts a high primary current into a smaller secondary current and is common among high current solid-state energy meters. As this device is a passive device, no extra driving circuitry is needed in its implementation. Another major advantage is that it can measure very high current while consuming little power. The disadvantage of the CT is that a very high primary current or a substantial DC component in the current can saturate the ferrite material used in the core ultimately corrupting the signal. Another problem is that once the core is magnetized, it will contain hysteresis and the accuracy will degrade unless it is demagnetized again.

### Hall Effect Sensor

The advantages of the Hall effect sensor is that it has outstanding frequency response and is capable of measuring very large current and because it is an integrated circuit element, it can be integrated into a system as a whole, something not possible with the other sensing solutions. Accuracy is also improved by eliminating the phase shift errors normally associated with CT's, which are large at low power factors. The disadvantage however, is that the output can have a large temperature drift and as the system is active, additional circuitry is required for successful implementation. Many techniques exist to combat these problems but at an additional circuit overhead.

This dissertation presents a power sensor system that utilizes the multiplication properties of the Hall generator thus greatly reducing the need for digital circuitry normally required in similar systems to execute multiplication of sensed line voltage and current and thus ultimately saving chip area required. The system is implemented in a standard CMOS process and can thus easily be integrated into embedded systems. Power meters based on the Hall effect may display useful reduction in support circuitry required when compared to similar systems using other sensing techniques. The work presented in this dissertation will also form a foundation for further study into increasing the accuracy of such a system as well as compensation techniques that would assist in exploiting the properties of the Hall effect generator. The gain in area performance can thus be used to add economic value to power metering systems.

### 1.2. SUMMARY OF RELATED WORK

Not much literature exists in the field of Hall effect based power sensors. Although some companies are manufacturing power sensors based on the Hall effect such as Load Controls Incorporated [3], most Hall effect sensors on the market in this field are only designed for current sensing. This utilizes only half of the properties inherent in such an element and it seems that hardly any manufacturers have exploited the full potential of these Hall effect devices. An example of a product from Load Controls Incorporated is the Power Cell, designed for sensing and monitoring power in electrical motor controlled applications. Hall sensors are extremely well suited to this application as it greatly simplifies installation and will also operate on the output of variable frequency drives as well as odd wave shapes.

The system design uses well-established micro-electronic design techniques and thus some emphasis must be placed upon the Hall generator. Traditionally, Hall generators consists of the well understood square plate but new geometries are now being investigated [4, 5] to improve on the relevant properties required for applications other than direct magnetic field sensing as well as to overcome certain second order effects [4, 6, 7, 8, 9, 10, 11] inherent in the square plate configuration. Popović [8] explains the design principles behind the Hall generator. Popović is the pioneer in the field of semiconductor Hall effect generators and has played a major role in the industry regarding Hall effect sensors.

The mechanical configuration of current sensing elements is also of great importance and most techniques employ a ferrite core structure so that the magnetic field can be concentrated

over the Hall generator [12, 13, 14, 15, 16]. Some micro-magnetic field concentrators have been investigated and successfully implemented [17] but at the cost of extra manufacturing steps. Here a metal layer is deposited over the semiconductor in a very specific manner such that its physical construction concentrates the magnetic field over the Hall generator. Micro machining techniques have also been applied here for high accuracy requirements.

## 1.3. CONTRIBUTIONS OF THIS STUDY

The research discussed in this dissertation aims to contribute knowledge to the field of power sensing based on Hall effect multiplication as an economically competitive alternative to current power sensing techniques. The main criteria is a fully integrated sensor and thus ultimately a cost efficient alternative in an increasingly competitive market. A fully functional power sensor system is implemented and evaluated according to the International Electrotechnical Commission (IEC) 1036 standard [18, 19]. An analysis in Hall generator design is also presented so as to emphasize the important aspects to be taken into consideration for the design of this specific application.

### 1.4. DISSERTATION OUTLINE

- Chapter 1 Introduction

- Chapter 2 A discussion of the IEC 1036 standard as a basis for the power sensor system architecture and specifications as well as an explanation of the basic operation of the system.

- Chapter 3 The galvanomagnetic effects in semiconductors as the basis for designing the Hall generator.

- Chapter 4 A description of the design and verification of the support circuitry required to obtain the required specifications.

- Chapter 5 An overview of the complete power sensor system as well as interfacing requirements and verification of specifications.

- Chapter 6 Concluding summary

## 2. POWER SENSOR ARCHITECTURE

#### 2.1. INTRODUCTION

The overall power sensor system consists of many basic building blocks that must be arranged into an architecture to perform according to the application requirements. Exact application requirements need to be taken into account such that the characteristics of the architecture may be exploited to the advantage of the final design specification. The design specification is deduced from the IEC 1036 standard, which is the international standard requirement for class I power meters. This chapter discusses the requirements for a class I power meter based on the IEC 1036 standard followed by the proposed sensor system architecture required to fulfill these specifications based on Hall effect multiplication including various aspects to consider during the design of the sub-system architectures such that system requirements are met.

#### 2.2. BACKGROUND

### 2.2.1. The IEC 1036 Standard

### Objective

The objective of the IEC is to promote international co-operation on all questions regarding the standardization in the electrical and electronic fields. The IEC is a world wide accepted organization and collaborates closely with the International Organization for Standardization (ISO). The preparation of the IEC 1036 was based on the IEC 521 and IEC 687 standards as reference. The standard covers the "standard meter" that will be used indoors and outdoors in large quantities worldwide. The standard distinguishes the accuracy of class index I and II meters, the protective class I and class II meters and also meters for use in networks equipped with or without earth fault neutralizers. Test levels in the standard are regarded as the minimum values required to guarantee the proper functioning of the meter in its normal operating environment.

#### **General Definitions**

Before we define the specifications of the power sensor, it is necessary to define the terminology used by the IEC standard. This terminology will be adhered to in any further technical description of the proposed sensor design. Although the standard describes active

energy meters as a fully completed entity, many of the specifications directly influence the design proposed in this dissertation. The standards applying to static watt-hour meters of accuracy class I for measuring alternating current (AC) electrical active energy of frequency in range 45 Hz to 65 Hz of line voltages less than 600 V will be used to define the applicable specifications for the proposed design.

- Static watt-hour meter Meter in which current and voltage act on solid-state (electronic)

elements to produce an output proportional to watt-hours.

- Continuous output linear power sensor using Hall effect vector multiplication The design

of a measuring device that senses line voltage and current and calculates the active power

and satisfies the applicable minimum specifications as required by a static watt-hour

meter. (Main part of the measuring element)

- Measuring element Part of the meter that produces an output proportional to the energy.

- Current circuit Internal connections of the meter and part of the measuring element through which flows the current of the circuit to which the meter is connected.

- Voltage circuit Internal connections of the meter, part of the measuring element and power supply for the meter, supplied with the voltage of the circuit to which the meter is connected.

#### **Definition of Meter Quantities**

- Basic current (I<sub>b</sub>) Value of current in accordance with which the relevant performance of

a direct connected meter is fixed.

- Maximum current (I<sub>max</sub>) Highest value of current, which the meter supports to meet the

accuracy requirements of this standard.

- Reference voltage (U<sub>n</sub>) Value of the voltage in accordance with which the relevant performance of the meter is fixed.

- Reference frequency Value of the frequency in accordance with which the relevant performance of the meter is fixed.

- Percentage error Percentage error is defined by the following formula:

$$\%error = \frac{measured\_energy - true\_energy}{true\_energy} \times 100$$

(2.1)

## **Electrical Requirements**

The standard defines the following for a class I meter using direct sensing techniques

Table 2.1 Standard references

| Measured Quantity               | Standard values           |  |

|---------------------------------|---------------------------|--|

| Voltage (V)                     | 120-230-277-400-480       |  |

| Current (A)                     | 5-10-15-20-30-40-5        |  |

| Frequency (Hz)                  | 50-60                     |  |

| Temperature (°C)                | -25°C to 70°C             |  |

| Voltage circuit max consumption | 2 W and 10 VA             |  |

| Current circuit max consumption | 4.0 VA                    |  |

| Power supply range              | 0.9 to 1.1 U <sub>n</sub> |  |

Maximum current for direct connected meter shall be preferably an integral multiple of the basic current (e.g. four times the basic current). The starting current will be  $0.004 I_b$ .

# Accuracy Requirements for Sensing Current

Table 2.2 Current sensing accuracy requirements

| Value of current                | Power factor                     | % Error limit |  |

|---------------------------------|----------------------------------|---------------|--|

| $0.05 I_b \le I \le 0.1 I_b$    | 1                                | ±1.5          |  |

| $0.1 I_b \le I \le I_{max}$     | 1                                | ±1.0          |  |

| $0.1 I_b \le I \le 0.2 I_b$     | 0.5 Inductive<br>0.8 Capacitive  | ±1.5<br>±1.5  |  |

| $0.2 I_b \le I \le 0.1 I_{max}$ | 0.5 Inductive<br>0.8 Capacitive  | ±1.0<br>±1.0  |  |

| $0.2 I_b \le I \le I_b$         | 0.25 Inductive<br>0.5 Capacitive | ±3.5<br>±2.5  |  |

## Accuracy Requirements for Temperature Stability

Table 2.3 Temperature stability requirements

| Value of current            | Power factor  | Mean temperature coefficient %/K |

|-----------------------------|---------------|----------------------------------|

| $0.1 I_b \le I \le I_{max}$ | 1             | 0.05                             |

| $0.2 I_b \le I \le I_{max}$ | 0.5 Inductive | 0.07                             |

# Accuracy Requirements for Voltage and Frequency Stability

Table 2.4 Voltage and frequency stability requirements

| Influence quantity  | Value of current            | Power factor  | % Error limit |

|---------------------|-----------------------------|---------------|---------------|

| Voltage variation   | $I_b \le I \le I_{max}$     | 1             | 0.7           |

| ± 10 %              | $0.1 I_b \le I \le I_{max}$ | 0.5 Inductive | 1.0           |

| Frequency variation | $I_b \le I \le I_{max}$     | 1             | 0.5           |

| ±10%                | $0.1 I_b \le I \le I_{max}$ | 0.5 Inductive | 0.7           |

## 2.3. PROBLEM DEFINITION

With the definition of the required relevant specifications needed for a complete static watthour metering system in place, it is now possible to outline the requirements as needed by the linear power sensor such that the requirement for integrating the sensor into a static watthour meter can be fulfilled. As the Hall generator executes the main functionality of the system, it is responsible for the fulfillment of the majority of the specifications as outlined by the IEC 1036 standard. The specifications will thus be grouped in two categories namely the Hall generator itself and the system requirements necessary to obtain these specifications.

- The Hall generator's characteristics are mainly dependent upon the technology in which it will be manufactured. These characteristics need to be analyzed to determine which of them will influence the final specification.

- The geometry of a Hall generator has a major influence over performance characteristic and the designer has control over the parameters that directly influence the size and geometry of the device. It will be necessary to identify the most important characteristics that will influence the performance according to the required specifications. The proposed device geometry is the cross-shaped Hall generator and it

will be necessary to investigate the sizing ratio required to maximize the sensitivity of the device while keeping offsets and short-circuiting effects to a minimum.

As the Hall voltage generated by Hall generators is extremely small and unstable in its own capacity, certain support circuitry will be required to meet the system specifications and will require the following circuits to be designed and implemented:

- A voltage to current converter that will transform the sensed line voltage into a well

defined biasing current needed by the Hall generator as well as the external

requirements and changes needed to adapt to the different standard references as

required by the IEC 1036 standard. (See table 2.1)

- The design of an accurate temperature independent voltage and current reference circuit that will assist in obtaining the temperature performance specifications in table 2.3.

- As mentioned earlier, the Hall voltage representing the active power is extremely small and it will thus be necessary to amplify the signal such that it can be presented at a suitable signal level and simply adapted as per requirements of future applications of the sensor.

- As the offsets inherent in the Hall generator and amplifiers are in the same order of

magnitude as the generated Hall voltage, it will be necessary to design and implement

offset cancellation circuitry as well as low pass filters to successfully extract the useful

information from the signal.

This dissertation concentrates on the theoretical design of the proposed sensor. Core parts of the design will be implemented using a standard 1.2  $\mu m$  CMOS process for experimental verification purposes only. All design parameters will be based on this process and can be seen in addendum A.

### 2.4. SYSTEM ARCHITECTURE

#### 2.4.1. Traditional Watt-Hour Meter Architecture

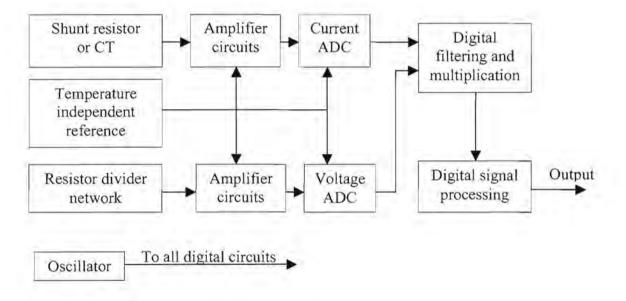

Traditional watt-hour meters consist of a voltage sensing circuit, a current sensing circuit, an analog to digital converter, various digital filters, digital multipliers and information extraction circuitry. Figure 2.1 illustrates the typical architecture normally implemented and it can be seen that a large circuit overhead is resident in the fact that two amplifiers and AD converters are required for the voltage and current sensing circuits.

Figure 2.1 Block diagram of traditional watt-hour meters

The meters are designed such that external components are used to calibrate the meters as well as set the meter up for the different standard references as in table 2.1. Voltage and current sensing circuits typically use signal levels in the order of a few tens of mV or  $\mu A$  respectively.

#### **Current Sensing**

Current sensing is achieved through the use of shunt resistors or CT's. Typically shunt resistors are in the order of 500  $\mu\Omega$  producing a voltage drop that is linear to the current passing through it according to Ohm's law. This voltage drop would thus be a few mV and can be used directly to represent sensed current. Although this method is extremely accurate, a power of about 1 W could easily be consumed in the shunt resistor at rated currents making

the solution expensive when viewed in large quantities. The use of CT's are also extremely popular as they consume very little power during sensing, but phase errors and saturation problems must be taken into consideration during design and also contribute to circuit overhead and cost. Furthermore, it must be remembered that these devices contribute to the cost of manufacturing watt-hour meters even though these devices are manufactured in large quantities. In many cases, the use of CT's can contribute a cost equivalent to the IC itself.

### Voltage Sensing

The voltage sensing circuit uses resistive divider networks to step the high line voltage down to suitable levels for solid-state electronic circuitry. This network typically consists of a few resistors in series such that the power dissipated in each resistor is distributed between them. Normally the input current of the voltage sensing input would be well defined such that the resistors are easily calculated according to Kirchoff's voltage or current laws.

## 2.4.2. The Hall Effect Multiplier

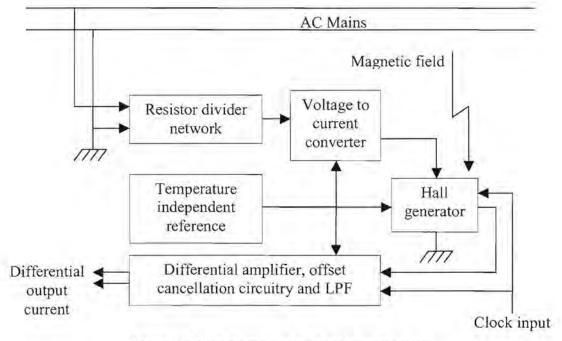

Figure 2.2 Block diagram of the linear power sensor

Figure 2.2 shows the block diagram of the Hall multiplication based linear power sensor. It can be seen that using the inherent multiplication properties of the Hall generator, the voltage and current sensing circuits are incorporated into a single unit. Furthermore, only one AD

converter is needed to encode the output signal of the Hall effect sensor. The complete system is based on differential signal processing to suppress noise and common mode signals.

### 2.5. SYSTEM OPERATION

### 2.5.1. Resistor Divider Network

This circuit represents the voltage-sensing element and has the same functionality as that of the voltage sensing element in figure 2.1. Once again the network consists of a few resistors in series for power dissipation distribution purposes. The network divides the voltage down to a value suitable for the solid-state electronics as well as assists in converting this voltage into a current signal. This current signal is used to bias the Hall generator and is linearly dependent upon the mains voltage. The Hall generator can be biased using either a biasing current or a biasing voltage. The problem however when using a voltage is that due to process variations, the Hall plate resistance itself may vary greatly thus resulting in an unpredictable biasing current. As the Hall voltage generated is directly proportional to this current, the result would be a Hall voltage signal with high tolerances. The result is to use a defined current to bias the plate thus greatly increasing the accuracy of the resultant signal.

#### 2.5.2. Hall Generator

The Hall generator consists of an extremely thin semiconductor plate configured in such a way so as to maximize the Hall effect in the presence of a magnetic field perpendicular to the plate. Equation 2.2 shows how the Hall voltage generated is the product of the biasing current  $I_{bias}$ , the perpendicular component of a magnetic field, B, approaching the plate at an angle  $\theta$ , and the sensitivity, consisting of the Hall coefficient  $R_{H_i}$  divided by the Hall plate thickness t. As the biasing current is proportional to the line voltage  $V_{line}$ , and the magnetic field is proportional to the line current  $I_{line}$ , the Hall voltage  $V_h$ , represents the instantaneous power consumed in the line as illustrated in equation 2.3.

$$V_h = \frac{R_H}{t} \left( I_{bias} B \sin \theta \right) \tag{2.2}$$

$$V_h \propto \frac{R_H}{I} \left( V_{line} I_{line} \right) \tag{2.3}$$

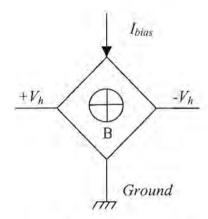

Figure 2.3 shows how the Hall generator is configured. It consists of a Hall plate manufactured of a semiconductor material with four leads attached. A bias current  $I_{bias}$  flows through two leads while a differential Hall voltage  $V_h$  is generated across the sensing leads.

Figure 2.3 The Hall generator

An important aspect here is the fact that the Hall voltage generated is a differential signal in that the Hall voltage is the difference between  $+V_h$  and  $-V_h$ . Furthermore, both  $+V_h$  and  $-V_h$  have a common mode voltage with respect to ground and is equal to the biasing current through the plate multiplied by half the plate resistance. The differential signal thus establishes the need for fully differential amplifier design and the Hall voltage will be amplified by a suitable factor such that the power information can be extracted with high accuracy.

Another problem that exists in Hall generators is offsets. In the presence of a zero magnetic field, the Hall generator ideally has a zero differential output. However, due to misalignments that occur as result of process variations as well as gradual changes in resistance gradients over the semiconductor, physical imbalances are created and when electrically stimulated result in a differential voltage being present at the output of the Hall generator in the absence of a magnetic field. These offsets can represent a significant value of the parameter under measurement and need to be compensated using offset cancellation techniques to reduce its effects. As operational amplifiers themselves produce a significant amount of offset, techniques for combining offset cancellation such that both the Hall generator and the operational amplifier's offsets are cancelled in the same signal processing step will be beneficial to minimize circuitry.

## 2.5.3. Temperature Independent Reference

Temperature independent referencing has become extremely important in IC design. Analog circuits extensively incorporate voltage and current referencing. These references are do quantities exhibiting little dependence on supply voltages and process parameter variations and a well-defined dependence on temperature. This is necessary as biasing currents affect differential pair voltage gain as well as noise performance of the circuit. The circuit will thus be responsible for all required biasing currents needed by the voltage to current converter, the amplifiers and the Hall generator itself.

### 2.5.4. Differential Amplifier, Offset Cancellation Circuitry and Low Pass Filtering

The amplifiers to be used will be fully differential operational amplifiers. This is necessary for increasing the linearity performance of the system and to suppress the common mode noise present. The amplifier design will focus on minimizing offsets as well as common mode signal suppression. The specifications for the operational amplifier will not need to be extremely stringent in terms of speed as the lines frequency is specified by the IEC 1036 in the range 45 to 65 Hz. The specification however, requires that the power content of at least the 5<sup>th</sup> harmonic also be measured, implying a minimum frequency response of 325 Hz. As the frequency response of the Hall generator itself is in the order of KHz, this specification is obtainable.

Offset cancellation will be based on differential techniques, which will be used in conjunction with the offset cancellation techniques implemented in the Hall generator itself. Offsets will be interpreted as a constant value of power being consumed and final offset specifications must be reduced such that the specification limits in current and voltage accuracy are still met as set out in table 2.2. Offset cancellation for the Hall generator will be based on the dynamic quadrature offset cancellation technique as suggested by Bilotti, Monreal and Vig [4]. Offset timing will be controlled by the clock input, a 50% duty cycle square wave signal of high frequency (in the order of tens of KHz). The signal will be generated externally such that the system effects as a result of clock variation can be studied. This however would be generated internally when integrated into a fully functional watt-hour meter and forms an important part of the stability requirements of the system as set out in the IEC 1036 standard.

Finally, as a result of the offset cancellation techniques proposed, it will be necessary to low pass filter the output signal. The IEC 1036 frequency specification will determine the -3 dB cut-off frequency of the filter, which will be in the order of 500 Hz. The filter will also assist in the filtering out of high frequency switching noise.

# 2.6. SYSTEM SPECIFICATIONS

The basic system requirements will now be stated. These are entirely based on the IEC 1036 standard and as mentioned before, the sensor must later form part of a watt-hour meter and thus adhere to all international standards. For experimental purposes it was necessary to define some parameters such as maximum line current  $I_{max}$  and others such that some components could be physically realized. These parameters will later form part of customer requirements and the system will be designed such that simple modifications will be possible to bring the sensor in line with these demands. Error specifications will be tested for a power factor of 1 unless otherwise specified. The following specifications make up the system performance requirements. These specifications form the basis for future research and development of the sensor.

Circuit operating voltage 5 V

Maximum supply current <2 mA

Operating temperature -25°C to 70°C

Maximum Line Voltage 230 V<sub>rms</sub>

Base current 20 A<sub>rms</sub>

Maximum line current 80 A<sub>rms</sub>

Line frequency 50 Hz

System sensitivity 0.231  $\mu$ A/kW (rms)

Temperature stability for 0.1  $I_b \le I \le I_{max}$   $\pm 0.05 \%/K$

Accuracy for  $0.05 I_b \le I \le 0.1 I_b$   $\pm 1.5 \%$

$0.1 I_b \le I \le I_{max}$   $\pm 1.0 \%$

Voltage circuit max consumption 2 W and 10 VA

Current circuit max consumption 4.0 VA

Process requirements Standard silicon 1.2 µm CMOS, double metal,

double poly

## 2.7. CONCLUSION

This chapter presented the IEC 1036 standard according to which the proposed linear power sensor will be designed and measured. The requirements relevant to the designing and implementation of the proposed sensor have been highlighted and discussed. A traditional watt-hour meter architecture was presented and discussed explaining the functionality of the system and how the new sensor design will affect this system. The proposed sensor system architecture was presented and discussed explaining the relevant issues to take into consideration during the design phase of the sensor. These include:

- Reasons for current biasing rather than voltage biasing of the Hall generator and the implementation thereof,

- The basic operation of the Hall generator,

- Temperature independent voltage and current referencing and its basic effect on system stability,

- The differential operation of the system and the basic requirements for the differential amplifiers, offset cancellation and low pass filtering.

Finally, the system specifications were proposed for the entire system and these included all system performance requirements, operating conditions and accuracy conformance specifications in compliance with the relevant requirements from the IEC 1036 standard.

## 3. HALL GENERATOR

#### 3.1. INTRODUCTION

The generation of a strong Hall effect requires a high velocity of charge carriers. This can be either achieved by a high electric field, or by a high mobility of the quasi-free charge carriers. Metal conductors as used at the time of the Hall effect discovery, fulfilled neither of these two requirements. Semiconductor technology revolutionized this. Low doped semiconductor materials possess a low density of quasi-free charge carriers. These carriers hardly interact with the ionic impurities, giving them a high mobility. Moreover, they are few enough, which permits us to apply a high electric drift field without thermally degenerating the material. Both these features lead to a high velocity and consequently to a high signal level. For this reason, Hall effect devices today, are exclusively made of semiconductor material. Since we are concerned with the designing of an integrated Hall generator in silicon that can accurately measure medium strength magnetic field intensities generated by the line current through a wire-wound ferromagnetic core, it is of particular interest for us to understand which material phenomena determine the behavior of the Hall effect in silicon for its successful design.

Semiconductor-integrated sensors has undergone major development over recent years and has been driven by the need for a reduction in size and increasing efficiency of electronic circuitry in semiconductor single chip solutions. This field has now completely revolutionized electronic sensing and holds particularly true for magnetic field sensors (MFS). Integrated silicon MFS's can now be manufactured using standard IC technologies without introducing any extra manufacturing steps or procedures such as "micromachining" or film deposition as in the case of most mechanical or chemical sensors.

The Hall generator falls under the category of magnetic field sensors and is a transducer that converts a magnetic field into a useful electronic signal. There exist two main groups of MFS applications namely direct (magnetic fields, reading of magnetic tapes, etc.) and indirect also called "tandem" transduction (mechanical displacement of magnets, current sensing, etc.). The linear power sensor thus requires the detection of magnetic fields in the micro- and millitesla (mT) range, which can be achieved with integrated semiconductor sensors. This chapter will thus focus on the magnetic properties and effects of the Hall generator upon which the design method for the Hall generator will be based.

# 3.2. BACKGROUND

Semiconductor MFSs are based on galvanomagnetic effects such as Hall voltage, carrier deflection, magnetoresistance and magnetoconcentration, all due to the action of the Lorentz force on the charge carriers (electrons and holes) and further magnetically form part of the low-permeability (dia- or paramagnetic) group where  $\mu \approx 1$ .

Silicon (Si) and gallium arsenide (GaAs) offer an advantage of inexpensive batch fabrication by the integration of single or multiple sensor elements together with appropriate support and signal processing circuitry in an advanced standard technology of established reliability, such as bipolar or CMOS technology. Many custom chip manufacturers around the globe using design rules of a standard chip manufacturing process have exploited this advantage. MFS development outside these processes requires special manufacturing techniques and appropriate test and reliability procedures. The development costs involved are usually far beyond the financial reach of small to medium sized companies.

# 3.3. GALVANOMAGNETIC EFFECTS IN SEMICONDUCTORS

For the designing of effective and efficient Hall generators, an understanding of the mechanism of galvanomagnetic effects in semiconductors is necessary. This chapter describes the bulk integrated Hall device for its widely explored and well-understood behavior as the benchmark for performance measurement of the proposed Hall generator. The device will be analyzed in terms of device sensitivity, noise performance, offsets, linearity, electrical functionality and technological compatibility with standard CMOS processes.

### 3.3.1. The Hall Effect

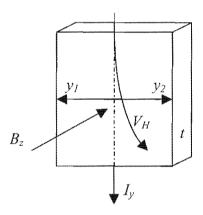

Figure 3.1 shows the generation of the Hall effect and is the occurrence of a current component perpendicular to a control current  $I_y$  and magnetic field  $B_z$  as a direct result of the Lorentz force [8, 9, 10, 11, 12, 20]. Charge carriers are deflected by the magnetic field. To ensure that the transverse current is zero, an electric field called the Hall field is established. If the magnetic field is zero, the two points  $y_I$  and  $y_2$  have the same potential, i.e., the voltage difference between the two points is zero and thus no Hall voltage is present.

If  $B_z \neq 0$ , there will be a voltage difference between points  $y_I$  and  $y_2$  which is proportional to the magnetic field and

$$V_H = R_H \left( \frac{I_y B_z}{t} \right) \tag{3.1}$$

where  $I_y = \text{current in direction } y$ ,

t =semiconductor thickness,

$R_H$  = proportionality factor (Hall coefficient).

The Hall coefficient is inversely proportional to the density of free carriers. To obtain a large Hall voltage, a material with a small carrier density is required.

Figure 3.1 The Hall effect in a piece of semiconductor material

The Hall effect, like other galvanomagnetic effects, is thus a manifestation of the charge carrier transport phenomena in condensed matter when carriers are under the influence of the Lorentz force. We assume isotropic n-type material with zero temperature gradient. Further, we denote the electron current density for B = 0 by  $J_n(0)$ . The diffusion approximation of the Boltzmann transport equation thus reduces to [8, 9, 10, 11],

$$J_n(0) = \sigma_n E + q D_n \nabla n \tag{3.2}$$

Where  $\sigma_n = q\mu_n n$ , denotes the electronic conductivity,

B = 0, denoting the magnetic field,

E, the electric field,

$q = 1.6 \times 10^{-19}$  A.s, the magnitude of electron charge,

$D_n = \frac{\mu_n kT}{q}$ , the electron diffusion constant with Boltzmann's constant, k = 1.380658

$\times 10^{-23}$  J/K and temperature T, in Kelvin,

n, the electron density and

$\mu_n$ , the electron drift mobility.

In equation (3.2) the term  $\sigma_n E$ , describes the drift current and  $qD_n Vn$ , the diffusion current. For nonzero magnetic induction B, the electron current density  $J_n(B)$ , obeys the equation

$$J_n(B) = J_n(0) - \mu_n^* (J_n(B) \times B)$$

(3.3)

Where  $\mu_n^*$  is the Hall mobility for electrons. The Hall mobility is proportional to the drift mobility  $\mu_n$  and  $\mu_n^* = r_n \mu_n$ . The scattering factor is defined as  $r_n = \frac{\langle \tau_n^2 \rangle}{\langle \tau_n \rangle^2}$ , where  $\tau_n$  denotes the free time between collisions. The energy-band structure and the underlying scattering processes determine the value of  $r_n$ , which is about 1.15 for n-type silicon at room temperature for low donor concentrations.

Solving equation (3.3) with respect to  $J_n(B)$  yields,

$$J_n(B) = \frac{J_n(0) - \mu_n^* (B \times J_n(0)) + (\mu_n^*)^2 (B \cdot J_n(0)) B}{1 + (\mu_n^* B)^2}$$

(3.4)

This equation comprises the isothermal galvanomagnetic effect for electrons and accounts for the direct effects of temperature on carrier concentration, diffusion and mobility excluding thermomagnetic and thermoelectric effects. The hole current density is defined in the same way. Poisson's equation as well as the pertinent continuity equations for electrons and holes is generally solved together with the electron and hole equations.

It is evident from equation (3.4) that the Lorentz force is included in both carrier drift and diffusion terms. Neglecting carrier concentration gradients as with n-type slabs with ohmic contacts reduces equation (3.4) to,

$$J_{n}(B) = \sigma_{nR}[E + \mu_{n}^{*}(B \times E) + \mu_{n}^{*2}(B \cdot E)B]$$

(3.5)

where,

$$\sigma_{nB} = \frac{\sigma_n}{1 + (\mu_n^* B)^2} \tag{3.6}$$

Hall Generator

With the magnetic field parallel to the electric field,  $\mathbf{B} \times \mathbf{E} = 0$ , and  $\mathbf{J}_n(\mathbf{B}) = \sigma_n \mathbf{E} = \mathbf{J}_n(\mathbf{0})$ . No longitudinal galvanomagnetic effect is observed in isotropic semiconductors. If the magnetic field is perpendicular to the electric field,  $\mathbf{B} \cdot \mathbf{E} = 0$ , and we obtain,

$$J_n(B) = \sigma_{nB}[E + \mu_n^*(B \times E)]$$

(3.7)

The equation describes transverse galvanomagnetic effects with negligible diffusion. When the test piece is orientated in space such that  $\mathbf{B} = (0,0,B)$ ,  $\mathbf{E} = (E_x, E_y, 0)$ , and  $\mathbf{J}_n(\mathbf{B}) = (J_{nx}, J_{ny}, 0)$ , equation (3.7) becomes

$$J_{nx} = \sigma_{nB} (E_x - \mu_n^* B E_y)$$

$$J_{ny} = \sigma_{nB} (E_y - \mu_n^* B E_x)$$

(3.8)

The two limiting cases namely the Hall field and carrier deflection and magnetoresistance are distinguishable and are now described respectively.

#### Hall Field

Explaining this limiting case, a long thin rod sample is used as an approximation, such that no Hall field is produced in the y-direction, i.e. the current density vector has only an x-component. The Hall field can thus be defined by

$$E_{y} = -\mu_{n}^{*}BE_{x} = R_{H}J_{nx}B \tag{3.9}$$

where,

$$R_{H} = -\frac{\mu_{n}^{*}}{\sigma_{n}} = -\frac{r_{n}}{qn} \tag{3.10}$$

denotes the Hall coefficient [21]. The result is a rotation of the equipotential lines by the Hall angle  $\theta_H$  with

$$\tan \theta_H = \frac{E_y}{E_x} = -\mu_n^* B = \sigma_n R_H B \tag{3.11}$$

A Hall voltage of  $V_H = \frac{R_H IB}{t}$ , is produced for long Hall plates of thickness t carrying a current I with a sensitivity of  $\frac{V_H}{IB} = \frac{R_H}{t} = \frac{r_n}{qnt}$ .

As one of the primary objectives is to achieve a high sensitivity, it is necessary to minimize the carrier concentration n. This substantiates the fact that semiconductors are more usefully implemented as Hall effect sensors than metals and why only since the discovery of semiconductors, Hall effect applications became viable.

### Carrier Deflection and Magnetoresistance

The second extreme case would now be to reduce the Hall field to zero. Using a short sample of wide cross section with current electrodes at the large faces, this condition can be defined, and from equations (3.8) and (3.11), the current deflection can be calculated as

$$-\frac{J_{ny}}{J_{ny}} = \mu_n^* B = \tan \theta_H \tag{3.12}$$

As the drift path has become substantially longer, the geometrical magnetoresistance will contribute significantly and is given by

$$\frac{\left(\rho_{nB}-\rho_{n}\right)}{\rho_{n}}=\left(\mu_{n}^{*}B\right)^{2}\tag{3.13}$$

where,

$$\rho_n = \frac{1}{\sigma_n}$$

, is the resistivity for  $B = 0$ , and

$$\rho_{nB} = \frac{E_x}{J_{nx}} = \frac{1}{\sigma_{nB}}$$

, the resistivity enhanced by the magnetic induction.

Silicon typically shows a resistivity of ,  $\rho_{nB} \approx 1.02 \rho_n$ , for magnetic field intensities as high as 1 T.

Equations (3.3) to (3.13) are approximations for weak field expansion and relative errors exist of  $(\mu_n^*B)^2$ . These equations however, show small errors for fields below 2T of  $(\mu_n^*B)^2 \le 0.1$ , and thus still yield good approximations. Analogous to n-type Si, p-type semiconductor materials are characterized by drift and Hall mobility constants  $\mu_p$  and  $\mu_p^* = r_p \mu_p$ , with the Hall coefficient given by

$$R_H = \frac{r_p}{qp} \tag{3.14}$$

with p, denoting hole concentration. At room temperature and for low doping, the scattering factor is  $r_p \approx 0.7$ . Analogous to n-type, the Hall angle is given by

$$\tan \theta_H = -\mu_p^* B \tag{3.15}$$

So too, the magnetoresistance effect is

$$\frac{\rho_{pB}}{\rho_{p}} = 1 + (\mu_{p}^{*}B)^{2} \tag{3.16}$$

where,

$$\rho_p = \frac{1}{q\mu_p p} \tag{3.17}$$

Using this information, the Hall coefficient takes on a general form given by equation (3.18) for mixed type conduction.

$$R_{H} = -\frac{\left[r_{n}\left(\frac{\mu_{n}}{\mu_{p}}\right)^{2}n - r_{p}p\right]}{q\left[\left(\frac{\mu_{n}}{\mu_{p}}\right)^{n} + p\right]^{2}}$$

(3.18)

# 3.4. THE IDEAL HALL PLATE

The ideal Hall plate is by far the most developed and well-understood semiconductor Hall effect device implemented as a magnetic sensor. They have found well-established commercial use since their discovery and have been implemented as monolithic silicon integrated devices since the early 1970s. These devices have now set the benchmark against which newly developed Hall effect devices are measured. This section describes the ideal Hall plate properties.

#### 3.4.1. Geometrical Considerations

The Hall plate is usually manufactured using a high resistivity material (semiconductor material), and provided with four ohmic contacts for biasing and sensing. From equation (3.1), it was seen that ideally a thin rectangular shaped plate was used. When biased, the plate builds up a Hall voltage across opposite sense electrodes in the presence of a magnetic field perpendicular to the plate plane as described in paragraph 3.3.1.

$$V_{H} = \frac{R_{H}}{t} G\left(\frac{l}{w}, \frac{s}{w}, \frac{y}{l}, \theta_{H}\right) B_{2} I$$

(3.19)

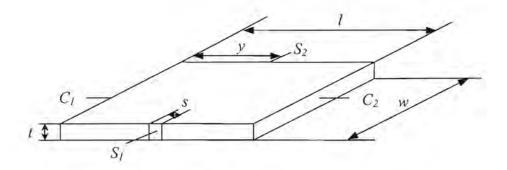

A new factor is introduced here and is referred to as the geometrical factor. Figure 3.2 illustrates the plate dimensions with the Hall angle given by equation (3.11). The Hall coefficient of mixed type conduction semiconductor is given by the general form of equation (3.18) but usually the Hall plates work under strong extrinsic conditions with n >> p, and thus equation (3.10) applies. Although the scattering parameters  $r_n$  and  $r_p$  of the Hall plates are always close to unity, they play an important role in the temperature behavior.

Equation (3.19) can thus be described as

$$|V_H| \cong \frac{r_n}{qnt} GB_z I \tag{3.20}$$

What can be seen from equation (3.20) is that the Hall voltage is inversely proportional to the carrier density and plate thickness. This explains why Hall plates are made from thin, high resistivity materials.

Figure 3.2 Rectangular Hall plate indicating dimensions

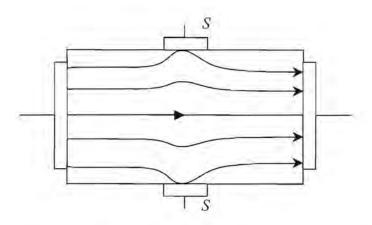

The geometrical factor in equation (3.19) and equation (3.20), expresses the difference between an infinitely long Hall plate and the finite one and is given by equation (3.21) and accounts for the short-circuiting effects resulting from current flowing through the sensor electrodes illustrated in figure 3.3.

$$G\left(\frac{l}{w}, \frac{s}{w}, \frac{y}{l}, \theta_H\right) \equiv \frac{V_H}{V_{H^{oo}}}$$

(3.21)

Figure 3.3 Short-circuiting effects due to sensor contacts

If it is assumed that only one type of carrier is involved and the geometry of the square plate is such that  $\frac{l}{w} > 1.5$ ,  $\frac{s}{w} < 0.18$  and  $y = \frac{l}{2}$ , G can be approximated by equation (3.22).

$$G_{L} = \left[1 - e^{\left(\frac{\pi I - \theta_{H}}{2 \text{ wtan}\theta_{H}}\right)}\right] \left[1 - \frac{2}{\pi} \frac{s}{w} \frac{\theta_{H}}{\tan \theta_{H}}\right]$$

(3.22)

Equation (3.22) approaches unity when  $\frac{l}{w} > 3$  and  $\frac{s}{w} < \frac{1}{20}$ . With small Hall angles and short samples with point sensor electrodes, G is approximated by equation (3.23).

$$G_s \cong 0.74 \frac{l}{w} \tag{3.23}$$

From equation (3.20) to equation (3.23), it can be seen that for maximizing the Hall voltage, it is necessary to maximize the plate length and minimize the thickness and carrier concentration. When analyzing the voltage drop across the plate in equation (3.24), it can be seen that a compromise is needed as maximizing the Hall voltage also increases the voltage drop across the plate.

$$V = \frac{1}{q\mu_n n} \frac{l}{wt} I \tag{3.24}$$

Substituting equation (3.24) in equation (3.20) yields the Hall voltage in terms of supply voltage and

$$V_H = \mu_n^* \frac{w}{l} G B_z V \tag{3.25}$$

The importance of high carrier mobility is evident here. It can also be seen that the Hall voltage increases with the  $\frac{w}{l}$  ratio. The limit is obtained by substituting equation (3.23) into equation (3.25) and is given by equation (3.26).

$$V_{H,0} \approx 0.74 \mu_n^* B_z V$$

(3.26)

Many other shapes have been proposed and even though Wick [9, 22] proved the invariance of Hall plate electrical efficiency with respect to geometry using his conformal mapping theory, some specific shapes have some technological advantages over others.

The two required properties for producing a more efficient Hall effect is a higher carrier mobility and lower doping. The question is now raised as to whether or not Si is an appropriate material for implementation as Hall effect devices. Si shows only a very moderate carrier mobility when operated at a given supply voltage, but materials such as InAs and InSb would be far superior in this respect. This however changes if the plate has to operate at a given power level which happens to be a considerably more important aspect of modern IC design. As high mobility materials feature small bandgaps, there is no way of obtaining at room temperature the low carrier densities that can be achieved using Si and GaAs. If the plate is operated with a constant current supply, its efficiency doesn't depend upon carrier mobility at all making both Si and GaAs well suited as Hall plate devices. Other criteria to consider are noise, offset and temperature behavior.

## 3.4.2. Electrical Compatibility Concerns

Electrical compatibility concerns are based on the two parasitic electrical effects [8] namely: effective plate thickness variation and leakage current and are associated with the reverse biased pn-junction associated with the Hall plate. Due to the junction field effect, the Hall plate thickness varies with the applied reverse bias junction voltage. There are two factors that come into play here, the first being the fact that the Hall plate introduces a voltage drop causing the effective junction bias to be position dependant and thus the effective plate thickness to vary across the plate. The second is the Hall voltage, due to its dependence upon the plate thickness, now too is affected and ultimately, equation (3.20) and equation (3.22) through equation (3.27) become invalid. However, in bulk Hall plates with nt products of more than  $10^{12} cm^{-2}$ , this effect is rather weak and these equations still yield good approximations. By making the reverse junction bias voltage adjustable, it is possible to vary the effective thickness of the plate and in so doing provides a means of adjusting the sensitivity of the plate. It has been reported that an adjustment range of up to  $\pm 25\%$  have been achieved using this technique.

Up to this time, no major studies have been done on the influence of leakage currents on the integrated Hall plate. The main reason for this is that the leakage current is extremely small when compared to the bias current and thus has little effect. The proposed Hall generator in this design will use a plate size of approximately 8300  $\mu m^2$  (see figure 3.12). The technology specifies 0.25 fA/ $\mu m^2$  leakage current for its n-well resulting in  $\approx$  2.1 pA/plate. The leakage is an order  $10^6$  smaller compared to the bias current of a few hundred  $\mu A$  and can be neglected.

## 3.4.3. Sensitivity

The absolute sensitivity of a Hall plate can be reported in one of two ways, supply-current-related sensitivity (equation (3.27)) and supply-voltage-related sensitivity (equation (3.28)).

$$S_{RI} = \left| \frac{1}{I} \frac{\partial V_H}{\partial B_z} \right| = \frac{r_n G}{qnt} [V/A.T]$$

(3.27)

$$S_{RV} \equiv \left| \frac{1}{V} \frac{\partial V_H}{\partial B_z} \right| = \mu_n^* \frac{w}{l} G[T^{-1}]$$

(3.28)

The theoretical limit for the sensitivity established from equation (3.26) and taking  $r_n \approx 1$ , with appropriate mobility constants at room temperature yields [9],

$$S_{RV,\text{max}} = \begin{cases} 0.128T^{-1} - Si \\ 0.725T^{-1} - GaAs \end{cases}$$

(3.29)

for the two material types.

#### 3.4.4. Noise

One of the major and dominant performance parameters of sensors is the signal to noise ratio (SNR). The voltage noise spectral density across the Hall electrodes is given by

$$S_{V}(f) = S_{V\alpha}(f) + S_{VT}$$

(3.30)

where  $S_{V\alpha}$ , represents the  $f^{-1}$  noise and  $S_{VT}$ , the thermal noise, the first dominating at low frequency and the other at high frequencies respectively.

Maximizing the SNR over the frequency spectrum can thus be divided into, low and high frequencies. The SNR at low frequencies is increased when the Hall plate contains a large number of carriers and is made of a material with a high mobility and a low Hooge  $\alpha$ -parameter. Geometrically, the SNR can be improved by designing for an aspect ratio of  $\frac{l}{w} \approx 1.3$  [8].

High frequencies is dominated by thermal noise and increasing the Hall generator bias current, directly increases the SNR and is limited by the maximum allowable power dissipation in the plate. Using a high mobility material also results in a larger SNR at high frequencies.

### 3.4.5. Offset Voltage

Offset voltage in Hall generators embed themselves as a constant voltage present at the signal contacts in the absence of a magnetic field. The offset voltage is usually reported as an equivalent offset magnetic field or

$$B_{O,eq} = \frac{V_O}{S_A} \tag{3.31}$$

with  $S_A$ , denoting the absolute sensitivity.

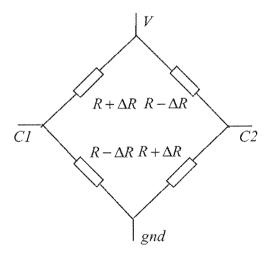

Offsets in Hall plates come from a contribution of a number of factors. The dominant factors come from imperfections in the manufacturing process e.g. misalignment and fluctuations in material characteristics, and piezoresistive effects. These two effects are usually modeled as a simple resistive bridge incorporating asymmetry as shown in figure 3.4. Typical applications require offsets of  $B_{O,eq} < 10$  mT.

Figure 3.4 Bridge circuit model of Hall plate

The second most important source of offset voltage contribution comes in the form of mechanical stress introduced during packaging. Up to  $B_{O,eq} \approx 8.4$  mT, can be introduced here

with the Hall device placed in the (110) crystal plane with current flowing in the <110> [8] direction. Consequently, a Hall plate placed in the (100) plane with a current in the <110> direction makes for a highly sensitive strain gauge [6, 7, 8]. Various techniques exist to reduce or effectively cancel offsets resident in Hall devices [4, 8, 23, 24, 25] and will be discussed in Chapter 4.

### 3.4.6. Linearity Error

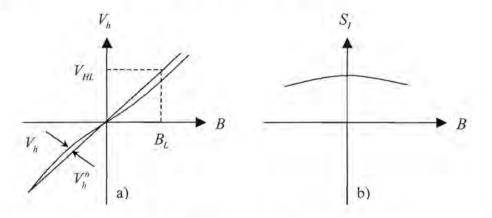

The linearity error is defined as the ratio

$$LE = \frac{\left(V_H - V_H^0\right)}{V_H^0} \tag{3.32}$$

where  $V_H$ , is the measured Hall voltage and  $V_H^0$ , is the assumed best linear fit to the measured values. With a constant bias current,  $V_H^0$  becomes

$$V_H^0 = \frac{V_{HL}}{B_L} B {3.33}$$

with  $V_{HL}$  and  $B_L$  the values as indicated in figure 3.5 a). Figure 3.5 b) shows non-linearity represented as a variation in sensitivity versus the magnetic field.

Figure 3.5 Non-linearity of Hall MFS in terms of a) Hall voltage and b) sensitivity versus magnetic field with constant current bias

This type of geometrical non-linearity is mainly due to the short-circuiting effects described by equation (3.20) and equation (3.22) and can be minimized through the proper resistive loading of the element. One of the lowest linearity error figures reported [26] was

manufactured from an implanted GaAs cross-shaped plate used in the range of less than 1 T at room temperature with an error of  $LE = \pm 3 \times 10^{-4}$ .

## 3.4.7. Temperature Coefficients

The temperature coefficients of the sensitivity are defined by

$$TC \equiv \frac{1}{S} \frac{\partial S}{\partial T} \tag{3.34}$$

with S, the absolute sensitivity or relative sensitivity as defined by equation (3.27) and equation (3.28) and T, the absolute temperature.

It is now assumed that the carrier concentration is constant, the Hall angle is very small and the junction field effect is ignored. If the Hall plate is supplied with a constant current, we obtain from equation (3.27) and equation (3.34) the pertinent temperature coefficient

$$TC_{I} = \frac{1}{r_{n}} \frac{\partial r_{n}}{\partial T} \tag{3.35}$$

It can thus be seen that the temperature coefficient of the sensitivity  $S_{RI}$ , is equal to that of the Hall scattering factor  $r_n$ . Typical values for Si have been experimentally determined to be around  $TC_I \approx +0.8 \times 10^{-3} \text{ K}^{-1}$  [8] for temperatures ranging from  $-20^{\circ}\text{C}$  to  $120^{\circ}\text{C}$  for low-doped Si.

For a constant voltage bias across the plate,

$$TC_{V} = \frac{1}{\mu_{n}^{*}} \frac{\partial \mu_{n}^{*}}{\partial T} \tag{3.36}$$

Typical values for  $TC_V$  in Si, have been determined experimentally to be in the order of -4.5 x  $10^{-3} \text{ K}^{-1}$  [8], for the same temperature range as above. Thermal variations in Hall voltage may be compensated for by proper variation in biasing conditions. Alternatively, the junction field effect can also be used to compensate for variations in sensitivity as discussed earlier.

### 3.4.8. Hall Generator Design

It is desired to design the Hall generator for sensing a vertical magnetic field with the following specifications:

- An expected magnetic field range of 0.1 mT to 100 mT,

- Magnetic field frequency of 45 to 325 Hz, inclusive of the 5<sup>th</sup> harmonic,

- Within specified accuracy for a temperature range of -25°C to 70°C.

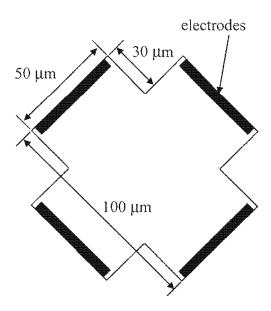

With these specifications in mind, it was found that the cross-shaped Hall plate was well suited to the design criteria and specific application. The device is discussed with reference to the different criteria namely, sensitivity, noise performance, offsets, temperature stability, linearity and technological compatibility with standard CMOS processes. The assumption made now is that the chosen process is based upon a standard silicon  $1.2~\mu m$  CMOS, double metal, double poly process.

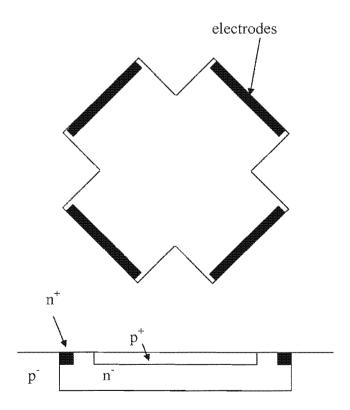

Figure 3.6 Top and cross-section view of the Hall generator geometry

Figure 3.6 shows an illustration of the geometry of the proposed Hall generator. The element is designed as a cross-shaped device. The cross-section view shows how the element is made up. The physical cross consists of an n-well layer inside the low-doped p-type substrate. Highly doped n-type contacts are placed on the n-well edges for ohmic contact into the well according to the layout design rules. Lastly, a strongly doped p-type layer covers the n-well such that a pinched, n-well structure is created. Detailed dimension are given in paragraph 3.6.

### 3.4.9. Sensitivity and Noise

The choice of geometry of the Hall generator can be greatly influenced by the sensitivity requirements and noise performance of the device. A device with higher sensitivity will produce better SNR performance. This does however result in higher power dissipation in the Hall generator. Investigating the theoretical noise performance of Hall plate generators, it was found that the minimum detection levels in the presence of noise was,  $B_{min} \approx 3 \times 10^{-7} \text{ T}$  @ 100 KHz and  $B_{min} \approx 5 \times 10^{-6} \text{ T}$  @ 1 Hz [27] and is typical for plates biased around 0.5 mA [8, 9]. It is desired to detect minimum magnetic field levels of 0.1 mT in the frequency range of 45 to 325 Hz. This makes the minimum detection levels required an order  $10^2$  higher than the minimum, low frequency detection limits. Noise will thus have little effect on the performance of the device. It can also be seen that the noise performance of Hall generators improves at higher signal frequencies.

From equation (3.10) it was seen that to maximize the Hall voltage, it was necessary to maximize the biasing current. When designed in optimum ratios, the cross-shaped Hall plate or generator will measure approximately 2 squares between terminals. (see figure 3.12). From experimental data, a pinched n-well resistor shows approximately 1.5 k $\Omega$ / sheet resistance for the given technology. This implies a 3 k $\Omega$  resistance between biasing and sensing electrodes. To ensure minimum detection limits remain negligible, a biasing current of 0.5 mA is proposed and is below the plate's maximum power dissipation levels of 6 mW, determined from previous experimental data. Taking into consideration that the n-well sheet resistance may vary up to 20% as well as the need for low power dissipation, a maximum bias current of 300  $\mu$ A will be implemented. This will also leave enough room for multiple Hall plate implementations without excessive power consumption. Lastly, this ensures that the biasing conditions of the Hall generator can be varied and used as a calibration parameter.

## 3.4.10. Linearity

Linearity errors are largely dependent upon the difference in contact area (short-circuiting effects) and non-uniformity of the Hall generator material. With this in mind, non-linearity becomes a practical problem that needs to be analyzed specific to the proposed technology being used. Techniques exist for reducing non-linearity such as correct resistive loading of the elements which also become process specific (doping concentrations, dopants etc.). Linearity is expected to be in the range  $LE = \pm 0.03$  %. Cross-shaped Hall plates are the most suited to this application with their highly linear characteristics. This is due to the fact that the geometrical design reduces the short-circuiting effects that are the major source for non-linearity.

### 3.4.11. Temperature

The proposed technology uses donor concentrations of approximately 3 x  $10^{16}$  cm<sup>-3</sup>, and is low-doped (n-well). The temperature coefficients are thus expected to be in the order of  $TC_I \approx +10^{-3}$  K<sup>-1</sup> for standard Si at a temperature ranging between -25 °C and 70 °C. Temperature affects both the sensitivity as well as the offset voltage of the device. Sensitivity compensation can be achieved fairly easily through the measurement of chip temperature and varying the bias conditions of the Hall generator accordingly [8]. This will be accomplished through the use of a similar pinched, n-well resistive structure with the same temperature coefficient as the Hall generator. Offset cancellation will take place dynamically using quadrature offset cancellation techniques [4].

#### 3.4.12. Offsets

Once again, offsets are dominated by the specific technology. It was seen that Hall plates generally show small offsets. Offset cancellation techniques will be applied to reduce any offsets inherent in the Hall generator. This once again proves to be a problem to be solved through signal conditioning external to the plate but an attempt should be made to keep offsets to a minimum, through careful design and orientation of the Hall generator itself. It is proposed to place the Hall device in the (110) crystal plane with current flowing in the <110> direction. This minimizes the piezoresistive effects and significantly reduces the offset. Furthermore, a dynamic quadrature offset cancellation technique will be implemented [4] whereby the offset signal is translated to a higher frequency and isolated through filtering.

According to the data given in addendum A and the requirements set out in this chapter, the following parameters were calculated based on equations (3.1) to (3.19).

$$\mu_n = 545 \text{ cm}^2/\text{V/s}$$

$\mu_n^* = 625 \text{ cm}^2/\text{V/s}$

$n = 3 \times 10^{16} \text{ cm}^{-3} = 3 \times 10^{22} \text{ m}^{-3}$

$t_{eff} = 1.17 \text{ } \mu\text{m}$

$r_n = 1.15 \text{ for Si}$

$q = 1.6 \times 10^{-19} \text{ C}$

Then from equation (3.10) and equation (3.27) with G = 1,

$$R_H = 218.75 \,\mu\text{V.m/A/T}$$

and  $\sigma_n = 286 \,(\Omega\text{m})^{-1}$   $R_{plate} = 3 \,\text{k}\Omega$   $S_{RI} = 187.5 \,\text{V/A/T}$

This data can now be used to configure the simulation model required for the system design.

## 3.5. SIMULATION

#### 3.5.1. Simulation Model for Hall Plate

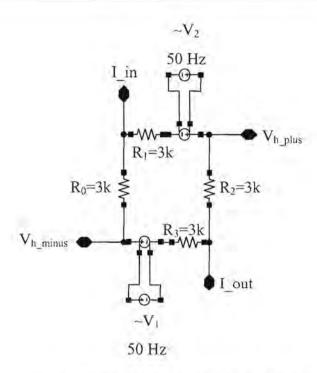

The simulation model for the Hall plate model will be based on the model shown in figure 3.4. This model simulates a first order approximation of the Hall plate and can be used for simulating both the sensitivity and offset inherent in the devices. The model is displayed in figure 3.7 and a transient simulation was done to show how the output responds. The model uses voltage controlled voltage sources to represent the magnetic field magnitude and uses a scale factor similar to that of the gain of the Hall plate to transform the "magnetic field" into the Hall voltage. This voltage is then measured across the output terminals Vh\_plus and Vh\_minus.

Figure 3.7 Simulation model used for Hall plate

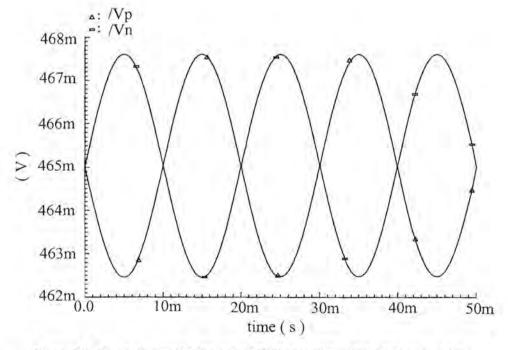

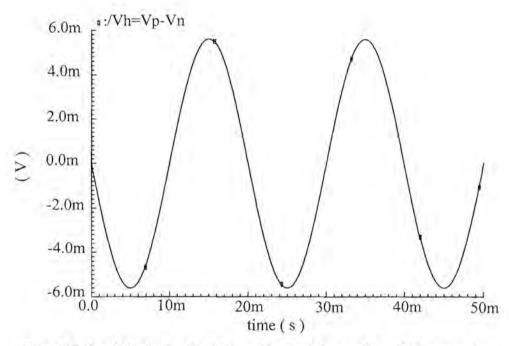

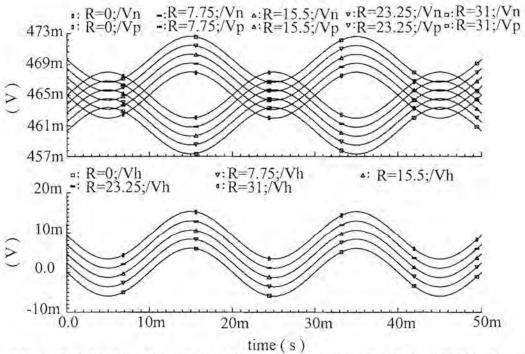

The output simulation is shown in figure 3.8 where it can be seen how each output displays a voltage signal of 3 mV and is  $180^{\circ}$  out of phase with each other. Taking the difference in the outputs results in figure 3.9 and represents the effective Hall voltage of the Hall generator in the presence of an ac magnetic field biased at  $300 \, \mu A$  dc. A peak magnetic field of  $100 \, mT$  results in an expected output Hall voltage of  $5.625 \, mV_{peak}$ .

Figure 3.8 Graph displaying the output Voltages of the Hall plate versus time

Figure 3.10 shows the simulation results for a change in the resistance gradient through the Hall plate. The simulation was again based on the model in figure 3.4 and figure 3.7. The results show how much the offset can change for a gradient change of up to 2% between the four corners. This result show that offsets of up to 9 mV or almost 200 mT could result in such extreme cases. Experimental data show that the proposed technology has an average gradient variation of approximately 0.2% thus yielding expected offsets in the range of less than 2 mV or 30 mT. Although this value is small, it suggests an offset line current of about 24 A or 5.3 Kw given an assumed linear transfer of the line current to magnetic field and should thus be compensated for.

Figure 3.9 Graph displaying the differential output between Vp and Vn versus time.

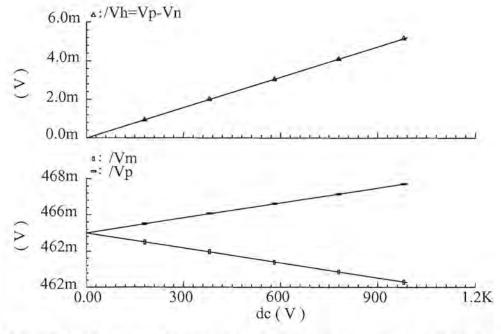

Figure 3.11 shows the transfer function for the Hall plate as a DC response. The graph consists of two parts namely the upper graph illustrating the differential Hall voltage and the lower Hall voltage illustrating the separate terminal voltages both as a function of the input line current ranging between 0 and 80 A and with the line voltage held constant. Voltage sources were used to simulate the line current in the Hall simulation model, where 1 kV equates to 80 A and 0 V equates to 0 A. The Hall voltage thus represents the consumed active power in the line. It can be clearly seen that the output Hall voltage is a linear function and is directly proportional to the input current when the line voltage is held constant.

Figure 3.10 Simulation showing offset voltages inherent in output versus time for a variation of up to 2% in resistance gradient

Figure 3.11 Graph showing transfer function of Hall generator with respect to changing line current where 1 kV equates to 80 A

### 3.6. EXPERIMENTAL VERIFICATION

A Hall effect device was manufactured in the proposed standard CMOS 1.2 µm technology and used to verify all the performance characteristics of the device. This section presents measurements of the electrical and magnetic device parameters of the cross-shaped Hall generator with dimension as illustrated in figure 3.12.

Figure 3.12 Cross-shaped Hall generator illustrating dimensions implemented

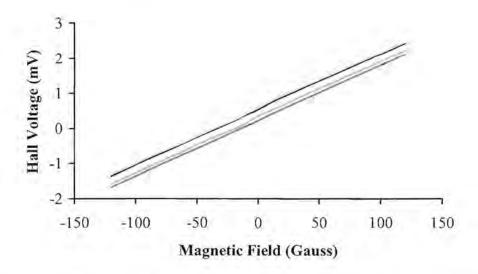

Mathematical approximations in paragraph 3.3. and 3.4. are now combined for comparison with physical behavior. Any deficiencies can thus be revealed and discussed and suggestions can be made for rectifying any under performance of the device. The device was tested according to the characteristics set out in paragraph 3.4.8. For most of the test procedure, unless otherwise specified, the characterization of the sensor was done at room temperature using a wire-wound ferromagnetic core as a magnetic transducer providing magnetic flux densities of up to 100 mT.

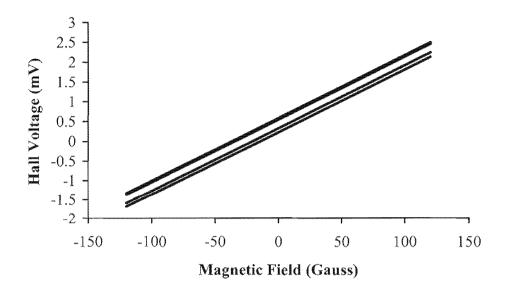

### 3.6.1. Sensitivity

The first parameter measured was the sensitivity of the device and to maximize the sensitivity for easier measurement, a biasing current of 1 mA was used. Passing current through the conductor of the wire-wound ferromagnetic core generated the magnetic field required for the measurements. A total of 12 devices were measured and the results of 4 chosen at random are presented in table 3.1 and figure 3.13.

Table 3.1 Measured sensitivity for cross-shaped Hall plate

| Sensor number | Measured sensitivity $S_{RI}$<br>(V/A/T) |  |  |

|---------------|------------------------------------------|--|--|

| 1             | 158.75                                   |  |  |

| 2             | 158.33                                   |  |  |

| 3             | 157.92                                   |  |  |

| 4             | 158.75                                   |  |  |

Figure 3.13 Graph showing the Hall voltage versus magnetic field of 4 independent samples

From equation (3.27) the geometrical correction factor could be determined when compared to an ideally calculated sensitivity i.e. G=1. This factor was determined to be G=0.845. Figure 3.14 shows the geometrical factor for a cross-shaped plate with  $m=\frac{\theta_H}{\pi/2}$ , and  $\lambda=\frac{c}{b}$ , where c= total electrode length and b= plate boundary length [8]. From figure 3.12, these values are determined as  $\lambda=0.455$ , and  $m\approx\frac{0.07}{\pi/2}$  (with  $\theta_H$  small i.e. 2°), this factor is justified.

Figure 3.14 Graph showing the reciprocal value of the geometrical correction factor for the crossshaped Hall plate

The minimum detection level was determined by the available laboratory equipment and a 10  $\mu$ V change was detectable. From equation (3.27) it can be seen that this results in a magnetic field, current product of  $IB = 6.3 \times 10^{-8}$  or 2.1 Gauss @ 300  $\mu$ A. When translating this variable into measured current, 2.1 Gauss represents a resolution of 70 mA. Once amplified, this resolution will be increased by the gain factor incorporated. It will thus be necessary to increase the bias current to 350  $\mu$ A<sub>peak</sub> to compensate for this loss in sensitivity resulting from the influence of the geometrical correction factor.

#### 3.6.2. Offsets

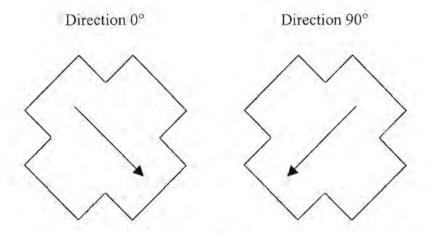

Table 3.2 shows the measured offsets of the 4 devices from the same wafer. Offsets were measured in two biasing directions separated by 90° as shown in figure 3.15 in the absence of a magnetic field. This will later form the dynamic behavior behind the offset cancellation scheme. These input offsets were measured for different biasing currents and the need for dynamic offset cancellation techniques was established here as the offset shows bias current dependence. The devices all showed similar offset properties and the reason for this is that the devices were all from the same wafer. This is also evident from the same polarities displayed in each sensor. As the biasing current is relatively small, the opposite polarity offsets are identical. These will however show signs of deviation under large current bias conditions.

Figure 3.15 Biasing conditions showing 90° rotations in current

Table 3.2 Measured offsets under varying biasing conditions

| Sensor Number | Biasing current (μA) | Direction 0° (mV) | Direction 90° |  |

|---------------|----------------------|-------------------|---------------|--|

| 1             | 100                  | 0.02              | - 0.02        |  |

|               | 200                  | 0.03              | - 0.03        |  |

|               | 300                  | 0.04              | - 0.04        |  |

| 2             | 100                  | 0.03              | - 0.03        |  |

|               | 200                  | 0.04              | - 0.04        |  |

|               | 300                  | 0,06              | - 0.06        |  |

| 3             | 100                  | 0.04              | - 0.04        |  |

|               | 200                  | 0.06              | - 0.06        |  |

|               | 300                  | 0.09              | - 0.09        |  |

| 4             | 100                  | 0.01              | - 0.01        |  |

|               | 200                  | 0.02              | - 0.02        |  |

|               | 300                  | 0.03              | - 0.03        |  |

### 3.6.3. Linearity Errors

Linear regression models served the basis for determining the linearity and the results are shown in figure 3.16. It can be seen that  $R^2 \approx 1$ . This was expected as the cross-shaped geometries have high performance in this respect [26]. Furthermore, it must be mentioned that only 10  $\mu$ V changes were measurable and this in itself causes a significant measuring inaccuracy.

Figure 3.16 Graph showing linear regression models of the Hall generator transfer functions versus magnetic field

Table 3.3 shows the linear first-order transfer functions for devices 1 to 4 presented in figure 3.13 respectively where V, represents the predicted Hall voltage in mV for a given magnetic field strength of B Gauss. The slope indicates the sensitivity of the device in V/G and the constant offset in mV at the given bias conditions. The  $R^2$  factor represents how well the model defines the experimental data where  $R^2 = 1$  represents and ideal linear fit. As seen from this, the sensors appear to show a high degree of linearity and will be fit for the application.

Table 3.3 Table showing first-order transfer functions determined through linear regression

|                   | Sensor 1          | Sensor 2          | Sensor 3         | Sensor 4          |

|-------------------|-------------------|-------------------|------------------|-------------------|

| Transfer function | $V_I = 0.0159B +$ | $V_2 = 0.0159B +$ | $V_3 = 0.0159$ B | $V_4 = 0.0159B +$ |

| (mV)              | 0.5488            | 0.2276            | + 0.5847         | 0.3282            |

| $R^2$ value       | $R^2_1 = 0.9999$  | $R^2_2 = 1$       | $R^2_3 = 0.9998$ | $R^2_4 = 0.9999$  |

#### 3.6.4. Temperature Behavior

The experiment was divided into two parts, the first to test the influence of temperature on the offset voltage and the second to test the influence of temperature on the sensitivity. The

results showed that the sensitivity had a temperature coefficient of  $TC_I \approx +3 \times 10^{-3} \text{ K}^{-1}$  for a temperature range of -25 °C to 70 °C and was as a direct result of a change in the Hall factor as explained in paragraph 3.4.7. The resultant effect was a directly proportional change in the sensitivity as well as the offsets. Once again the importance of dynamic offset cancellation is demonstrated as it can be seen how the offset varies with temperature. The variation in offsets with respect to temperature displayed a positive temperature coefficient. As the offset will be dynamically measured and cancelled, its magnitude has no effect. Compensation for the change in sensitivity is however of great importance as a  $TC_I$  of  $+3 \times 10^{-3}$  K<sup>-1</sup> represents a sensitivity change of 48 V/A/T across the required temperature range. Furthermore, this temperature coefficient is not completely linear and thus compensation using the same pinched, n-well resistive structure is of the essence and will be implemented in the amplifier gain stages.

### 3.7. CONCLUSION

In this chapter the galvanomagnetic properties of silicon leading to the formulation of the Hall effect was presented as a basis for designing, simulating and verifying the Hall generator. After a brief introduction to Hall effect based power sensors, the galvanomagnetic transport equations were discussed. From these equations it was found that for a given technology, the biasing current is the only parameter having influence on the Hall voltage. Following this, the bulk Hall effect device in silicon was presented as a basis for measuring the performance of other geometrical derivatives. The device was then analyzed in terms of electrical performance characteristics comprising of sensitivity, noise, offset characteristics, linearity and temperature behavior. These characteristics were then followed as the design procedure for the Hall generator along with the given requirements and technology data. A simulation model was developed and simulated so as to study the basic behavior of the sensor. A physical device was manufactured for experimental verification and the results of the proposed mathematical approximations agree well with the physical results. The knowledge in this chapter will be used in subsequent chapters for the design of the support circuitry required such as to complete a fully functional device.