#### DESIGN METHODS FOR INTEGRATED SWITCHING-MODE POWER AMPLIFIERS

by

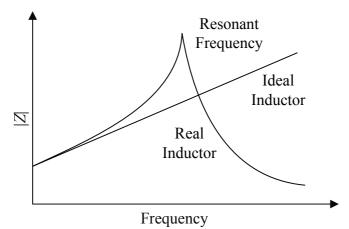

Mladen Božanić

Submitted in partial fulfilment of the requirements for the degree

#### **Philosophiae Doctor (Electronic Engineering)**

in the

Department of Electrical, Electronic and Computer Engineering Faculty of Engineering, Built Environment & Information Technology

#### UNIVERSITY OF PRETORIA

July 2011

(Non-disclosure version)

© University of Pretoria

#### SUMMARY

## DESIGN METHODS FOR INTEGRATED SWITCHING-MODE POWER AMPLIFIERS

by

#### Mladen Božanić

| Supervisor: | Prof S Sinha                                                                                                                                                                                                              |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Department: | Electrical, Electronic and Computer Engineering                                                                                                                                                                           |

| University: | University of Pretoria                                                                                                                                                                                                    |

| Degree:     | PhD (Electronic Engineering)                                                                                                                                                                                              |

| Keywords:   | Power amplifier, spiral inductor, switch-mode amplifier, Class-E<br>amplifier, Class-F amplifier, impedance matching, streamlined design,<br>SPICE netlist, BiCMOS, 0.35 µm process, 180 nm process, software<br>routine. |

While a lot of time and resources have been placed into transceiver design, due to the pace of a conventional engineering design process, the design of a power amplifier is often completed using scattered resources; and not always in a methodological manner, and frequently even by an iterative trial and error process.

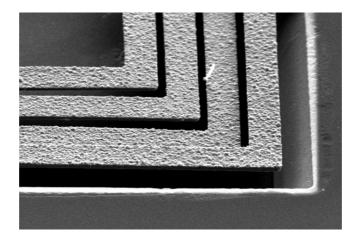

In this thesis, a research question is posed which enables for the investigation of the possibility of streamlining the design flow for power amplifiers. After thorough theoretical investigation of existing power amplifier design methods and modelling, inductors inevitably used in power amplifier design were identified as a major drawback to efficient design, even when examples of inductors are packaged in design HIT-Kits. The main contribution of this research is engineering of an inductor design process, which in-effect contributes towards enhancing conventional power amplifiers. This inductance search algorithm finds the highest quality factor configuration of a single-layer square spiral inductor within certain tolerance using formulae for inductance and inductor parasitics of traditional single- $\pi$  inductor model. Further contribution of this research is a set of algorithms for the complete design of switch-mode (Class-E and Class-F) power amplifiers and their output matching networks. These algorithms make use of classic deterministic design equations so that values of parasitic components can be calculated given input parameters, including required output power, centre frequency, supply voltage, and choice of class of operation.

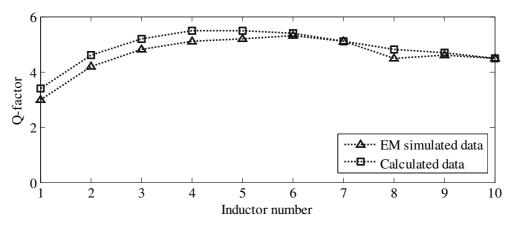

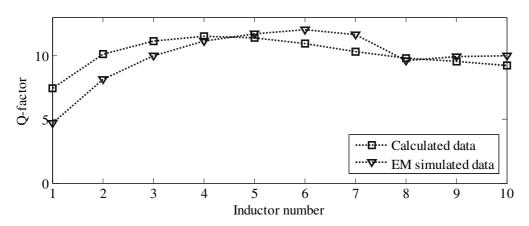

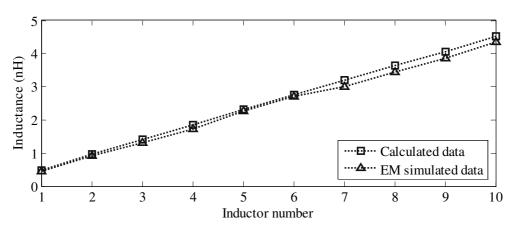

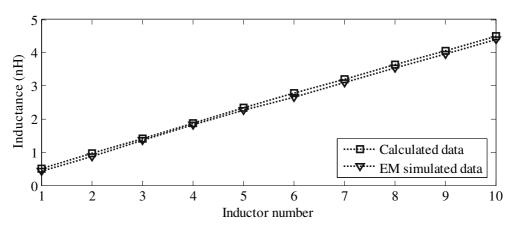

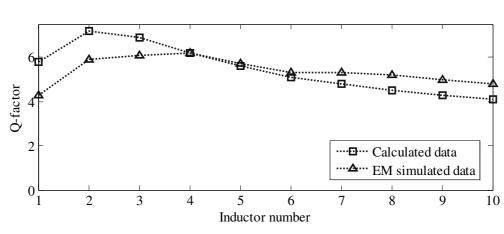

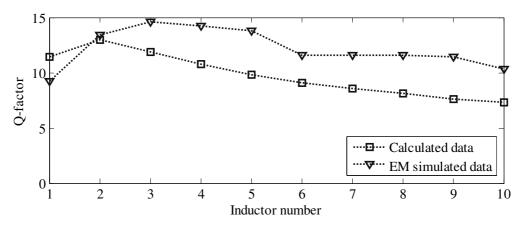

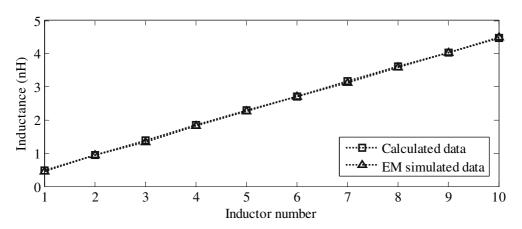

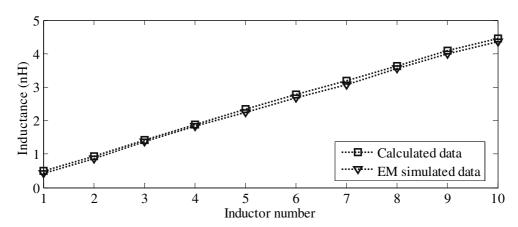

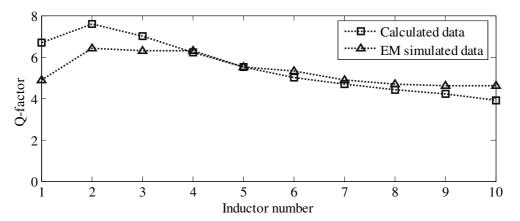

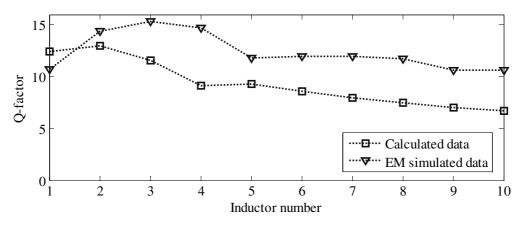

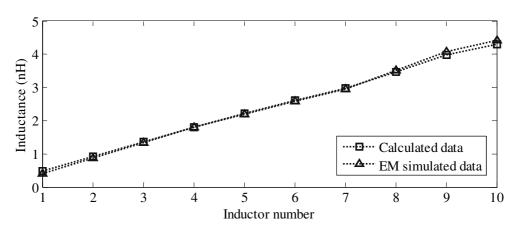

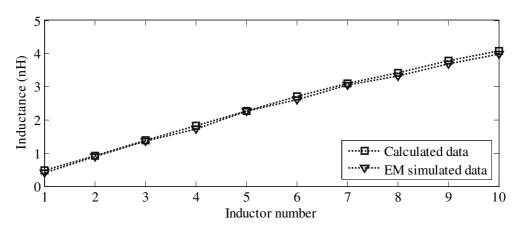

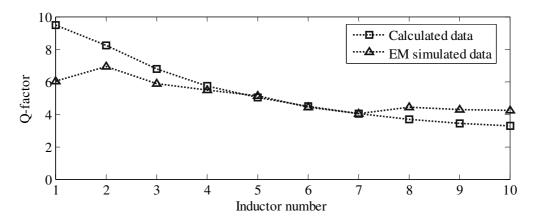

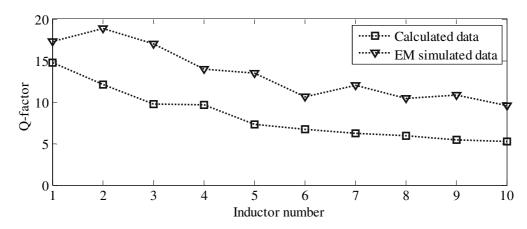

The hypothesis was satisfied for SiGe BiCMOS S35 process from Austriamicrosystems (AMS). Several metal-3 and thick-metal inductors were designed using the abovementioned algorithm and compared with experimental results provided by AMS. Correspondence was established between designed, experimental and EM simulation results, enabling qualification of inductors other than those with experimental results

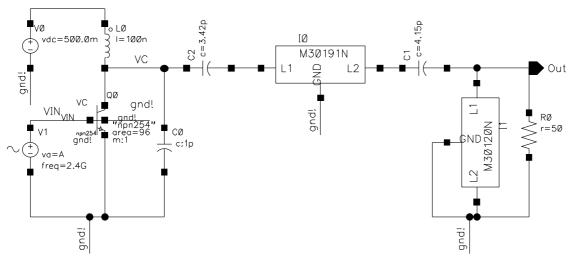

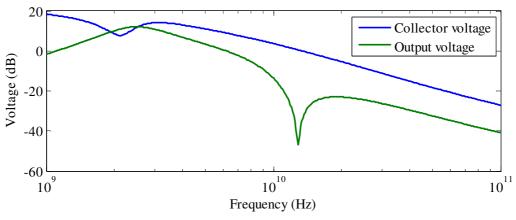

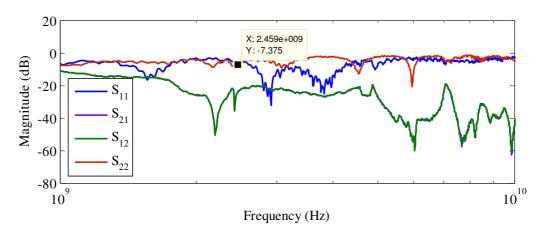

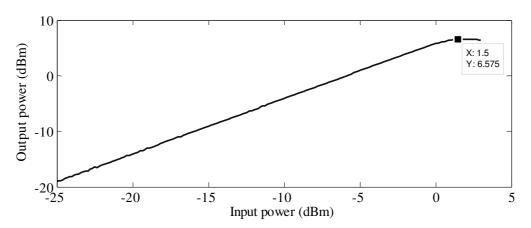

available from AMS by means of EM simulations with average relative errors of 3.7 % for inductance and 21 % for the Q factor at its peak frequency. For a wide range of inductors, Q-factors of 10 and more were readily experienced. Furthermore, simulations were performed for number of Class-E and Class-F amplifier configurations with HBTs with  $f_t$ greater than 60 GHz and total emitter area of 96  $\mu$ m<sup>2</sup> as driving transistors to complete the hypothesis testing. For the complete PA system design (including inductors), simulations showed that switch-mode power amplifiers for 50  $\Omega$  load at 2.4 GHz centre frequency can be designed using the streamlined method of this research for the output power of about 6 dB less than aimed. This power loss was expected, since it can be attributed to non-ideal properties of the driving transistor and Q-factor limitations of the integrated inductors, assumptions which the computations of the routine were based on. Although these results were obtained for a single micro-process, it was further speculated that outcome of this research has a general contribution, since streamlined method can be used with a much wider range of CMOS and BiCMOS processes, when low-gigahertz operating power amplifiers are needed. This theory was confirmed by means of simulation and fabrication in 180 nm BiCMOS process from IBM, results of which were also presented. The work presented here, was combined with algorithms for SPICE netlist extraction and the spiral inductor layout extraction (CIF and GDSII formats). This secondary research outcome further contributed to the completeness of the design flow.

All the above features showed that the routine developed here is substantially better than cut-and-try methods for design of power amplifiers found in the existing body of knowledge.

#### **OPSOMMING**

## ONWERPMETODES VIR GEÏNTEGREERDE SKAKELMODUS-DRYWINGSVERSTERKERS

deur

#### Mladen Božanić

| Studieleier:   | Prof S Sinha                                                                                                                                                                                                             |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Departement:   | Elektriese, Elektroniese en Rekenaaringenieurswese                                                                                                                                                                       |

| Universiteit:  | Universiteit van Pretoria                                                                                                                                                                                                |

| Graad:         | PhD (Elektroniese-Ingenieurswese)                                                                                                                                                                                        |

| Sleutelwoorde: | Drywingsversterker, spiraalinduktor, skakelmodusversterker, Klas-E versterker, Klas-F versterker, impedansieaanpassing, geoptimeerde ontwerp, SPICE-netlys, BiCMOS, 0.35 $\mu$ m-proses, 180 nm-proses, sagtewareroetine |

Alhoewel baie tyd en hulpbronne spandeer word op die ontwerp van sender/ontvangers, word die onwerp van drywingsversterkers dikwels voltooi met verspreide hulpbronne as gevolg van die tempo van die konvensionele ingenieursontwerpsproses en ook nie altyd op 'n metodiese manier nie, wat daartoe lei dat dit soms 'n iteratiewe proses raak.

In hierdie tesis word 'n navorsingsvraag gevra wat lei tot die ondersoek van die moontlikheid om die ontwerpsvloei van drywingsversterkers te optimeer. Na 'n sorgvuldige ondersoek van bestaande drywingsversterkerontwerpmetodes en modellering is die noodwendige gebruik van induktors geïdentifiseer as een van die groot struikelblokke in doeltreffende ontwerp, selfs wanneer induktorvoorbeelde deel vorm van die hoëprestasie-koppelvlakpakket (HIT-kit). Die grootste bydra van hierdie navorsing is die formulering van 'n ontwerpproses vir induktors, wat dan ook bydra tot die verbetering van konvensionele drywingsversterkers. Hierdie soekalgoritme vind die uitleg van 'n enkellaag- reghoekige spiraalinduktor met die hoogste kwaliteitfaktor binne sekere toleransies deur die formules vir die induktansie- en induktor- parasitiese komponente van die tradisionele enkel- $\pi$ -induktormodel te gebruik. 'n Verdere bydrae van die navorsing is 'n stel algoritmes vir die volledige ontwerp van skakelmodus- (Klas-E en Klas-F) drywingsversterkers sowel as uitset-aanpasnetwerke. Hierdie algoritmes maak gebruik van die klassieke deterministiese ontwerpsvergelykings sodat die waardes van die parasitiese komponente bereken kan word vir gegewe insetparameters, wat die vereiste uitsetdrywing, werksfrekwensie, toevoerspanning en keuse van versterkerklas insluit.

Die hipotese is bewys in 'n SiGe BiCMOS S35-proses van Austriamicrosystems (AMS). Verskeie drie-metaal en dikmetaal-induktors is ontwerp deur bogenoemde algoritmes te gebruik en is vergelyk met die eksperimentele resultate wat deur AMS voorsien is.

Ooreenstemming is gevind tussen die ontwerps-, eksperimentele en elektromagnetiese simulasieresultate, wat die kwalifikasie van induktors, anders as dié waarvoor eksperimentele resultate van AMS beskikbaar is, moontlik maak deur die gebruik van EMsimulasies met 'n gemiddelde fout van 3.7 % vir die induktansie en 21 % vir die kwaliteitfaktor by die piekfrekwensie. Vir 'n wye verskeidenheid induktors is kwaliteitfaktors van 10 of meer gevind. Verder is simulasies gedoen vir 'n aantal Klas-E en Klas-F versterkerkonfigurasies met hetero-voegvlaktransistors met  $f_T$  groter as 60 GHz en 'n totale emitterarea van 96  $\mu$ m<sup>2</sup> as drywingstransistor om die hipotesetoetsing te voltooi. Vir die drywingsversterkerstelselontwerp (wat induktors insluit) het simulasies gewys dat skakelmodusdrywingsversterkers vir 'n 50  $\Omega$  las by 'n 2.4 GHz-werksfrekwensie ontwerp kan word deur die geoptimeerde metode in hierdie navorsing te gebruik, in welke geval die uitsetdrywing ongeveer 6 dB minder is as waarvoor ontwerp is. Hierdie drywingsverlies is verwag, aangesien dit toegeskryf kan word aan die nie-ideale eienskappe van die drywingstransistor en die kwaliteitfaktorbeperkings van die geïntegreerde induktors, sowel as die aannames wat gemaak is in die berekeninge in die ontwerpproses. Alhoewel hierdie resultate vir 'n enkele mikroproses verkry is, is gevind dat hierdie navorsingsuitset steeds 'n algemene bydrae is deurdat die proses gebruik kan word vir 'n verskeidenheid CMOSen BiCMOS-prosesse, wanneer laegigahertz-drywingsversterkers vereis word. Hierdie teorie is bevestig deur middel van simulasie en vervaardiging in die 180-nm BICMOSproses van IBM, waarvan die resultate ook voorgelê is. Die werk wat hier aangebied word, is gekombineerd met algoritmes wat SPICE netlyste formuleer en ook die spiraalinduktoruitleg skryf in die CIF- en GDSII-formate.

Al bogenoemde kenmerke wys dat die roetine wat geformuleer is, aansienlik beter is as lukrake iteratiewe metodes vir drywingsversterkerontwerp wat in die bestaande literatuur gevind word.

## **ACKNOWLEDGEMENTS**

This research would have not been possible without my supervisor, mentor and dear friend Saurabh Sinha, who had encouraged me to take up postgraduate studies at Carl and Emily Fuchs Institute for Microelectronics (CEFIM). I also thank him for providing necessary funding for the research, and everything else he has done to make this experience as painless as possible.

I also thank Marius Goosen and Marnus Weststrate whose teamwork I appreciated during our joint MPW run. I extend special thanks to Marnus, who also translated the summary of this thesis from English to Afrikaans. I would also like to thank my friend and colleague Tjaart Opperman for providing initial guidance and suggestions for my research.

I would also like to thank Jannes Venter for providing the support for Cadence Virtuoso at CEFIM and for his time spent in configuring the Cadence servers.

I thank other people of CEFIM for providing guidance or co-authoring research papers: Prof Monuko du Plessis and Johan Schoeman. I also thank Prof Louis Linde whose transceiver topic eventually resulted in my concentrating on the research in the field of power amplification. I thank Tilla Nel for all the administrative work she did for me in the course of my studies. I also thank Dr Alexandru Müller of IMT Romania, a partner of CEFIM, for sponsoring my trip to CAS conference in 2009, which added to the depth of my research.

Thanks also to Neil Naudé of Grintek Ewation and Johann de Jager of CSIR for being so kind as to arrange several IC characterisation sessions in their respective companies' laboratories.

I would like to extend thanks to my parents, who provided funds for my undergraduate studies and for my initial stay in South Africa, and who have trusted in me from the beginning of my academic career. Special thanks go to my mother, Zorana Božanić, who also acted as a proofreader for this thesis.

And last but not least, I thank my company, Azoteq (Pty Ltd), and particularly Dieter Mellet, Dr Frederick Bruwer, also former students or lecturers at CEFIM, as well as Trudie Landman, for their great understanding of my obligations during the course of my research at CEFIM.

#### LIST OF ABBREVIATIONS

| 2-D     | Two-dimensional                                 |

|---------|-------------------------------------------------|

| 3-D     | Three-dimensional                               |

| 3-G     | Third generation                                |

| 3M      | Third metal                                     |

| AC      | Alternating current                             |

| ADE     | Analog Design Environment                       |

| AMS     | Austriamicrosystems                             |

| BiCMOS  | Bipolar complementary metal-oxide semiconductor |

| BJT     | Bipolar junction transistor                     |

| CAD     | Computer-aided design                           |

| CDMA    | Code divison multiple access                    |

| CMOS    | Complementary metal-oxide semiconductor         |

| CIF     | Caltech intermediate form                       |

| DAT     | Distributed active transformer                  |

| DC      | Direct current                                  |

| DRC     | Design rules check                              |

| DSSS    | Direct sequence spread spectrum                 |

| EDA     | Electronic design automation                    |

| EM      | Electromagnetic                                 |

| GaAs    | Gallium-arsenide                                |

| GDS     | Graphic Data System                             |

| GUI     | Graphical user interface                        |

| HBT     | Heterojunction bipolar transistor               |

| HEMT    | High-electron-mobility-transistor               |

| HIT-Kit | High Performance Interface Tool Kit             |

| HS      | High speed                                      |

| HV      | High voltage                                    |

| IBM     | International Business Machines                 |

| ISI     | Institute for Scientific Information            |

| ISM     | Industrial, Scientific and Medical              |

| LF      | Low frequency                                   |

| LNA     | Low-noise amplifier                             |

|         |                                                 |

| LVS         | Layout versus schematic                             |

|-------------|-----------------------------------------------------|

| MEMS        | Microelectro-mechanical system                      |

| MEP         | MOSIS Education Programme                           |

| MESFET      | Metal-semiconductor field-effect transistor         |

| MOSFET      | Metal-oxide semiconductor field-effect transistor   |

| MOSIS       | Metal Oxide Semiconductor Implementation Service    |

| MPW         | Multi-purpose wafer                                 |

| NDA         | Non-disclosure agreement                            |

| NMOS        | n-channel MOS                                       |

| PA          | Power amplifier                                     |

| PAE         | Power added efficiency                              |

| PCB         | Printed circuit board                               |

| PDA         | Personal data assistant                             |

| PEEC        | Partial Element Equivalent Circuit                  |

| pHEMT       | Pseudomorphic HEMT                                  |

| PMOS        | p-channel MOS                                       |

| PWM         | Pulse-width modulated                               |

| Q-factor, Q | Quality factor                                      |

| QFN         | Quad flat no-lead                                   |

| RF          | Radio frequency                                     |

| RFC         | Radio-frequency choke                               |

| RFIC        | Radio-frequency integrated circuit                  |

| RFID        | Radio-frequency identification                      |

| Si          | Silicon                                             |

| SiGe        | Silicon-germanium                                   |

| SMA         | SubMiniature version A                              |

| SPICE       | Simulation program with integrated-circuit emphasis |

| THD         | Total harmonic distortion                           |

| ТМ          | Thick metal                                         |

| VBIC        | Vertical Bipolar Inter-Company                      |

| VCO         | Voltage-controlled oscillator                       |

| WLAN        | Wireless local area network                         |

|             |                                                     |

# TABLE OF CONTENTS

| СНАРТ | TER 1 INTRODUCTION                               | 1  |

|-------|--------------------------------------------------|----|

| 1.1   | BACKGROUND TO THE RESEARCH                       | 1  |

| 1.2   | RESEARCH PROBLEM AND HYPOTHESIS                  | 3  |

| 1.3   | JUSTIFICATION FOR THE RESEARCH                   | 4  |

| 1.4   | METHODOLOGY                                      | 4  |

| 1.5   | DEFINITIONS                                      | 4  |

| 1.6   | DELIMITATIONS OF SCOPE AND KEY ASSUMPTIONS       | 5  |

| 1.7   | CONTRIBUTION OF THE RESEARCH                     | 5  |

| 1.8   | PUBLICATIONS LEADING FROM THIS RESEARCH          | 9  |

| 1.9   | OUTLINE OF THIS THESIS                           |    |

| 1.10  | CONCLUSION                                       | 11 |

| СНАРТ | TER 2 LITERATURE REVIEW                          | 12 |

| 2.1   | INTRODUCTION                                     | 12 |

| 2.2   | POWER AMPLIFICATION                              | 12 |

| 2.2   | .1 Power capability                              | 13 |

| 2.2   | .2 Power consumption                             | 13 |

| 2.2   | .3 Power efficiency                              | 14 |

| 2.2   | .4 Matching for desired power                    | 15 |

| 2.2   | .5 Classification of PAs                         | 16 |

| 2.2   | .6 Techniques for performance improvement of PAs |    |

| 2.2   | .7 Temperature aspects of PAs                    |    |

| 2.2   | .8 Biasing                                       |    |

| 2.3   | INDUCTORS FOR POWER AMPLIFIER IMPLEMENTATIONS    |    |

| 2.3   | .1 Inductor implementation options               |    |

| 2.3   | .2 Spiral inductors on silicon and SiGe          |    |

| 2.4   | TECHNOLOGIES FOR POWER AMPLIFIER INTEGRATION     | 50 |

| 2.5   | RAPID POWER AMPLIFIER DESIGN AND AUTOMATION      |    |

| 2.5   | .1 The need for rapid PA design                  |    |

| 2.5   | .2 Automating the rapid PA design                |    |

| 2.6   | CONCLUSION                                       |    |

| СНАРТ | TER 3 METHODOLOGY                                | 55 |

| 3.1   | INTRODUCTION                                     |    |

| 3.2   | RE   | SEARCH METHODOLOGY OUTLINE                                  | 55 |

|-------|------|-------------------------------------------------------------|----|

| 3.3   | TH   | E IC PROCESS                                                | 56 |

| 3.4   | CO   | NCEPTUAL DESIGN AND ALGORITHM DEVELOPMENT                   | 57 |

| 3.5   | MC   | DELLING, SIMULATION, AND LAYOUT DESIGN                      | 57 |

| 3.5   | .1   | Modelling and simulation                                    | 57 |

| 3.5   | .2   | Layout design and verification                              | 58 |

| 3.5   | .3   | EM simulation                                               | 58 |

| 3.5   | .4   | SPICE model of the HBT                                      | 58 |

| 3.6   | ME   | ASUREMENT SETUP AND EQUIPMENT                               | 59 |

| 3.7   | CO   | NCLUSION                                                    | 59 |

| СНАРТ | ER   | 4 SYSTEM LEVEL DESIGN ROUTINE                               | 61 |

| 4.1   | INT  | TRODUCTION                                                  | 61 |

| 4.2   | ME   | THOD FOR DESIGNING THE CLASS-E POWER AMPLIFIERS             | 61 |

| 4.2   | .1   | Input parameters                                            | 62 |

| 4.2   | .2   | Subroutine outputs                                          | 63 |

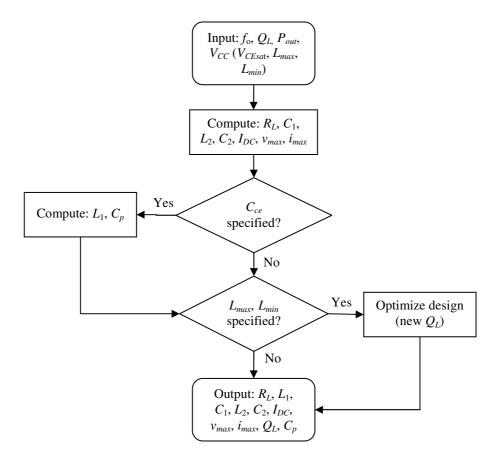

| 4.2   | .3   | Description and flow diagram of the Class-E subroutine      | 64 |

| 4.3   | ME   | THOD FOR DESIGNING THE CLASS-F POWER AMPLIFIERS             | 65 |

| 4.3   | .1   | Input parameters                                            | 66 |

| 4.3   | .2   | Subroutine outputs                                          | 68 |

| 4.3   | .3   | Description and flow diagram of the Class-F subroutine      | 68 |

| 4.4   | ME   | THOD FOR OUTPUT MATCHING                                    | 70 |

| 4.4   | .1   | Input parameters                                            | 70 |

| 4.4   | .2   | Subroutine outputs                                          | 70 |

| 4.4   | .3   | Description of the matching network subroutine              | 70 |

| 4.5   | ME   | THOD FOR DESIGNING SPIRAL INDUCTORS                         | 74 |

| 4.5   | .1   | Input parameters                                            | 75 |

| 4.5   | .2   | Subroutine outputs                                          | 77 |

| 4.5   | .3   | Description and flow diagrams of inductor design subroutine | 78 |

| 4.6   | MA   | ATCHING AND BIASING AT THE INPUT SIDE OF THE POWER          |    |

| AMP   | LIFI | ER                                                          | 80 |

| 4.7   | CO   | MPLETE SYSTEM INTEGRATION                                   | 83 |

| 4.7   | .1   | Input parameters                                            | 83 |

| 4.7   | .2   | Routine outputs                                             | 83 |

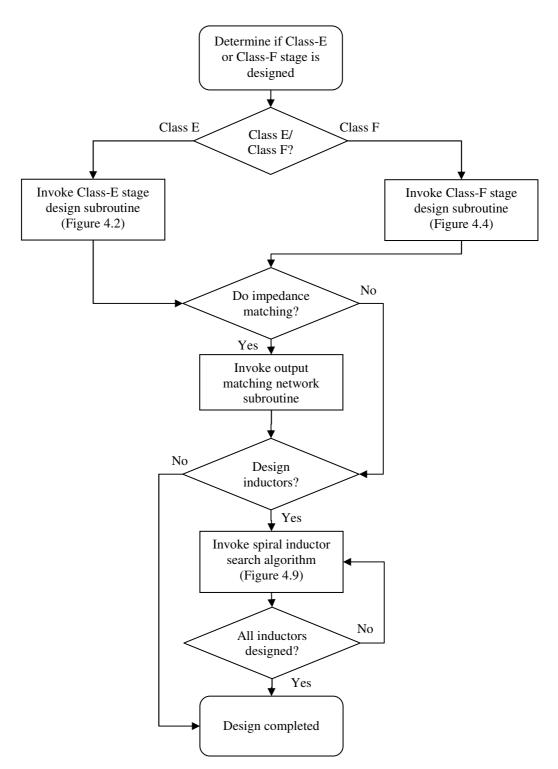

| 4.7   | .3   | Description and flow diagram of the PA design routine       | 84 |

| 4.8   | CONC          | LUSION                                            | 86     |

|-------|---------------|---------------------------------------------------|--------|

| CHAPT | FER 5         | FULL CIRCUIT DESIGN AND SIMULATION                | 88     |

| 5.1   | INTRO         | DDUCTION                                          | 88     |

| 5.2   | VERIF         | FICATION OF THE SPIRAL INDUCTOR MODEL AND THE     |        |

| INDU  | JCTAN         | CE SEARCH ALGORITHM                               | 88     |

| 5.3   | VERIF         | FICATION OF THE FULL SYSTEM INTEGRATION ROUTINE   | 97     |

| 5.3   | .1 Lo         | ower power Class-E configuration                  | 97     |

| 5.3   | .2 Hi         | gher power Class-E configuration                  | 103    |

| 5.3   | .3 Lo         | ower power Class-F configuration                  | 109    |

| 5.3   | .4 Hi         | gher power Class-F configuration                  | 114    |

| 5.3   | .5 Cł         | noice of better Class-E and Class-F configuration | 120    |

| 5.4   | FURTI         | HER DESIGN OF THE CLASS-E AMPLIFIER               | 121    |

| 5.5   | FURTI         | HER DESIGN OF THE CLASS-F AMPLIFIER               | 125    |

| 5.6   | CONC          | LUSION                                            | 129    |

| CHAPT | FER 6         | LAYOUT, FABRICATION AND MEASUREMENT RESULT        | 'S 130 |

| 6.1   | INTRO         | DDUCTION                                          | 130    |

| 6.1   | .1 In         | ductor measurements                               | 130    |

| 6.2   | FULL          | SYSTEM INTEGRATION MEASUREMENTS                   | 131    |

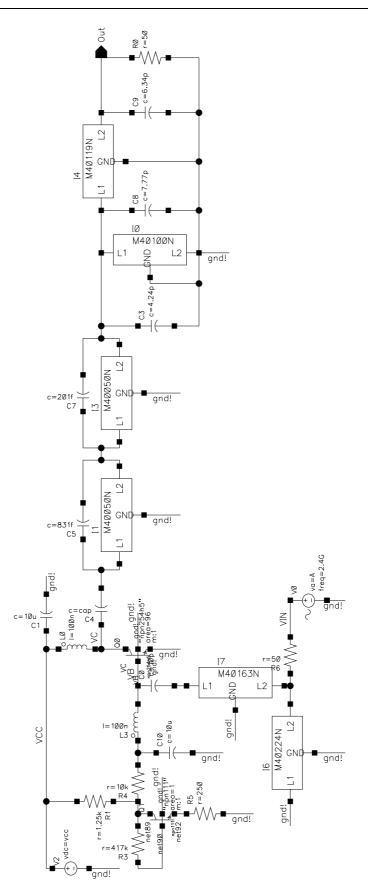

| 6.2   | .1 Ci         | rcuit layouts                                     | 131    |

| 6.2   | 2.2 Pa        | ckaging                                           | 134    |

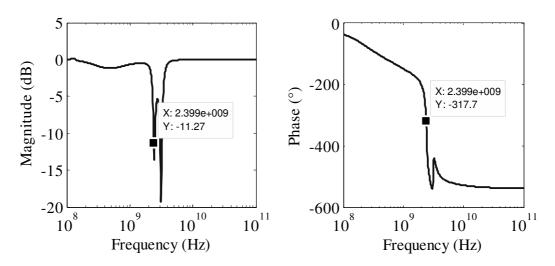

| 6.2   | 2.3 Pa        | ckage simulations                                 | 135    |

| 6.2   | .4 Th         | ne PCB design                                     | 137    |

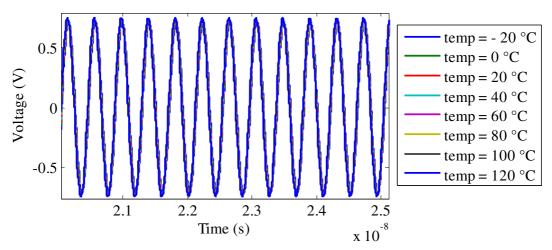

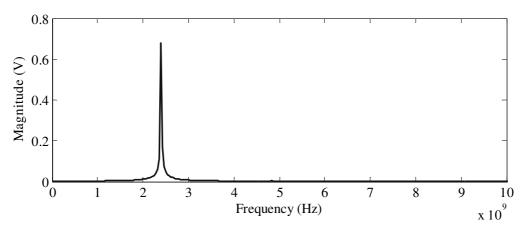

| 6.2   | .5 M          | easurement results                                | 138    |

| 6.3   | CONC          | LUSION                                            | 140    |

| CHAPT | Γ <b>ER 7</b> | CONCLUSIONS AND IMPLICATIONS                      | 142    |

| 7.1   | INTRO         | DUCTION                                           | 142    |

| 7.2   | CONC          | LUSIONS ABOUT THE RESEARCH PROBLEM                | 142    |

| 7.3   | IMPLI         | CATIONS FOR THE THEORY                            | 144    |

| 7.4   | IMPLI         | CATIONS FOR FUTURE RESEARCH                       | 145    |

| REFER | RENCES        | 5 147                                             |        |

| APPEN | DIX A         | MATLAB CODE                                       | 160    |

| A.1   |               | DDUCTION                                          |        |

| A.2   | MAIN          | PA DESIGN PROGRAM                                 | 160    |

| A.3   | CLASS         | S-E DESIGN SUBROUTINE                             | 162    |

| A.4         | CLASS-F DESIGN SUBROUTINE                              |

|-------------|--------------------------------------------------------|

| A.5         | IMPEDANCE MATCHING                                     |

| A.6         | INDUCTANCE VALUE OVERRIDE                              |

| A.7         | SETUP OF INDUCTANCE SEARCH ALGORITHM PARAMETERS        |

|             |                                                        |

| A.8         | SEARCH FOR REQUIRED INDUCTORS                          |

| A.9         | PA NETLIST EXPORT                                      |

| A.10        | ENTERING PROCESS PARAMETERS 175                        |

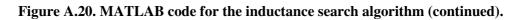

| A.11        | INDUCTANCE SEARCH ALGORITHM 177                        |

| A.12        | EXPORT OF THE SPIRAL INDUCTOR SUBCIRCUIT 178           |

| A.13        | EXPORT OF THE PART OF NETLIST INVOLVING MATCHING       |

| A.14        | CALCULATING PARASITICS OF ANY DESIGNED SPIRAL INDUCTOR |

|             | 179                                                    |

| A.15        | DESIGN OF SPIRAL INDUCTORS AS A MAIN ROUTINE           |

| A.16        | DESIGN OF INDUCTORS WITH KNOWN GEOMETRY 181            |

| A.17        | EXPORT OF THE STAND-ALONE NETLIST OF A SPIRAL INDUCTOR |

|             | 183                                                    |

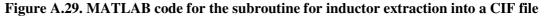

| A.18        | EXTRACTION OF INDUCTOR LAYOUT INTO A CIF FILE          |

| A.19        | EXTRACTION OF INDUCTOR LAYOUT INTO A GDSII FILE186     |

| A.20        | MATCHING AS A MAIN ROUTINE                             |

| APPEN       | DIX B PROCESS FILES FOR EM SIMULATIONS                 |

| <b>B</b> .1 | INTRODUCTION                                           |

| B.2         | PROCESS FILE FOR 3M AMS S35 TECHNOLOGY                 |

| B.3         | PROCESS FILE FOR TM AMS \$35 TECHNOLOGY188             |

| APPEN       | DIX C DESIGN METHOD – BE AT UP (PTY) LTD               |

# CHAPTER 1 INTRODUCTION

#### 1.1 BACKGROUND TO THE RESEARCH

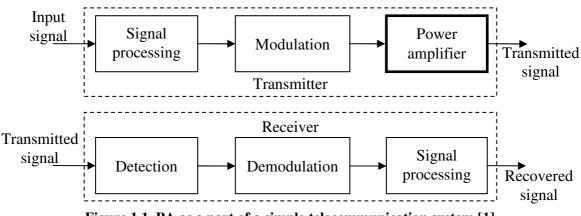

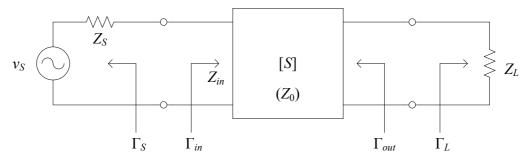

In the recent mobile telecommunication history, a number of wireless modulation schemes have found commercial use. Transmitter devices employing these schemes all demand a power amplifier (PA) for their successful operation. Figure 1.1 shows the PA as a part of a simple telecommunication system [1]. Bulky and high-power off-the-shelf component-based PAs are being replaced by radio-frequency (RF) integrated circuit (RFIC) PAs [2], operating from low-voltage power supplies [3]. This trend is evident in a wide spectrum of analogue and digital applications, starting from short distance (cordless phones, Bluetooth, wireless local area networks (WLANs)), to medium (RF identification (RFID)) and long distance applications (cellular phones, third generation (3G) devices) [4]. The PA remains a bottleneck in the full integration of wireless transceivers, especially if integration is done in pure silicon complementary metal-oxide semiconductor (CMOS) processes. For this reason, most commercial wireless devices use an external PA to drive an antenna. This external device is usually fabricated in technologies superior to the silicon (Si) CMOS, such as gallium-arsenide (GaAs) heterojunction bipolar transistor (HBT) technology [5].

Figure 1.1. PA as a part of a simple telecommunication system [1].

Nevertheless, it is not always possible to separate a PA from the rest of the system, so that designers often have to be satisfied with a simple PA design in a pure CMOS process, or alternatively, a hybrid processes such as silicon-germanium (SiGe) bipolar-CMOS (BiCMOS) process [6].

In many RF modulation schemes, such as the direct sequence spread spectrum (DSSS) technique, it is necessary to design several PAs in order to ensure operation over different channels of the same band. For example, for a system based on DSSS [7], transmission is possible over a number of channels in Industrial, Scientific and Medical (ISM) band; their centre frequencies ranging from 2.4000 GHz to 2.4835 GHz. If a correct design methodology is not employed, designing of all PAs for all channels can be quite time consuming.

Basic PA is designed around one or more active devices, either metal-oxide semiconductor field-effect transistors (MOSFETs), bipolar junction transistors (BJTs) or HBTs. Several PA output stages are commonly used in telecommunications, with Class E and Class F widely used [8].

Irrespective of the output stage, and additional to the active devices, a number of passive components (inductors and capacitors) must be included. At the schematic design level this does not present a problem, because ideal capacitors and inductors can be used for the first design. However, translating of the design onto the layout level (where layout refers to actual drawing of components on a silicon wafer) becomes more intricate. Here, designing of an inductor poses a special problem, because of a great number of inductor options [9].

Even with a proper integrated inductor topology selected, the more affordable electronic design automation (EDA) software packages do not have built-in procedures for integrated inductor netlist extraction, but designers have to rely on inductors, if any, provided in High Performance Interface Tool Kits (HIT-kits). Furthermore, the built-in netlist extractors usually interpret an inductor as simply a long piece of metal or wire (which short-circuits the nodes placed at the two ends of an inductor), thus making the extracted netlists incorrect. Although there are a few models of integrated inductors described in literature [10-12], they are often not used by designers who are either satisfied by simulations at the schematic level or replace actual inductors with ideal inductors in order to proceed with the post-layout simulations. Drawbacks of such an approach might not be apparent at low frequencies, but they become particularly important in the design of PAs at RF, due to the fact that even small differences between actual and designed values of inductance can strongly affect the centre frequency, gain or efficiency of the amplifier. Often, these

mismatches can only be seen after the fabrication of the chip is completed, thus introducing additional unnecessary chip fabrication iterations.

#### **1.2 RESEARCH PROBLEM AND HYPOTHESIS**

In the description in Section 1.1, the following research problem can be identified:

What kind of methodology can be employed to speed up the design of power amplifiers together with their passives (inductors) for a range of wireless applications, at the same time taking care that high quality of amplification is maintained?

To answer the research question, the following hypothesis is formulated:

If the performance of a power amplifier system is related to optimising its subsystems, then implementing a methodology that uses software algorithms to perform the optimization will produce better quality power amplifiers.

To test the hypothesis, various PA and inductor options were investigated and those of Class E, and Class F identified as most commonly used topologies in RF design, because of their predisposition for high efficiencies and high power. Inductors were modelled as monolithic spiral inductors. Equations describing the PA and inductor models were used as a starting point when developing a method that allows that for a given a set of specifications such as PA bandwidth, centre frequency and class of operation, the best possible PA is found and designed. It is speculated, inter alia, that this method can be coined as a software routine. The same routine determines a geometry of a spiral inductor that gives the highest possible Q (quality) factor, using process parameters for a particular process. In parallel with the development of the software routine, a number of PAs were designed in the SiGe S35 (0.35  $\mu$ m BiCMOS) process from Austriamicrosystems (AMS) [13] and simulated in order to verify the correctness of developed algorithms. Finally, the layouts of designed systems were prepared and then sent for fabrication to an auxiliary process from IBM<sup>1</sup> (IBM 7WL) process [14], in order to investigate aspects that cannot be

<sup>&</sup>lt;sup>1</sup> IBM is the short name for International Business Machines.

covered in simulations, such as influence of parasitics, as well as correctness of the quality factor and inductance values of spiral inductors.

#### 1.3 JUSTIFICATION FOR THE RESEARCH

Computer-aided design (CAD) is not uncommon in circuit design. Conceptual design is usually performed in a mathematical package, which can be followed by schematic design in a schematic editor. Performance of the circuit is normally simulated in SPICE<sup>2</sup> [15] based simulators. However, there are often various missing links, and the designer needs to resort to hand design to complete the design cycle. Being a common example of this problem, the design of PAs leaves an opportunity for a software routine to be developed that will aid this task.

#### **1.4 METHODOLOGY**

Various PA concepts were explored in depth to identify a few commonly used simple PA models to be used as a starting point for automating a PA design. A number of PAs based on these models were designed from the first principles in MATLAB from Mathworks [16], and then simulated with the aid of a Cadence Virtuoso circuit design and simulation package from Cadence Design Systems [17]. Knowledge gained from the design and simulation was at the same time used to design a program in MATLAB that automates this design. Layouts for several good circuits were drawn (in Virtuoso Layout Editor which is also a part of Cadence Virtuoso), and then the IC was sent for fabrication in the 180 nm BiCMOS process.

The detailed methodology followed in this thesis is described in Chapter 3.

#### **1.5 DEFINITIONS**

Definitions adopted by researchers are often not uniform; therefore the key and controversial terms have been defined to establish positions taken in PhD research.

As it will be explained in detail in Section 2.2.5, the PAs are grouped in classes, for example *Class A*, *Class E*. etc. If the letter naming the class follows the keyword *Class* without a dash (*Class A*), the keyword-letter combination is used as a noun. If a hyphen is

<sup>&</sup>lt;sup>2</sup> SPICE stands for simulation program with integrated-circuit emphasis.

used, the combination is an adjective (*Class-A amplifier*). The keyword *Class* is capitalized in most cases, in order to point out that it is part of the name of the particular PA.

#### **1.6 DELIMITATIONS OF SCOPE AND KEY ASSUMPTIONS**

Although concepts developed in this thesis can be transferred to a vast number of fabrication technologies, due to the time and financial constraints for obtaining prototypes, the use of only two (SiGe BiCMOS) technologies was possible. Application of the developed methodology to other technologies is proposed, but testing of this idea was only possible from conceptual perspective.

#### **1.7 CONTRIBUTION OF THE RESEARCH**

A new method for the design of the full PA systems has been proposed for the use in the low-gigahertz integrated applications. A detailed list of the resulting contributions to the body of knowledge is given here.

- Inductors have been identified as being traditionally difficult to integrate due to low quality factors and their indeterministic behaviour. Main contribution of this research is engineering of an inductor design process. This inductance search algorithm finds the highest quality factor configuration of a single-layer square spiral inductor within a certain tolerance using formulae for inductance and inductor parasitics of traditional single-π inductor model. This algorithm in effect contributes towards enhancing conventional PA design and is a major improvement over the common trial-and-error methods used by current designers.

- An algorithm for calculating inductance, parasitics and Q-factor of the existing square geometries, has also been developed, so that the feature for the quick analysis of existing inductor structures can be retained.

- This research also shows that in fact, with the correct design methodology, which includes optimisation for operation at correct frequency, quality factors in excess of 10 can be obtained for on-chip inductors without modification to the process or flow of fabrication.

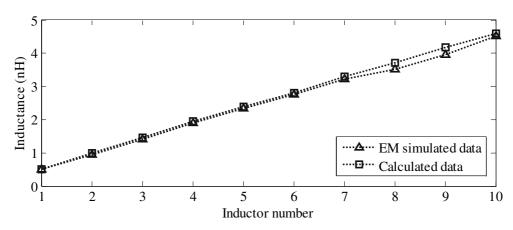

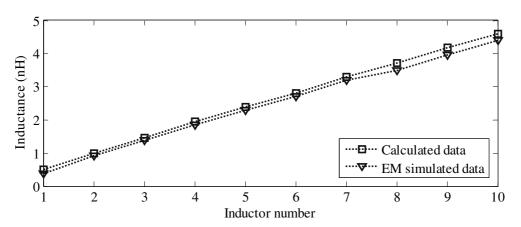

- Several inductors have been designed using the above mentioned algorithm and comparisons made with the experimental results for the AMS S35 process provided by the AMS foundry. Correspondence is established between designed, experimental and EM simulation results. EM simulations enabled qualification of inductors other than those with experimental results available. Average relative errors of 3.7 % for inductance and 21 % for the Q factor at its peak frequency were obtained for both metal-3 and thick-metal inductor options available.

- Although intended for the use with PAs, the spiral inductor design algorithms can contribute in any other application that might require integrated inductors, for example the low-noise amplifiers (LNAs) [18], DC to DC converters [19] or voltage-controlled oscillators (VCOs) [20].

- Further contribution of this research is a set of algorithms for the complete design of the switching-mode (Class-E and Class-F) PAs. These algorithms make use of the classic design equations so that the values of the parasitic components can be calculated given input parameters, including the required output power, centre frequency, supply voltage, and choice of class of operation (Class E or Class F). These design equations are brought forward from the existing body of knowledge and combined into a single routine which makes them easier to handle during the design process.

- In high power and low voltage supply applications, antenna resistances reaching values of less than 10  $\Omega$  would be needed. To overcome this impracticality this thesis provides algorithms that automate impedance matching from optimum to standard antenna impedances (50  $\Omega$ ).

- Simulations showed that, for the complete PA system design, output matching and real (spiral) inductors, switch-mode PAs for 50  $\Omega$  load at 2.4 GHz centre frequency can be designed using the streamlined method of this research for the power output of about 6 dB less than aimed. This power loss was expected, and it can be attributed to non-ideal properties of the driving transistor and Q-factor limitations of the integrated inductors.

- While these results were obtained for only two fabrication processes, it has been found that principles devised in this thesis are technology independent and can be used with a range of CMOS and BiCMOS processes.

- Additional algorithms, such as the one for the SPICE netlist extraction and spiral inductor layout extraction (CIF and GDSII formats), were found extremely beneficial for the completeness of the design flow and integration into a compact EDA tool.

Table 1.1 shows some PA and spiral inductor designs found in literature and their design methods, while focusing on strengths and weaknesses of each employed method. This table also shows where and how the research presented in this thesis extends the existing body of knowledge by overcoming the identified weaknesses.

| Ref  | Impact factor <sup>1</sup> | Торіс                                            | Strengths                                                                                                                                                                                                                             | Weaknesses                                                                                                                                                                                                                                                                                                                    |

|------|----------------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [21] | 2.043                      | Class-E PA<br>design                             | <ul> <li>Single ended Class-E PA design is performed while taking the advantages of the BiCMOS process over inferior CMOS processes.</li> <li>Design is optimised for high efficiency.</li> </ul>                                     | <ul> <li>Simulation-driven cut-and-try approach for the PA design is used.</li> <li>Although the bond wire used for the resonant tank of the PA exhibits high Q-factor, such an approach cannot be extended to wider set of applications since the range of inductance values obtainable by bond wires is limited.</li> </ul> |

| [22] | 2.043                      | Two-stage<br>Class-E design<br>optimization tool | <ul> <li>Template-driven simulation-based<br/>methodology coined as software tool<br/>is presented.</li> <li>The effects of parasitics for both<br/>active (transistors) and passive<br/>devices (inductors) are included.</li> </ul> | • The tool seems to be too detailed for<br>the goal that it accomplishes: the<br>design of only one topology, viz. two-<br>stage Class-E PA.                                                                                                                                                                                  |

| [23] | 2.043                      | Class-E PA in<br>65 nm CMOS                      | <ul><li>The design employs a differential topology.</li><li>Finite DC feed inductance reduces high-voltage stress.</li></ul>                                                                                                          | <ul> <li>No design methodology for inductors<br/>is presented.</li> <li>Although available switch-mode<br/>topologies are well researched, a<br/>repeatable design method is not<br/>speculated.</li> </ul>                                                                                                                   |

| [24] | 1.140                      | Class-F PA for<br>low-voltage<br>supplies        | <ul> <li>Class-F PA utilizes a simple single-<br/>ended topology with input and output<br/>harmonic terminations.</li> <li>High gain and high efficiency are<br/>accomplished.</li> </ul>                                             | <ul> <li>No design methodology for inductors presented</li> <li>A repeatable PA design method is not speculated.</li> </ul>                                                                                                                                                                                                   |

| [25] | 1.436                      | Optimizing the design of spiral inductors        | <ul> <li>Analysis of the spiral inductor model<br/>leads to inductor width that<br/>maximises the Q-factor.</li> <li>It is identified that the width is<br/>dependent on the spiral length</li> </ul>                                 | • Spiral length depends on input and output diameters making optimisation method impractical.                                                                                                                                                                                                                                 |

# Table 1.1. Comparison of the PA design methods found in literature with the one proposed in this thesis.

<sup>1</sup> ISI Web of Knowledge - Journal Citation Reports (Published by Thomson Reuters)

Chapter 1

#### Table 1.1 (Continued). Comparison of the PA design methods found in literature with the one

#### proposed in this thesis.

| Ref          | Impact factor | Торіс                                                                            | Strengths                                                                                                                                                                                                                                                                                                                         | Weaknesses                                                                                                                                         |

|--------------|---------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| [26]         | 2.730         | Analysis and<br>synthesis of<br>spiral inductors                                 | <ul> <li>Advanced inductor modelling.</li> <li>Full web-based inductor tool<br/>employs a search algorithm to<br/>synthesize inductors.</li> <li>Both synthesis and analysis are<br/>performed.</li> </ul>                                                                                                                        | • Although designs have been<br>optimised for different parameters,<br>little discussion pertaining Q-factors<br>has been carried out.             |

| [27]         | 2.730         | Inductor layout<br>design<br>optimisation                                        | • The method looks into the effects of core diameter, turn spacing and turn width on the overall performance of inductors.                                                                                                                                                                                                        | • Multiple fabrication runs and wafer testing are necessary to optimise inductor designs.                                                          |

| [28]         | 2.730         | Enhancement of<br>the inductor Q-<br>factor with low<br>temperature<br>annealing | • Although the substrate resistance is decreased which also decreases the Q-factor of the inductor, resistance of the spiral is decreased, resulting in overall inductor Q-factor increase.                                                                                                                                       | • Substrate resistance decrease apart<br>from decreasing inductor Q-factor,<br>could be influential on other<br>components of a PA.                |

| [29]         | 2.302         | Q-factor<br>improvement by<br>means of deep-<br>trench-mesh<br>substrate         | <ul> <li>Decreased capacitive coupling and<br/>resistive losses lead to Q-factor<br/>improvements up to 28 % in 0.35 μm<br/>BiCMOS process.</li> </ul>                                                                                                                                                                            | <ul> <li>Cut-and-try method is used to optimise inductor designs.</li> <li>Deep-trench-mesh might not be available in all technologies.</li> </ul> |

| This<br>work | -             | Design<br>methodology for<br>switch-mode PA<br>design                            | <ul> <li>Fully streamlined PA design method<br/>is presented for two-most common<br/>high-power high-frequency stages<br/>(Class F, Class E).</li> <li>Matching and inductor design are<br/>presented.</li> <li>Theory is fully backed up by means<br/>of simulations and experimental<br/>results (where applicable).</li> </ul> | • The method only includes the design of the output stage.                                                                                         |

| This<br>work | -             | Optimisation of<br>Q-factors of<br>spiral inductors<br>for square<br>geometries  | <ul> <li>All geometry parameters are taken<br/>into consideration and total geometry<br/>search is performed.</li> <li>Search is governed by inductance and<br/>Q-factor.</li> <li>Technology independent.</li> <li>Simulation/model oriented (no<br/>fabrication is needed for test runs).</li> </ul>                            | • No post-processing has been attempted.                                                                                                           |

Chapter 1

#### **1.8 PUBLICATIONS LEADING FROM THIS RESEARCH**

The following journal articles have been published as part of research activities of the author:

- Božanić, M., Sinha, S., and Müller, A., 2010. Streamlined Design of SiGe Based Power Amplifiers. *Romanian Journal of Information Science and Technology* (*RJIST*), Vol. 13, No. 1, pp. 22-32.

- Božanić, M. and Sinha, S., 2009. Design Approach to CMOS Based Class-E and Class-F Power Amplifier. SAIEE Africa Research Journal, Vol. 100, No. 3, pp. 79-86.

- Božanić, M. and Sinha, S., 2008. Software Aided Design of a CMOS Based Power Amplifier Deploying a Passive Inductor. *SAIEE Africa Research Journal*, Vol. 99, No. 1, pp. 18-24.

The following peer-reviewed international conference articles have been published and presented by the author:

- Božanić, M, Sinha, S., Müller, A. and du Plessis, M., 2009. Design Flow for A SiGe BiCMOS Based Power Amplifier, *Proceedings: IEEE International Semiconductor Conference (CAS) 2009*, 12-14 October, Sinaia, pp. 311-314.

- Božanić M. and Sinha, S., 2009. Design Flow for CMOS Based Class-E and Class-F Power Amplifiers, *Proceedings: IEEE AFRICON 2009*, 23-26 September, Nairobi, pp. 1-6.

- Božanić M. and Sinha, S., 2009. Design methodology for SiGe-based Class E power amplifier, *Proceedings: South African Conference on Semi and Superconductor Technology (SACSST)*, 8-9 April, Stellenbosch, pp. 31-36.

- Božanić, M. and Sinha, S., 2007. Design methodology for a CMOS based power amplifier deploying a passive inductor, *Proceedings: IEEE AFRICON 2007*, 26-28 September, Windhoek, pp. 1-7.

The following article was submitted to an ISI-listed peer-reviewed journal:

• Božanić, M. and Sinha, S., 2011. Switch-Mode Power Amplifier Design Method, submitted for publication in *Microwave and Optical Technology Letters*.

Program developed during the course of this research has also been commercialized (Appendix C).

#### **1.9 OUTLINE OF THIS THESIS**

Chapter 1 includes introduction to the thesis and a brief background for the research. The research question and hypothesis are clearly stated and justification for the research and its contributions are provided.

Chapter 2 provides the review of body of knowledge related to the context of this research. A brief discussion on PAs is given, followed by the more detailed discussion on the Class-A, Class-B, Class-C, Class-E and Class-F amplifiers, as well as on some hybrid classes. This is followed by a detailed discussion on inductors for PA applications, with special attention paid to the spiral inductor, its modelling, and techniques for increased quality factor integrated inductor design. Subsequently, some fabrication processes have been discussed in brief, with a more detailed discussion on the SiGe BiCMOS process and its relation to the silicon CMOS and GaAs HBT processes. The chapter concludes with the discussion on the importance of the rapid PA design.

Chapter 3 describes the methodology applied for the successful completion of the research presented in this thesis. It includes the research methodology outline, details on the software packages and design suites used for both research and development, background to the design process as well as description of the HBT SPICE model.

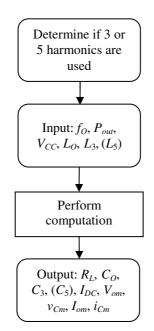

Chapter 4 describes concepts behind the MATLAB-routine based method for a rapid PA design. Flow diagrams of algorithms for the design of the Class-E and Class-F output stages, spiral inductor design, output impedance matching, as well as the flow diagram of the routine for the full PA system design are given here. For the complete program listings, the reader is referred to Appendix A. For the commercial version of the program, the reader is referred to Appendix C.

Chapter 5 describes the circuit level design and simulation of various PA systems used for testing of the first (MATLAB) version of the PA design routine. Circuit diagrams and simulation test benches and results constitute the bulk of this chapter. Inductor model and

inductance search algorithm are verified by means of EM simulations, as well as by comparison to the measured results. The streamlined use of the complete PA design routine is demonstrated by designing one Class-E and one Class-F output stage complete with input and output matching as well as biasing with minimum optimisation effort. For the technology files needed for completion of EM simulations, the reader is referred to Appendix B.

Chapter 6 presents layouts and photographs of the PA circuits submitted for fabrication as well the experimental results. The packaging and circuit board design issues are also discussed.

Chapter 7 concludes this thesis and gives suggestions for future research.

#### **1.10 CONCLUSION**

Chapter 1 laid the core foundations for this thesis. The research problem, viz. the need for a method to perform the tedious design of PAs and spiral inductors, has been formulated as a hypothesis, followed by the introduction to the research background. Solution to the research problem was proposed in the form of set of algorithms (initially developed in MATLAB) that will cover many aspects of a switch-mode PA design. Algorithms will additionally be able to handle modelling and design of the most important component of a PA – the passive inductor.

This chapter also briefly dealt with justification for the research and methodology used to carry out the research as well its contributions and research outputs to date. Finally, the outline of the thesis has been given. Chapter 2 follows with the review of literature.

# **CHAPTER 2 LITERATURE REVIEW**

#### 2.1 INTRODUCTION

Chapter 1 dealt with the introduction to the research performed in this thesis. In this chapter, a literature review is presented to place this into context of available knowledge. A few key concepts seminal to this study are identified and presented. Firstly, basic concepts of power amplification are listed, including some examples of good PA designs from the second part of the first decade of the twenty-first century. Secondly, a very important component of any PA, the inductor, is explored in depth, because a large number of different implementations and models available in literature make identifying a suitable inductor a time-consuming task. Thirdly, available fabrication technologies are investigated because understanding of the technology available for testing forms the foundation of this study. The fourth section of this review deals with the gap in knowledge when it comes to automating the task of rapid PA and passive inductor design. Finally, the conclusion of the chapter is drawn.

#### 2.2 POWER AMPLIFICATION

PAs are used on the transmit side of RF circuit, typically to drive antennas with high power [8]. In such a scenario, the scaled-up versions of small-signal amplifiers used in the low-power low-frequency CMOS circuits are fundamentally incapable of high frequency, and other approaches must be considered [30]. In the monolithic PA implementations, the trade-off between efficiency and linearity is very significant [8]. In addition to these two determining factors for the PA integration, some other challenges, such as the limited supply voltage and heat generation, are also present. These factors often lead to the discrete PA designs or integration separate from the rest of the front end of the RF circuit.

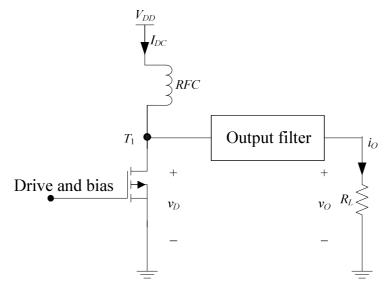

Figure 2.1 shows a general single-ended PA model [31]. In this model,  $V_{DD}$  is the voltage supply,  $R_L$  is the load and *RFC* is the RF choke, and inductor is large enough to ensure the substantially constant current through the drain. In some designs, this inductor can be replaced by a finite one, if it forms a part of the output filter, also shown in this figure [32]. The output filter can include harmonic tuning and wave shaping, impedance matching or any other passive circuitry. The transistor  $T_1$  is shown as an n-channel MOS (NMOS)

Chapter 2

transistor, but it can be any power transistor (HBT, MOS, BJT or other) used in a particular PA application.

Figure 2.1. General model of PA [31].

#### 2.2.1 Power capability

The task of a PA is to deliver a given power into the load [1]. This power is determined by the power supply voltage and the load. Maximum power that can be delivered is

$$P = \frac{V_{DD}^{2}}{2R_{L}}$$

(2.1)

In case of Class-E and Class-F PAs, somewhat larger power can be delivered to the load. This will be detailed in Chapter 4.

#### 2.2.2 Power consumption

Total DC power consumption is an important quantity in PA design, especially for battery powered portable devices. DC input power of a PA is the current drawn from the voltage supply over a period of time, or

$$P_{dc} = \frac{1}{T} \int_0^T V_{DD} i_D dt = \frac{V_{DD}}{T} \int_0^T i_D dt = V_{DD} I_{DC}, \qquad (2.2)$$

where  $i_D$  is the drain current and  $I_{DC}$  is the DC component of the current waveform.

#### 2.2.3 Power efficiency

Efficiency is a measure of performance of a PA. The performance of a PA will be better if efficiency is higher, irrespective of its definition. There are several definitions of efficiency commonly used with the PAs [8, 30, 31]. Drain (or collector) efficiency  $\eta$  is defined as the ratio of RF output power ( $P_{out}$ ) to DC input power ( $P_{dc}$ ), or

$$\eta = \frac{P_{out}}{P_{dc}} \tag{2.3}$$

Assuming sinusoidal voltage and current, the RF output power is given by

$$P_{out} = v_{eff} i_{eff} = \frac{i_1 v_1}{2} = \frac{i_1^2 R_L}{2}, \qquad (2.4)$$

where  $i_{eff}$  and  $v_{eff}$  are effective and  $i_1$  and  $v_1$  are the peak fundamental components of current and voltage respectively, and the DC input power is given by Equation (2.2).

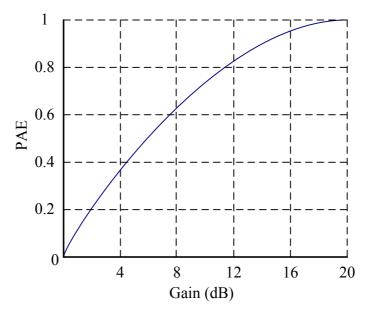

Power added efficiency (PAE) takes into account the input power ( $P_{in}$ ) by subtracting it from the output power:

$$PAE = \frac{P_{out} - P_{in}}{P_{dc}} = \frac{P_{out} - \frac{P_{out}}{G}}{P_{dc}} = \eta \left(1 - \frac{1}{G}\right),$$

(2.5)

where  $G = P_{out}/P_{in}$  is the gain of the PA. The PAE will give a good indication of the performance of a PA for high amplifier gains but it can even become negative for low gains. This relationship is shown in Figure 2.2.

The third type of efficiency is overall efficiency, the ratio of output power to the sum of input power and DC input power:

$$OE = \frac{P_{out}}{P_{dc} + P_{in}}$$

(2.6)

Figure 2.2. Normalized PAE versus the PA gain [1].

The above efficiencies are instantaneous quantities. The instantaneous efficiency is highest at the peak output power. Instead of instantaneous efficiencies, average efficiency can be used for the signals with time varying amplitudes:

$$\eta_{AVG} = \frac{\overline{P}_{out}}{\overline{P}_{dc}},\tag{2.7}$$

where  $\overline{P}_{out}$  is average output power and  $\overline{P}_{dc}$  is average DC input power.

#### 2.2.4 Matching for desired power

The maximum power transfer theorem, commonly used in RF electronics for optimal power transfer by means of conjugate matching, can only be used at the input side of a PA [1, 30], but it does not apply at the output side. At the input side, the PA has to be designed so that correct current and voltage waveforms are delivered at the gate or base of the transistor (biasing). At the output side load has to be correctly chosen. From Equation (2.1), it is obvious that the only two parameters influencing the output power are the voltage supply,  $V_{DD}$  or  $V_{CC}$  and the load impedance,  $R_L$ . The supply is normally fixed for a given application, so that the only degree of freedom left to the designer is the impedance of the load. Looking for correct impedance for maximum power output is called load pull. This impedance will often differ from standard impedances of 50 or 75  $\Omega$ .

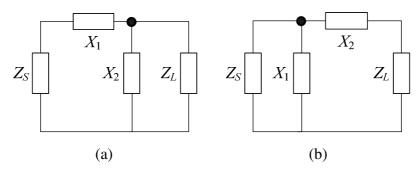

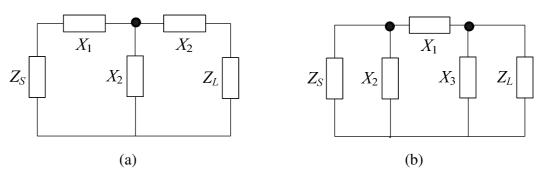

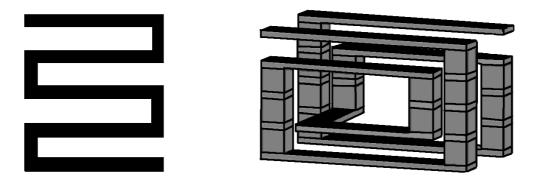

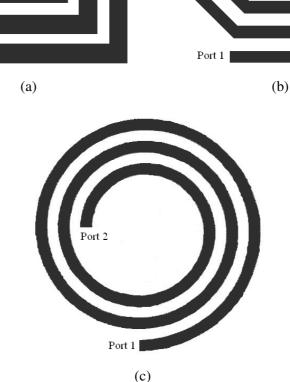

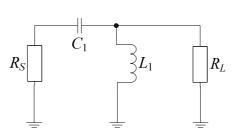

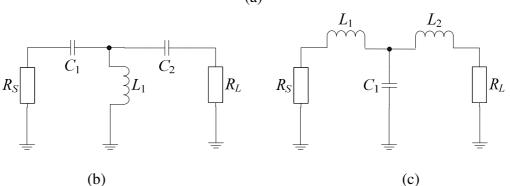

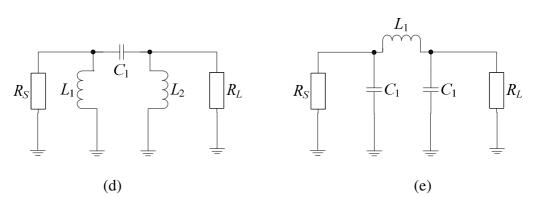

Impedance matching networks are used to convert standard impedances to required impedances. At microwave frequencies, where wavelengths are correspondingly small, this matching can be accomplished with microstrip lines [33]. At low gigahertz frequencies, the microstrip lines are impractically long to be used on a chip, so that impedance matching using discrete components is employed. The two-component networks (L networks) and three-component networks (T and  $\Pi$  networks) are commonly used. Eight L-network configurations are possible, as shown in Figure 2.3 (a) and (b), where  $X_1$  and  $X_2$  can be any combination of inductors and capacitors,  $Z_S$  is the source impedance and  $Z_L$  is the load impedance. Such an L network is a broadband (high-pass or low-pass) network. Conversely, the T and  $\Pi$  networks with passives  $X_1$ ,  $X_2$  and  $X_3$ , shown in Figure 2.4 (a) and (b), are narrowband networks.

Figure 2.3. Two-component matching networks where passive component is parallel to (a) load and (b) source [33].

Figure 2.4. Three component matching networks: (a) T network and (b) Π network [33].

#### 2.2.5 Classification of PAs

PAs can be divided into several categories. They are commonly grouped into broadband and narrowband amplifiers. Alternatively, they can be grouped depending on whether they are intended for the linear or constant envelope operation [30]. However, the most common grouping of PAs is grouping into classes according to the nature of their voltage and current waveforms. The variety of PA classes reflects the inability of any single circuit to satisfy stringent requirements for linearity, power gain, output power and efficiency. Each class is designated with a letter or a combination of letters of the alphabet. The following classes are commonly used for different applications: A, B, AB, C, D, DE, E, F, FE, G, H and S [1, 8, 34]. Inverse classes, where the shape of voltage and current waveforms across the power transistors are inverted, are also possible. Common examples are inverse Class-C ( $C^{-1}$ ) and inverse Class-F ( $F^{-1}$ ) amplifiers [35]. Most of the real-life PAs are operating with current and voltage waveforms that lie between two different classes.

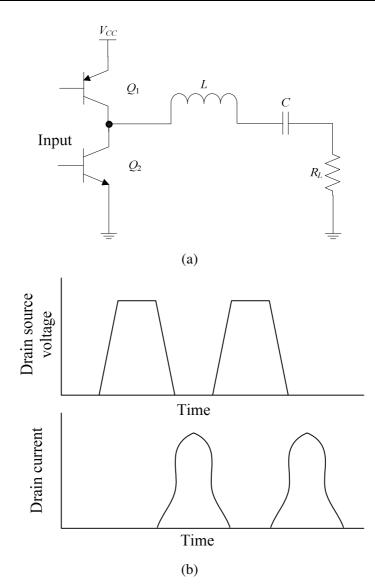

Not all of the classes are suitable for use at RF. For example, Class-D amplifiers are the switching-mode PAs generally used in low-frequency applications [36]. One such PA and its waveforms is shown in Figure 2.5 [37]. Ideally, only one of the two transistors in this figure is switched at a time and efficiency is 100% [31]. However, the use of this PA at high frequencies is limited due to prominent parasitic reactances that lead to substantial losses. This high-frequency performance degradation is less severe in current-mode Class-D implementations [36]. Class-S amplifiers are similar to those of Class D, but their input is driven with pulse-width modulated (PWM) waveform. This class needs transistors  $Q_1$  and  $Q_2$  to be switched with frequencies much higher than the signal frequency, thus making them impractical in RF range [1]. Class-G and Class-H amplifiers are also commonly used for audio applications, with some limited use in digital telephony and for code divison multiple access (CDMA) at low megahertz frequencies.

Traditionally, power amplification at RF was done with amplifier classes A through C, often termed classic amplifiers [8]. Class-E and Class-F amplifiers are considered modern amplifiers since they can be used in many hi-end applications. Because of their importance, all these amplifiers will be presented in separate sections.

Figure 2.5. General Class-D amplifier: (a) circuit, (b) voltage and current waveforms.

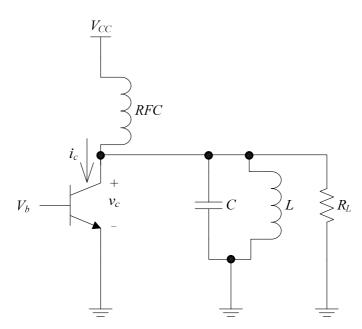

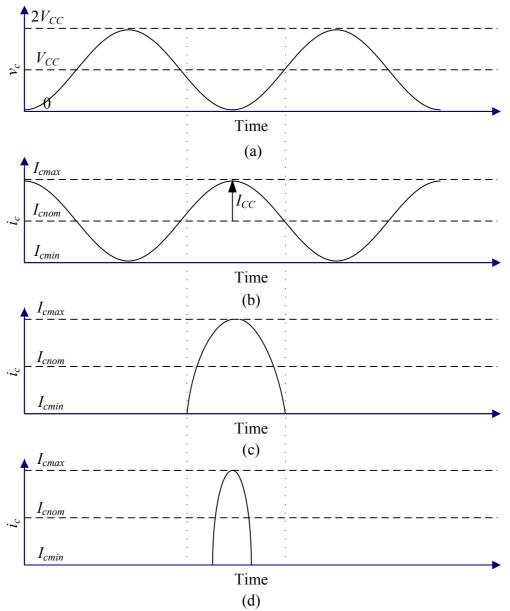

#### 2.2.5.1 Classes A through C

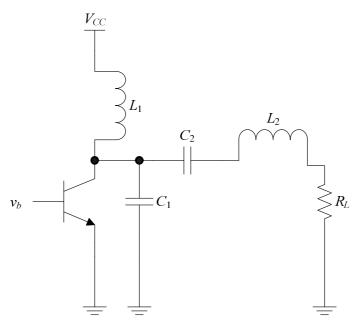

Class-A, B, AB and C amplifiers, or classic amplifiers, are usually analyzed together because of the minimal differences in their waveforms. Figure 2.6 shows a circuit operating as either Class-A, Class-AB, Class-B or Class-C amplifier [8]. Depending on the biasing, the fraction of the cycle during which the current through the PA is flowing (defined as conduction angle or  $2\theta$ ) is different resulting in different class operation, as analyzed in Table 2.1, with efficiency to be explained later in this section. The voltage ( $v_c$ ) and current ( $i_c$ ) waveforms marked in Figure 2.6 are shown in Figure 2.7 for each class. In this figure, current  $i_c$  is sinusoidal waveform in all cases, with its bottom part cut off by biasing ( $V_b$ ) for classes B and C. The waveform for the Class-AB amplifier, shaped between the Class-A and B waveforms, is not shown in this figure.

Figure 2.6. Circuit schematic of a single ended Class-A, AB, B or C PA used for theoretical analysis [8].

Table 2.1. Comparison of conduction angles and efficiencies for Class-A through C PAs [1].

| Class | Conduction angle (°) | Maximum theoretical | Normalized output |

|-------|----------------------|---------------------|-------------------|

|       | conduction angle ()  | efficiency (%)      | power             |

| А     | 360                  | 50                  | 1                 |

| AB    | 360 - 180            | 50 - 78.5           | 1                 |

| В     | 180                  | 78.5                | 1                 |

| С     | 180 - 0              | 78.5 - 100          | 1 – 0             |

Classic PAs can be analyzed for efficiency as follows [1]. The DC component of the current,  $I_{DC}$ , can be derived as

$$I_{DC} = \frac{I_{CC}}{\pi} (\sin \theta - \theta \cos \theta), \qquad (2.8)$$

where  $\theta$  is a half of the conduction angle and  $I_{CC}$  is the peak of the current waveform across the transistor if it was operating in the Class-A mode (Figure 2.7 (b)). Power from the power supply is given by

$$P_{dc} = V_{CC} I_{DC} = \frac{V_{CC} I_{CC}}{\pi} (\sin \theta - \theta \cos \theta)$$

(2.9)

Fundamental current  $i_1$  is derived as

$$i_1 = \frac{I_{CC}}{2\pi} \left( 2\theta - \sin 2\theta \right) \tag{2.10}$$

Figure 2.7. Voltage and current waveforms for classic amplifiers: (a) voltage for classes A, B and C, (b) current for Class A, (b) current for Class B and (c) current for Class C [8].

Output power is

$$P_{out} = \frac{v_{peak} i_{peak}}{2} \tag{2.11}$$

Maximum power will be reached if  $v_{peak} = V_{CC}$ . Hence (assuming  $V_{CEsat} = 0$ ),

$$P_{out,\max} = \frac{V_{CC}i_{peak}}{2} = \frac{V_{CC}I_{CC}}{4\pi} (2\theta - \sin 2\theta)$$

(2.12)

The maximum possible efficiency is then

$$\eta = \frac{P_{out,\max}}{P_{DC}} = \frac{2\theta - \sin 2\theta}{4(\sin \theta - \theta \cos 2\theta)}$$

(2.13)

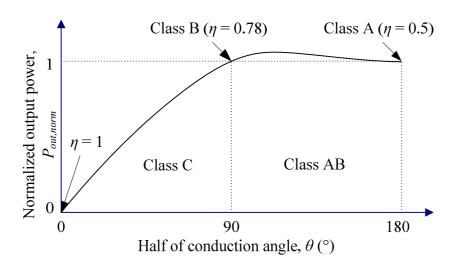

Figure 2.8 shows the plot of maximum normalized output power versus  $\theta$ . Maximum possible efficiencies and regions of operation are also marked on the figure. From this figure, it is clear that maximum efficiency of 100% can be obtained with the Class-C operation, but with zero output power, which makes such configuration impractical. Usually, the compromise between efficiency and output power is considered optimum design solution, resulting in  $\theta$  lying in 30 to 60 degrees range. It should be noted that linearity of this amplifier is highest with the Class-A operation, while it decreases for the Class-AB, B and C operation. The passives *C* and *L* in Figure 2.6 are not explicitly defined by the PA formulae as in the case of the Class-E amplifiers described in Section 2.2.5.2, but they must be chosen for the amplifier to operate at correct resonant frequency given by

$$f_o = \frac{1}{2\pi\sqrt{LC}},\tag{2.14}$$

with acceptable Q-factor

$$Q = \frac{2\pi fL}{R_L} \tag{2.15}$$

Efficiencies for monolithic Class-A through C PAs are much lower than ideal values due to a number of factors: low quality factor of inductors, saturation voltage in the transistors, tuning errors and temperature variations. Because high efficiencies are possible only at low conduction angles which are difficult in ICs, fully integrated classic PAs are rare, but not impossible. One example is a Class-AB amplifier for Bluetooth applications [38].

#### 2.2.5.2 Class E

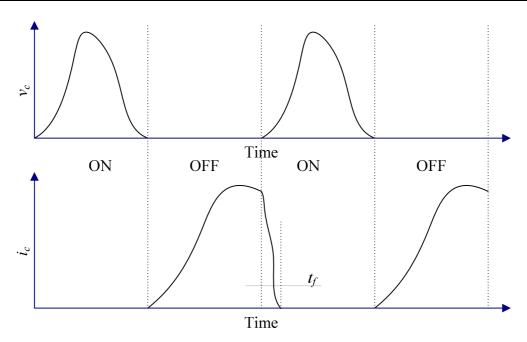

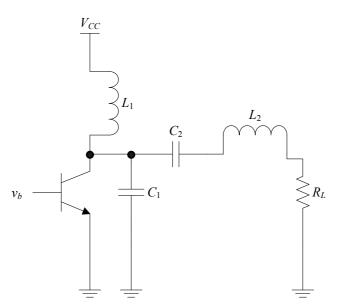

Class-E amplifiers were proposed by Sokal and Sokal in 1975 [39] and together with the Class F amplifiers [40] have been used in communication ever since. They are classified as switching amplifiers and as such they can exhibit efficiencies close to 100%. A single ended Class-E PA is shown in Figure 2.9 [37]. A simple PA analysis can be performed if the following is assumed:

Figure 2.8. Maximum normalized output power versus half of conduction angle for the classic PAs [1].

- Inductance of the RF choke  $(L_1)$  is very high;

- Output capacitance of the transistor is independent of the switching voltage;

- Transistor is an ideal switch with zero resistance and zero switching time, open for half of the signal period.

From [39], the value of the optimum load resistance to deliver the highest power to the load with  $v_{peak} = V_{CC}$  and non-zero  $V_{CEsat}$  is

$$R_{L} = \frac{2}{\frac{\pi^{2}}{4} + 1} \frac{\left(V_{CC} - V_{CEsat}\right)^{2}}{P} = 0.577 \frac{\left(V_{CC} - V_{CEsat}\right)^{2}}{P}$$

(2.16)

For desired Q-factor of the output resonant tank, inductance  $L_2$  can be calculated:

$$L_2 = \frac{Q_L R_L}{2\pi f} \tag{2.17}$$

Shunt capacitance  $C_1$  is given by

$$C_{1} = \frac{1}{2\pi f R_{L} \left(\frac{\pi^{2}}{4} + 1\right) \left(\frac{\pi}{2}\right)} = \frac{1}{5.447(2\pi f R_{L})}$$

(2.18)

and resonant capacitance  $C_2$  is given by

Chapter 2

Figure 2.9. Circuit diagram of a single ended Class-E PA used for theoretical analysis [37].

$$C_{2} = \frac{1}{(2\pi f)^{2} L_{2}} \cdot \left(1 + \frac{1.42}{Q_{L} - 2.08}\right) = C_{1} \left(\frac{5.447}{Q_{L}}\right) \cdot \left(1 + \frac{1.42}{Q_{L} - 2.08}\right)$$

(2.19)

Capacitance  $C_1$  includes parasitic capacitances of the transistor.

Efficiency of Class E is

$$\eta = \frac{1 - \frac{(2\pi A)^2}{6} - \frac{V_{CEsat}}{V_{CC}} \left[ 1 + A - \frac{(2\pi A)^2}{6} \right]}{1 - \frac{(2\pi A)^2}{12}},$$

(2.20)

where

$$A = \left(1 + \frac{0.82}{Q_L}\right) ft_f \tag{2.21}$$

and  $t_f$  is the collector current fall time. For the ideal PA  $t_f$  and  $V_{CEsat}$  are zero, and efficiency is 100%. This efficiency is obtained at 78.5% of the Class-AB output power [1]. Practical waveforms for this topology with transistor turned on and off are shown in Figure 2.10.

Figure 2.10. Voltage and current waveforms for the Class-E amplifiers when transistor is ON and OFF [39].

Although the Class-E amplifiers have output powers typically a few dB less than their Class-AB counterparts, they are used because of their high efficiency and swing that is more than three times the supply voltage. A recent example of the Class-E amplifier design can be found in [41].

## **2.2.5.3** Class F and $F^{-1}$

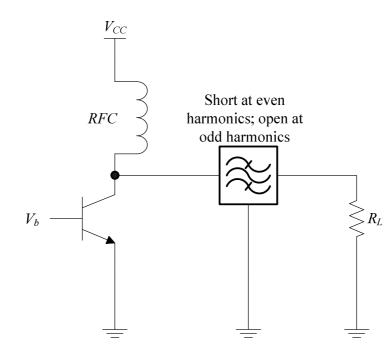

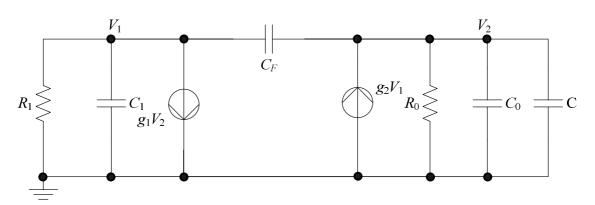

The Class-F amplifier is similar to that of the Class E in a sense that it can also result in 100% efficiency. However, at the same time, the output power can be similar to that of the Class-AB amplifiers [42]. This efficiency and power boost is a result of the presence of harmonic resonators in the output networks that shape drain (collector) waveforms in such a way that load appears to be short at even harmonics and open at odd harmonics, as shown in the general model in Figure 2.11. As a result, the ideal collector voltage waveform approximates a square wave, while collector current waveform approximates a half-sine wave. There is no overlap between the two waveforms. In case of the Class-F<sup>-1</sup> amplifier resonators are swapped around, and the collector voltage is shaped as a half-sinusoid and collector current is shaped as a square wave.

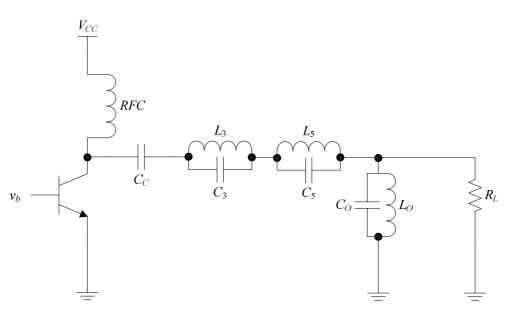

Figure 2.11. General Class-F amplifier model [42].

Shaping of waveforms can be done by means of transmission lines, as the case is with the Class-F amplifier with the quarter-wave transmission line. However, this is not a practical implementation for the low-gigahertz integration. Instead, passive resonators are used. Monolithic implementations of the Class-F amplifiers would require an infinite number of resonators to correctly shape output waveforms. Figure 2.12 shows efficiencies that can be obtained with increasing number of harmonic traps [43]. If only first harmonic trap is implemented, amplifier behaves as a Class-A amplifier, with maximum efficiency of 50%.

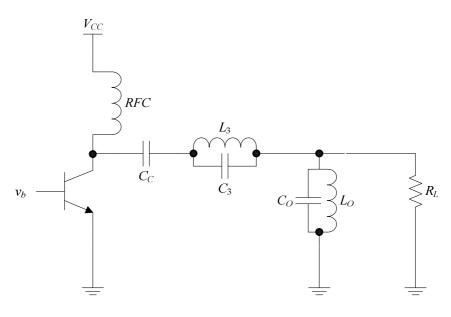

Most real life integrated Class-F amplifier implementations consider only a few harmonics, usually two or three. Figure 2.13 shows the third harmonic peaking circuit [42]. In this circuit, the tank at  $3f_o$  provides an open circuit at  $3f_o$  and short circuit at  $2f_o$ . A resonant tank at  $f_o$  ensures optimum load at  $f_o$ .

If fundamental frequency components of voltage and current are  $V_{om}$  and  $I_{om}$ , waveform factors that relate them to the fundamental frequency components  $V_{CC}$  and  $I_{DC}$  can be defined as [42]

$$V_{om} = \gamma_V V_{CC} \tag{2.22}$$

and

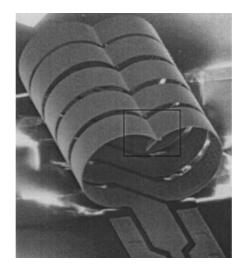

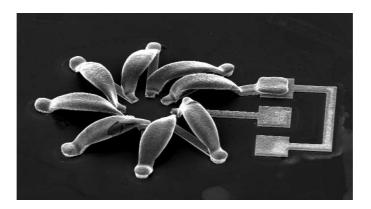

Number of resonators

4

5

$\infty$

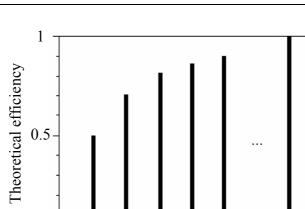

Figure 2.12. Efficiency of a Class-F amplifier versus a number of resonators [43].

3

2

1

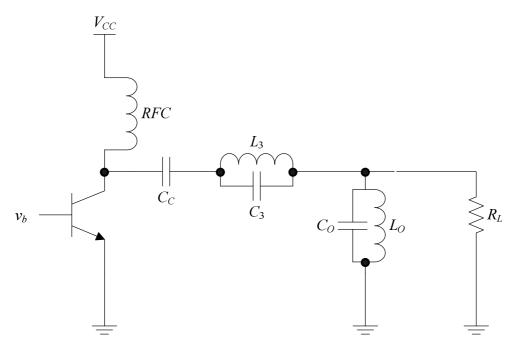

Figure 2.13. Class-F third harmonic peaking circuit [43].

$$I_{om} = \gamma_I I_{DC}, \qquad (2.23)$$

whilst the efficiency of a Class-F circuit is

0

$$\eta = \frac{\gamma_v \gamma_I}{2} \tag{2.24}$$

For the third harmonic peaking circuit,  $\gamma_V$  and  $\gamma_I$  are calculated in [43] for the highest possible efficiency as 1.1574 and 1.4142 respectively, resulting in an efficiency of  $\eta = 81.65\%$ .

As it is the case with other classes, the Class-F amplifiers also exhibit efficiencies lower than predicted, mostly because of the presence of a large number of resonant circuits that suffer a loss because of the low Q-factors possible for on-chip inductors. A recent monolithic Class-AB/Class-F implementation in the InGaP/GaAs HBT process can be found in [44].

## 2.2.6 Techniques for performance improvement of PAs

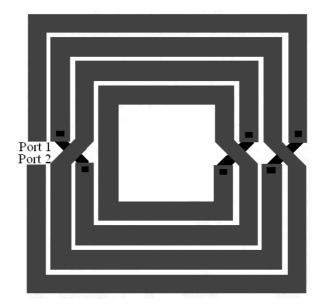

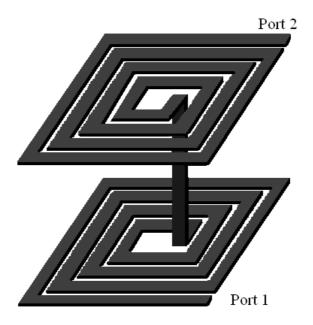

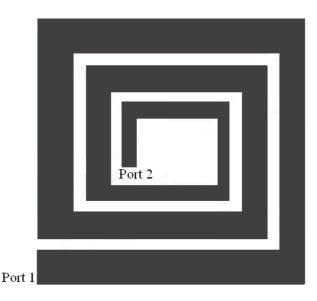

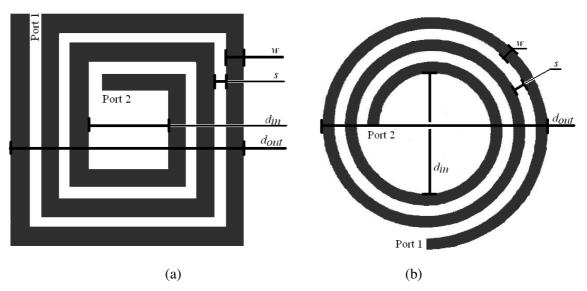

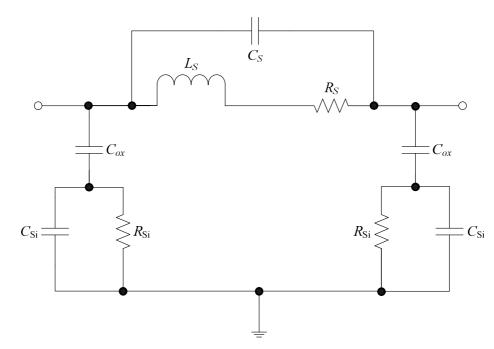

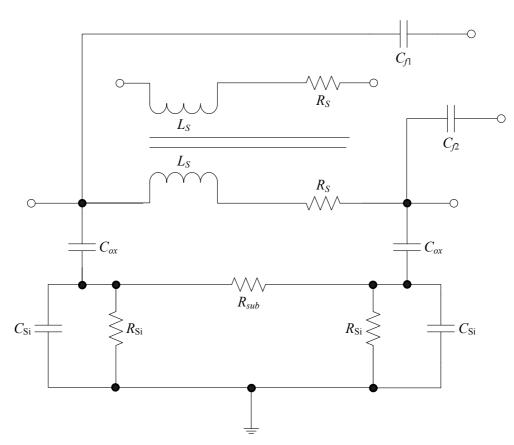

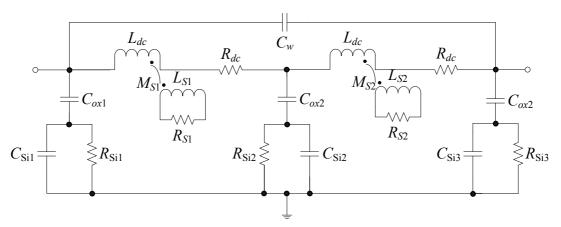

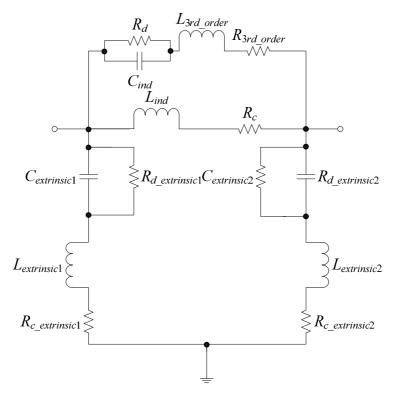

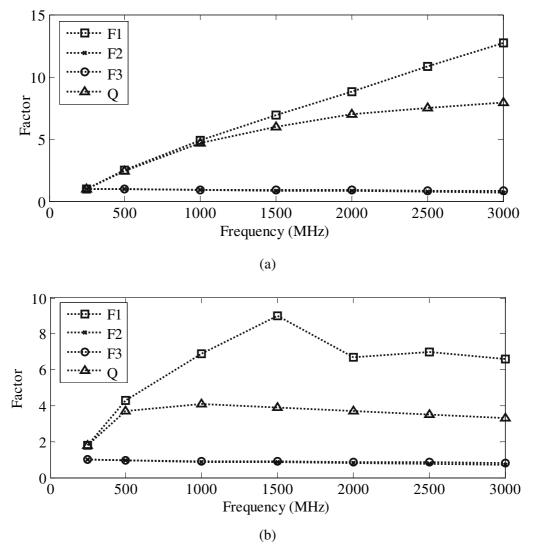

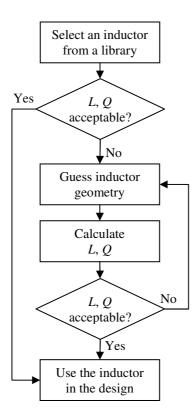

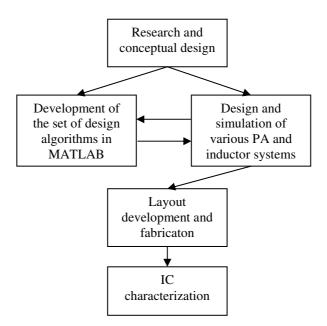

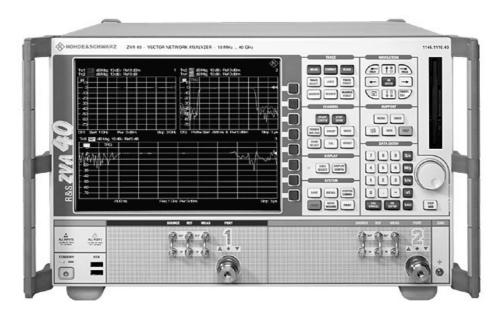

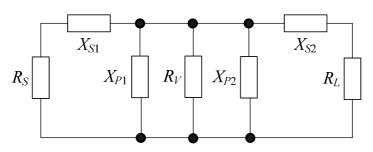

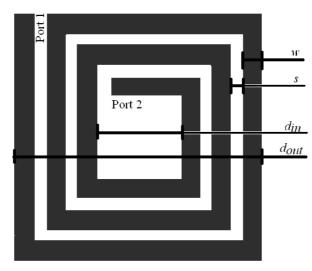

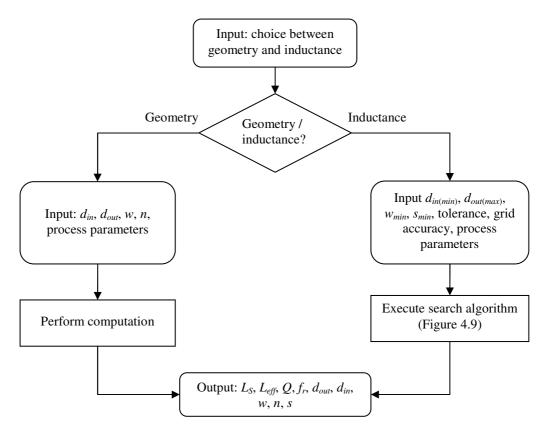

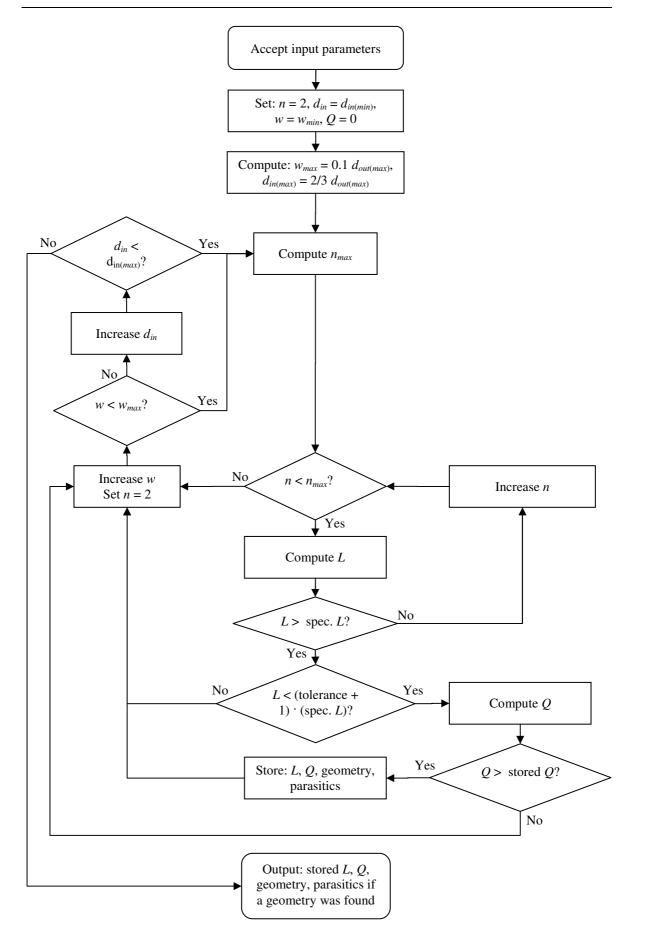

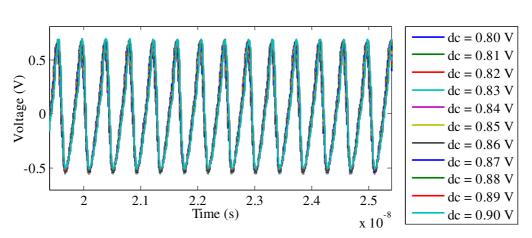

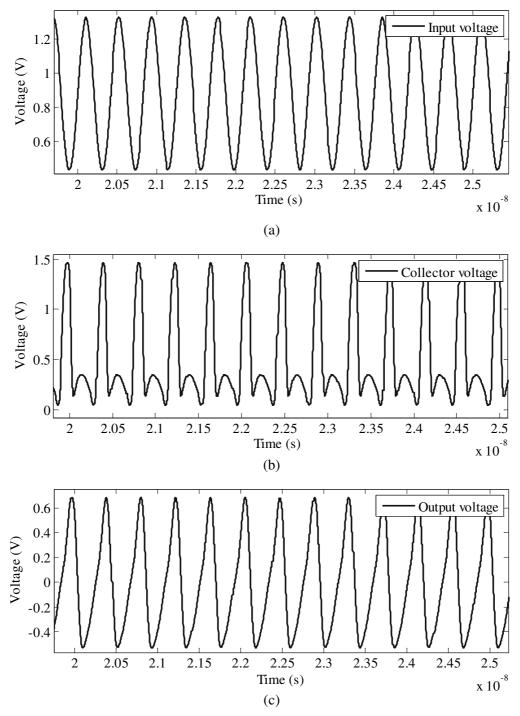

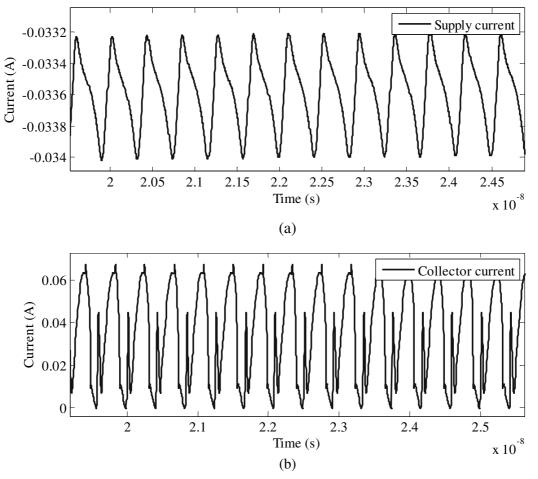

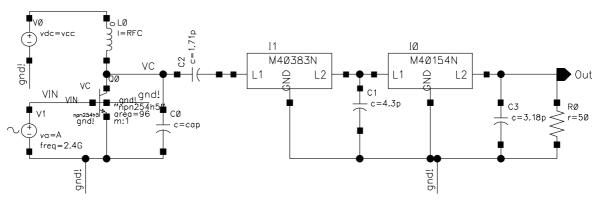

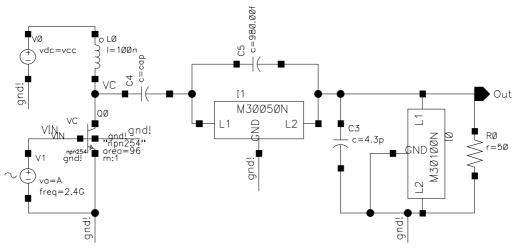

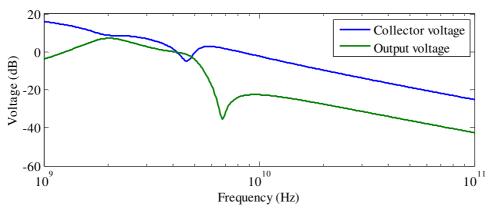

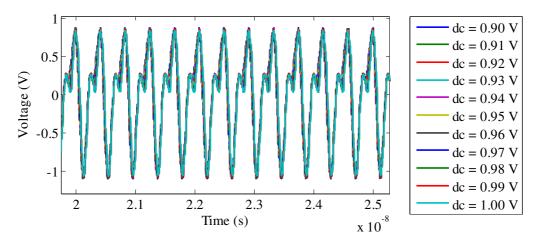

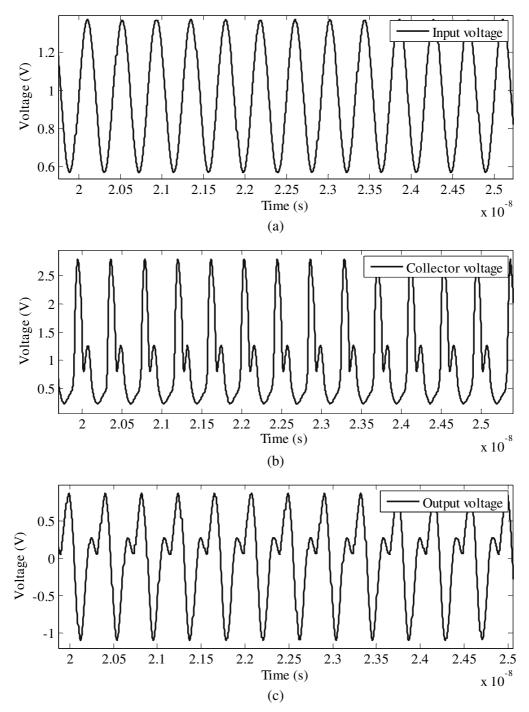

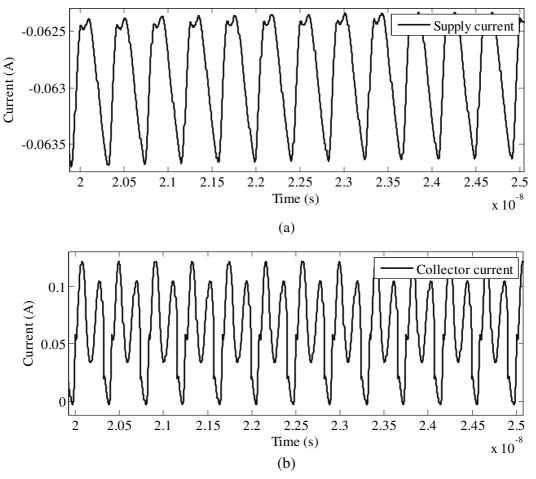

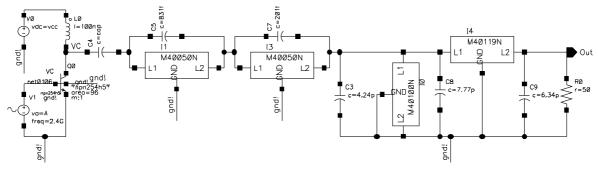

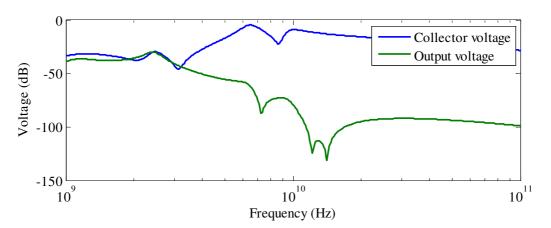

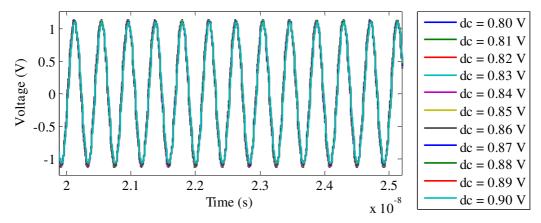

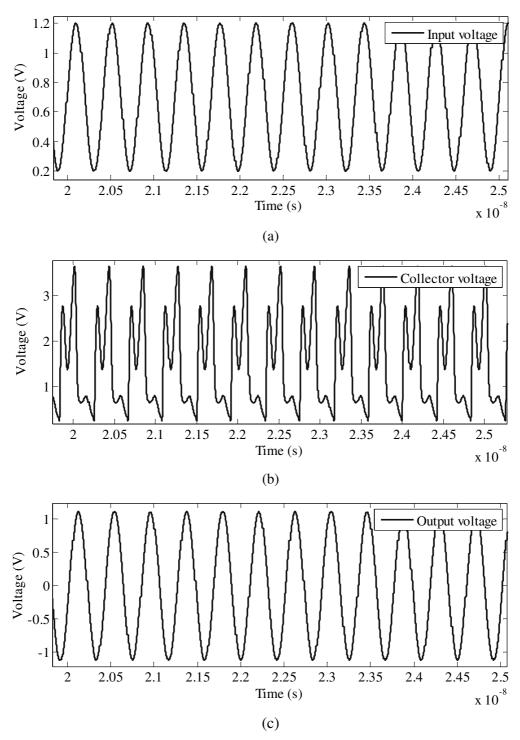

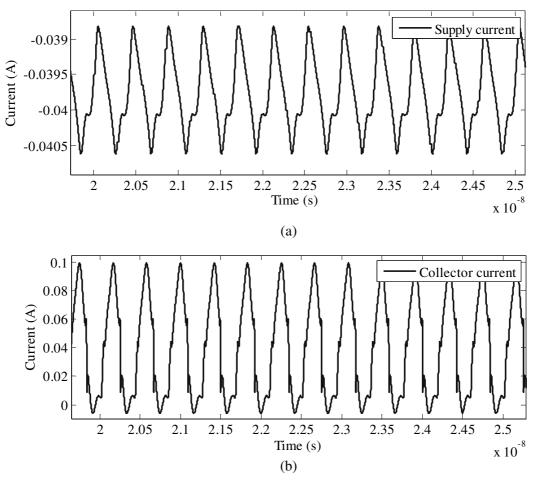

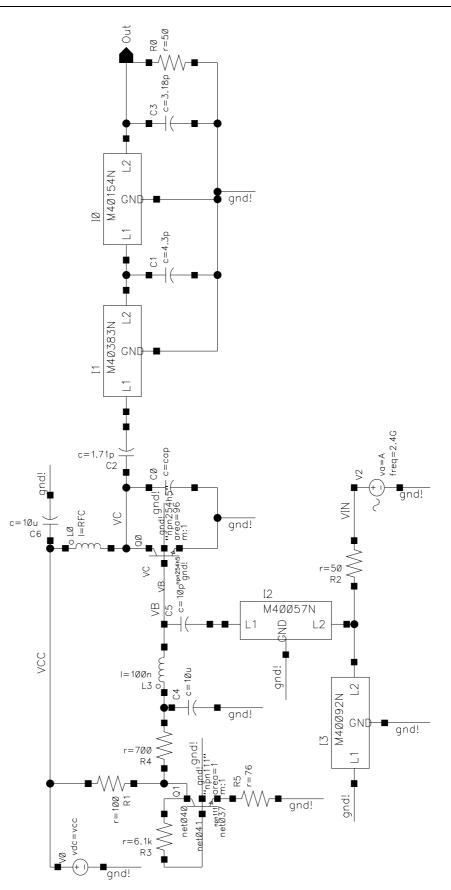

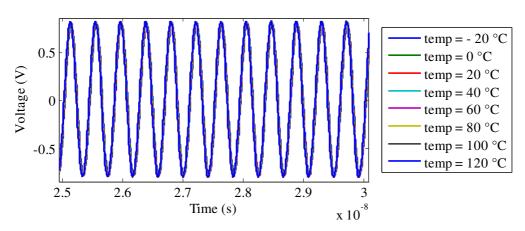

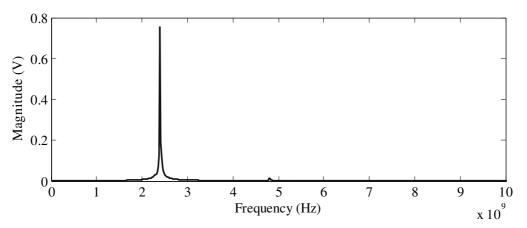

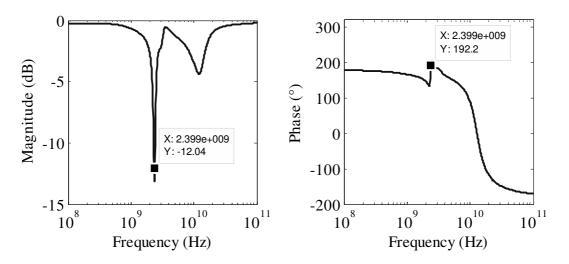

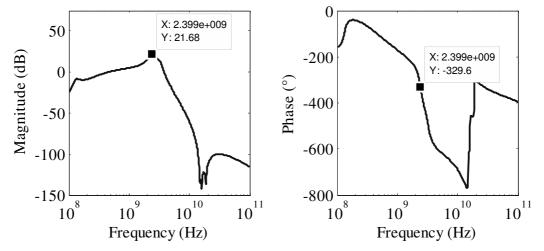

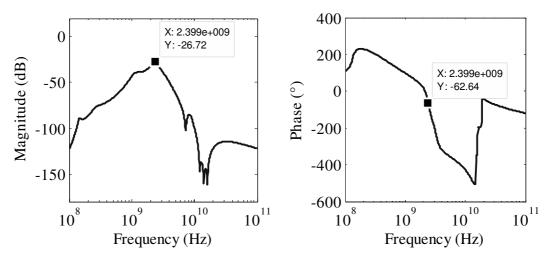

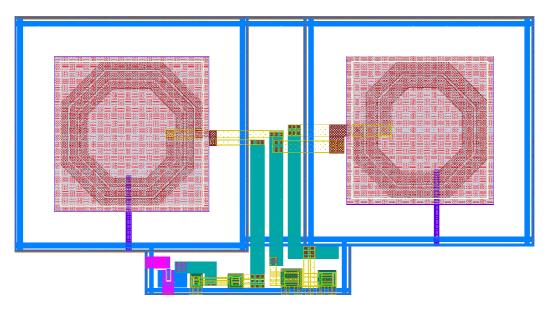

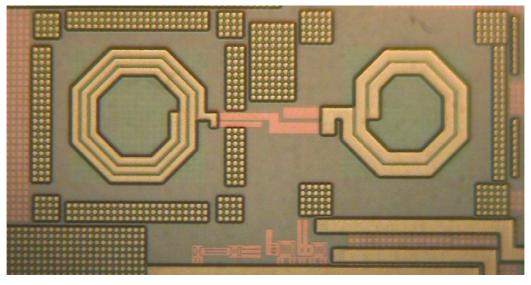

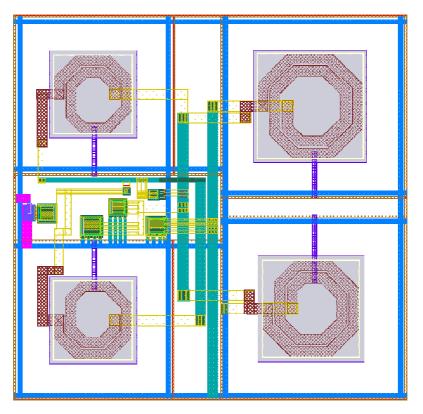

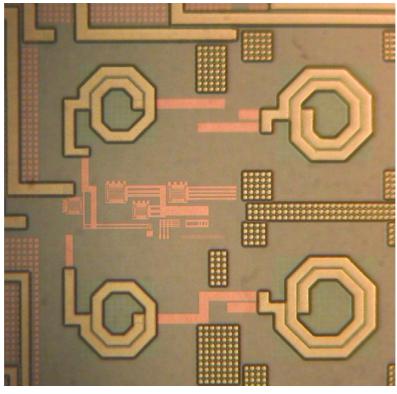

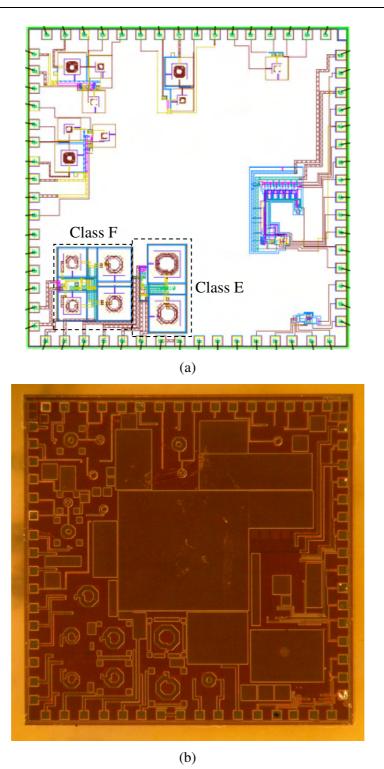

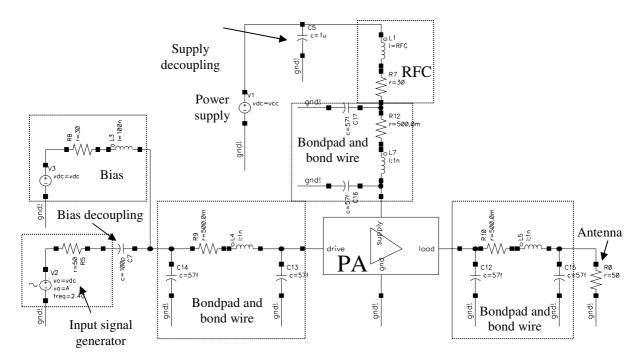

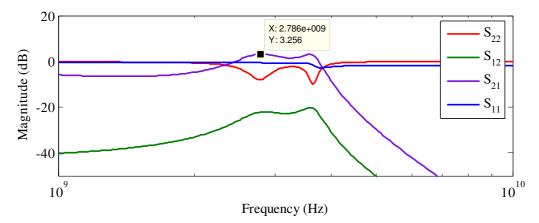

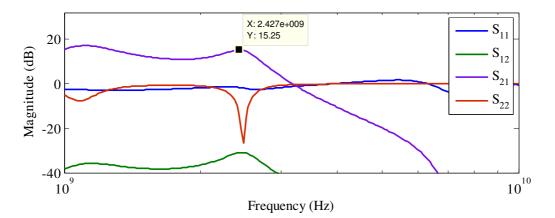

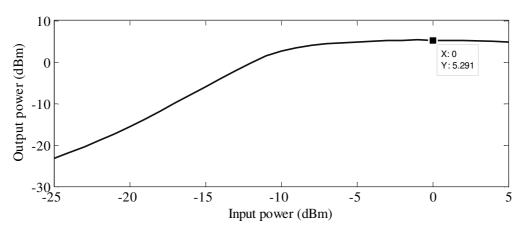

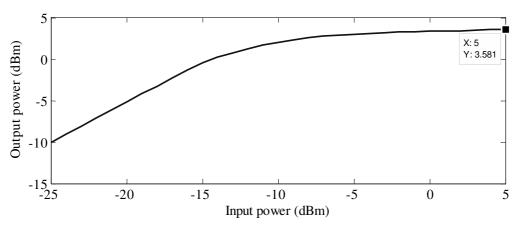

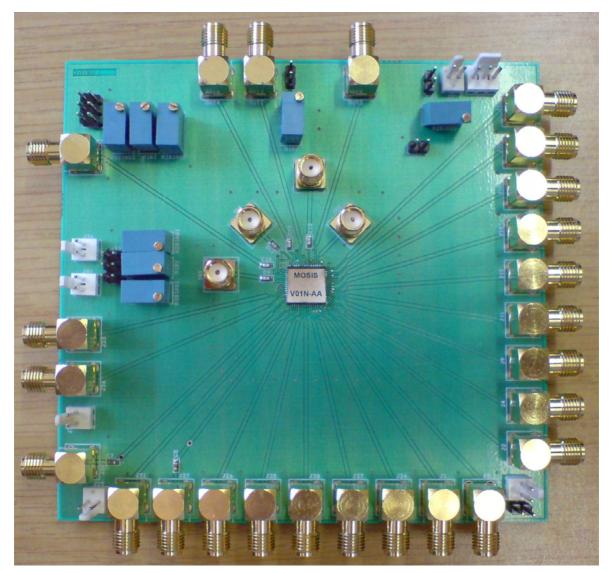

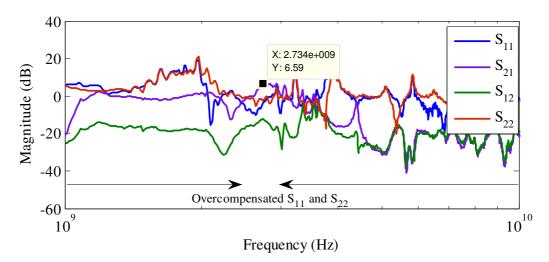

Quality of the PA output is usually improved by various linearization techniques [45-47]. These include feedback, feedforward, pre- and postdistortion outphasing, as well as PWM and supply modulation. Efficiency can be boosted by means of adaptive bias and Doherty techniques [48]. Power combining is usually used to increase the total output power of a PA system. This can be performed on- and off-chip [1]. A good example of a high power amplifier that employs power combining can be found in [49]. The circuit uses distributed active transformer (DAT) architecture to deliver 35 dBm of power from an IC fabricated in 130 nm CMOS technology. Further two power combining transformer configurations are described in [50].