# LC-LADDER AND CAPACITIVE SHUNT-SHUNT FEEDBACK LNA MODELLING FOR WIDEBAND HBT RECEIVERS

by

# **Marnus Weststrate**

Submitted in partial fulfilment of the requirements for the degree

**Philosophiae Doctor (Electronic Engineering)**

in the

Department of Electrical, Electronic and Computer Engineering

Faculty of Engineering, Built Environment and Information Technology

UNIVERSITY OF PRETORIA

July 2011

# **SUMMARY**

# LC-LADDER AND CAPACITIVE SHUNT-SHUNT FEEDBACK LNA MODELLING FOR WIDEBAND HBT RECEIVERS

by

#### **Marnus Weststrate**

Promoter: Prof. S. Sinha

Department: Electrical, Electronic and Computer Engineering

University: University of Pretoria

Degree: Philosophiae Doctor (Electronic Engineering)

Keywords: Low noise amplifier, wideband, ladder filters, capacitive feedback,

noise generators, impedance matching, mathematical model, noise optimization, performance trade-offs, mm-wave, SiGe Heterojunction

Bipolar Transistor (HBT)

Although the majority of wireless receiver subsystems have moved to digital signal processing over the last decade, the low noise amplifier (LNA) remains a crucial analogue subsystem in any design being the dominant subsystem in determining the noise figure (NF) and dynamic range of the receiver as a whole.

In this research a novel LNA configuration, namely the LC-ladder and capacitive shunt-shunt feedback topology, was proposed for use in the implementation of very wideband LNAs. This was done after a thorough theoretical investigation of LNA configurations available in the body of knowledge from which it became apparent that for the most part narrowband LNA configurations are applied to wideband applications with suboptimal results, and also that the wideband configurations that exist have certain shortcomings.

A mathematical model was derived to describe the new configuration and consists of equations for the input impedance, input return loss, gain and NF, as well as an approximation of the worst case IIP3. Compact design equations were also derived from

this model and a design strategy was given which allows for electronic design automation of a LNA using this configuration. A process for simultaneously optimizing the circuit for minimum NF and maximum gain was deduced from this model and different means of improving the linearity of the LNA were given. This proposed design process was used successfully throughout this research.

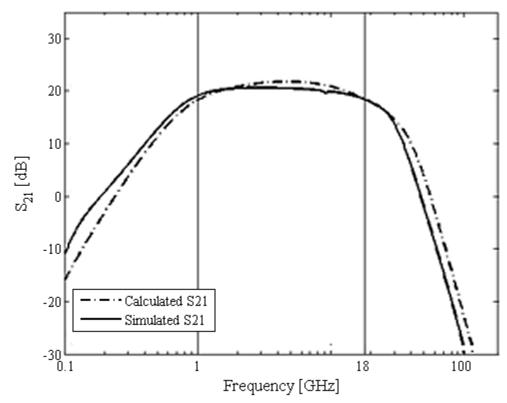

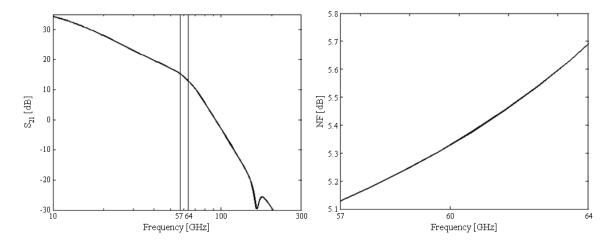

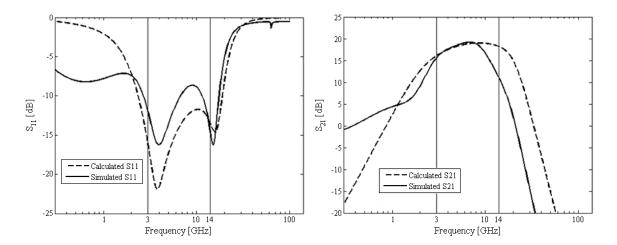

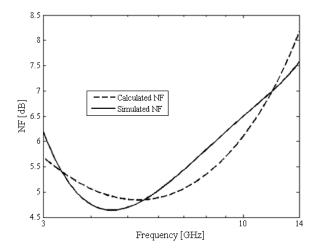

The accuracy of the mathematical model has been verified using simulations. Two versions of the LNA were also fabricated and the measured results compared well with these simulations. The good correlation found between the calculated, simulated and measured results prove the accuracy of the model, and some comments on how the accuracy of the model could be improved even further are provided as well.

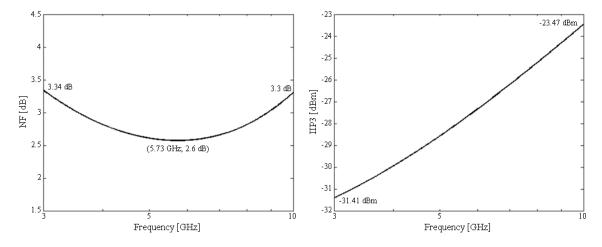

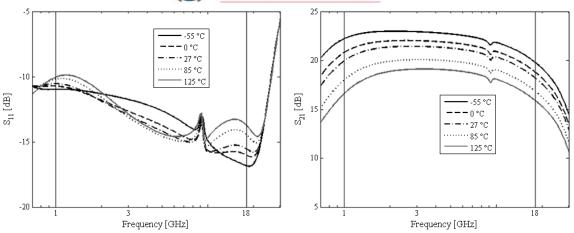

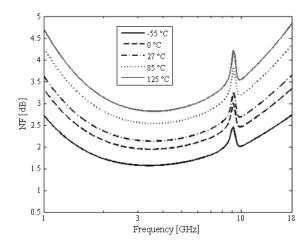

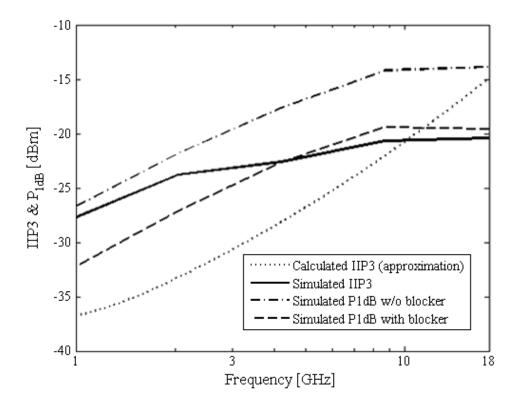

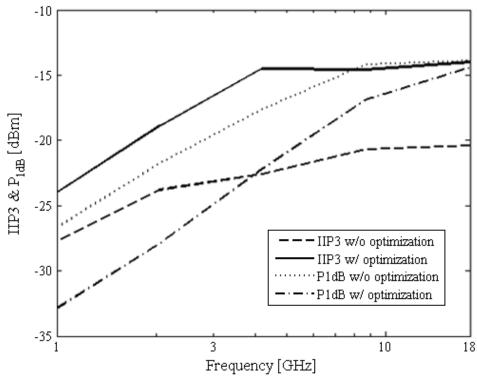

The simulated results of a LNA designed for the 1 GHz to 18 GHz band in the IBM 8HP process show a gain of 21.4 dB and a minimum NF of only 1.7 dB, increasing to 3.3 dB at the upper corner frequency while maintaining an input return loss below -10 dB. After steps were taken to improve the linearity, the IIP3 of the LNA is -14.5 dBm with only a small degradation in NF now 2.15 dB at the minimum. The power consumption of the respective LNAs are 12.75 mW and 23.25 mW and each LNA occupies a chip area of only 0.43 mm<sup>2</sup>.

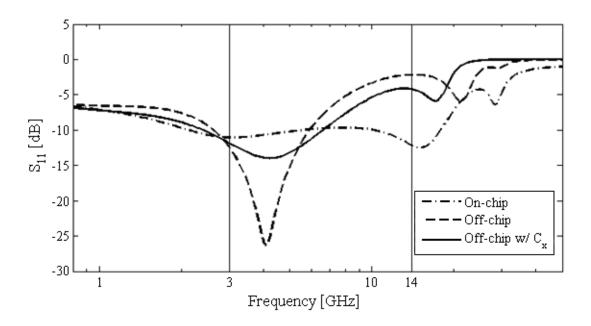

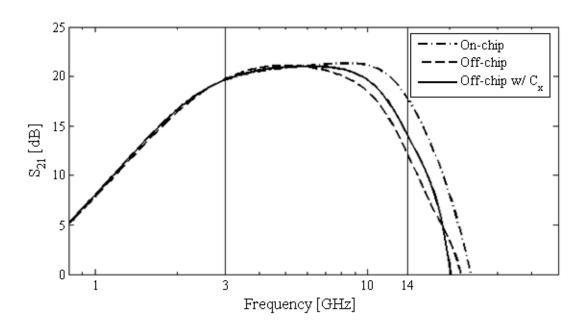

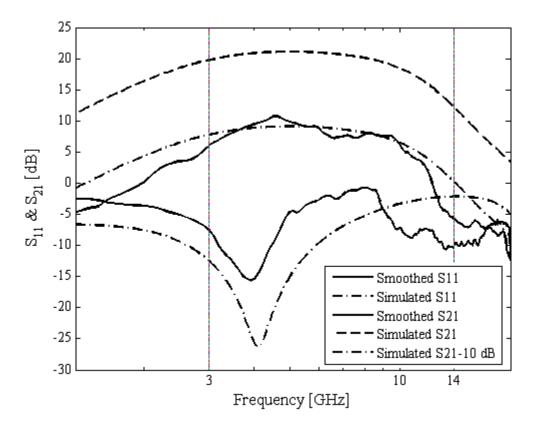

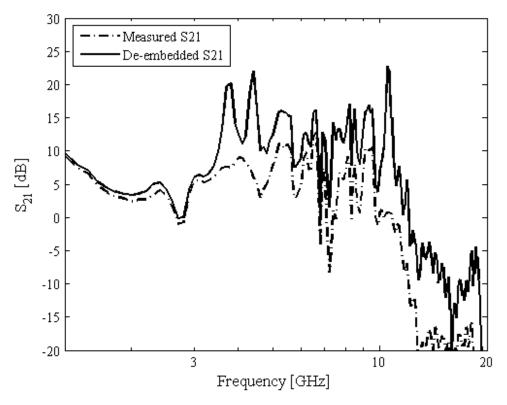

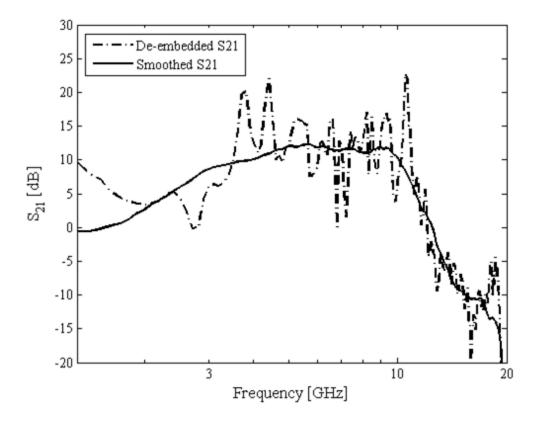

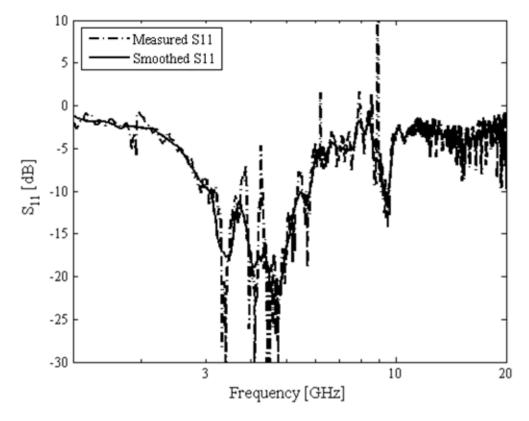

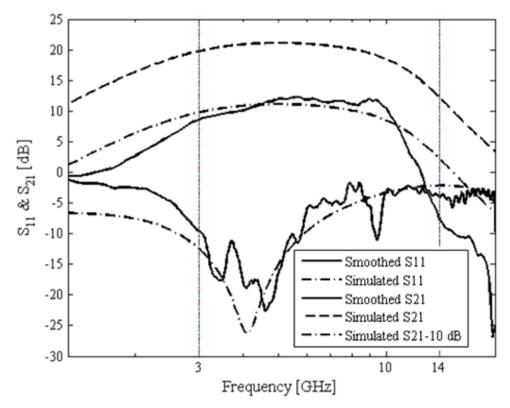

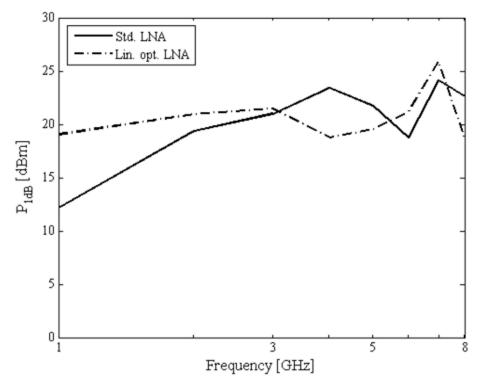

Measured results of the LNA fabricated in the IBM 7WL process had a gain of 10 dB compared to an expected simulated gain of 20 dB, however significant path loss was introduced by the IC package and PCB parasitics. The  $S_{II}$  tracked the simulated response very well and remained below -10 dB over the feasible frequency range. Reliable noise figure measurements could not be obtained. The measured  $P_{IdB}$  compression point is -22 dBm.

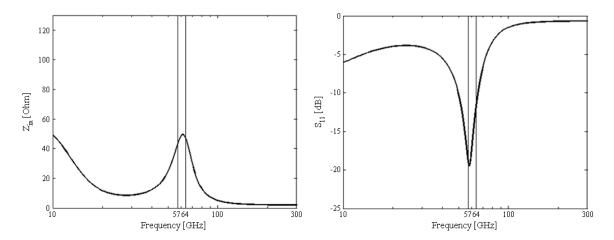

A 60 GHz LNA was also designed using this topology in a SiGe process with  $f_T$  of 200 GHz. A simulated NF of 5.2 dB was achieved for a gain of 14.2 dB and an input return loss below -15 dB using three amplifier stages. The IIP3 of the LNA is -8.4 dBm and the power consumption 25.5 mW. Although these are acceptable results in the mm-wave range it was however found that the wideband nature of this configuration is redundant in the unlicensed 60 GHz band and results are often inconsistent with the design theory due to second order effects.

The wideband results however prove that the LC-ladder and capacitive shunt-shunt feedback topology is a viable means for especially implementing LNAs that require a very wide operating frequency range and also very low NF over that range.

# **OPSOMMING**

# LC-LEER EN KAPASITIEWE SJUNT-SJUNT-TERUGVOER LRV-MODELLERING VIR WYEBAND-HBT-ONTVANGERS

deur

#### **Marnus Weststrate**

Promotor: Prof. S. Sinha

Departement: Elektriese, Elektroniese en Rekenaaringenieurswese

Universiteit: Universiteit van Pretoria

Graad: Philosophiae Doctor (Elektroniese Ingenieurswese)

Sleutelwoorde: Laeruis-versterker, wyeband, LC-leerfilters, kapasitiewe terugvoer,

ruisbronne, impedansieaanpassing, wiskundige model, ruisoptimering, verrigtings-kompromieë, mm-golf, SiGe Heterovoegvlak- Bipolêre

Transistor (HBT).

Alhoewel die meeste draadlose ontvangersubstelsels oor die laaste dekade na syfer-seinprosessering verskuif het, bly die laeruis-versterker (LRV) steeds 'n noodsaaklike analoogsubstelsel in enige ontwerp, aangesien dit die substelsel is met die grootste impak op die ruissyfer van die ontvanger as geheel.

In hierdie navorsing word 'n nuwe LRV-topologie, naamlik die LC-leer en kapasitiewe sjunt-sjunt-terugvoertopologie, voorgestel vir gebruik in uiters wyeband-LRVs. Dit is gedoen na 'n deeglike teoretiese ondersoek van huidige LRVs in die literatuur. Hieruit het dit duidelik geword dat smalband-LRV-topologië oor die algemeen vir wyeband-toepassings gebruik word, wat lei tot suboptimale resultate, en ook dat die wyeband-topologië wat wel bestaan, bepaalde tekortkominge het.

'n Wiskundige model is afgelei om hierdie nuwe topologie te beskryf en bestaan uit vergelykings vir die inset-impedansie, die inset-weerkaatsingsverlies, die spanningswins en die ruissyfer, asook 'n benadering vir die ergste IIP3-geval. Kompakte ontwerpvergelykings is ook van die model afgelei en 'n ontwerpstrategie geskik vir

elektroniese ontwerpsoutomatisasie van LRVs met hierdie topologie is voorgestel. 'n Proses vir die optimering van die versterker om die ruissyfer te minimeer is afgelei van die model en verskillende metodes om die lineariteit van die LRV te verbeter, is bespreek. Die voorgestelde ontwerpproses is deurgaans suksesvol toegepas tydens hierdie navorsing.

Die akkuraatheid van die wiskundige model is bevestig deur simulasies. Twee weergawes van die LRV is vervaardig en die gemete resultate vergelyk goed met die simulasies. Die goeie korrellasie tussen die berekende, simulasie- en gemete resultate bewys die akkuraatheid van die model. Opmerkings oor moontlike verbeterings aan die model om die akkuraatheid selfs verder te verbeter, is ook gemaak.

Die simulasieresultate van 'n LRV wat ontwerp is vir die 1 GHz- tot 18 GHz-band in die IBM 8HP-proses wys 'n wins van 21.4 dB en 'n minimum ruissyfer van slegs 1.7 dB, wat vermeerder tot 3.3 dB by die boonste afsny-frekwensie, terwyl die inset-weerkaatsingsverlies onder -10 dB bly. Nadat stappe gedoen is om die lineariteit te verbeter, is die IIP3 van die LRV -14.5 dBm met slegs 'n klein verswakking in ruis, waar die minimumruissyfer nou 2.15 dB is. Die LRVs se drywingsverbruik is onderskeidelik 12.75 mW en 23.25 mW en elke LRV beslaan 'n oppervlak van slegs 0.43 mm<sup>2</sup>.

Gemete resultate van die LRV wat in the IBM 7WL-proses vervaardig is, toon 'n wins van 10 dB teenoor 'n verwagte gesimuleerde wins van 20 dB. Merkwaardige verliese is egter teenwoordig as gevolg van die geïntegreerde stroombaanpakkie en die toets-etsbord. Die gemete  $S_{II}$  volg die simulasies egter besonder goed en bly onder -10 dB oor die totale moontlike frekwensiebereik soos gevind in die simulasies. 'n Betroubare ruissyfermeting kon nie geneem word nie. Die gemete  $P_{1dB}$ -winssaamperspunt is -22 dBm.

Verder is 'n 60 GHz LRV ontwerp met hierdie topologie in 'n SiGe-proses met 'n  $f_T$  van 200 GHz. 'n Gesimuleerde ruissyfer van 5.2 dB is behaal met 'n wins van 14.2 dB en insetweerkaastingsverlies laer as -15 dB deur drie versterkerstadiums te gebruik. Die IIP3 van die LRV is -8.4 dBm met 'n drywingsverbruik van 25.5 mW. Alhoewel die resultate aanvaarbaar is in die mm-golflengteband, is so 'n wyeband-implementasie oorbodig in die ongelisensieerde 60 GHz-band en is gevind dat die resultate ook dikwels nie ooreenstem met die ontwerpsteorie nie as gevolg van tweede-orde-effekte.

Die wyeband-resultate bewys egter dat die LC-leer en kapasitiewe sjunt-sjunt-terugvoertopologie goeie potensiaal inhou vir LRV implementasies, wat veral 'n uiters wye bandwydte nodig het, asook 'n baie lae ruissyfer oor daardie band.

# **ACKNOWLEDGMENT**

First and foremost I thank God for the grace of giving me the ability to complete this work and I trust that He will use my qualification for the glory of His name.

This research would not have been possible if it was not for my supervisor Prof. Saurabh Sinha who has over time been my teacher, mentor and friend. For not only offering me the opportunity to continue my postgraduate studies at the Carl and Emily Fuchs Institute for Microelectronics (CEFIM), but also securing funding for the research, and the invaluable guidance, advice and review of my work many thanks. Your availability, dedication to the betterment of your students, and effort towards providing quality feedback in as short a time as possible does not go unnoticed and was a key factor in the success of my research.

It has also been a pleasure working alongside my friends and colleagues Marius Goosen and Mladen Božanić towards the submission or our circuits on a combined MPW run. The teamwork is much appreciated. Also special thanks to Marius with whom I was able to discuss my work throughout the past few years leading up to this thesis which served as a catalyst in finding solutions to many problems.

I would also like to thank Jannes Venter for the Cadence support he provides at CEFIM and the great amount of time spent towards configuring a Cadence server compatible with the IBM HIT-kits. Our informal conversations on circuit design and layout have also been invaluable.

Thanks also to my other colleagues and friends at CEFIM, namely Wayne Maclean, Christo Janse van Rensburg, Johan Schoeman and Wynand Lambrechts for making the time spent on this research fun. And thanks to Johan and Wynand for reviewing the Afrikaans version of my summary. I also thank Professor Monuko du Plessis for his sound directing of the activities at CEFIM and Tilla Nel for ensuring that the admin runs so smoothly.

Finally I thank my other friends and family for the support they have given me, and in particular my mother for teaching me how to learn and strive for excellence from a young age, and my father for imparting his interest and experience in circuit design to me and for the countless discussions to the benefit of my research.

This research has been funded by ARMSCOR (the Armaments Corporation of South Africa Ltd.) under the direction of Rob Calitz and Knowledge Ramolefe for which I am truly grateful. The funds were administered by the Council for Scientific and Industrial Research (CSIR), South Africa.

I would also like to thank the Defence, Peace, Safety and Security (DPSS) business unit at the CSIR as well as Grintek Ewation for availing their laboratories for the experimental testing of the low noise amplifier.

I thank Denel Dynamics, a division of Denel (Pty) Ltd., for both extending my bursary to include my postgraduate studies and allowing me the time to complete this research.

I thank MOSIS for accepting my research proposal and granting the free IBM 7WL MPW production run that was used to fabricate the LNA.

I also thank the National Research Foundation (NRF) of South Africa for contributing toward travel expenses for conferences where this work was presented, as well as IMT-Bucharest in Romania for paying my local expenses in Romania through their bilateral agreement with CEFIM on two accounts. I thank also the Federal Ministry for Education and Research (BMBF), Germany, for paying my local expenses for a long term exchange at the Technical University of Dresden (TUD), and my colleagues at TUD for the pleasure of working with them.

# TABLE OF CONTENTS

| SUM  | MARY   | 7                                                          | i   |

|------|--------|------------------------------------------------------------|-----|

| OPSC | OMMI   | NG                                                         | iv  |

| ACK  | NOWL   | EDGMENT                                                    | vii |

| TABI | LE OF  | CONTENTS                                                   | ix  |

| LIST | OF AI  | BBREVIATIONS                                               | xiv |

| CHA  | PTER   | 1: INTRODUCTION                                            | 1   |

| 1.1  | BA     | CKGROUND TO THE RESEARCH                                   | 1   |

| 1.2  | HY     | POTHESIS AND RESEARCH QUESTIONS                            | 3   |

| 1.3  | JU     | STIFICATION FOR THE RESEARCH                               | 4   |

| 1.4  | RE     | SEARCH METHODOLOGY                                         | 6   |

| 1.5  | DE     | LIMITATIONS OF SCOPE AND KEY ASSUMPTIONS                   | 7   |

| 1.6  | CO     | NTRIBUTION TO THE FIELD                                    | 7   |

| 1.7  |        | BLICATIONS LEADING FROM THIS RESEARCH                      |     |

| 1.8  | OU     | TLINE OF THE THESIS                                        | 11  |

| CHA  | PTER 2 | 2: LITERATURE REVIEW                                       | 14  |

| 2.1  | IN     | FRODUCTION                                                 | 14  |

| 2.2  | NC     | DISE IN AMPLIFIER CIRCUITS                                 | 15  |

| 2.3  | NC     | DISE IN HBT AMPLIFIERS                                     |     |

| 2    | 2.3.1  | Common-emitter amplifier noise and gain parameters         |     |

| 2    | 2.3.2  | Low noise capability of HBTs                               |     |

| 2    | 2.3.3  | Design for minimum transistor noise figure                 | 22  |

| 2.4  | LIN    | NEARITY OF HBT AMPLIFIERS                                  | 23  |

| 2.5  | INI    | PUT MATCHING                                               | 25  |

| 2    | 2.5.1  | Traditional input matching techniques                      | 25  |

| 2    | 2.5.2  | Impedance matching in the super high frequency range       | 26  |

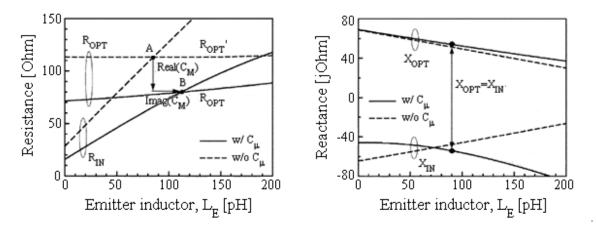

| 2    | 2.5.3  | Inductive emitter degeneration                             | 28  |

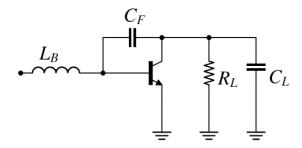

| 2    | 2.5.4  | Capacitive shunt-shunt feedback technique                  | 34  |

| 2    | 2.5.5  | LC-ladder input matching network with emitter degeneration | 36  |

| 2    | 2.5.6  | Wideband matching using shunt-shunt feedback               |     |

| 2.6  | PE     | RFORMANCE MEASURE TRADE-OFFS                               |     |

| 2    | 2.6.1  | Noise figure                                               |     |

| 2    | 2.6.2  | Linearity                                                  | 41  |

|    | 2.6 | .3   | Gain                                                          | . 41 |

|----|-----|------|---------------------------------------------------------------|------|

| 2  | 2.7 | ON   | -CHIP PASSIVE INDUCTORS                                       | . 42 |

| 2  | 2.8 | AC'  | TIVE INDUCTORS                                                | . 44 |

| 2  | 2.9 | CO   | NCLUSION                                                      | . 48 |

| СН | APT | ER 3 | 8: SiGe MONOLITHIC TECHNOLOGIES                               | . 50 |

| 3  | 3.1 | INT  | RODUCTION                                                     | . 50 |

| 3  | 3.2 | HE   | TEROJUNCTION BIPOLAR TRANSISTORS                              | . 50 |

| 3  | 3.3 | HB'  | T MODELS                                                      | . 51 |

|    | 3.3 | .1   | VBIC – vertical bipolar inter-company model                   | .51  |

|    | 3.3 | .2   | HICUM – high current model                                    | . 52 |

| 3  | 3.4 | ME   | TAL AND INTERCONNECT LAYERS                                   | . 54 |

| 3  | 3.5 | 8HI  | P AND 7WL RESISTORS                                           | . 54 |

| 3  | 3.6 | CA   | PACITORS                                                      | . 54 |

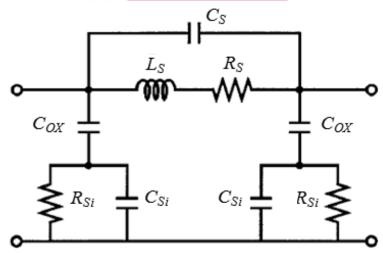

| 3  | 3.7 | IND  | DUCTORS AND TRANSMISSION LINES                                | . 55 |

|    | 3.7 | .1   | Inductor and RF-line layout considerations                    | . 55 |

| 3  | 3.8 | BO   | ND PADS                                                       | . 56 |

| 3  | 3.9 | CO   | NCLUSION                                                      | . 56 |

| СН | APT | ER 4 | : MATHEMATICAL MODELLING                                      | . 57 |

| 4  | .1  | INT  | RODUCTION                                                     | . 57 |

| 4  | .2  | INP  | PUT MATCHING                                                  | . 57 |

|    | 4.2 | .1   | LC-ladder network                                             | . 58 |

|    | 4.2 | .2   | Capacitive feedback Miller impedance                          | . 59 |

|    | 4.2 | .3   | Input reflection coefficient                                  | . 61 |

|    | 4.2 | .4   | Comparison to the inductively degenerated LC-ladder technique | . 62 |

| 4  | .3  | GA   | IN EQUATIONS                                                  | . 63 |

|    | 4.3 | .1   | Input matching network gain                                   | . 63 |

|    | 4.3 | .2   | First stage gain                                              | . 64 |

|    | 4.3 | .3   | Second stage gain and gain flattening                         | . 65 |

|    | 4.3 | .4   | Further gain stages                                           | . 66 |

| 4  | .4  | LN   | A DESIGN EQUATIONS                                            | . 66 |

| 4  | 5   | INP  | PUT MATCHING MODELLING IMPROVEMENT                            | . 68 |

| 4  | .6  | NO   | ISE FIGURE DERIVATION                                         | . 69 |

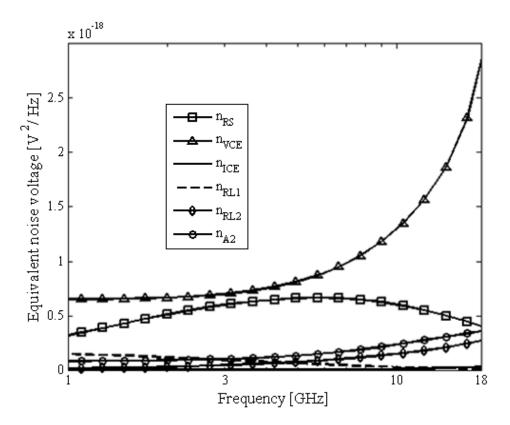

|    | 4.6 | .1   | Noise sources                                                 | . 70 |

|    | 4.6 | .2   | Simplifying the circuit                                       | .71  |

| 4.6   | 5.3  | Noise figure equation derivation                                           | 72  |

|-------|------|----------------------------------------------------------------------------|-----|

| 4.7   | IMI  | PROVING NOISE FIGURE AND GAIN                                              | 74  |

| 4.7   | .1   | Noise figure improvement                                                   | 75  |

| 4.7   | .2   | Simultaneous gain improvement                                              | 79  |

| 4.8   | LIN  | EARITY APPROXIMATION                                                       | 80  |

| 4.9   | PEF  | RFORMANCE LIMITS AND TRADE-OFFS                                            | 81  |

| 4.9   | .1   | Noise figure vs. bandwidth                                                 | 81  |

| 4.9   | .2   | Parasitic base-collector capacitance vs. lower corner frequency            | 83  |

| 4.10  | LIN  | MITS OF THE MODEL AND CONFIGURATION                                        | 84  |

| 4.1   | 0.1  | Input matching approximation                                               | 84  |

| 4.1   | 0.2  | Hybrid- $\pi$ transistor model and assumptions with regards to parasitics. | 85  |

| 4.1   | 0.3  | Gain bandwidth product                                                     | 85  |

| 4.1   | 0.4  | Passive on-chip components                                                 | 86  |

| 4.1   | 0.5  | Simplified inductor model                                                  | 86  |

| 4.1   | 0.6  | Base- and collector current noise correlation                              | 87  |

| 4.11  | TH   | EORETICAL RESULTS                                                          | 87  |

| 4.12  | LN   | A ELECTRONIC DESIGN AUTOMATION                                             | 88  |

| 4.13  | CO   | NCLUSION                                                                   | 89  |

| СНАРТ | ER 5 | S: SIMULATION RESULTS                                                      | 91  |

| 5.1   | INT  | RODUCTION                                                                  | 91  |

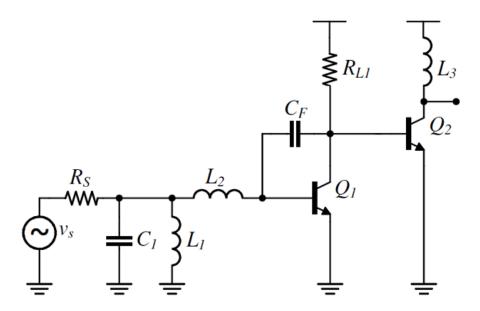

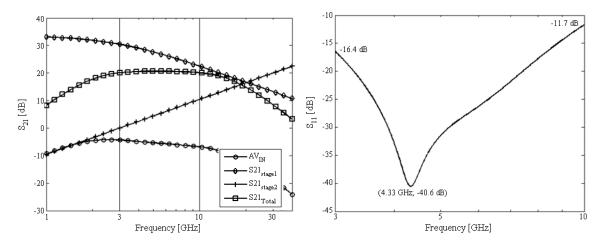

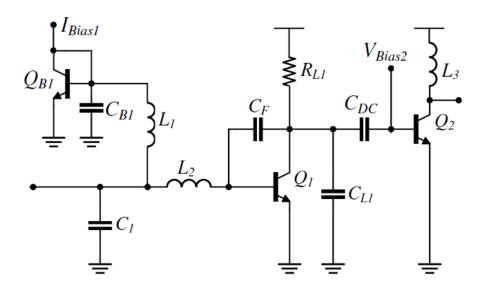

| 5.2   | CIR  | CUIT SCHEMATIC AND SPECIFICATIONS OF THE DESIGN                            | 92  |

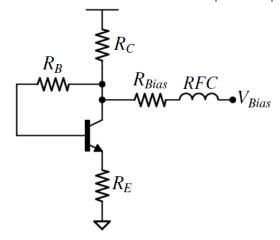

| 5.2   | .1   | Transistor biasing                                                         | 93  |

| 5.3   | 8HI  | P DESIGN FOR 1-18 GHZ                                                      | 94  |

| 5.3   | .1   | Initial design                                                             | 94  |

| 5.3   | .2   | Noise optimization                                                         | 96  |

| 5.3   | 3.3  | Stability                                                                  | 100 |

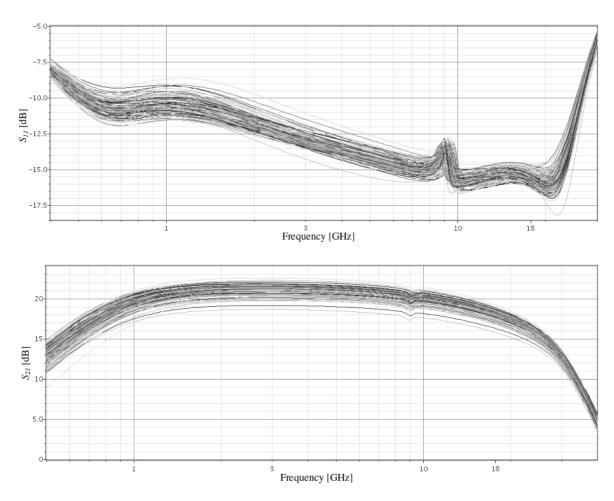

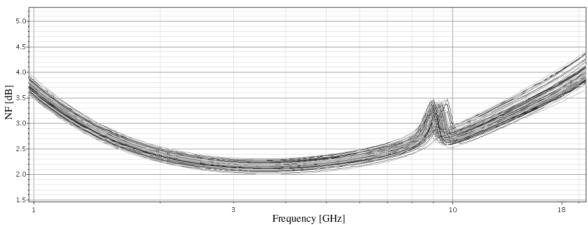

| 5.3   | .4   | Monte Carlo analysis and temperature sweep                                 | 100 |

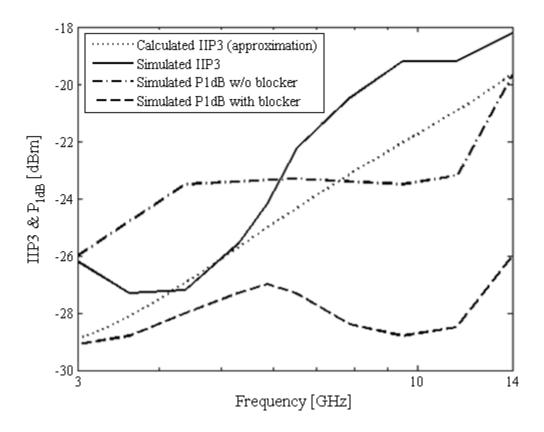

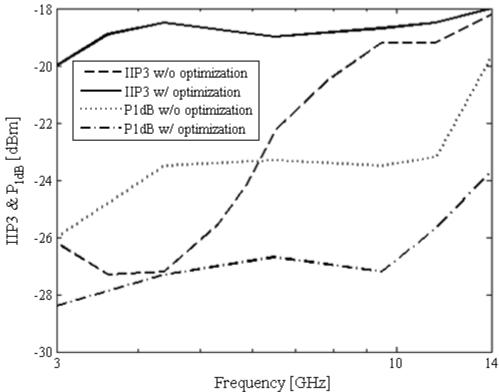

| 5.3   | 5.5  | Linearity of the LNA and its optimization                                  | 104 |

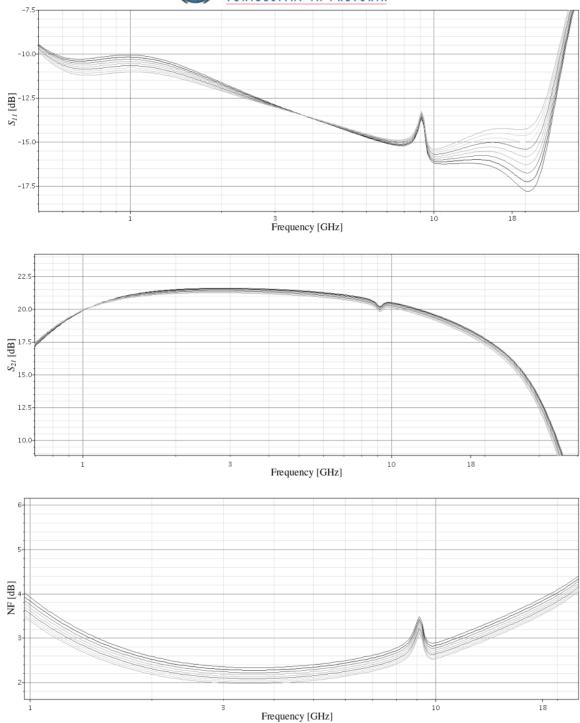

| 5.3   | .6   | Sensitivity of the LNA optimized for linearity                             | 108 |

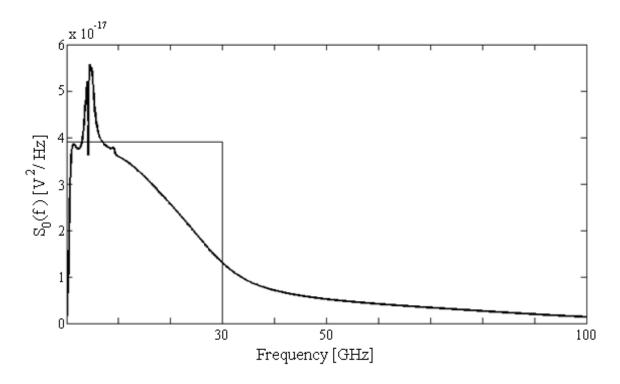

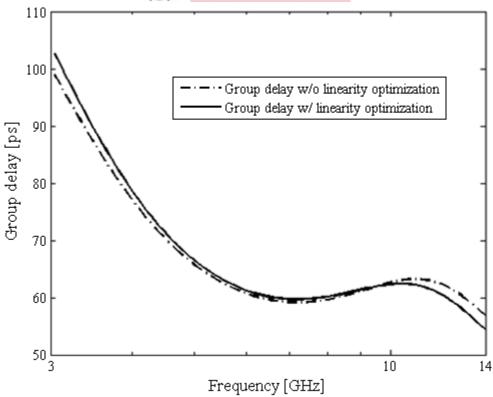

| 5.3   | .7   | Dynamic range and group delay                                              | 111 |

| 5.3   | 8.8  | Third amplifier stage                                                      | 113 |

| 5.3   | .9   | Final LNA specifications                                                   | 113 |

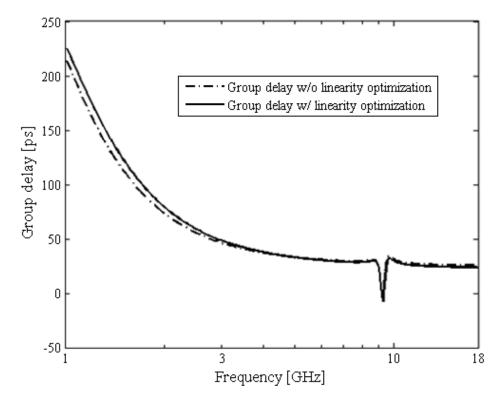

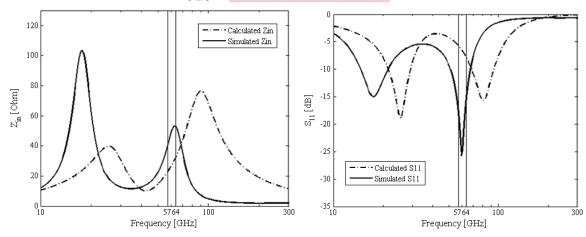

| 5.4   | 8HI  | P DESIGN AT 60 GHZ                                                         | 113 |

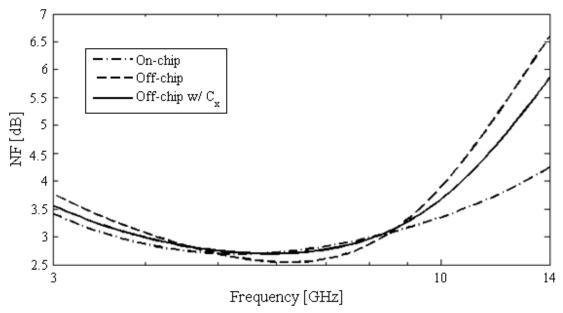

| 5.5   | 7W   | L DESIGN FOR 3-14 GHZ                                                      | 117 |

| 5.5.   | .1   | Initial design                                 | 117 |

|--------|------|------------------------------------------------|-----|

| 5.5.   | .2   | Noise optimization                             | 119 |

| 5.5.   | .3   | Stability                                      | 121 |

| 5.5.   | .4   | Monte Carlo analysis and temperature sweep     | 121 |

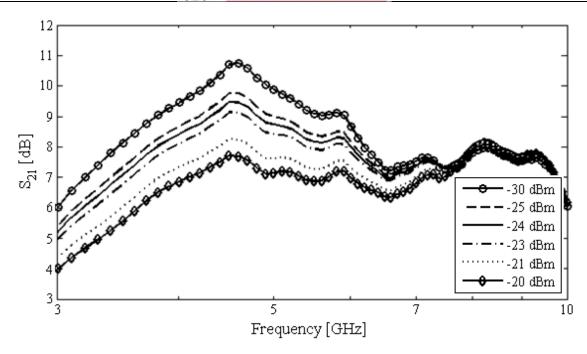

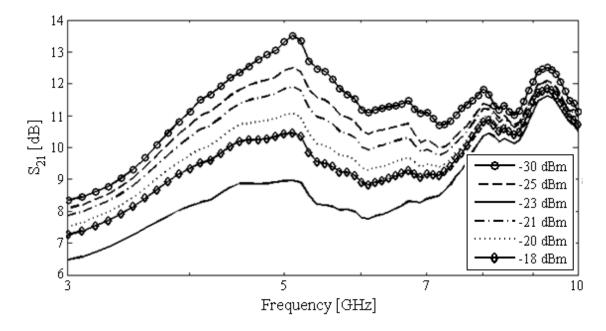

| 5.5.   | .5   | Linearity of the LNA and its improvement       | 124 |

| 5.5.   | .6   | Sensitivity of the LNA optimized for linearity | 126 |

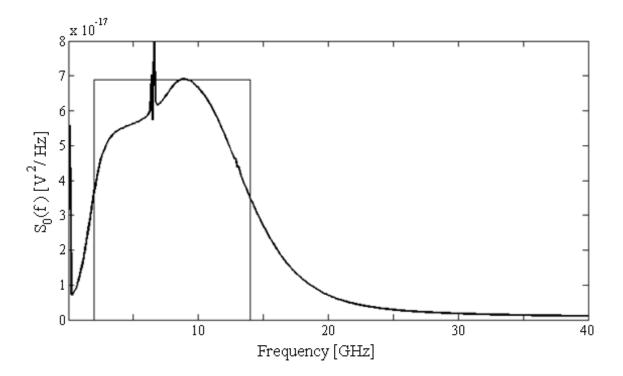

| 5.5.   | .7   | Dynamic range and group delay                  | 127 |

| 5.5.   | .8   | Final LNA specifications                       | 128 |

| 5.6    | CO   | NCLUSION                                       | 128 |

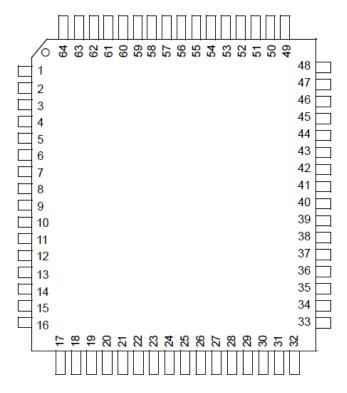

| CHAPT  | ER 6 | : LAYOUT AND FABRICATION                       | 130 |

| 6.1    | INT  | RODUCTION                                      | 130 |

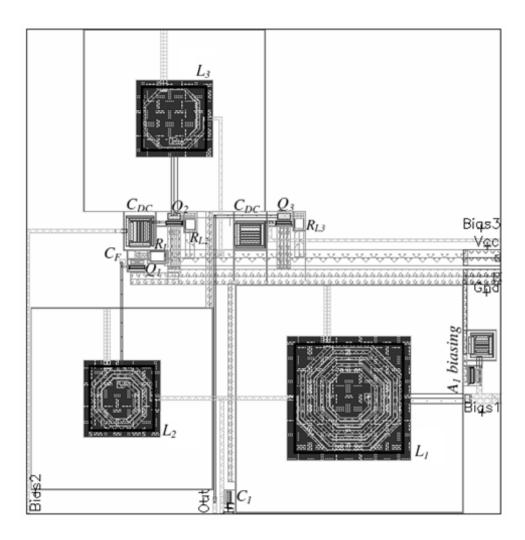

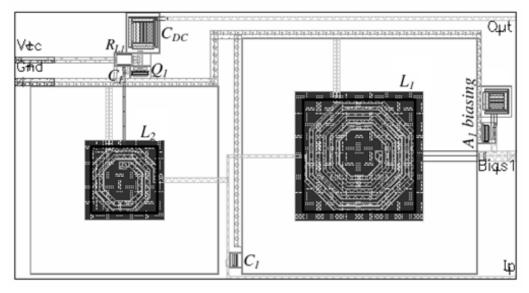

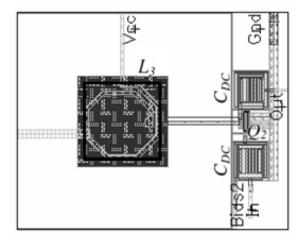

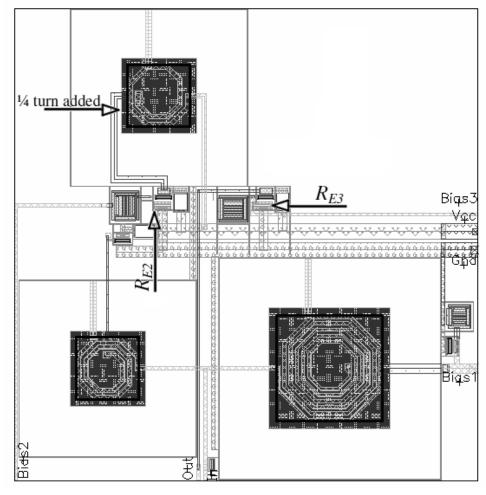

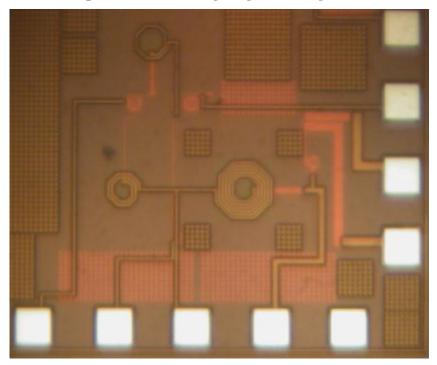

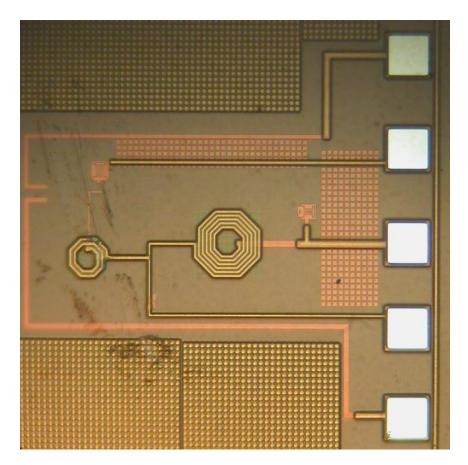

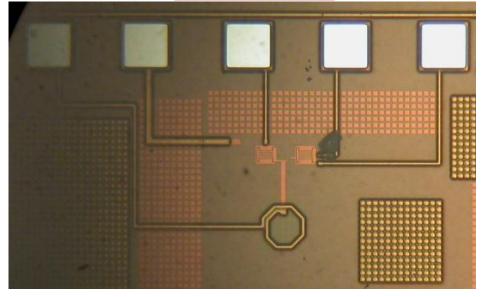

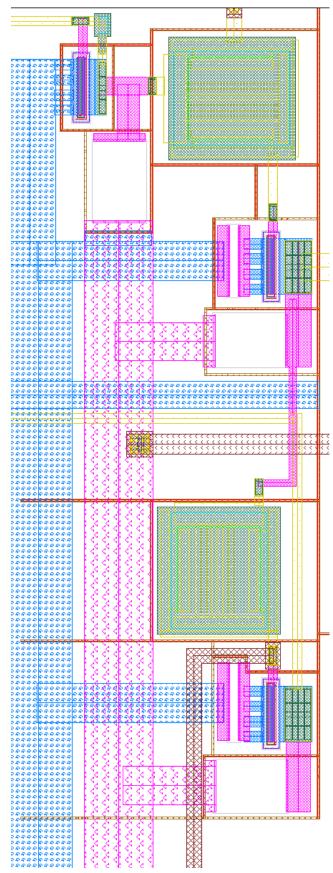

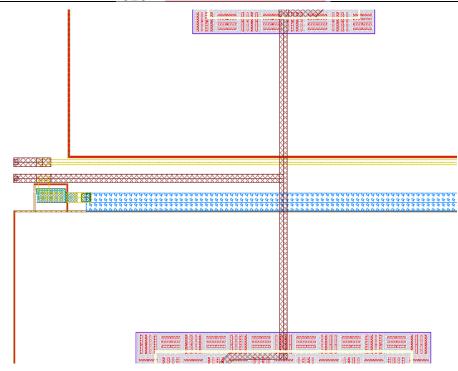

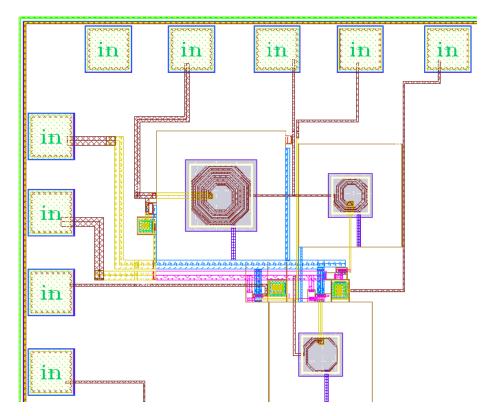

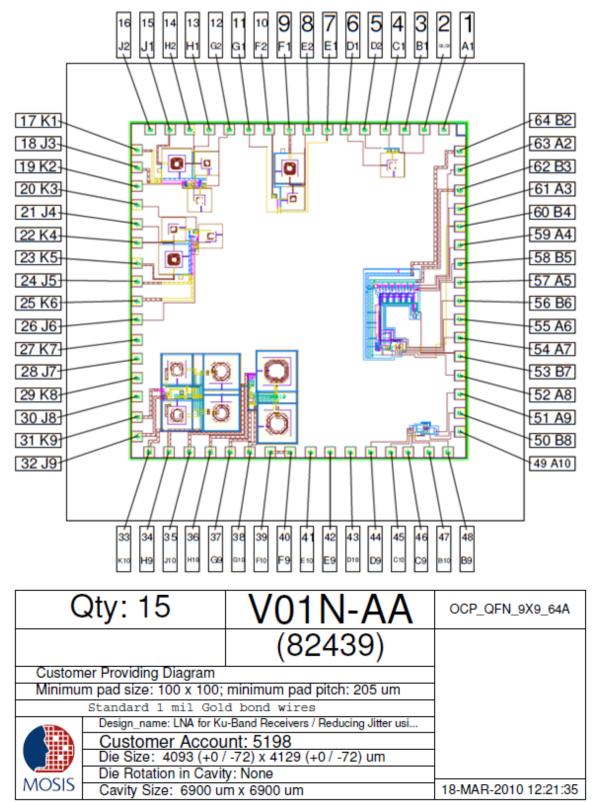

| 6.2    | CIR  | CUIT LAYOUTS                                   | 130 |

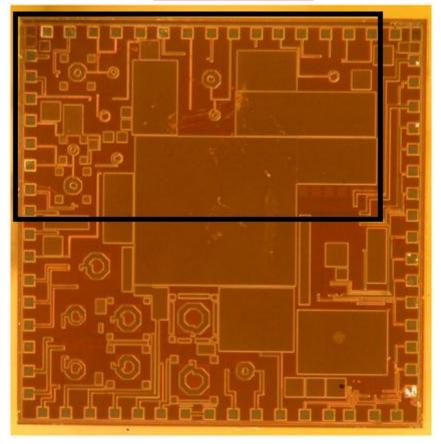

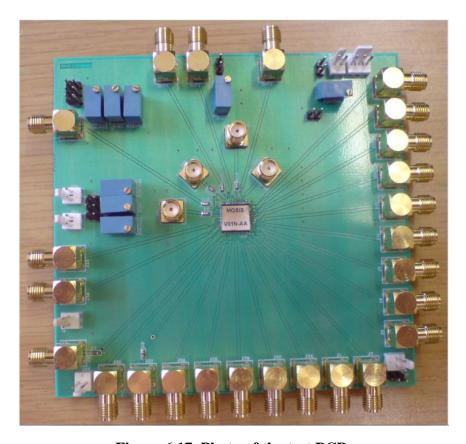

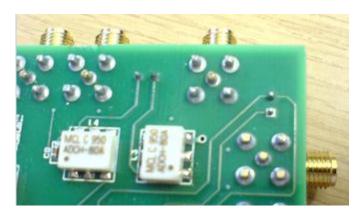

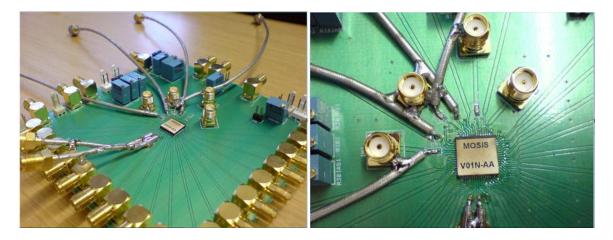

| 6.3    | PHC  | OTOS OF THE FABRICATED CHIP                    | 133 |

| 6.4    | PAC  | CKAGING                                        | 136 |

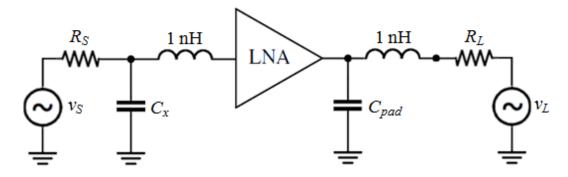

| 6.5    | PAC  | CKAGE PARASITICS AND ITS EFFECT ON PERFORMANCE | 137 |

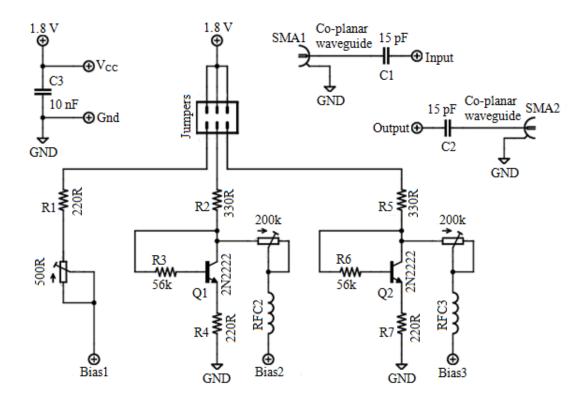

| 6.6    | TES  | T PCB                                          | 139 |

| 6.7    | SHC  | ORTCOMINGS OF THE TEST PCB                     | 141 |

| 6.7.   | .1   | SMA connectors                                 | 141 |

| 6.7.   | .2   | On chip DC blocking capacitors                 | 142 |

| 6.7.   | .3   | Layout recommendations for future testing      | 142 |

| 6.8    | COl  | NCLUSION                                       | 143 |

| CHAPT  | ER 7 | : EXPERIMENTAL RESULTS                         | 144 |

| 7.1    | INT  | RODUCTION                                      | 144 |

| 7.2    | ME   | ASUREMENT EQUIPMENT AND TEST PROCEDURE         | 144 |

| 7.3    | ME   | ASURED S-PARAMETERS                            | 146 |

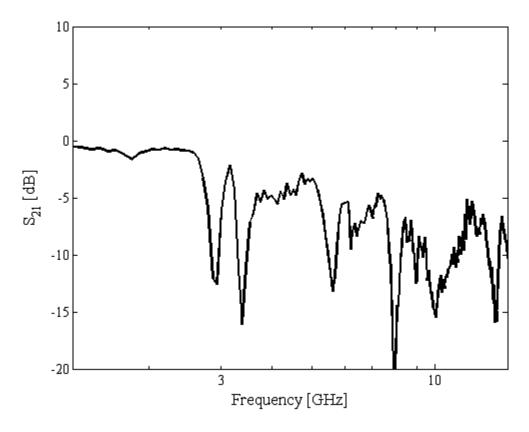

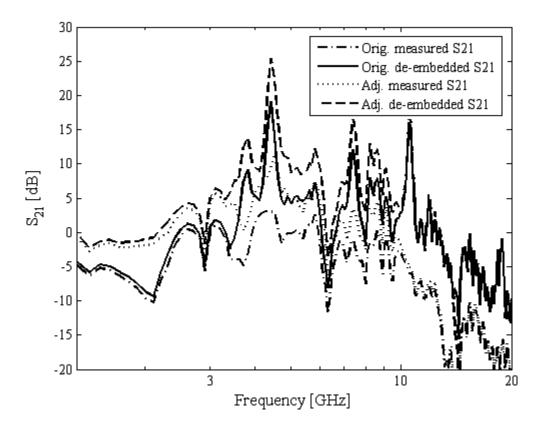

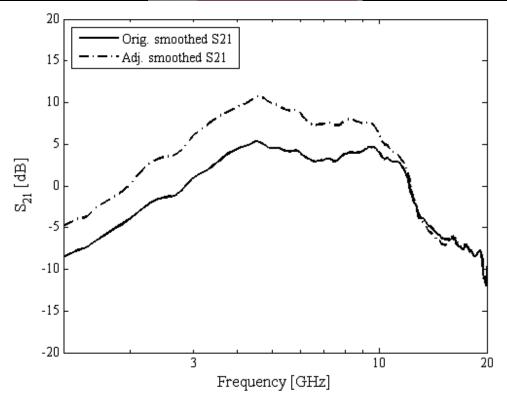

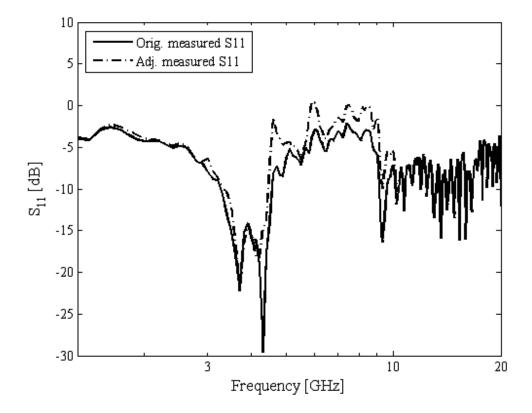

| 7.3.   | .1   | Standard LNA                                   | 148 |

| 7.3.   | .2   | LNA optimized for linearity                    | 150 |

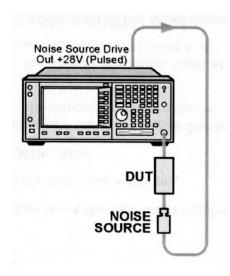

| 7.4    | ME   | ASURED NOISE FIGURE                            | 153 |

| 7.5    | ME   | ASURED P <sub>1DB</sub> COMPRESSION            | 154 |

| 7.6    | CO   | NCLUSION                                       | 156 |

| CHAPT  | ER 8 | : CONCLUSION                                   | 158 |

| 8.1    | CRI  | TICAL EVALUATION OF THE WORK                   | 158 |

| 8.2    | SUC  | GGESTIONS FOR FUTURE WORK                      | 161 |

| REFERE | ENCI | ES                                             | 164 |

| ADDENDUM A: | PRELIMINARY MATLAB CODE FOR EDA | 171 |

|-------------|---------------------------------|-----|

| ADDENDUM B: | DETAILED FIGURES OF THE LAYOUT  | 177 |

| ADDENDIM C  | DATASHEET OF THE LNA            | 182 |

# LIST OF ABBREVIATIONS

ADE Analog Design Environment

ARJ Africa Research Journal

BEOL Back end of line

BGA Ball grid array

BiCMOS Bipolar and CMOS

BJT Bipolar junction transistor

CMOS Complementary metal oxide semiconductor

CSIR Council for scientific and industrial research

DC Direct current

DPSS Defence, peace, safety and security

DUT Device under test

EDA Electronic design automation

ENR Excess noise ratio

ESR Equivalent series resistance

FET Field effect transistor

FOM Figure of merit

GaAs Gallium arsenide

GBP Gain-bandwidth product

HA Hyper abrupt

HBT Heterojunction bipolar transistor

HICUM High current model

HIT-kit High performance interface tool kit

IC Integrated circuit

IF Impact factor

IIP3 Third order input intermodulation product

InP Indium phosphate

I/O Input / output

IMN Input matching network

ISI Institute for Scientific Information

LNA Low noise amplifier

LVS Layout versus schematic

MDS Minimum detectable signal

MIM Metal-insulator-metal

MOS Metal-oxide-semiconductor

MOSIS MOS implementation service

MEP MOSIS educational program

MPW Multi-project wafer

NDA Non-disclosure agreement

NF Noise figure

PA Power amplifier

PCB Printed circuit board

PDK Process design kit

PSD Power spectral density

QFN Quad flat no-lead (package)

RF Radio frequency

SHF Super high frequency

SiGe Silicon-germanium

SPICE Simulation program with integrated circuit emphasis

UWB Ultra-wideband

VBIC Vertical bipolar inter-company model

# **CHAPTER 1: INTRODUCTION**

The research question addressed in this thesis is whether a combined LC-ladder and capacitive shunt-shunt feedback matching network can be used successfully in wideband low noise amplifier (LNA) implementations, especially with improved performance compared to current LNA implementations in literature.

#### 1.1 BACKGROUND TO THE RESEARCH

In wireless receiver modules the first subsystem is usually a LNA designed to provide sufficient amplification for subsequent stages while adding as little noise as possible. The ability of a design to meet this objective is quantified in the noise factor of the amplifier which is defined as the ratio of the signal-to-noise ratio at the output of the amplifier to the signal-to-noise ratio at the input. It is well known that the first amplification stage dominates the total noise figure (NF) of the system [1] and thus the noise optimization of this first stage is critical. In general the important characteristics of low noise amplifiers are: low noise figure, good input matching, sufficient flat gain over a required frequency band, good linearity and reasonable power consumption.

As applications move to higher frequencies new design challenges are introduced. At high frequencies with wide frequency bands the noise performance of silicon bipolar junction transistors (BJT) are no longer satisfactory. Traditionally III-V compounds such as GaAs or InP were used in high speed applications as they are capable of achieving high unity gain frequencies, albeit at a much higher fabrication cost than that of silicon processes [2]. III-V compound devices require high supply current to achieve this high speed performance though, which makes their usage less desirable. Although the optimal noise performance and fabrication cost of GaAs and InP devices are comparable to that of silicon-germanium (SiGe) processes, the SiGe heterojunction bipolar transistors (HBT) have higher associated gain in amplifiers designed for minimum noise figure [3].

The increased availability of SiGe processes has positioned it as an important alternative to III-V compounds and has led to the use of SiGe HBTs in many high frequency applications. One of the major reasons for the success of SiGe HBTs in wireless applications is its very low noise capability [4] due to very high beta as well as a small base spreading resistance due to aggressive lateral and vertical scaling. In addition, HBTs

are high speed devices with unity gain frequencies above 200 GHz in certain processes making it an attractive choice for amplifier design at high frequencies. Since the SiGe fabrication process is an extension of the CMOS fabrication process to which extra processing steps are added it is also possible to integrate digital logic with efficient radio frequency (RF) circuits on the same die.

It has been shown that the input impedance matching plays an important role in achieving minimum noise figure and that an optimal source impedance exists for achieving the best noise performance [5]. This impedance is usually different than for maximum power transfer. LNA design entails achieving a low noise figure and usually optimal noise matching for a first amplifier stage. The obvious trade-off between minimum noise and maximum available gain has sparked much research interest into achieving a simultaneous optimal noise and power match. A traditional approach is the use of shunt-shunt feedback to modify the amplifier input impedance achieving such a simultaneous match [6], [7]. This also provides wide band operation. Emitter scaling is also a very common method used to modify the optimal source resistance of a transistor which could then be set equal to the characteristic impedance of the system [8], [9] achieving a simultaneous match in narrowband applications.

The LNA configurations mentioned above often employ inductive input matching or emitter degeneration. Through process scaling and lower inductor values required at high frequencies, the use of on-chip passive inductors have become common in integrated RF applications; however, these on-chip inductors suffer from low quality factor (Q-factor) due to the high permittivity of silicon dioxide which has a relative permittivity of 3.9. Although active inductors increase the noise figure of an amplifier they offer an important alternative for achieving a high Q-factor and reducing chip size and have been used in low noise amplifiers with good results [10].

At present narrowband techniques are often applied directly to wideband LNA implementations and as such good performance over the entire frequency band is often not achieved. This emphasizes the need for novel wideband LNA topologies capable of achieving good and relatively constant performance over the entire band of interest.

# 1.2 HYPOTHESIS AND RESEARCH QUESTIONS

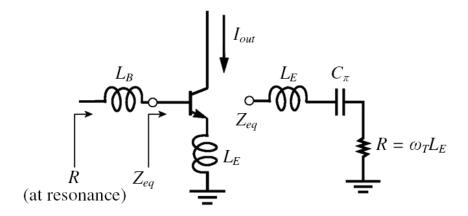

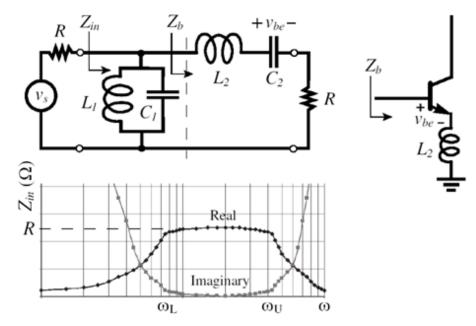

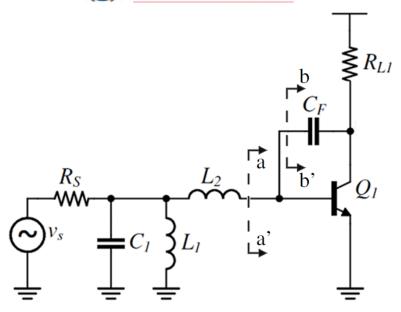

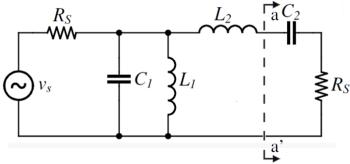

Use of the LC-ladder input matching network has been shown as an effective means of achieving an arbitrary wide conjugate input impedance match and has been implemented in conjunction with the emitter degeneration technique [11]. This configuration has the shortcoming of introducing a pole at the lower frequency end, and this in turn requires an inductive load to equalize the voltage gain with the result that the final LNA requires four area consuming inductors. Due to the nature of the matching network a given lower corner frequency also fixes the collector current limiting the design decisions.

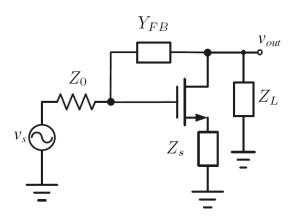

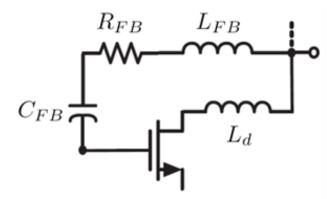

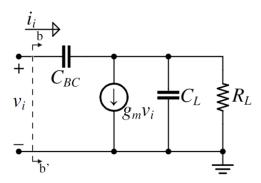

The shunt-shunt capacitive feedback technique has been shown capable of synthesizing an equivalent series RC network and used effectively in the design of a LNA for the ultra-wideband (UWB) [12]. This is however a narrowband configuration and is not ideal for wideband implementation.

From the above, the following hypothesis was formulated:

If a fourth order LC-ladder filter can be used to realize input matching over an arbitrary frequency band, and a shunt-shunt capacitive feedback common-emitter configuration can be modelled as an equivalent series RC circuit, then a combination of these two circuits can be used as a wideband LNA overcoming selected shortcomings of current LNAs in literature.

To prove the hypothesis the following research questions must be addressed:

- Can it be proven through mathematical modelling that the proposed configuration is capable of wideband matching and low noise operation?

- Does this configuration avoid introducing a pole at the lower corner frequency?

- Can the inductor count be reduced compared to the LC-ladder and inductive emitter degeneration configuration?

- Does this configuration decouple the collector current from the lower corner frequency value?

### 1.3 JUSTIFICATION FOR THE RESEARCH

The goal of most wireless communication systems is achieving a high data rate. Even with the vast improvements allowed by the coding schemes employed in wireless communications today the signal-to-noise ratio remains a fundamental limiting factor of data throughput. Since the LNA is the determining factor in the noise figure of a system any improvement in noise figure is of great importance. Good linearity, which also limits the data rate, should however be maintained as the high power consumption required to compensate for poor linearity is undesirable, especially in battery-powered devices.

Table 1.1 lists the specifications of some related work found in literature indicating the state-of-the-art LNA performance. The simulated and measured results of designs done in this research using the proposed LC-ladder and capacitive shunt-shunt feedback configuration are also shown. For the same input matching and gain specification a lower NF and power consumption is achieved compared to most of the listed LNAs at the cost of reduced IIP3. This makes the proposed configuration especially suited to applications were low noise is very important and linearity only a secondary concern. Furthermore it is suited to very wideband designs such as the designed LNA operating from 0.8 to 18 GHz [13].

The desired specifications of the LNA that was designed in this research were defined towards the implementation of a receiver that is able to operate at multiple 800 MHz bands over the 1 GHz to 18 GHz range. A configuration capable of achieving such a wide band can however also be used for software defined radio (SDR) applications [14], [15] in general, or applied directly to smaller application specific sub-bands.

Since there is an abundance of bandwidth available in the unlicensed part of the mm-wave frequency band (57-64 GHz) which can be leveraged against power consumption in mobile devices [16], the investigation of a design at these frequencies is also warranted.

Although this research was done towards bipolar transistor LNA implementations the simple high frequency small-signal transistor model was used in the derivation of the mathematical model with  $r_{\pi}$  neglected in the frequency range of operation. The described techniques can therefore also be easily applied to field effect transistors (FET) with the only required change being the substitution of the appropriate equivalent noise source equations and transconductance equation for FETs.

Table 1.1. Simulated and measured results of the LNAs designed for this research using the proposed topology compared to state-of-the-art measured LNA results from literature.

| Ref.         | Impact<br>factor (IF) | 5 year<br>IF | Technique                                                             | Technology $/f_T$        | BW<br>[GHz] | S <sub>11</sub> [dB] | S <sub>21</sub> [dB] | NF<br>[dB]       | IIP3 [dBm]                 | P<br>[mW] | Area<br>[mm²] |

|--------------|-----------------------|--------------|-----------------------------------------------------------------------|--------------------------|-------------|----------------------|----------------------|------------------|----------------------------|-----------|---------------|

| This work    | -                     | -            | LC-ladder & capacitive-feedback (simulated)                           | 0.13 μm (8HP) / 200 GHz  | 1-18        | < -10                | 21.4                 | 1.7-3.6          | -22.6 @ 4.2 GHz            | 12.75     | -             |

| This<br>work | -                     | -            | LC-ladder & capacitive-feedback (optimized for linearity) (simulated) | 0.13 μm (8HP) / 200 GHz  | 1-18        | < -9.8               | 20                   | 2.2-3.9          | -14.5 @ 4.2 GHz            | 23.25     | -             |

| This<br>work | -                     | -            | LC-ladder & capacitive-feedback (simulated)                           | 0.18 μm (7WL) / 60 GHz   | 3-14        | < -10                | 20.7                 | 2.8-4.3          | -22.5 @ 6.5 GHz            | 14.22     | 0.4272        |

| This<br>work | -                     | -            | LC-ladder & capacitive-feedback (optimized for linearity) (simulated) | 0.18 μm (7WL) / 60 GHz   | 3-14        | < -9.7               | 20.1                 | 2.9-4.8          | -19.0 @ 6.5 GHz            | 33.3      | 0.4272        |

| This<br>work | -                     | -            | LC-ladder & capacitive-feedback (optimized for linearity) (measured)  | 0.18 μm (7WL) / 60 GHz   | 3-6         | < -9.7               | 11 <sup>†</sup>      | N/A <sup>‡</sup> | -22.0 ( P <sub>1dB</sub> ) | 33.3      | 0.4272        |

| [17]         | 3.4661 <sup>1</sup>   | 4.037        | Inductive emitter degeneration                                        | 0.6 μm CMOS              | 1.5         | < -10                | 22                   | 3.5              | -9.3 @ 1.5 GHz             | 30        | -             |

| [11]         | 3.4661 <sup>1</sup>   | 4.037        | LC-ladder & inductive-emitter degeneration                            | 0.18 μm (Jazz semicond.) | 3-10        | < -9                 | 21                   | 2.5-4.5          | -5.5 @ 3.4 GHz             | 30        | 1.35*         |

| [6]          | Proc.                 | Proc.        | Frequency controlled shunt-shunt feedback                             | 0.18 μm CMOS             | 3-10        | < -13                | 8                    | 3.5-4.4          | -                          | 18.5      | -             |

| [18]         | 2.7111 <sup>1</sup>   | 3.187        | Resistive feedback                                                    | 0.18 μm / 150 GHz        | 3–10        | < -10                | 20                   | 3.4-4.7          | -17 @ 3.5 GHz              | 42.5      | 0.18          |

| [19]         | 3.4661 <sup>1</sup>   | 4.037        | Inductive emitter degeneration                                        | 0.18 μm CMOS             | 3-10        | < -10                | 9.3                  | 4-7              | -6.7 @ 6 GHz               | 9         | 1.1*          |

| [20]         | Proc.                 | Proc.        | Emitter degeneration with added BE-capacitance                        | 0.18 μm / 120 GHz        | 0.1-13      | < -7.2               | 20.3                 | 1.8-3.1          | 2.1 @ 6 GHz                | 26        | 0.72          |

| [12]         | 2.7111 <sup>1</sup>   | 3.187        | Shunt-shunt capacitive-feedback                                       | 0.35 μm SiGe BiCMOS      | 3-14        | < -9                 | 23                   | 2.5-5.8          | -17 @ 5 GHz                | 25.8      | 0.2223        |

| [21]         | $1.13^{2}$            | -            | Parallel LC resonators & emitter degeneration                         | 0.13 μm CMOS             | 6.8-8.8     | < -10                | 29.5                 | 4.0-5.2          | -8.5 @ 7.7 GHz             | 15        | 0.4           |

| [9]          | 2.3021 <sup>1</sup>   | 2.533        | Inductive emitter degeneration                                        | 0.13 μm (8HP) / 200 GHz  | 28-40       | < -10                | 23.5                 | 2.3-3.2          | -19.5 @ 35 GHz             | 11        | 0.09          |

| [22]         | Proc.                 | Proc.        | Multiple resistive feedback paths                                     | 0.35 μm (Jazz semicond.) | 3-10        | < -10                | 21                   | 4.0-4.9          | -                          | -         | -             |

| [23]         | Proc.                 | Proc.        | Diff. emitter-coupled pair with emitter followers                     | 0.8 μm                   | 3.1-10.6    | < -7                 | 19.9                 | 2.1-2.9          | -17.5 @ 7 GHz              | 77        | 0.14*         |

| [24]         | Proc.                 | Proc.        | Three stage with CE and resistive feedback                            | 0.18 μm / 120 GHz        | 5.2-15.8    | < -10                | 19.1                 | 4.2-5.2          | -6.47 @ 13 GHz             | 116       | 0.0954*       |

<sup>1.</sup> ISI web of knowledge

† From 3 GHz to 10 GHz

<sup>2.</sup> https://www.researchgate.net/journal/1549-7747\_Circuits\_and\_Systems\_II:\_Express\_Briefs,\_IEEE\_Transactions\_on

<sup>‡</sup> NF measurement was not feasible due to the low gain

\* Including bond pads

### 1.4 RESEARCH METHODOLOGY

Various LNA configurations were investigated in a thorough literature study to find the most appropriate option for wideband implementations. The shortcomings of many configurations were subsequently identified and narrowband configurations were deemed unsuitable for the design. A new LNA topology which is a combination of the LC-ladder input matching network (IMN) and capacitive feedback topology was then proposed to overcome many of these shortcomings [25].

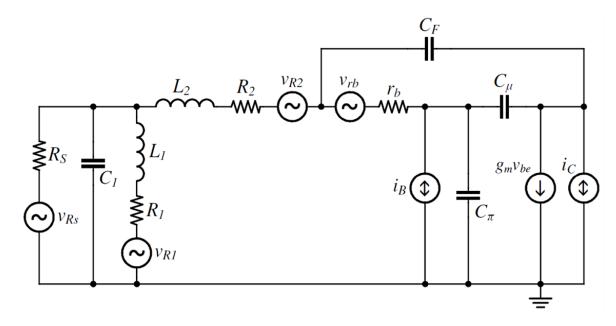

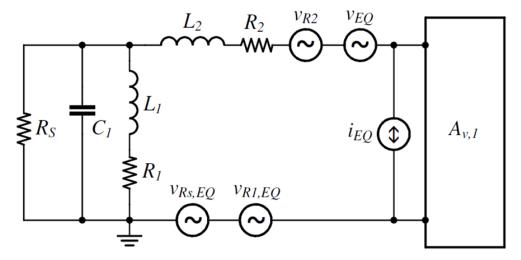

A complete mathematical model which characterizes this configuration was subsequently derived and MATLAB was used to model the LNA performance. The derivation was done using an RF analogue approach. This mathematical model was also used to define compact design equations for a first order design and a process for optimizing the circuit for minimum NF was determined.

The design equations were used in the design of wideband LNAs using two different IBM SiGe BiCMOS processes, namely the 0.18  $\mu$ m 7WL process and the 0.13  $\mu$ m 8HP process with  $f_T$  of 60 GHz and 200 GHz respectively. Selected process parameters are discussed in Chapter 3. The calculated results were verified through simulations using Cadence Virtuoso and the high performance interface tool kits (HIT-kits) supplied by IBM.

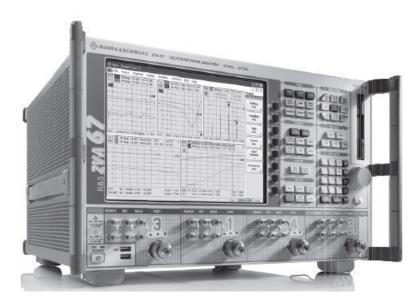

Finally, after the LNA was optimized further using simulations it was submitted for fabrication in the IBM 7WL 0.18  $\mu$ m SiGe BiCMOS process. The dies were packaged in quad flat no-lead (QFN) packages and soldered onto a test printed circuit board (PCB). The noise figure, gain, input reflection coefficient and  $P_{1dB}$  of one prototype was measured using a Rohde & Schwarz ZVA40 Vector Network Analyzer and an Agilent E4440A PSA spectrum analyzer.

To verify the accuracy of the initial calculated results and subsequent simulations, the measured performance was compared to results of simulations which included the package parasitics.

### 1.5 DELIMITATIONS OF SCOPE AND KEY ASSUMPTIONS

In the derivation of the mathematical model of the LNA the simple high frequency small-signal transistor model was used to derive equations that could be easily interpreted. Inductors were also viewed simply as a series inductance and parasitic resistance. This is however sufficient for a first order design and in fact agrees well with simulations done using complex transistor models despite the simplicity of this approach.

In the circuit simulations parameterized cells (p-cells) were used which include the device parasitics present in the circuit. The interconnect capacitance was however not included in simulation and may cause slight deviations in the expected performance.

During the experimental testing the characteristics of only a single prototype was measured due to the shortcomings of the test PCB discussed in Section 6.7. Therefore the presented results merely offers a proof of concept, but more rigorous testing should be performed to fully characterize the LNA performance based on a larger sample.

The noise figure was measured at room temperature and not at 290 °K as specified in the definition of NF [1].

#### 1.6 CONTRIBUTION TO THE FIELD

A new LNA configuration, namely the LC-ladder and capacitive shunt-shunt feedback topology, has been proposed for use in wideband applications up to 20 GHz. A detailed list of the resulting contributions to the body of knowledge is given here.

- This configuration has been demonstrated successfully through the design and simulation of a 1-18 GHz LNA achieving a simulated 21.4 dB gain and  $S_{II} < -10$  dB with a minimum NF of 1.7 dB increasing to a maximum of 3.6 dB at the upper corner frequency. The power consumption of this LNA is only 12.7 mW and it occupies a chip area of 0.43 mm<sup>2</sup> including three on-chip inductors.

- A second LNA with improved linearity from -22.6 dBm IIP3 to -14.5 dBm is also presented and achieves 20 dB gain with a minimum and maximum NF of 2.2 dB and 3.9 dB respectively, and power consumption of 23.3 mW.

- This proposed technique followed a thorough literature study on existing LNA configurations which were analyzed to find the performance and shortcomings of each as now given and compared in Chapter 2.

- o It became apparent that there is a need for wideband LNA configurations that can be applied directly to wideband implementations as is the case with the proposed configuration which is a true wideband topology instead of, as is often done [12], [20], adapting more well known narrowband techniques to wideband applications leading to undesirable and, as proven in this work, to a large extent unnecessary trade-offs between input matching, noise and gain performance.

- Many wideband configurations that do exist do not optimize all LNA performance measures simultaneously, as in [6] for instance where high NF and low gain negates the advantages of a wideband conjugate match. It has been shown that minimizing NF and maximizing gain in the LC-ladder and capacitive shunt-shunt feedback topology can always be obtained simultaneously.

- A large number of on-chip inductors (three being typical in narrowband and four in wideband implementations [9], [6], [11]) usually characterizes topologies in the body of knowledge. The LC-ladder and capacitive feedback topology however requires only a maximum of three inductors when operating close to the limits of the technology node where the first stage output pole could fall within the band of interest. When this is not the case, the first amplifier stage produces constant gain with frequency and the number of on-chip inductors could be reduced to only two.

- o In some cases a pole is introduced in the frequency response by the IMN, which could be at the lower corner frequency [11] requiring an inductive load to equalize the voltage gain, this however is not the case with the proposed technique in which there is no such intrinsic pole introduce by the IMN.

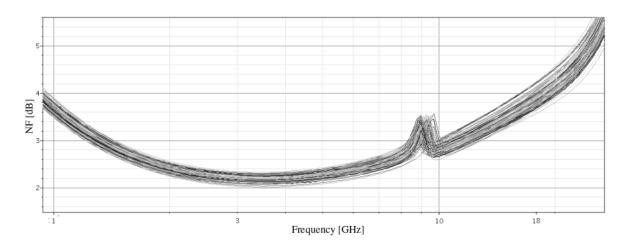

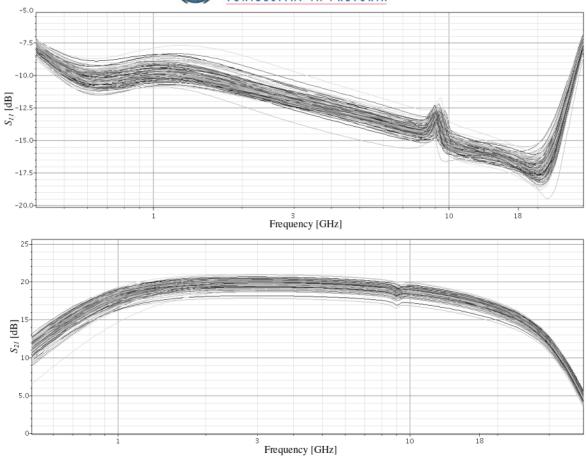

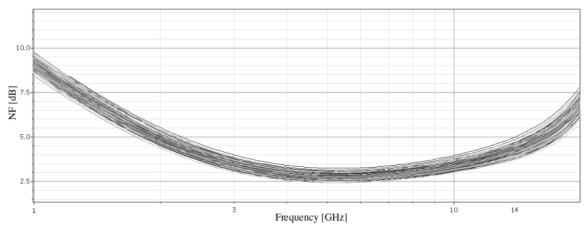

- A Monte Carlo analysis and temperature sweep showed that this is a very robust configuration, especially when the feedback techniques proposed to improve linearity are applied.

- O The gain of the LNA varies by only 2.4 dB on average and between 18.8 dB and 21.4 dB in the mid-band. Although  $S_{11}$  also varies by 2 dB it remains within specification over most of the operating bandwidth, and NF varies by as little as 0.3 dB over most of the band with the maximum NF in extreme cases being 4.25 dB.

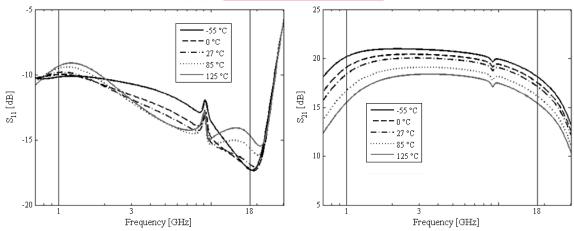

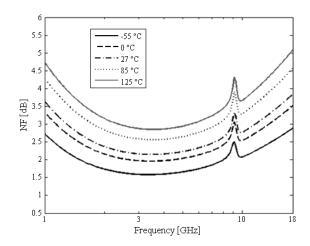

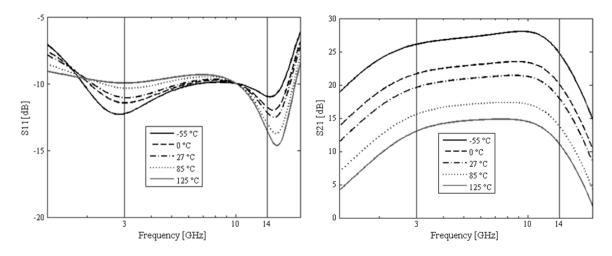

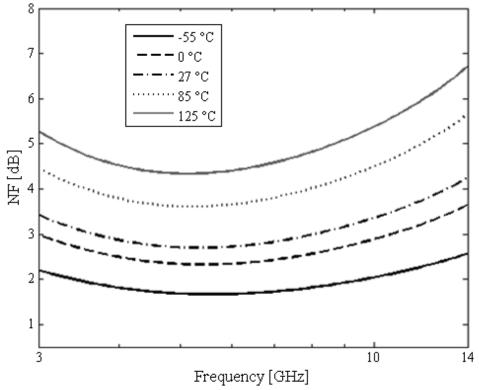

- A sweep over the military specification temperature range revealed only a

2.5 dB variation in gain and a 2 dB variation in NF from -55 °C to 125 °C.

- A first order mathematical model has been derived to characterize the proposed topology, and this model has also been used to derive compact design equations for such a LNA. The most novel contribution in this model is the derivation of the NF equation, in which the individual noise source powers occur as individual terms in the equation from which the dominant contribution could be determined, and strategies for optimization deduced. This allowed for a more focussed procedure for noise optimization.

- The model is suitable for use in electronic design automation (EDA) software that determines component values for a LNA based on a specified frequency range, gain and maximum NF. Preliminary MATLAB source code for such software used successfully throughout this research is given in Appendix A; and as such the design-for-design of this configuration has also been done. At the moment only a complete derivation for IIP3 is lacking and suggestions regarding this have been made for future work. Implementation of such EDA software will also ensure the repeatability of this novel design procedure and effectively archive it for future use.

- Some limitations of this topology have been identified and were also demonstrated in a 60 GHz LNA design where the wideband nature of the configuration proved redundant and the design theory did not meet with the expected results due to second order effects.

- It was noted that this topology can be used to push a transistor of a given technology node to its limits and then allows for trading gain, NF, bandwidth and power consumption during the design process. This trade-off has been quantified in the noise figure versus bandwidth trade-off equation which forms part of the model.

- The accuracy of the model has been verified through simulations in Cadence Virtuoso using the IBM HIT-kits, and LNAs of two versions of this topology have been submitted for fabrication. The measured performance from these LNAs conform well to the expected results from simulations when the shortcomings of the PCB and test procedure are taken into account which further validates this topology as a candidate for wideband LNA implementations.

#### 1.7 PUBLICATIONS LEADING FROM THIS RESEARCH

The following peer reviewed conference articles have been published and presented by the author as part of his research activities:

- M. Weststrate and S. Sinha, "Noise optimization of a wideband capacitive shunt-shunt feedback LNA design suitable for software-defined radio," *Proc. of the IEEE International Conference on Electronics, Circuits and Systems (ICECS)*, Hammamet, 13-16 December 2009.

- M. Weststrate, S. Sinha and D. Neculoiu, "Limitations of a LC-ladder and Capacitive Feedback LNA and Scaling to mm-Wave Frequencies," *Proc. of the IEEE CAS 2009 (International Semiconductor Conference)*, Sinaia, pp. 315-318, 12-14 October 2009.

- M. Weststrate and S. Sinha, "Analysis of a Low Noise Amplifier with LC-Ladder Matching and Capacitive Shunt-Shunt Feedback," *Proc. of IEEE Africon* 2009, Nairobi, 23-25 September 2009.

- M. Weststrate and S. Sinha, "Mathematical Analysis of Input Matching Techniques

With Application in Wide-band LNA Design," *Proc. of the South African*Conference on Semi- and Superconductor Technology (SACSST), Stellenbosch,

pp. 128-132, 8-9 April 2009.

- D. Foty, S. Sinha, M. Weststrate, C. Coetzee, A.H. Uys, and E. Sibanda, "mm-Wave Radio Communications Systems: The Quest Continues," *Proc. of the 3rd International Radio Electronics Forum (IREF) on "Applied Radio Electronics. The State and Prospects of Development,"* Kharkov, pp. 14-17, 22-24 October 2008 (Invited Paper).

Presentations were also given by the author at both the 9<sup>th</sup> and 10<sup>th</sup> European high current model (HICUM) workshop. At the workshop held in Würzburg, Germany on 23 October 2009 the presentation entitled *Design and Simulation of Wideband LNAs up to 60 GHz* was given and at the workshop in Dresden, Germany on 24 September 2010 a presentation entitled *Sensitivity of LNA performance characteristics to individual HICUM parameters*.

The following peer reviewed journal articles submitted by the author as part of his research activities have been published. All journals except the ARJ are accredited by the Institute for Scientific Information (ISI). The ARJ is, however, a fully peer-reviewed accredited journal – Dept. of Higher Education and Training (DoHET), Ministry of Education, South Africa:

- M. Weststrate and S. Sinha, "Mathematical Modelling of the LC-Ladder and Capacitive Shunt-Shunt Feedback LNA Topology," SAIEE Africa Research Journal (ARJ), vol. 100, pp. 72-78, September 2009.

- M. Weststrate, S. Sinha and D. Neculoiu, "Design Trade-offs and Limitations of a LC-Ladder and Capacitive Feedback LNA and its Application at mm-Wave Frequencies," *Romanian Journal of Information Science and Technology* (ROMJIST), vol. 13, no. 1, pp. 98-107, 2010.

- M. Weststrate and S. Sinha, "Wideband LNA design using the LC-Ladder and Capacitive Shunt-Shunt Feedback Topology," *Microwave and Optical Technology* Letters, accepted for publication in July 2011.

The following article by the author has also been submitted and conditionally accepted in an ISI accredited peer reviewed journal:

M. Weststrate, A. Mukherjee, S. Sinha and M. Schröter, "Sensitivity of narrowand wideband LNA performance characteristics to individual HICUM parameters," submitted to the *International Journal of Electronics, submitted in March 2011*, resubmitted in May 2011.

#### 1.8 OUTLINE OF THE THESIS

Chapter 1 serves as an introduction to the thesis providing a brief background to the research research research. The hypothesis is stated and the justification for the research is

provided. A summary of the research methodology as well as the contribution of the research to the body of knowledge is also given with a list of publications leading from this research.

Chapter 2 provides a review of the literature pertaining to this research topic. A brief general discussion on the noise sources in transistors is given, followed by the effects of these sources in HBT amplifier circuits, as well as the characteristics of HBTs making them suitable for low noise design. A general discussion on input matching techniques is presented after which various matching schemes found in present literature are discussed with comments on the advantages and disadvantages of each. These include the well known inductive emitter degeneration technique which by way of emitter scaling used to adjust the optimal noise resistance can achieve a simultaneous optimal noise and conjugate input match. Also some techniques using feedback to adjust the input impedance and topologies with more complex input matching networks. The discussion involves a comparison of the gain, noise and linearity of these configurations. Subsequently the use of on-chip inductors, as well as the trade-offs and characteristics of active inductors are presented. This chapter concludes with the proposal of a new LNA topology combining the LC-ladder and capacitive feedback approach to provide wideband matching and good noise performance.

Chapter 3 describes the SiGe transistor processes used in the wideband LNA designs intended to verify the soundness of the mathematical model, and also the transistor models used in simulations.

Chapter 4 discusses the derivation of the mathematical model of the proposed amplifier configuration. Equations for input matching, gain and noise figure are derived and these are also rewritten to provide compact design equations. An approximation for the linearity and quantification of certain design trade-offs are also presented. Finally the design steps are given in a way that can potentially be used in a software package to automate the design process.

Chapter 5 describes the design and simulation of three different amplifiers. The first is a design for the 1 GHz to 18 GHz range using the IBM 8HP  $0.13~\mu m$  process. The second is a design at 60 GHz using the same process and finally the amplifier to be fabricated using the IBM 7WL  $0.18~\mu m$  process is presented over the 3 GHz to 14 GHz frequency band.

The layouts of the circuits that were fabricated are presented in Chapter 6 with some discussion as well as the packaging choices and its limitations. The schematic of a test PCB for the biasing and measurement of the packaged devices is also given.

The measurement setup and test procedures are discussed in Chapter 7. The experimental results are also presented with some comments on its comparison with the expected results from simulations.

The conclusion, critical evaluation of the work and potential areas for future research are provided in Chapter 8.

# **CHAPTER 2: LITERATURE REVIEW**

### 2.1 INTRODUCTION

The objective in LNA design is to achieve sufficient gain over a required frequency band while maintaining a very low noise figure. This is crucial for the first amplification stage since it dominates the NF of the system as a whole as shown in

$$F = F_1 + \frac{F_2 - 1}{G_{A1}} + \frac{F_3 - 1}{G_{A1}G_{A2}} + \frac{F_4 - 1}{G_{A1}G_{A2}G_{A3}} + \cdots,$$

(2.1)

where F is the noise factor,  $G_A$  the associated gain and the subscripts indicate successive amplifier stages [1]. The linearity of the amplifier as well as power consumption are also important specifications and thus limitations that the design must contend with. This chapter provides a review of the literature pertaining to low noise amplifier design and achieving these design objectives.

The increased availability of silicon-germanium (SiGe) processes has led to the use of SiGe HBT in many high frequency applications. One of the major reasons for the success of the SiGe HBTs in wireless applications is its low noise capability [4] and high speed, which also makes it attractive for low noise amplifier design; thus the use of HBTs is elaborated. Inductors are also important in RF design and the availability of on-chip inductors have allowed for complete integration of RF circuits. However, passive on-chip inductors are costly in terms of chip area and suffer from a low Q-factor and thus various inductor types and optimization techniques are briefly discussed, as well as the possibility of employing active inductors to avoid these shortcomings at the cost of higher noise.

The first part of this chapter discusses the noise sources present in transistors, followed by the effect of these sources in HBT amplifier circuits. The characteristics of HBTs making them suitable for low noise design are discussed, as well as important linearity considerations. Various input matching techniques are then presented, including a detailed discussion of the very common use of emitter scaling to adjust the optimal noise resistance for a simultaneous optimal noise and power input match.

### 2.2 NOISE IN AMPLIFIER CIRCUITS

There are five types of well known noise sources present in circuits with active and passive devices. These are [26]: Thermal noise, shot noise, Flicker or 1/f noise, burst noise and avalanche noise.

Thermal noise occurs due to the random thermal motion of electrons. For a given circuit component with a resistance R the average thermal noise voltage is given by

$$\overline{v^2} = 4kTR\Delta f , \qquad (2.2a)$$

and the equivalent noise current by

$$\overline{i^2} = \frac{4kT}{R} \Delta f , \qquad (2.2b)$$

where k = 13.8E-24 J/K is Boltzmann's constant,  $\Delta f$  is the amplifier noise bandwidth and T is absolute temperature. Since the standard definition of noise figure is at T = 290 °K [1] this will be the assumed temperature throughout this thesis unless otherwise stated. Since the thermal noise spectrum is frequency independent within the noise bandwidth it contributes to amplifier white noise. The thermal noise voltage or current is minimized for very small or very large values of R respectively.

Shot noise is associated with direct current (DC) flow through a p-n junction and is always present in diodes, MOSFETs and bipolar transistors. In a forward biased p-n junction the forward current exists as a result of holes and electrons gaining enough energy to cross the electric field present in the depletion region. Thus the passage of each carrier across the junction is a random event occurring when a specific carrier has sufficient energy and velocity directed toward the junction and the apparent steady forward current is in fact composed of a large number of random independent current pulses [26]. The fluctuations that occur in this current are called shot noise and is usually specified in terms of its mean-square variation about the average value as

$$\overline{i^2} = 2qI_D \Delta f , \qquad (2.3)$$

where q is the electron charge,  $I_D$  the average forward current and  $\Delta f$  the amplifier noise bandwidth. The spectrum of shot noise is also frequency independent and thus contributes to white noise.

Flicker noise and burst noise are both frequency dependent and occur at lower frequencies. Flicker noise is caused mainly by traps associated with contamination and crystal defects which capture and release carriers in a random fashion. The time constants associated with this process give rise to a noise signal with energy concentrated at low frequencies [26]. Burst noise is not fully understood but does show some relation to the presence of heavy-metal ion contamination. Since the dependence of the noise spectral density on frequency for flicker noise is 1/f (pink noise) and that of burst noise  $1/f^2$  (brown noise) above a cut-off frequency, these noise sources are not important in super high frequency (SHF) circuits, with the exception of voltage controlled oscillators where flicker noise can be up-converted as phase noise [4].

Avalanche noise occurs in reverse biased p-n junctions where electrons in the depletion region acquire sufficient energy to create electron-hole pairs by colliding with silicon atoms. This creates large noise spikes and generally dominates all other noise sources when present. The noise magnitude is proportional to the DC flow [26]. This source of noise can be minimized by ensuring the reverse bias voltage is small enough to limit the occurrence of avalanche breakdown.

In summary, for high frequency amplifier circuits, assuming reverse bias is sufficiently low such that avalanche breakdown becomes negligible, the noise sources to contend with are thermal noise and shot noise.

## 2.3 NOISE IN HBT AMPLIFIERS

The LNA noise figure is tied to the physical noise sources in the transistor which are, for SiGe HBTs, the shot noise associated with the base and collector DC as well as the thermal noise of the base resistance  $(r_b)$  [4].

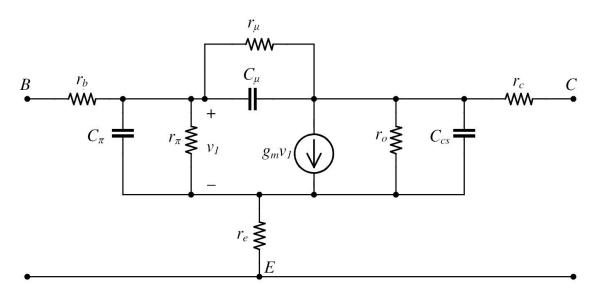

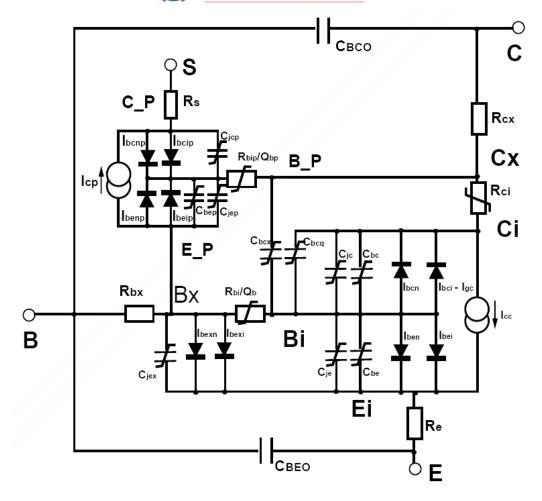

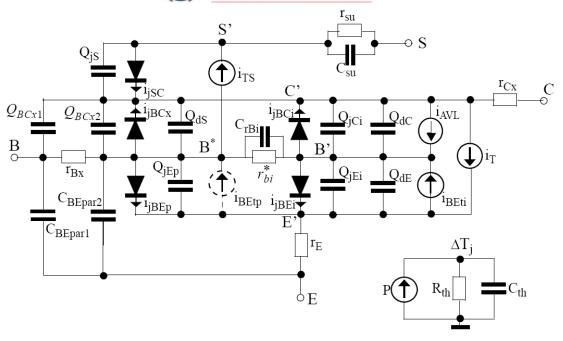

Although many virtual resistors such as the output resistance of a transistor are included in the complete transistor model shown in Figure 2.1, these resistances, being virtual, do not contribute to the transistor thermal noise. The actual resistances present in a transistor are the base, emitter and collector series resistances which exist due to the resistivity of the p- and n-material. In SiGe HBTs the emitter and collector resistances can usually be neglected since the emitter resistance is very small and the collector resistance thermal noise is reduced by the gain of the transistor when referred back to the input. This makes the base resistance the most important contributor of thermal noise. Since this noise is applied at the base of the transistor it is not reduced by the amplifier voltage gain and forms a major limitation on minimum NF.

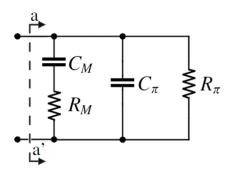

Figure 2.1. Complete bipolar transistor small-signal equivalent circuit.

As discussed in Section 2.2 shot noise is generated by DC flowing in forward [26] biased p-n junctions. In bipolar transistors both the base and collector currents introduce shot noise at the base-emitter junction. From the base majority carrier holes cross the base-emitter junction to form the base current and majority carrier electrons in the emitter cross the junction to form the collector current in *npn*-transistors. At the reverse biased collector-base junction the electric field causes a drift process which simply transports the electrons from the base into the collector without adding additional shot noise. The base transit time ( $\tau_F$ ) of the electrons across the base changes the correlation between the base and collector current noise in the common emitter configuration [4], however it is feasible to neglect this transit time (effectively assuming the noise is generated in the BC-junction) at frequencies much lower than  $f_T/2$  [8]. In such cases the correlation admittance seen by the equivalent input noise voltage and current generators is only due to the collector current noise component (see (2.9) and (2.10) in Section 2.3.1) and equal to  $Y_{II}$  of the amplifier two-port.

### 2.3.1 Common-emitter amplifier noise and gain parameters

SHF LNAs are often implemented as narrowband amplifiers using active devices characterised by *S*-parameters and tuned with distributed passive structures. An alternative design technique is a RF analogue approach combining lumped passive devices with the transistor model to achieve the desired functionality [27].

The noise optimization methods of these approaches differ significantly. With the lumped element method the equivalent circuit of the transistor with the noise sources described in the previous section are considered with the elements comprising the matching networks and their noise sources in order to define an overall equation for the noise figure indicating which component values could be optimized. With a distributed design the minimum NF of a transistor (NF<sub>min</sub>) is quantified and the deviation of the source impedance from the optimal noise match determines the final NF of the system. The following discussion assumes the latter approach.

Starting with the equations for a two-port's noise parameters in terms of the power spectral density (PSD) of the equivalent noise current and voltage as well as their correlation as given in [5], it can be shown that when written in terms of the intrinsic transistor parameters, the noise parameters of a common emitter amplifier are given by equations (2.4) through (2.7) [4].

$$R_n = r_b + \frac{1}{2g_m} \tag{2.4}$$

$$G_{s,opt} = \sqrt{\frac{g_m}{2R_n} \frac{1}{\beta} + \frac{(\omega C_i)^2}{2g_m R_n} \left(1 - \frac{1}{2g_m R_n}\right)}$$

(2.5)

$$B_{s,opt} = -\frac{\omega C_i}{2g_m R_n} \tag{2.6}$$

$$NF_{\min} = 1 + \frac{1}{\beta} + \sqrt{\frac{2g_m R_n}{\beta} + \frac{2R_n (\omega C_i)^2}{g_m} \left(1 - \frac{1}{2g_m R_n}\right)}$$

(2.7)

$R_n$  is the noise resistance,  $G_{s,opt} + jB_{s,opt}$  is the optimal source admittance and  $NF_{min}$  the minimum noise figure achieved when optimal noise input matching is used. Equation (2.7) can also be written in the more practically useful form [8]

$$NF_{\min} = 1 + \frac{n}{\beta_0} + \frac{f}{f_T} \sqrt{\frac{2I_C}{V_T} (r_E + r_B) \left(\frac{f_T^2}{\beta_0 f^2}\right) + \frac{n^2 f_T^2}{\beta_0 f^2}},$$

(2.8)

where n is the collector current ideality factor, approximately equal to one, except under high current injection bias when its value can exceed 1.2. Equation (2.8) shows that the absolute minimum attainable noise figure is fixed for a specific process through the first and second terms. The third term indicates that  $NF_{min}$  is frequency dependent. It is apparent that at a given collector current the noise is primarily a function of four key parameters: the series resistances ( $r_b$  and  $r_e$ ), the unity gain frequency ( $f_T$ ), and the transistor common-emitter current gain ( $\beta$ ) [28].

The two terms inside the second square root term become equal at  $f = f_T / \sqrt{\beta}$  which defines the transition of  $NF_{min}$  from a white noise behaviour to becoming frequency dependent. Below this frequency  $NF_{min}$  is proportional to  $\sqrt{r_b/\beta}$  which together with the second term indicate the need for high  $\beta$  and low  $r_b$ . Above this corner frequency  $NF_{min}$  increases with a slope proportional to  $\sqrt{r_b}/f_T$  also making high  $f_T$  critical for achieving good noise performance. In this case  $\beta$  becomes irrelevant as long as it is sufficiently large (> ~50-100) [28].

When examined in terms of the physical noise sources in the transistor it can be seen that higher  $\beta$  reduces the base current ( $I_B$ ) and the referred collector current shot noise which decreases the PSD of the equivalent input noise current ( $S_i$ ) significantly as given by [29]

$$S_{i_n} = 2qI_B + \frac{2qI_C}{\beta^2} \,. \tag{2.9}$$

The frequency dependence of the noise current arises from the roll-off of  $\beta$  with frequency above  $f_b = f_T / \sqrt{\beta}$  [26]. Lowering  $r_b$  causes a drop in the PSD of the equivalent input noise voltage  $(S_v)$  given by [29]

$$S_{\nu_n} \approx 4kT \left(r_b + \frac{1}{2g_m}\right). \tag{2.10}$$

The dependence of NF on  $I_C$  is apparent from both (2.9) and (2.10) through  $g_m$ .

The associated gain  $(G_a)$  of an amplifier is the power gain that can be achieved when the input of an amplifier is noise matched in order to minimize NF. It has been shown that the associated gain for HBT amplifiers is given by [29], [30]

$$G_{a} = \frac{1}{\omega^{2} C_{bc} C_{i} r_{b}} \sqrt{\frac{g_{m} r_{b} + \frac{1}{2}}{2} \frac{g_{m}^{2}}{\beta} + \frac{(\omega C_{i})^{2}}{2} g_{m} r_{b}} . \tag{2.11}$$

It can be seen that increasing  $f_T$  by decreasing the input capacitance  $(C_i)$  serves to increase the gain in addition to improving noise performance. An increased  $\beta$  however decreases the associated gain since  $G_a$  is inversely proportional to the square-root of  $\beta$ . This is an important limitation since at low frequencies increasing  $\beta$  is the only means of reducing noise figure [4]. Although the base-collector capacitance  $(C_{bc})$  does not impact  $NF_{min}$  directly, it does affect  $G_a$  which indicates that, in addition to large  $f_T$ , a large  $f_{max}$  is also desirable and is defined as [31]

$$f_{\text{max}} = \sqrt{\frac{f_T}{8\pi r_b C_{bc}}} . \tag{2.12}$$

Finally it is seen that  $G_a$  increases with  $I_C$  through  $g_m$  indicating the need for a certain amount of  $I_C$  to have sufficient associated gain [30]. Equation (2.8) however shows that the NF also increases with  $g_m$  which implies a trade-off between NF and associated gain. To better quantify this trade-off the noise measure (M) which includes both the noise factor and associated gain in a single parameter is often used as a figure of merit (FOM) and is defined as [28]

$$M = \frac{F - 1}{1 - \frac{1}{G_a}}. (2.13)$$

## 2.3.2 Low noise capability of HBTs

The intrinsic properties of SiGe HBTs make them especially well suited for low noise design. The additional freedom offered by band-gap engineering allows SiGe HBTs to simultaneously achieve high  $\beta$ , a high  $f_T$  and low  $r_b$  all of which are important for noise performance as described in the preceding section. This is in contrast to Si BJTs where these requirements often result in limiting constraints where for example decreasing  $r_b$  by increasing the base doping causes a drop in  $\beta$  [30]. Through the addition of germanium to the base of the transistor the band-gap energy of the base material is reduced which allows for much higher doping while maintaining good emitter injection efficiency.

A review of four generations of IBM technology [28] reveals the improvements in noise performance through both scaling and structural enhancements. Vertical scaling of the base and collector has resulted in a rise in  $f_T$  from 47 GHz in 0.25  $\mu$ m technology to more than 200 GHz and even above 350 GHz in some 0.13  $\mu$ m processes. With the reduction of base width using a higher Ge mole fraction to maintain a constant total Ge content in the base also increases  $\beta$  [4]. As a result of lateral scaling which reduced the minimum emitter area,  $f_T$  vs.  $I_C$  characteristics have been shifted toward lower currents allowing successive generations to achieve higher  $f_T$  at any given  $I_C$  value. This is especially desirable since SiGe HBTs typically have the best noise performance at less than 20 % of the peak  $f_T$  or  $f_{max}$  current density and high-current-density performance may be traded for improved noise at lower current densities [28].

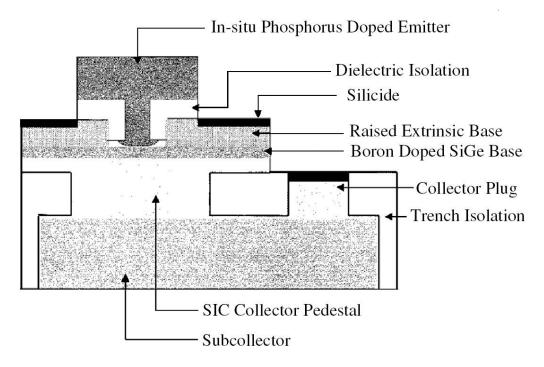

Lateral scaling has also reduced the contribution of the sheet resistance of the intrinsic base to the overall  $r_b$  as it is inversely proportional to the emitter width. Although  $r_b$  could be further reduced by higher doping of the extrinsic base this is seldom done in traditional structures since the higher doping tends to diffuse toward the collector pedestal which increases  $C_{bc}$  and thus reduces  $f_{max}$  and the power gain. A key improvement in this regard has been the introduction of the raised base structure which is illustrated in Figure 2.2. The raised base decouples  $r_b$  and  $C_{bc}$  allowing extremely high extrinsic base doping for very low  $r_b$  without risk of a trade-off against  $C_{bc}$  [28].

The improvement of  $f_T$  has led to a 2.5 dB reduction in  $NF_{min}$  at 26 GHz and reduction of  $r_b$  has contributed another 1 dB drop. This gives a total NF improvement of 3.5 dB from the 0.5  $\mu$ m to the 0.13  $\mu$ m processes. At 15 GHz  $NF_{min}$  remains below 1 dB when  $I_C$  is varied

from 5 to 40 mA. The associated power gain is more than 10 dB with the highest value of 13 dB at 40 mA and continuing to rise beyond the maximum current used in the study [28].

These results show that HBTs are a good choice for high frequency and low noise applications.

Figure 2.2. Cross section of a raised extrinsic base SiGe HBT [32].

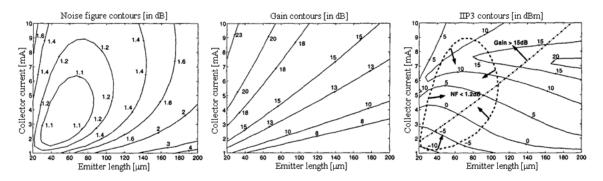

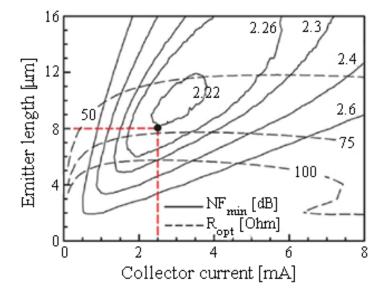

## 2.3.3 Design for minimum transistor noise figure

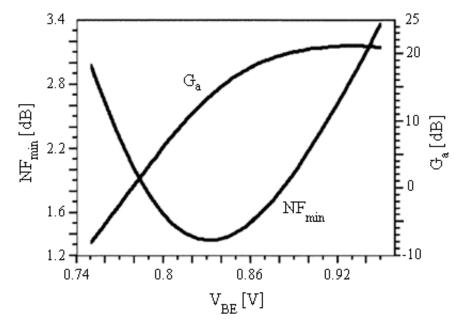

It was shown in Section 2.3.1 that there is a minimum attainable noise figure for transistors in a given technology. The transistor deviates from this minimum noise figure through its dependence on the collector current through  $g_m$ , as well as an increase with frequency at higher frequencies as  $\beta$  starts to roll-off. From (2.7) it can be shown that NF<sub>min</sub> first decreases with increasing  $I_C$  and then increases with  $I_C$  monotonically, if the dependence of  $C_i$  on  $I_C$  for bipolar transistors is observed [4]. This is shown in Figure 2.3 and indicates the absolute minimum noise figure that can be attained for this specific transistor by selection of a suitable  $I_C$ . Since the power gain is also dependent on  $I_C$  the associated gain was traded-off with a smaller NF which occurs at a  $f_T$  smaller than the maximum  $f_T$  for the device; typically at less than 20 % of the value for peak  $f_T$  in SiGe HBTs [28].

Figure 2.3. Typical minimum NF and current gain vs. VBE characteristic [4].

In selecting an amplifier topology for a multi-stage amplifier the FOM defined in Section 2.3.1 can be used as it captures both noise and available gain characteristics. The noise measure for identical SiGe HBTs in a common-emitter, common-base and cascode configuration was measured [33] at the minimum-noise bias and resulted in noise measures:  $M_{CE}$ =3.75,  $M_{CB}$ =3.40 and  $M_{casc}$ =3.47. These results show that for a simultaneous optimal noise and power match a common base amplifier stage would result in the best figure, however such simultaneous match is feasible noise a not CB-amplifiers and thus a cascode configuration should be used instead [33]. Cascode amplifiers have the further advantage of good reverse isolation which simplifies the matching network design and also better frequency response due to reduced Miller multiplication of  $C_{\mu}$  in the first transistor.

## 2.4 LINEARITY OF HBT AMPLIFIERS

The linearity of an amplifier can be quantified by either the 1 dB gain compression point  $(P_{1dB})$  or the third order input intermodulation product (IIP3).  $P_{1dB}$  is the input power resulting in a 1 dB drop in the first harmonic power gain due to the output power present in the second and higher order harmonics. The IIP3 is the two tone input power resulting in the first and third harmonic output power becoming equal. It is usually necessary to extrapolate this value since it typically occurs at an input power larger than the onset of

gain compression and it can in fact be shown that  $P_{1dB}$  is typically 9.6 dB lower than IIP3 [34].

Five sources of non-linearity can be identified in bipolar transistor amplifiers. The collector current transported from the emitter ( $I_{CE}$ ) is a nonlinear function of  $V_{BE}$ . The hole injection into the emitter ( $I_{BE}$ ) is also a nonlinear function of  $V_{BE}$ . The avalanche multiplication current ( $I_{CB}$ ) is a strong nonlinear function of both  $V_{BE}$  and  $V_{CB}$ . Finally,  $C_{BE}$  and  $C_{BC}$  are both nonlinear junction capacitance [35], [36].

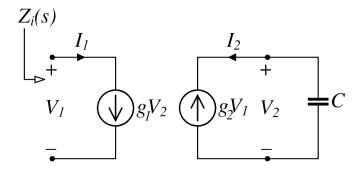

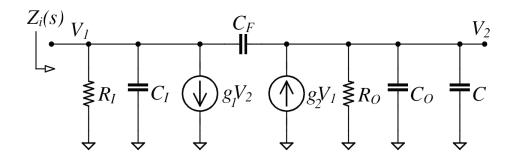

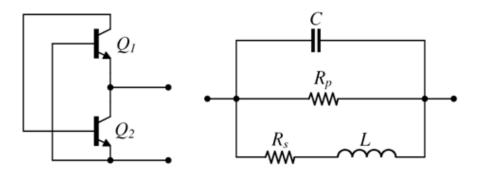

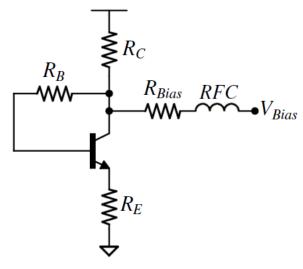

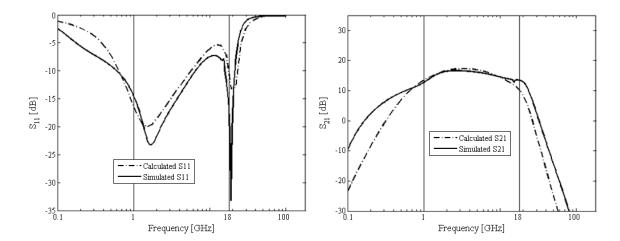

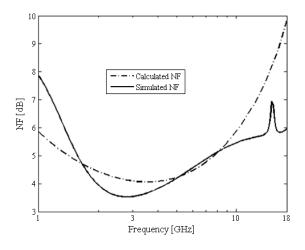

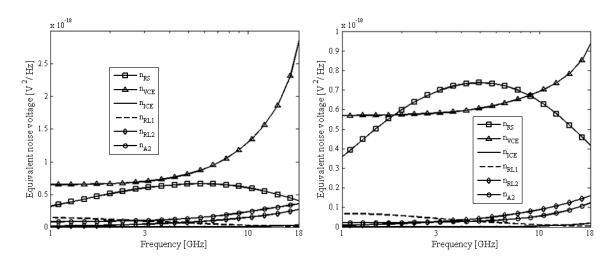

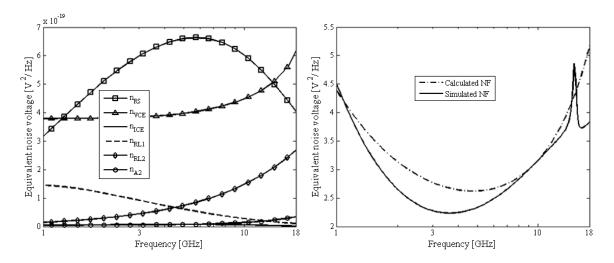

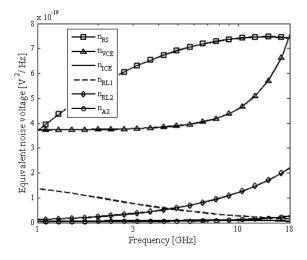

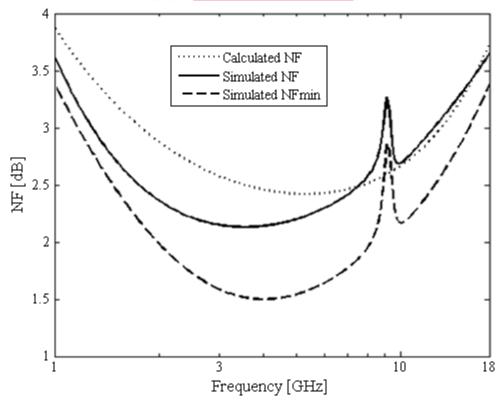

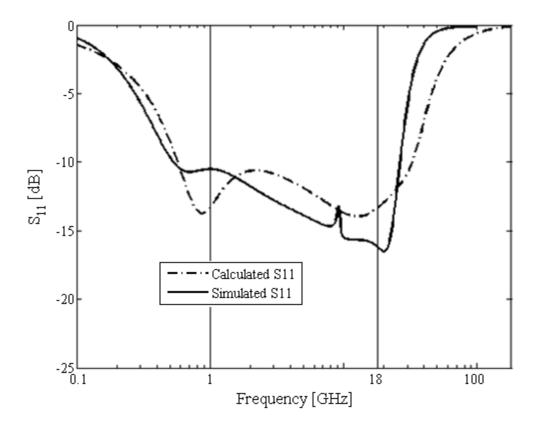

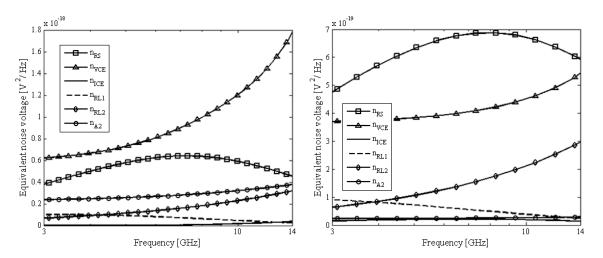

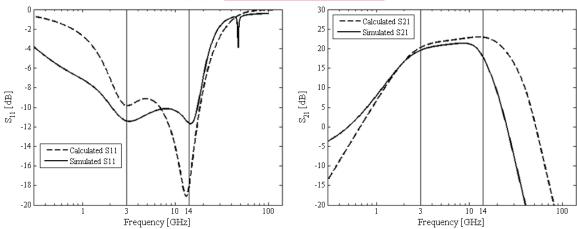

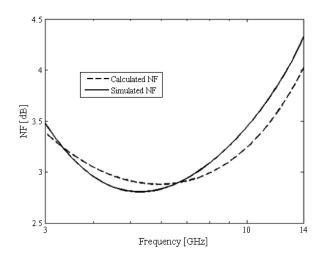

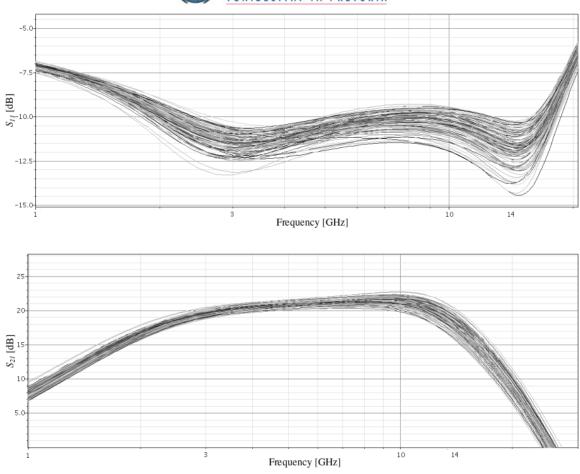

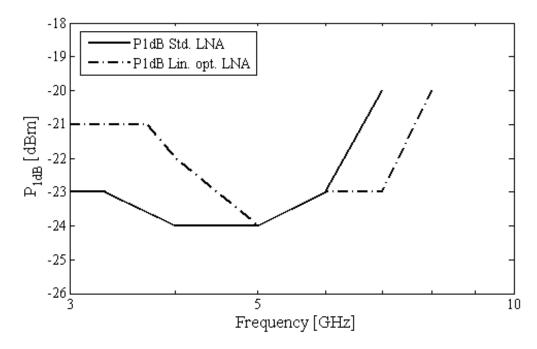

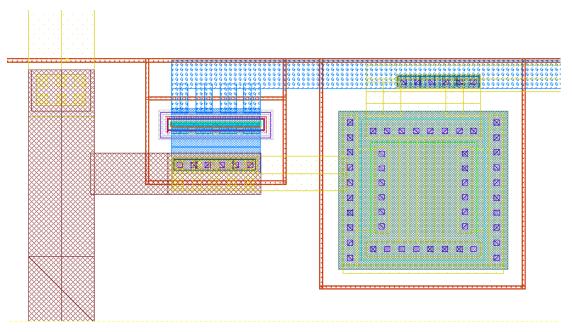

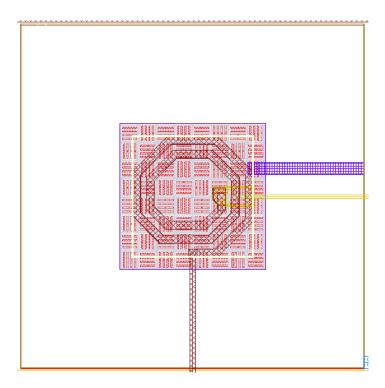

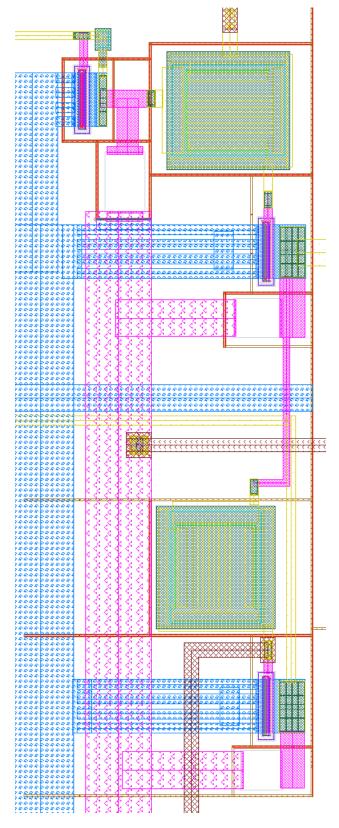

In [37] a Volterra-series based approach was used which completely distinguishes individual nonlinearities and is practical in circuits operating in weak nonlinearity such as LNAs. It was found that in HBT amplifiers the nonlinearity is dominated by the  $I_{CE} - V_{CE}$  nonlinearity for small collector currents, by the nonlinearity due to avalanche multiplication for 5 mA  $< I_C < 25$  mA, and by the  $C_{CB}$  nonlinearity for collector currents above 25 mA.