### 4. DESIGN

To achieve the previously stated objective of creating Si wire junctions with diameters less than 50 nm, the SOI test-devices could not be manufactured in a standard process with supplied design rules. Instead, the layout and process design had to consider various equipment limitations and characteristics as well as physical effects occurring during the self-processing.

#### 4.1. Starting Material

Before any design can commence the properties of the starting material need to be taken into consideration.

Table 4.1 shows the specifications of the SOI starting material wafers as supplied by Siegert Consulting e.K.<sup>2</sup>.

| Parameter                 | Value                                     | Grapl                                            | hical Representation                      |                    |

|---------------------------|-------------------------------------------|--------------------------------------------------|-------------------------------------------|--------------------|

| Туре                      | Epitaxial Transfer SOI                    |                                                  |                                           |                    |

| $D_{Wafer}$               | $76.2 \pm 0.3 \text{ mm}$                 |                                                  |                                           |                    |

| Doping                    | <i>p</i> (B)                              |                                                  |                                           |                    |

| t <sub>Device Layer</sub> | $0.5 \pm 0.1  \mu m$                      |                                                  | <i>p</i> -Si device layer<br>20 - 40 Ω·cm | 0.5 μm ± 0.1 μm    |

| 0                         | 20 - 40 Ω·cm                              |                                                  | $(\sim 4.10^{14} \text{ cm}^{-3})$        |                    |

| hoDevice Layer            | $(\sim 4 \cdot 10^{14} \mathrm{cm}^{-2})$ |                                                  | BOX                                       | $1 \mu m \pm 3 \%$ |

| $t_{Box}$                 | $1 \ \mu m \pm 3 \ \%$                    | $\leftarrow 76.2 \pm 0.3 \text{ mm} \rightarrow$ |                                           | <br>↑              |

| $ ho_{Handle}$            | $0.01 - 0.02 \ \Omega \cdot cm$           |                                                  | Si handle                                 | 350 μm ± 10 μm     |

| $t_{Handle}$              | $350 \mu\text{m} \pm 10 \mu\text{m}$      |                                                  |                                           | ¥                  |

| Edge exclusior            | n < 3 mm                                  |                                                  |                                           |                    |

Table 4.1. Siegert SOI Starting Material Specifications.

The 500 nm thick SOI active device layer above the BOX is the region where the light sources were implemented after its thickness was reduced to about 150 nm through thermal oxidation.

The 100 nm tolerance in SOI active device layer thickness might seem excessive, but is useful since a large variation in SOI light source thicknesses can be achieved with relative ease.

<sup>&</sup>lt;sup>2</sup> Siegert Consulting e.K., TZA-Technologiezentrum Aachen, Dennewartstr. 25-27, Raum A 1.14, D-52068 Aachen, Germany.

# 4.2. Lithographic Patterning

As indicated in Table 4.2, the small geometries and precise pattern alignment of the current work required electron-beam lithography (EBL), but the single beam exposure scan of EBL is too slow to write all features across complete wafers.

| Aspect                   | Photolithography                     | EBL                                      |  |

|--------------------------|--------------------------------------|------------------------------------------|--|

| Wavelength/spot-size     | $\approx 300 \text{ nm}$             | $\approx 2 \text{ nm}$                   |  |

| Minimum feature size     | $\approx 0.5 \ \mu m$                | $\approx 6 \text{ nm}$                   |  |

| Alignment accuracy       | > 1 µm                               | > 6 nm                                   |  |

| Exposure speed per wafer | Whole wafer at once<br>Fast: Minutes | Serial scanning beam<br>Very slow: hours |  |

Table 4.2. Photolithography and EBL Comparison.

While photolithographic patterning is possible at the CEFIM, the Microelectronic Research Centre (MiRC) of the Georgia Institute of Technology was visited to make use of their JEOL JBX-9300FS EPG.

### 4.3. Mask Definitions

For the reasons in previous subsection, as Table 4.3 shows, different processing steps and geometry areas of the wafer selectively employed photolithography or EBL.

| Processing | g Document | GDS | Layout                                                                                                                                                                                       | М                    | ask     |               | Alignment                |           |

|------------|------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------|---------------|--------------------------|-----------|

| Step       | Section    | No. | Rendering                                                                                                                                                                                    | Name                 | Туре    | Polarity      | Marker                   | Align to  |

| 3d         | 5.3        | 1   |                                                                                                                                                                                              | Si Island            | Photo   | Positive      | -                        | -         |

| 4d         | 5.4        | 2   | PERENERENENEN<br>NERENERENENEN<br>NERENERENEREN                                                                                                                                              | Arsenic (EBL)        | EBL     | Positive Tone | AlignmentMarkerEBL       | Si Island |

| 4j         | 5.4        | 3   | aPaPaPaPaPaPa<br>afarananyanan<br>afarananyanan<br>afarananyan<br>afarananyan<br>afarananyan<br>afarananyan<br>afarananyan<br>afarananyan<br>afarananyan<br>afarananyan<br>afarananyan       | Arsenic (Photo)      | Photo   | Negative      | AlignmentMarkerPhotoNoOx | Si Island |

| 5b         | 5.5        | 4   |                                                                                                                                                                                              | Finger Spacing       | EBL     | Positive Tone | AlignmentMarkerEBL       | Si Island |

| 6b         | 5.6        | 5   |                                                                                                                                                                                              | Oxidation (EBL)      | EBL     | Positive Tone | AlignmentMarkerEBL       | Si Island |

| 6c         | 5.6        | 6   | 07070707070707070<br>070707070707070<br>070707070707070<br>070707070707070<br>070707070707070<br>070707070707070<br>070707070707070<br>070707070707070<br>070707070707070<br>070707070707070 | Oxidation (Photo)    | Photo   | Negative      | AlignmentMarkerOx        | Si Island |

| 7a         | 5.7        | 7   |                                                                                                                                                                                              | Contact              | Photo   | Negative      | AlignmentMarkerPhotoNoOx | Si Island |

| 7e         | 5.7        | 8   |                                                                                                                                                                                              | Metal                | Photo   | Positive      | AlignmentMarkerPhotoNoOx | Contact   |

| 8          | -          | 9   |                                                                                                                                                                                              | Si Isolation Spacing | g Photo | Negative      | AlignmentMarkerPhotoNoOx | Si Island |

Table 4.3 Photolithographic and EBL Mask Detail.

Six photolithographic plates and three EBL file masks were required. The photolithographic *Si Island* mask defines where Si islands remain on the BOX after reactive ion etching (RIE) removes the superfluous Si. The thin Si fingers are created by using the fine *Finger Spacing* EBL mask to RIE slits into the Si islands. The *Oxidation* mask was then used to selectively oxidize the Si between the slits into thin SOI fingers.

# 4.4. Design Rules

To facilitate the successful manufacture of the SOI light sources, self-made design rules had to be set-up. These design rules had considered possible mask alignment errors, limitations of the processing equipment and physical phenomena occurring during the wafer manufacturing process. These self-setup design rules are listed in Addendum C.

# 4.5. SOI Light Sources

Two types of SOI light sources were designed and manufactured:

2D-confined light sources are thin in two dimensions, thickness and width.

1D-confined light sources are only thin in one dimension, the thickness.

Both light source types were implemented for comparative purposes to investigate the possible increase in Si electroluminescence power efficiency improvement of 2D-confined device over 1D-confined Si light sources.

# 4.5.1. 2D-confined SOI Light Sources

Three types of 2D-confined SOI light sources were implemented:

- 1)  $n^+p$  finger junction avalanche light sources,

- 2)  $n^+pn^+$  punch-through light sources and

- 3) Injection-enhanced light sources.

The design of these three types of 2D-confined Si light sources is described in the remainder of this sub-section.

# 4.5.1.1. n<sup>+</sup>p Finger Junction Avalanche Light Sources

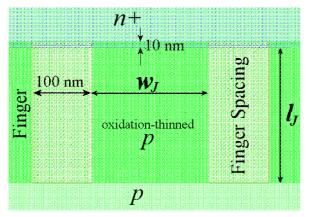

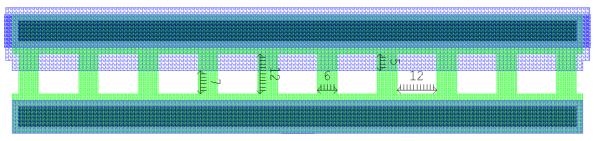

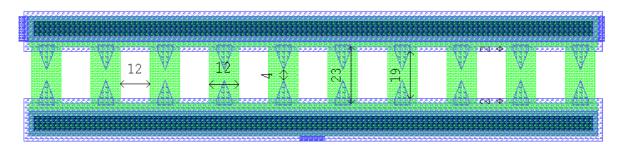

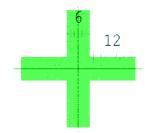

Figure 4.1 shows the pre-oxidized avalanche SOI finger light source layout.

Figure 4.1. Avalanche finger layout dimensions.

The Si island regions above and below the fingers remained thick while an EBL-written oxidation mask opening across the fingers allowed the selective thinning through oxidation of the SOI finger junctions.

The dimensioning of the devices shown in Figure 4.1 had to comply with the following specifications to ensure proper functionality of the devices:

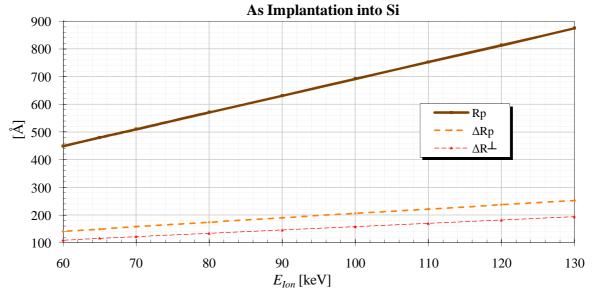

$$l_J \ge w_d + d_{O_X} + 3\varDelta R_{\perp A_S} \approx 226 \text{ nm and}$$

(4.1)

$$w_J \approx 2t_{Si},\tag{4.2}$$

where  $w_d$  is the reverse bias depletion region width at breakdown (see section 2.1.8),  $d_{Ox}$  is the worst-case As diffusion distance during all thermal oxidation steps after As implantation,  $\Delta R \perp_{As}$  is the transverse As implantation straggle (Figure 5.4) and the initial Si thickness before oxidation was assumed to be 100 nm  $\leq t_{Si} \leq 150$  nm.

Relation (4.1) ensured that the fingers were long enough to accommodate the complete depletion region width after the implanted As (with its horizontal implant straggle) has diffused into the fingers after oxidation.

Equation (4.2) aimed to create semi-circular round fingers by assuming isotropic finger shaping oxidation that would thin the Si fingers equally from all sides.

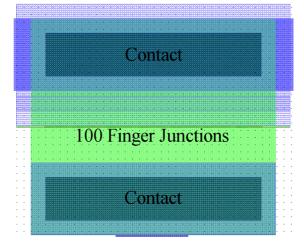

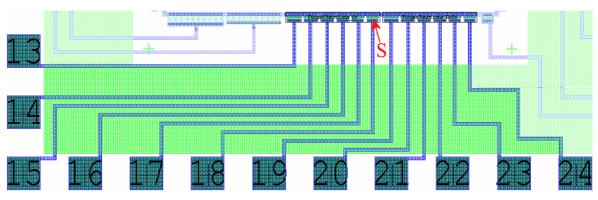

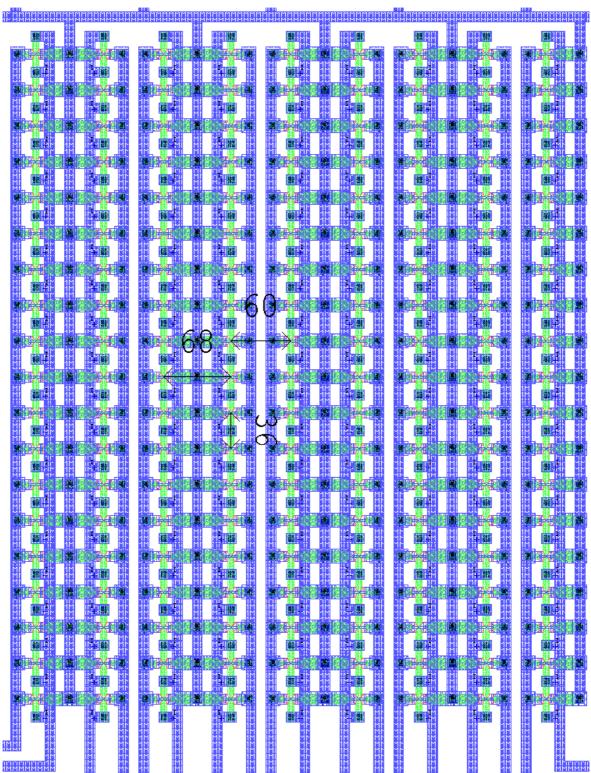

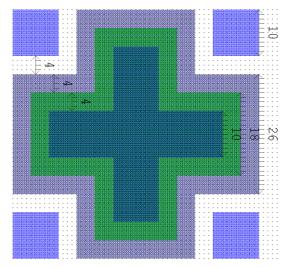

Figure 4.2 depicts a 30  $\mu$ m x 34  $\mu$ m  $n^+p$  junction device with 100 parallel finger junctions.

Figure 4.2. Finger junction device layout on a 1-µm grid.

Design

Table 4.4 shows the dimensions of implemented  $n^+p$  avalanche SOI light sources.

| Chip | Group                 | Device                       | Pin | Tuno                       | Oxidized?    | w <sub>J</sub> | $l_J$ |

|------|-----------------------|------------------------------|-----|----------------------------|--------------|----------------|-------|

| #    |                       | Name                         |     | Туре                       | Oxiuizeu:    | [ni            | m]    |

|      |                       | 100FingerJunctions200nm      | 18  |                            |              | 200            |       |

|      |                       | 100FingerJunctions220nm      | 17  |                            |              | 220            |       |

|      | Finantunations Or     | 100FingerJunctions240nm      | 16  |                            | Oxidized     | 240            |       |

|      | FingerJunctions_Ox    | 100FingerJunctions260nm      | 15  |                            |              | 260            |       |

|      |                       | 100FingerJunctions280nm      | 14  |                            |              | 280            |       |

| 1    |                       | 100FingerJunctions300nm      | 13  | n <sup>+</sup> p Avalanche |              | 300            | 230   |

| 1    |                       | 100FingerJunctions200nm_NoOx | 24  | n p Avalanche              |              | 200            |       |

|      |                       | 100FingerJunctions220nm_NoOx | 23  |                            | Not oxidized | 220            |       |

|      | Eineen kunstiene NeOu | 100FingerJunctions240nm_NoOx | 22  |                            |              | 240            |       |

|      | FingerJunctions_NoOx  | 100FingerJunctions260nm_NoOx | 21  |                            |              | 260            |       |

|      |                       | 100FingerJunctions280nm_NoOx | 20  |                            |              | 280            |       |

|      |                       | 100FingerJunctions300nm_NoOx | 19  |                            |              | 300            |       |

Table 4.4. Implemented  $n^+p$  avalanche finger junctions.

The common  $n^+$  terminal to all above devices is connected to pad 5.

Figure 4.3 shows the 2D-confined finger junction avalanche SOI device layouts in *Chip1* (Figure 4.24) and the location of light source **S** with the narrowest pre-oxidized finger width  $(w_J = 200 \text{ nm})$ .

Figure 4.3. Finger junction devices layout.

# 4.5.1.2. n<sup>+</sup>pn<sup>+</sup> Punch-through Light Sources

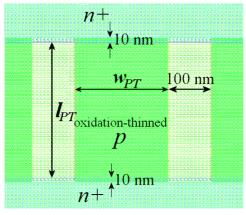

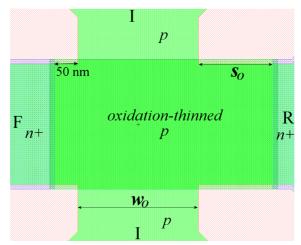

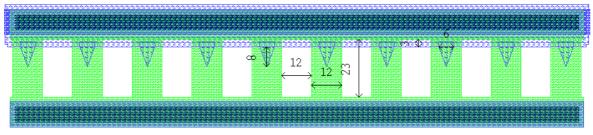

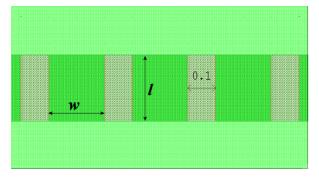

Figure 4.4 shows the designed layout dimension definitions of the punch-through SOI light source fingers.

Figure 4.4.  $n^+pn^+$  punch-through finger layout dimension definitions.

Similar to the avalanche breakdown devices the dimensioning of the devices shown in Figure 4.4 had to comply with the following specifications to ensure proper functionality of the devices:

$$l_{PT} \approx w_d + 2(d_{Ox} + 3\varDelta R_{\perp As}) \approx 352 \text{ nm and}$$

(4.3)

$$w_{PT} \approx 2t_{Si}.\tag{4.4}$$

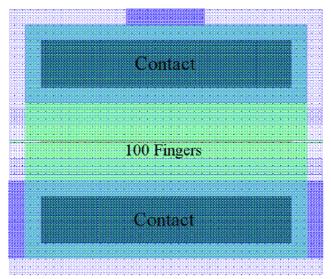

Figure 4.5 shows how 100 punch-through fingers shown in Figure 4.4 are placed in parallel between thicker and larger Si islands that allow electrical biasing through the interconnect metallization.

Figure 4.5. Device layout incorporating 100 parallel  $n^+pn$  punch-through fingers of Figure 4.4.

Table 4.5 and Table 4.6 show the implemented  $n^+pn^+$  punch-through device dimensions.

| Oxidized                      |                                                 |     |     |     |     | <i>l<sub>PT</sub></i><br>[nm] |     |     |     |     |

|-------------------------------|-------------------------------------------------|-----|-----|-----|-----|-------------------------------|-----|-----|-----|-----|

|                               |                                                 | 320 | 330 | 340 | 350 | 360                           | 370 | 380 | 390 | 400 |

|                               | 220                                             | 34  | 25  | 29  | 35  | 26                            | 30  | 38  | 27  | 33  |

| <i>w<sub>PT</sub></i><br>[nm] | 260                                             | 36  | 39  | 31  | 34  | 28                            | 37  | 40  | 32  | 35  |

| []                            | 300                                             | 38  | 3   | 33  | 1   | 4                             | 36  | 2   | -   | 37  |

|                               | Legend: <i>pin on Chip1</i> <b>pin on Chip2</b> |     |     |     |     |                               |     |     |     |     |

Table 4.5. Oxidation-thinned punch-through device pin-out.

Table 4.6. Non-thinned punch-through device pin-out.

| Not oxidized                  |     |     |     |     |     | <i>l<sub>PT</sub></i><br>[nm] |     |     |     |     |

|-------------------------------|-----|-----|-----|-----|-----|-------------------------------|-----|-----|-----|-----|

|                               |     | 320 | 330 | 340 | 350 | 360                           | 370 | 380 | 390 | 400 |

|                               | 220 | 22  | 16  | 28  | 23  | 17                            | 29  | 11  | 18  | 6   |

| <i>w<sub>PT</sub></i><br>[nm] | 260 | 24  | 12  | 30  | 7   | 19                            | 26  | 13  | 31  | 8   |

| []                            | 300 | 27  | 20  | 32  | 14  | 21                            | 9   | 15  | -   | 10  |

All pins on *Chip2*

The node common to all above devices is connected to pad 5.

Design

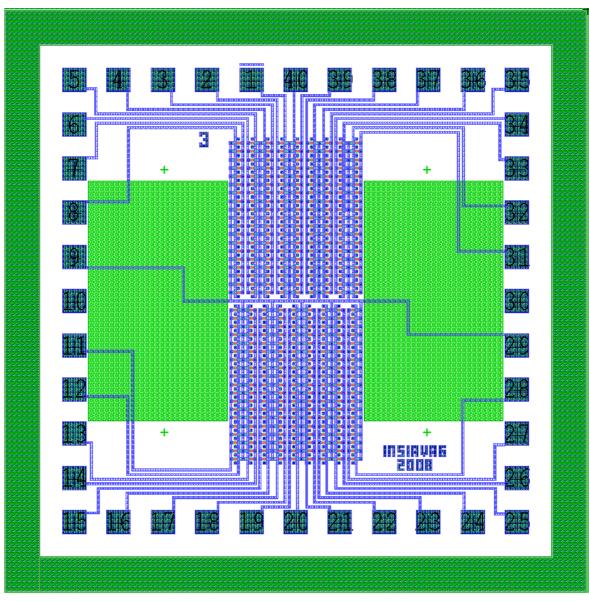

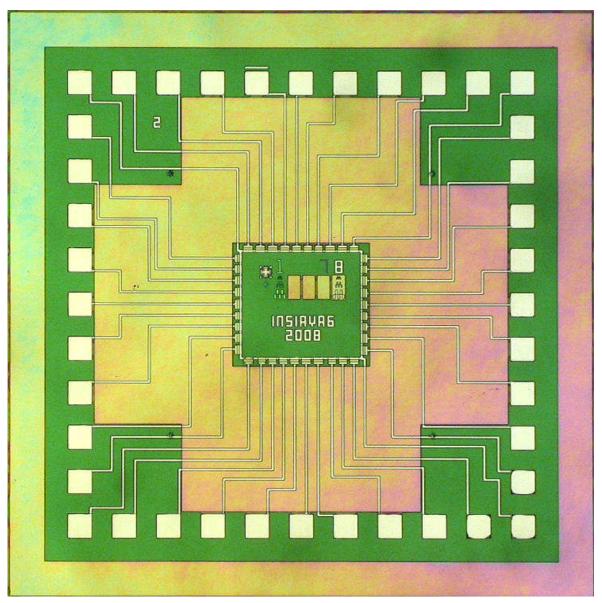

Figure 4.24 shows *Chip2*, which is populated with the 2D-confined  $n^+pn^+$  punch-through SOI light sources.

Figure 4.6. Chip2 layout.

*Chip1* and *Chip2* contain 2D-confined  $n^+pn^+$  punch-through SOI light sources, but most are located on *Chip2*.

#### 4.5.1.3. Carrier-injection Light Sources

Two different carrier-injection SOI light sources were designed and implemented: The *Opposite* injector configuration has a forward-biased injector and reversed-biased acceptor junctions opposite to each other and the *Side* configuration where two injection junctions are adjacent to the acceptor junction.

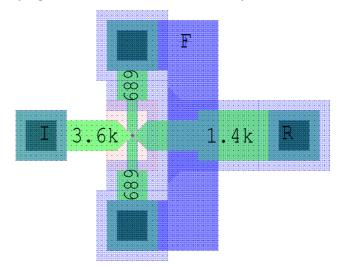

#### 4.5.1.3.1 Opposite-injectors

Figure 4.7 shows that the opposite-injection SOI light source element has the forward-biased  $n^+p$  injector junction (interface between F and I regions) opposite to the reverse-biased  $n^+p$  acceptor junction (between R and I regions).

Figure 4.7. Opposite-injection SOI element layout dimension definitions.

It is expected that the reverse-bias depletion region extending from the R-I interface will stretch towards the forward-biased injector junction (F-I interface) from where it will receive cool electrons for radiative recombination with hot holes in its high electric field.

The dimensioning of the devices shown in Figure 4.7 had to comply with the following specifications to ensure proper functionality of the devices:

$$s_o \approx d_{ox} + 3\varDelta R_{\perp As} \approx 126 \text{ nm},$$

(4.5)

$$w_0 > w_d + \Delta Si, \tag{4.6}$$

where  $\Delta Si$  is the Si thickness removed during the thinning oxidations. Equation (4.5) intends to advance the final (after all thermal processing) reverse-bias  $n^+$  interface a distance  $s_0$  to the left, i.e. on the right side of the drawn intermediate (I) nodes. Relation (4.6) ensures that the final intermediate node widths are not completely covered by the reverse-bias depletion region so that the injector can still be forward-biased.

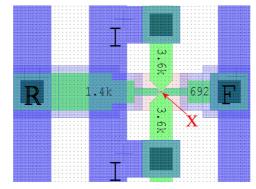

Single opposite-side injection elements are implemented in cells as shown in Figure 4.12, which allowed laying them out in interconnected arrays of 19 devices in parallel.

Figure 4.8. Single opposite-injector element layout on a 1-µm grid.

"X" demarcates the location of an injector type shown in Figure 4.7. R, F and I denote the reverse-biased acceptor, forward-biased injector and intermediate nodes respectively. Table 4.7 lists the dimensions of the implemented opposite-side SOI injector light sources.

| <b>Opposite-injectors</b> |          |          |                       |       |  |  |  |

|---------------------------|----------|----------|-----------------------|-------|--|--|--|

|                           | Oxidized |          |                       |       |  |  |  |

| Dimens                    | ion      |          | <i>s</i> <sub>0</sub> |       |  |  |  |

| Dimens                    |          |          | [nm]                  |       |  |  |  |

|                           | Pin #    | 120      | 160                   | 200   |  |  |  |

|                           | 200      | F: 11    | F: 14                 | F: 15 |  |  |  |

|                           |          | I: 12    | I: 13                 | I: 16 |  |  |  |

| <i>w<sub>o</sub></i> [nm] | 260      | F: 18    | F: 19                 | F: 22 |  |  |  |

|                           | 200      | I: 17    | I: 20                 | I: 21 |  |  |  |

|                           | 300      | F: 23    | F: 26                 | F: 27 |  |  |  |

|                           | 500      | I: 24    | I: 25                 | I: 28 |  |  |  |

|                           | Non-     | oxidized |                       |       |  |  |  |

| Dimens                    | ion      |          | \$ <sub>0</sub>       |       |  |  |  |

| Dimens                    | ion      |          | [nm]                  |       |  |  |  |

|                           | Pin #    | 120      | 160                   | 200   |  |  |  |

|                           | 200      | F: 31    | F: 34                 | F: 35 |  |  |  |

|                           | 200      | I: 32    | I: 33                 | I: 36 |  |  |  |

| w <sub>o</sub> [nm]       | 260      | F: 38    | F: 39                 | F: 2  |  |  |  |

| <i>w<sub>0</sub></i> [nm] | 200      | I: 37    | I: 40                 | I: 1  |  |  |  |

|                           | 300      | F: 3     | F: 6                  | F: 7  |  |  |  |

|                           | 500      | I: 4     | I: 5                  | I: 8  |  |  |  |

| Table 4.7   | Opposite-si | de injection | devices | nin-out |

|-------------|-------------|--------------|---------|---------|

| 1 auto 4.7. | Opposite-si | ue injection | uevices | pm-out. |

The common reverse-biased node R of all devices is connected to pads 9 and 29.

Figure 4.9 shows how the nine differently dimensioned opposite-side injection light source arrays are arranged in a matrix.

Figure 4.9. Nine columns of 19-element opposite-side injection device line-arrays.

Design

Figure 4.10 shows *Chip3*, which contains the oxidized and non-oxidized opposite-side injection devices.

Figure 4.10. *Chip3* layout containing the *Opposite* injector light sources..

# 4.5.1.3.2 Side-injectors

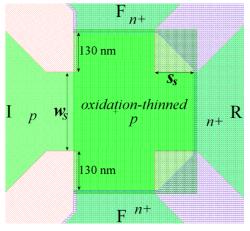

As shown in Figure 4.11 the side-injection device has two injecting forward-biased junctions (F-I interface) adjacent to the reverse-biased acceptor junction (R-I interface).

Figure 4.11. Side-injection SOI device layout dimension definitions.

The dimensioning of the devices shown in Figure 4.11 had to comply with the following specifications to ensure proper functionality of the devices:

$$s_s \approx d_{Ox} + 3\varDelta R_{\perp As} \approx 86 \text{ nm and}$$

(4.7)

$$w_s = w + 2\Delta Si. \tag{4.8}$$

While relation (4.7) attempts to place the final reverse-biased R-I  $pn^+$  acceptor interface a distance  $s_s$  to the left so that it borders in line with the right edge of the drawn forward-biased F-I injector interface, equation (4.8) intends to round the final Si strips.

The injection devices in Figure 4.11 are implemented in elemental cells as shown in Figure 4.12, which allowed laying them out in interconnected arrays of 19 devices in parallel.

Figure 4.12. Single side-injection SOI injector element layout on a 1-µm grid.

Table 4.8 lists the dimensions of the implemented side-injection SOI light sources.

| Side-injectors    |       |                   |                |                |  |  |

|-------------------|-------|-------------------|----------------|----------------|--|--|

|                   | Ox    | idized            |                |                |  |  |

| Dimension         |       | <i>xs</i><br>[nm] |                |                |  |  |

|                   | Pin # | 50                | 90             | 130            |  |  |

|                   | 200   | F: 12<br>I: 11    | F: 13<br>I: 14 | F: 16<br>I: 15 |  |  |

| <i>ws</i><br>[nm] | 260   | F: 17<br>I: 18    | F: 20<br>I: 19 | F: 21<br>I: 22 |  |  |

|                   | 300   | F: 24<br>I: 23    | F: 25<br>I: 26 | F: 28<br>I: 27 |  |  |

|                   | Non-  | oxidized          |                |                |  |  |

| Dimension         |       | <i>xs</i><br>[nm] |                |                |  |  |

|                   | Pin # | 50                | 90             | 130            |  |  |

|                   | 200   | F: 32<br>I: 31    | F: 33<br>I: 34 | F: 36<br>I: 35 |  |  |

| <i>ws</i><br>[nm] | 260   | F: 37<br>I: 38    | F: 40<br>I: 39 | F: 1<br>I: 2   |  |  |

|                   | 300   | F: 4<br>I: 3      | F: 5<br>I: 6   | F: 8<br>I: 7   |  |  |

Table 4.8. Side-injection devices pin-out.

The common reverse-biased node R of all devices connects to pads 9 and 29 (Figure 4.13).

Figure 4.13 shows the layout of *Chip4*, which contains the oxidized and non-oxidized side-injection SOI light sources.

Figure 4.13. Chip4 layout.

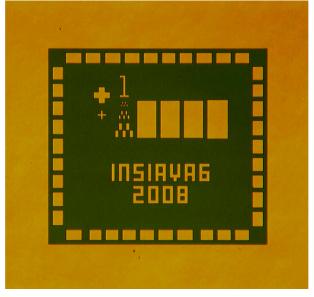

# 4.5.2. 1D-confined Comparison Light Sources

In parallel to the manufacture of the nanometre-scale SOI light sources, another SOI design (*INSiAVA1*) was manufactured entirely at the CEFIM. This test-chip did not make use of EBL or RIE processing steps and could only produce horizontally large (planar), but vertically thin SOI light sources.

For comparative purposes, some *INSiAVA1* avalanche and punch-through devices were implemented in this work. The implemented *INSiAVA1* devices are geometrically identical to *INSiAVA1* devices manufactured in the CEFIM clean-room, but exist in two variants: One version of *INSiAVA1* devices are oxidation-thinned to about 20 nm while the other set incorporates devices that remain at the initial silicon island thickness of about 150 nm.

# 4.5.2.1. n<sup>+</sup>p Avalanche Light Sources

Figure 4.14 and Figure 4.15 show the dimensions of two *INSiAVA1* avalanche breakdown devices.

Figure 4.14. INSiAVA1  $n^+p$  avalanche breakdown device layout.

To possibly increase the light intensity with a higher electric field in a confined light generation area, the device in Figure 4.15 implemented triangular  $n^+$  regions.

Figure 4.15. Triangular *INSiAVA1*  $n^+p$  avalanche breakdown device layout.

# 4.5.2.2. n<sup>+</sup>pn<sup>+</sup> Punch-through Light Sources

Figure 4.16 and Figure 4.17 display the two types of *INSiAVA1* punch-through devices implemented.

Figure 4.16. *INSiAVA1*  $n^+pn^+$  punch-through device layout.

Figure 4.17. *INSiAVA1* triangular  $n^+pn^+$  punch-through device layout.

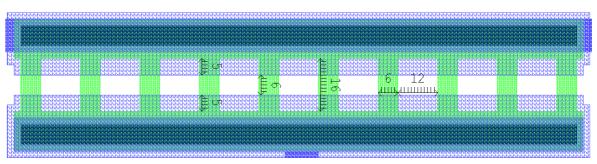

### 4.6. Process Monitor Resistors

To measure process and material properties like finger thicknesses and doping concentrations, a matrix of  $n^+$  and p resistor finger devices were included in the design. These resistors had similar dimensions to the avalanche-breakdown junction devices, but were either doped completely  $n^+$  or p.

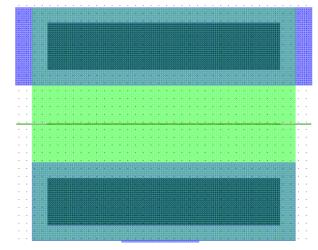

#### Figure 4.18 illustrates the process monitor resistor finger width *w* and length *l* definitions.

Figure 4.18. Process monitor resistor finger dimension definition.

Figure 4.19 shows a 100-finger process monitoring resistor device layout.

Figure 4.19. 100-finger process monitor resistor layout.

To enable the determination of doping concentration and thickness through resistive measurements, the  $n^+$  and p resistors were each designed in two variants: While the one version had the fingers as shown above, the second version omitted the finger definition mask from the layout. In this way the resistance of various finger widths, as well as very wide, but thin silicon structures could be measured.

Figure 4.20 shows the configuration of the four different process-monitor resistor types.

Figure 4.20. Process monitoring resistors.

Table 4.9 lists the dimensions and pin-out of all implemented resistor types.

| Chip       | Group         | Device      | Pin | Tune  | Oxidized?     | w   | l   |

|------------|---------------|-------------|-----|-------|---------------|-----|-----|

| No.        |               | Name        | No. | Туре  | Oxidized :    | [n: | m]  |

|            |               | Rn200nmOx   | 3   |       |               | 200 |     |

|            |               | Rn260nmOx   | 2   |       |               | 260 |     |

|            | RnOx          | Rn300nmOx   | 1   |       | Oxidized      | 300 |     |

|            | кнол          | Rn400nmOx   | 24  |       | Oxidized      | 400 |     |

|            |               | Rn500nmOx   | 23  |       |               | 500 |     |

|            |               | Rn600nmOx   | 22  | $n^+$ |               | 600 |     |

|            | RnNoOx        | Rn200nmNoOx | 21  | n     | Not oxidized  | 200 |     |

|            |               | Rn260nmNoOx | 20  |       |               | 260 |     |

|            |               | Rn300nmNoOx | 19  |       |               | 300 |     |

|            |               | Rn400nmNoOx | 18  |       |               | 400 |     |

|            |               | Rn500nmNoOx | 17  |       |               | 500 |     |

| 1          |               | Rn600nmNoOx | 16  |       |               | 600 | 240 |

| (RsFramed) |               | Rp200nmOx   | 15  |       | Oxidized      | 200 | 240 |

|            |               | Rp260nmOx   | 14  |       |               | 260 |     |

|            | PnOr          | Rp300nmOx   | 13  |       |               | 300 |     |

|            | RpOx          | Rp400nmOx   | 12  |       | Oxidized      | 400 |     |

|            |               | Rp500nmOx   | 11  |       |               | 500 |     |

|            |               | Rp600nmOx   | 10  |       |               | 600 |     |

|            |               | Rp200nmNoOx | 9   | р     |               | 200 |     |

|            |               | Rp260nmNoOx | 8   |       |               | 260 |     |

|            | DnNaOc        | Rp300nmNoOx | 7   |       | Not oviding 1 | 300 |     |

|            | <i>RpNoOx</i> | Rp400nmNoOx | 6   |       | Not oxidized  | 400 |     |

|            |               | Rp500nmNoOx | 5   |       |               | 500 |     |

|            |               | Rp600nmNoOx | 4   |       |               | 600 |     |

Table 4.9. Implemented process-monitor resistors.

The common terminal to all above resistors is connected to a pad at the centre of the resistor cluster in Figure 4.20.

# 4.7. Alignment Markers

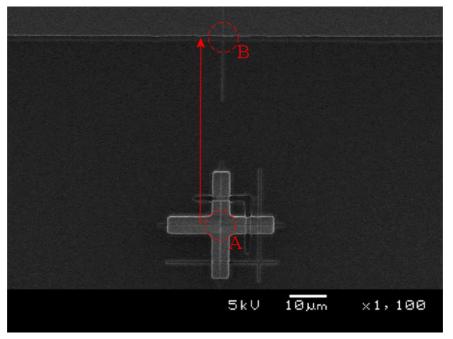

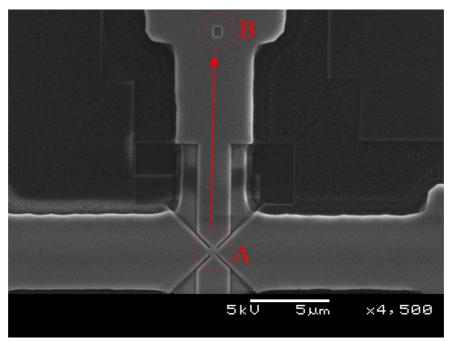

To achieve the required alignment accuracy when positioning the *Arsenic*, *Finger Spacing* and *Oxidation* masks relative to each other, EBL alignment marker crosses were initially etched into the SOI active layer and refined with the first EBL and etch step.

The marker in Figure 4.21 aligned *Finger Spacing* to *Si Island* and then the following EBL features to *Finger Spacing*.

Figure 4.21. *AlignmentMarkerEBL* layout.

The marker in Figure 4.22 aligned Oxidation (Photo) to Si Island.

Figure 4.22. *AlignmentMarkerOx* layout.

The marker in Figure 4.23 aligned all photo masks, except Oxidation (Photo), to Si Island.

Figure 4.23. *AlignmentMarkerPhotoNoOx* layout.

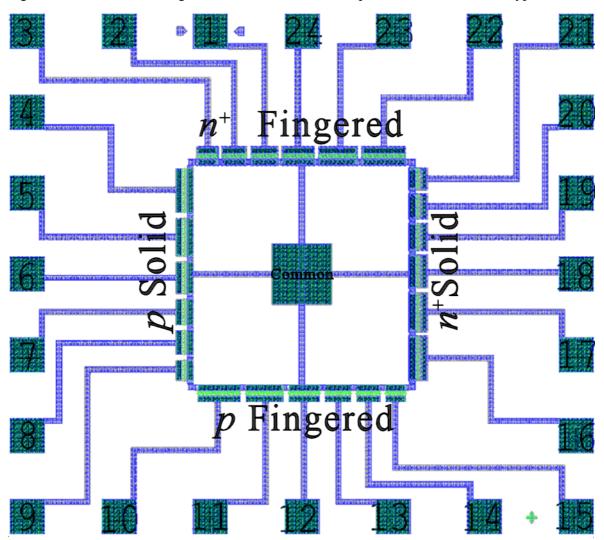

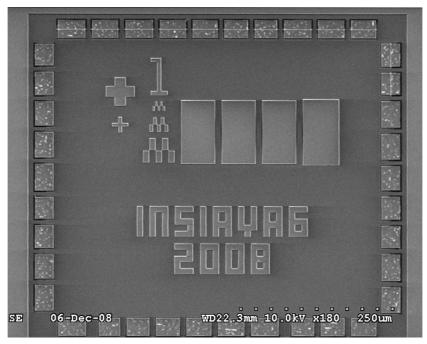

# 4.8. Overall Layout

# 4.8.1. Chip1

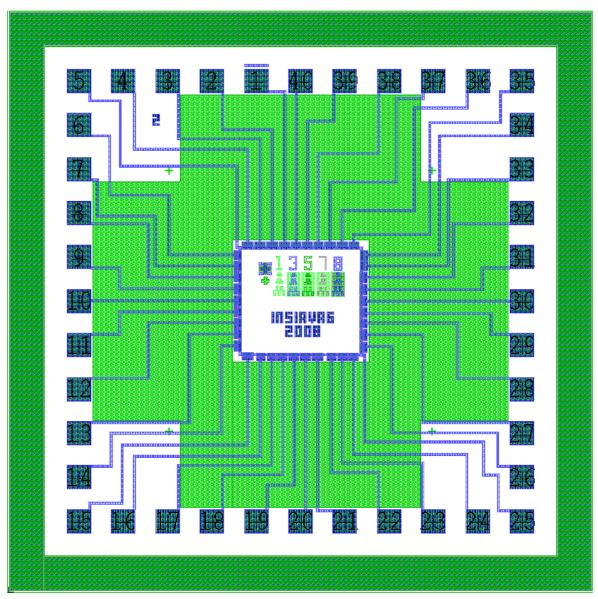

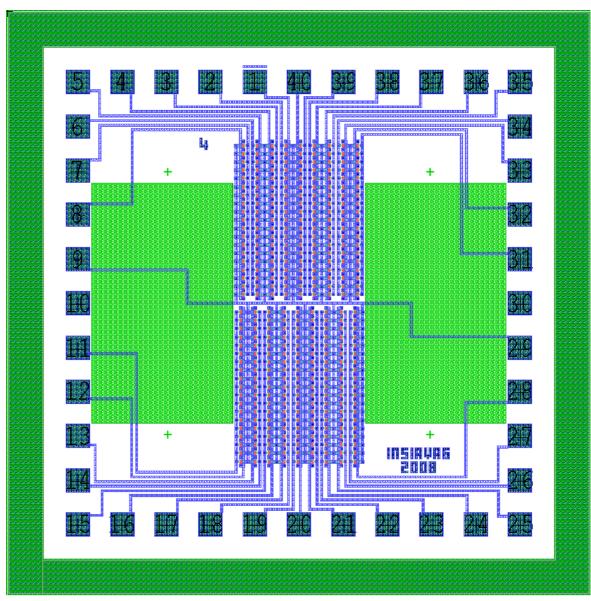

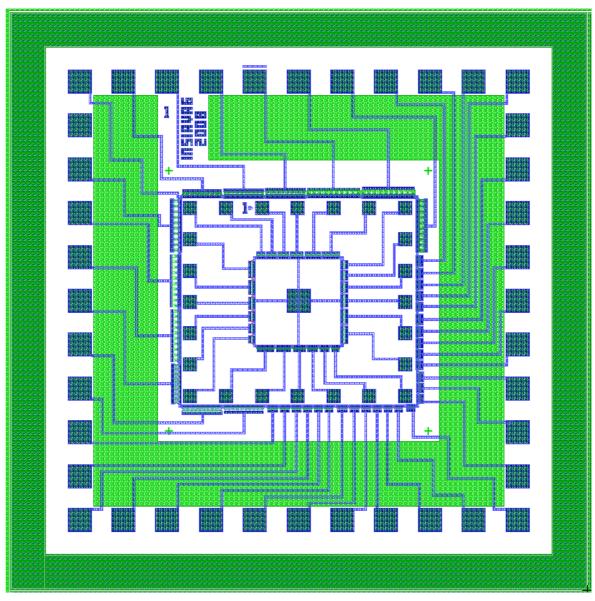

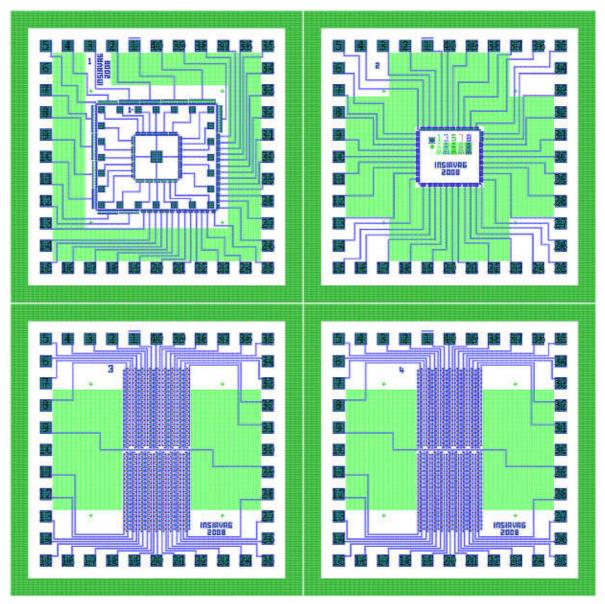

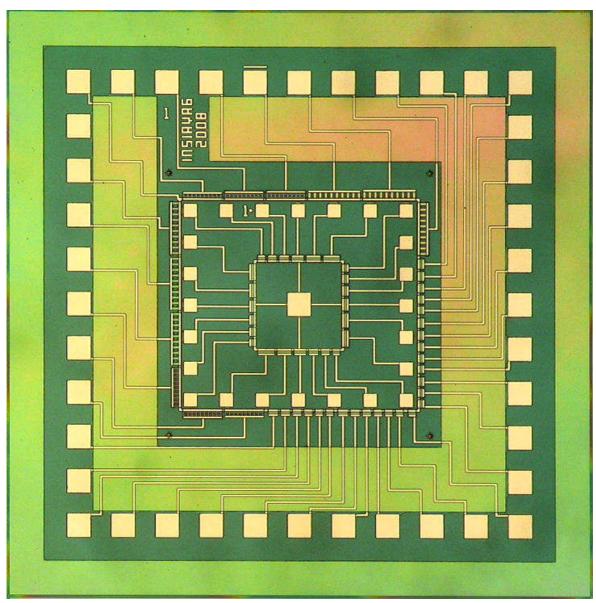

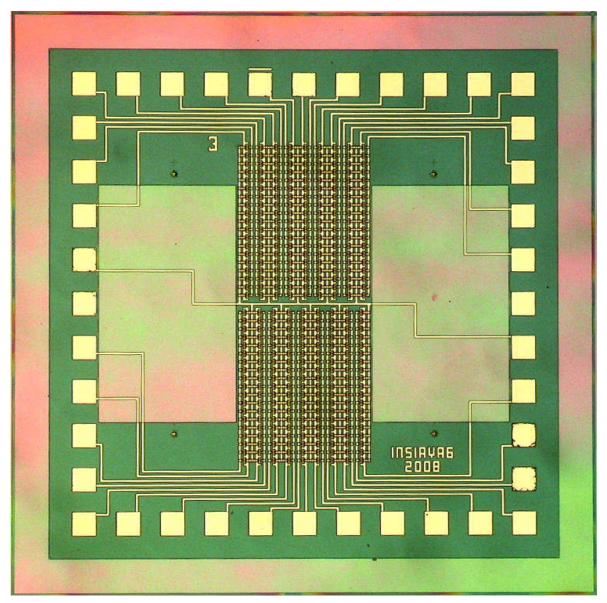

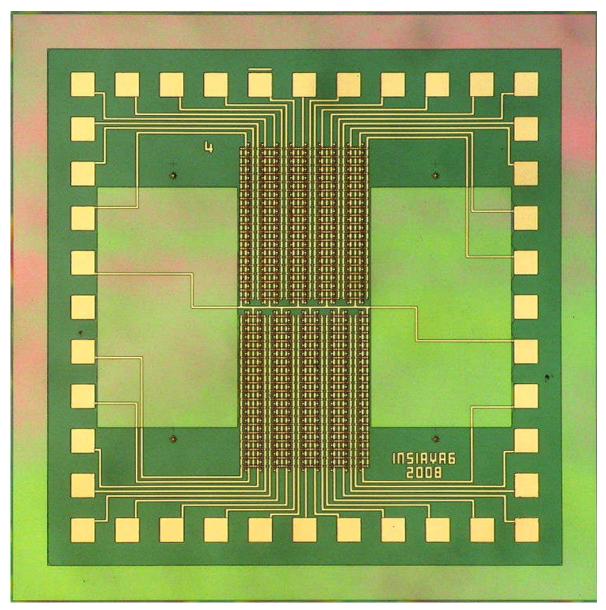

Figure 4.24 shows the complete *Chip1* layout that contains the 1D-confined test-devices, the 2D-confined  $n^+p$  avalanche breakdown finger-junction light sources, some 2D-confined  $n^+pn^+$  punch-through devices and all process-monitoring resistors

Figure 4.24. Chip1 layout.

The other three chip layouts were already presented in the sections that described their constituent test devices.

Design

Figure 4.24 depicts the complete four-chip test-cluster CAD layout that was used to manufacture the photolithographic masks and generate the EBL data files required by the JEOL JBX-9300FS electron-beam pattern generator EPG.

Figure 4.25 CAD layout showing the four chips in a 5.1 mm x 5.1 mm cluster.

*Chip 1* in the top-left quadrant of the cluster contains 18 avalanche and 19 punch-through 100finger SOI light source arrays, *Chip 2* (top right) contains 39 100-finger punch-through device arrays while *Chip 3* and *Chip 4* contain 36 19-element arrays of the two different injection light source types.

# 4.9. Photo-mask Layout

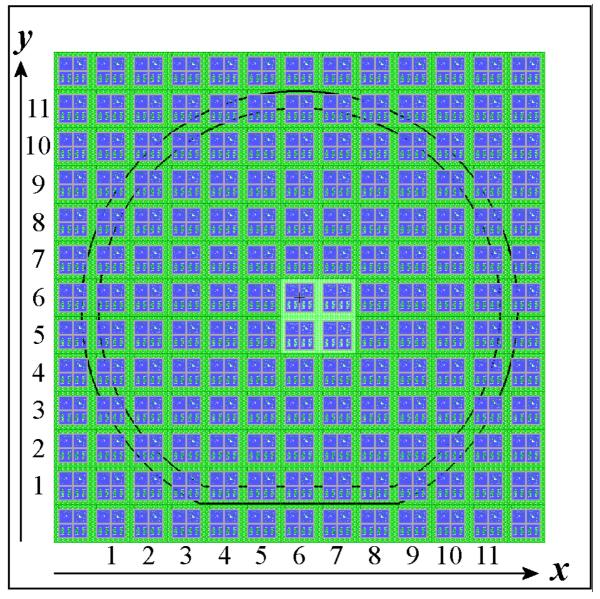

Figure 4.26 shows that 73 test-chip clusters fit on a 3-inch SOI wafer if 1.5 mm wide Si oxidation-monitoring areas are maintained between clusters.

Figure 4.26. Layout and position denotation of the 73 test-chip clusters on a 3-inch wafer.

The four clusters in the approximate middle of the wafer (x = 6, 7; y = 5, 6) are the "*EBL clusters*" and are different from the surrounding "*Photo clusters*". While the *As* and *Oxidation* masks are duplicated on the photo and EBL masks (except for the omission of large oxidation control areas in the EBL files), the *photo-clusters* do not contain the 100 nm wide finger-spacing slits that could only be patterned through EBL.

# **5. MANUFACTURE**

Table 5.1 gives a brief summary of the processing steps, equipment and facilities involved in the manufacture of the SOI light sources.

| Step | Section | Action                       | Equipment                                                | Facilities            | Graphical representation                     |

|------|---------|------------------------------|----------------------------------------------------------|-----------------------|----------------------------------------------|

| 1    | 5.1     | Si thinning                  | Furnace,<br>Reflective spectrometer                      | CEFIM,<br>MiRC        | p <sup>-</sup> Si ‡≈ 150 nm<br>BOX<br>Handle |

| 2    | 5.2     | Blanket B implant            | Ion implanter                                            | Core Systems          | p Si<br>BOX<br>Handle                        |

| 3    | 5.3     | Si island definition         | PECVD,<br>Mask aligner,<br>RIE                           | MiRC                  | Si Island<br>BOX<br>Handle                   |

| 4    | 5.4     | As implant                   | PECVD,<br>EPG,<br>Mask aligner,<br>RIE,<br>Ion implanter | MiRC,<br>Core Systems | n+ p<br>BOX<br>Handle                        |

| 5    | 5.5     | Finger definition            | EPG,<br>RIE                                              | MiRC                  | n+ p BOX                                     |

| 6    | 5.6     | Finger<br>thinning oxidation | PECVD,<br>EPG,<br>Furnace                                | MiRC,<br>CEFIM        | BOX                                          |

| 7    | 5.7     | Metallization                | PECVD,<br>Mask aligner,<br>Sputterer                     | CEFIM,<br>Elume       | Al Al                                        |

| 8    | -       | Si isolation spacing         | Mask aligner                                             | CEFIM                 | BOX                                          |

| Table 5.1. | Process | flow | overview. |

|------------|---------|------|-----------|

Each of the manufacturing steps in Table 5.1 is discussed in more detail in the following subsections in the remainder of this chapter.

Since no standard process recipe was employable, the complete manufacturing process had to be designed on self-obtained equipment characterization data, material and chemical properties.

To ensure consistent results and confirm acceptable manufacturing performance, process control and monitoring was employed. This involved the simultaneous processing of monitor wafer pieces and the measurement of on-chip test-structures that could be analyzed with a SEM, a reflective spectrometer (to measure thin film thicknesses) and a profilometer.

The processing equipment was controlled by adapting machine-specific "recipe" variables like processing time, pressure, DC & AC (plasma) power, gas flows, etc.

# 5.1. Si Thinning

Since as shown in Table 4.1, the initial SOI wafer handle was too thick (0.5  $\mu$ m ± 0.1  $\mu$ m), the very first processing requirement was to thin down the SOI device layer. The requirements of the Si island thickness were:

- 1) The alignment marker thickness should be automatically recognizable by the EPG.

- 2) The step height from the BOX surface to the Si pad and contact area islands should not cause metal step coverage problems.

- The difference between initial and final finger thickness (≈ 30 nm) should be easily be reduced through dry oxidation.

- The Si island thickness should consider the possible handle thickness variation of about 100 nm so that that Si islands should remain after the thinning oxidation.

As a compromise to above requirements, it was decided to aim for an average Si island thickness of about 150 nm.

Table 5.2 lists the processing steps associated with thinning down the SOI wafer handle thicknesses down to about 150 nm.

| Step | Action                                                          | Equipment                                 | Material         | Facilities | Graphical representation                                            |

|------|-----------------------------------------------------------------|-------------------------------------------|------------------|------------|---------------------------------------------------------------------|

| 1a   | Si wet oxidation<br>1 h 48 Min @ 1050 °C<br>(oxidizes ~ 322 nm) | Furnace                                   | H <sub>2</sub> O | CEFIM      | $SiO_{2}$ $p^{-} Si \qquad \uparrow \approx 0.5 \ \mu m$ BOX Handle |

| 1b   | SiO <sub>2</sub> etch                                           | Fume hood                                 | BOE              | / MiRC     | A                                                                   |

| 1c   | Measure <i>t<sub>si</sub></i>                                   | Reflective spectrometer<br>Chemical scale | -                |            | p <sup>-</sup> Si ↓≈ 150 nm<br>BOX<br>Handle                        |

| I    | Repeat steps 1a to 1c ur                                        | til $t_{Si}$ of each wafer $\approx 15$   | 50 nm            |            |                                                                     |

Table 5.2. Si thinning processing steps.

The initial thinning oxidations were done in the CEFIM clean-room at UP. Since no reflective spectrometer was available and four-point probe measurements delivered vague Si thickness variation monitoring results during the oxidations, it was decided to use a highly sensitive chemical scale in the CEFIM clean-room to measure the change in wafer weight  $\Delta w_{Wafer}$  and use the wafer diameter  $D_{Wafer}$  (Table 4.1) and density of Si  $d_{Si}$  (Addendum A) in the relation

$$\Delta t_{Si} = \frac{\Delta w_{Wafer}}{\pi \left(\frac{D_{Wafer}}{2}\right)^2 d_{Si}},$$

(5.1)

to determine the Si thickness  $\Delta t_{Si}$  removed during oxidation. Since Si was removed on both sides of the wafer, the Si device layer thickness reduction  $\Delta t_{Device} = \frac{1}{2}\Delta t_{Si}$ . Table 5.3 shows the estimated wafer thicknesses after wet oxidation in the CEFIM clean-room and which wafers were selected for further processing at the MiRC.

| W           | afer       | Start   |         | 1 <sup>st</sup> oxida<br>Min we |                     | Af      | <b>čter 2<sup>nd</sup> (</b><br>(48 Mi | Processed<br>further |                            |                                                |

|-------------|------------|---------|---------|---------------------------------|---------------------|---------|----------------------------------------|----------------------|----------------------------|------------------------------------------------|

| I           | No.        | WN      | Vafer   | $\Delta w_{Wafer}$              | $\Delta t_{Device}$ | W Wafer | $\Delta w_{Wafer}$                     | $\Delta t_{Device}$  | $\Sigma \Delta t_{Device}$ |                                                |

|             |            |         | [mg]    |                                 | [nm]                | [m      | g]                                     | [r                   | nm]                        | at                                             |

|             | S1         | 3616.24 | 3612.81 | 3.43                            | 161                 | 3609.66 | 3.15                                   | 148                  | 310                        | MiRC                                           |

|             | S2         | 3632.64 | 3629.11 | 3.53                            | 166                 | 3625.95 | 3.16                                   | 149                  | 315                        | CEFIM                                          |

|             | <b>S</b> 3 | 3593.39 | 3589.85 | 3.54                            | 167                 | 3586.61 | 3.24                                   | 152                  | 319                        | MiRC                                           |

|             | S4         | 3563.90 | 3560.36 | 3.54                            | 167                 | 3556.82 | 3.54                                   | 167                  | 333                        | CEFIM                                          |

|             | S5         | 3605.66 | 3602.13 | 3.53                            | 166                 | 3598.82 | 3.31                                   | 156                  | 322                        | MiRC                                           |

|             | <b>S6</b>  | 3592.44 | 3588.92 | 3.52                            | 166                 | 3585.53 | 3.39                                   | 160                  | 325                        | MiRC                                           |

|             | <b>S</b> 7 | 3564.79 | 3561.26 | 3.53                            | 166                 | 3557.83 | 3.43                                   | 161                  | 328                        | CEFIM                                          |

|             | S8         | 3609.29 | 3605.76 | 3.53                            | 166                 | 3602.46 | 3.30                                   | 155                  | 321                        | MiRC                                           |

|             | S9         | 3630.30 | 3626.72 | 3.58                            | 168                 | 3623.40 | 3.32                                   | 156                  | 325                        | CEFIM                                          |

| S           | 510        | 3647.60 | 3644.05 | 3.55                            | 167                 | 3640.69 | 3.36                                   | 158                  | 325                        | CEFIM                                          |

|             |            |         |         |                                 |                     |         |                                        |                      |                            |                                                |

| SIC         | Max        | 3616.24 | 3612.81 | 3.54                            | 167                 | 3609.66 | 3.39                                   | 160                  | 325                        | $\Rightarrow t_{Final} \geq 75 \text{ nm}$     |

| Vafe        | Avg        | 3603.40 | 3599.89 | 3.51                            | 165                 | 3596.62 | 3.28                                   | 154                  | 319                        | $\Rightarrow t_{Final} \approx 181 \text{ nm}$ |

| MiRC Wafers | Min        | 3592.44 | 3588.92 | 3.43                            | 161                 | 3585.53 | 3.15                                   | 148                  | 310                        | $\Rightarrow t_{Final} \leq 290 \text{ nm}$    |

| Mil         | Δ[%]       | 0.66    | 0.66    | 3.13                            | 3                   | 0.67    | 7.32                                   | 7                    | 5                          |                                                |

Table 5.3. Siegert SOI wafer thinning at CEFIM.

Department of Electrical, Electronic and Computer Engineering University of Pretoria

The five wafers to be processed further at the GT MiRC were optically selected to have the least thickness variation. This could be judged by counting the interference rings visible on the surface of the wafer.

Reflective spectrometer measurements at the MiRC showed that the SOI device layer thicknesses were in fact quite a bit thicker than estimated from wafer weights at the CEFIM. Table 5.4 shows the MiRC-measured SOI device layer thicknesses and the required oxidation times for each wafer to obtain the desired 150 nm layer thickness.

|            |                 |      |     | Me  | easu | red |     |     |     | To be | After Removal |     | Desired | T <sub>Oxidation</sub> |              |

|------------|-----------------|------|-----|-----|------|-----|-----|-----|-----|-------|---------------|-----|---------|------------------------|--------------|

| Wafer      | Measurement     | BOX  | Mid | N   | Е    | S   | w   | Avg | Min | Max   | removed       | Min | Max     | t <sub>SiO2</sub>      | @<br>1100 °C |

| No.        | Set             |      |     |     |      |     | ÷   |     | [1  | nm]   |               |     |         |                        | 1100 C       |

| S1         | 1 <sup>st</sup> | 9795 | 312 | 460 | 392  | 259 | 260 |     | 258 | 461   | 188           | 70  | 273     | 426                    | 49 Min       |

| 51         | $2^{nd}$        |      | 308 | 459 | 387  | 258 | 279 | 550 | 250 | 401   | 100           | 10  | 215     | 420                    | 49 Willi     |

| <b>S</b> 3 | 1 <sup>st</sup> | 9829 | 280 | 211 | 291  | 340 | 167 | 261 | 167 | 340   | 111           | 56  | 230     | 251                    | 21 Min       |

| 55         | $2^{nd}$        |      | 260 | 229 | 331  | 317 | 180 |     | 107 | 540   | 111           | 50  | 250     | 231                    | 21 101111    |

| S5         | 1 <sup>st</sup> | 9811 | 444 | 408 | 401  | 467 | 417 |     | 393 | 468   | 282           | 111 | 186     | 640                    | 1 h 37 Min   |

| 55         | $2^{nd}$        |      | 463 | 409 | 393  | 468 | 448 | +52 | 575 | 400   | 202           | 111 | 100     | 040                    | 1 II 37 WIII |

| <b>S</b> 6 | 1 <sup>st</sup> | 9826 | 525 | 560 | 436  | 423 | 513 | 497 | 123 | 599   | 347           | 76  | 252     | 789                    | 2 h 19 Min   |

| 30         | $2^{nd}$        |      | 536 | 599 | 439  | 430 | 512 |     | 423 | 577   | 547           | 70  | 232     | 109                    | 2 II 19 WIII |

| <b>S</b> 8 | $1^{st}$        | 9763 | 299 | 348 | 258  | 295 | 392 | 316 | 258 | 392   | 166           | 93  | 227     | 376                    | 40 Min       |

| 50         | $2^{nd}$        |      | 297 | 349 | 282  | 293 | 343 | 510 | 238 | 372   | 100           | 75  | 221     | 570                    | +0 WIII      |

|            | Average         | 9805 | 372 | 403 | 361  | 355 | 351 | 369 | 167 | 599   | 219           |     |         |                        |              |

Table 5.4. Siegert SOI wafer thicknesses measured at the MiRC after oxidation at CEFIM.

Above table also shows that the original device layer thicknesses averaged about 369 nm + 319 nm = 688 nm, which is above the maximum Siegert wafer thickness specification of 500 nm + 100 nm = 600 nm.

Table 5.5 shows the final measured silicon device-layer thicknesses after thermal oxidation in the Lindburg furnace.

| Wafer      |        |       |       |       | Thio  | ckness [nm | ]     |                               |       |

|------------|--------|-------|-------|-------|-------|------------|-------|-------------------------------|-------|

| No.        | Centre | North | East  | South | West  | Random     | Min   | Average<br>(Average – 150 nm) | Max   |

|            | 124.8  | 255.8 | 174.2 | 44.8  | 63.6  | 106.6      |       |                               |       |

|            | 129.9  | 273.9 | 188.2 | 50.2  | 77.3  | 143.6      |       | 132.4                         |       |

| <i>S1</i>  |        |       |       |       |       | 112.5      | 44.8  | (-17.6)                       | 273.9 |

|            |        |       |       |       |       | 133.5      |       | (17.0)                        |       |

|            |        |       |       |       |       | 107.6      |       |                               |       |

|            | 178.3  | 112.7 | 187.6 | 226.0 | 75.6  | 145.6      |       |                               |       |

| <i>S3</i>  | 193.1  | 111.4 | 214.0 | 208.0 | 65.5  | 144.6      | 65.5  | 154.3                         | 226.0 |

| 35         |        |       |       |       |       | 148.1      | 05.5  | (+4.3)                        | 220.0 |

|            |        |       |       |       |       | 150.0      |       |                               |       |

| <i>S5</i>  | 152.1  | 139.9 | 119.5 | 173.3 | 171.6 |            | 119.5 | 157.2                         | 197.7 |

| 35         | 154.4  | 133.5 | 162.0 | 197.7 | 167.8 |            | 119.5 | (+7.2)                        | 197.7 |

| S6         | 209.0  | 282.7 | 105.1 | 128.0 | 148.8 |            | 105.1 | 173.3                         | 286.5 |

| 30         | 183.6  | 286.5 | 121.8 | 120.5 | 146.9 |            | 105.1 | (+23.3)                       | 280.3 |

|            | 138.2  | 186.3 | 102.6 | 105.3 | 148.7 | 123.3      |       |                               |       |

|            | 118.0  | 216.3 | 98.7  | 120.5 | 157.7 | 132.1      |       |                               |       |

|            | 131.6  |       |       |       |       | 104.0      |       |                               |       |

| <i>S</i> 8 |        |       |       |       |       | 132.8      | 98.7  | 132.3                         | 216.3 |

|            |        |       |       |       |       | 100.1      |       | (-17.7)                       |       |

|            |        |       |       |       |       | 148.3      |       |                               |       |

|            |        |       |       |       |       | 144.3      |       |                               |       |

| Average    | 155.7  | 199.9 | 147.4 | 137.4 | 122.4 | 129.3      | 44.8  | 149.9                         | 286.5 |

| Table 5.5. | Wafer | thicknesses | after | thinning | oxidation | (with | aimed | 150 m | m average). |

|------------|-------|-------------|-------|----------|-----------|-------|-------|-------|-------------|

|            |       |             |       |          |           |       |       |       |             |

The average device-layer thicknesses are very close to the desired 150 nm, but *S1* and *S8* were about 18 nm thinner and *S6* was about 23 nm thicker than the desired 150 nm device layer thickness.

#### 5.2. Blanket B Implant

Since the initial device-layer *p*-doping of  $4 \cdot 10^{14}$  cm<sup>-3</sup> of the supplied wafers (Table 4.1) was too low, a blanket B implant was necessary to achieve the desired impurity concentration of about  $10^{18}$  cm<sup>-3</sup>.

As shown in Table 5.6, the wafers had to be annealed after the B implantation at Core Systems<sup>3</sup> in California.

| Step | Action                                                            | Equipment      | Material | Facility     | Graphical representation |

|------|-------------------------------------------------------------------|----------------|----------|--------------|--------------------------|

| 2a   | Blanket B implant<br>7·10 <sup>14</sup> cm <sup>-2</sup> @ 10 keV | Ion implanter  | -        | Core Systems | p Si<br>BOX              |

| 2b   | Annealing<br>30 Min @ 950 °C                                      | Tystar Furnace | $N_2$    | MiRC         | Handle                   |

Table 5.6. Blanket B implant processing steps.

The B implant was actually performed twice. The first implant  $(7.24 \cdot 10^{14} \text{ cm}^{-2} \text{ at } 24 \text{ keV})$  occurred after the first oxidation thinning oxidation at CEFIM, but after receiving the wafers at the MiRC it was noticed that the first B implant was based on the erroneously derived Si thickness of about 181 nm. The resultant impurity concentration after Si thinning oxidation from about 369 nm to 150 nm was too low (see Table 5.7) and required another "top-up" B implant.

<sup>&</sup>lt;sup>3</sup> Core Systems, A Subsidiary of Implant Sciences Corporation, 1050 Kiefer Road, Sunnyvale, CA

Manufacture

|              |                                                | Resistivity |         |         |         |         |         |         |         |     |          |  |  |  |  |

|--------------|------------------------------------------------|-------------|---------|---------|---------|---------|---------|---------|---------|-----|----------|--|--|--|--|

| Wafer<br>No. |                                                |             |         |         |         | Avg     | Max     | Δ       | $N_A$   |     |          |  |  |  |  |

|              |                                                | [Ω-cm]      |         |         |         |         |         |         |         |     |          |  |  |  |  |

| <i>S1</i>    | 3.93E-1                                        | 3.74E-2     | 4.22E-2 | 2.34E-1 | 3.98E-1 | 3.74E-2 | 2.21E-1 | 3.98E-1 | 3.61E-1 | 163 | 8.27E+16 |  |  |  |  |

| <i>S3</i>    | 1.79E-2                                        | 3.90E-2     | 2.06E-2 | 1.87E-2 | 1.97E-1 | 1.79E-2 | 5.86E-2 | 1.97E-1 | 1.79E-1 | 306 | 5.22E+17 |  |  |  |  |

| <i>S5</i>    | 9.49E-2                                        | 1.98E-1     | 1.06E-1 | 7.91E-2 | 7.94E-2 | 7.91E-2 | 1.11E-1 | 1.98E-1 | 1.19E-1 | 107 | 2.14E+17 |  |  |  |  |

| <i>S6</i>    | 9.11E-2                                        | 7.18E-2     | 2.12E-1 | 3.77E-1 | 1.16E-2 | 1.16E-2 | 1.53E-1 | 3.77E-1 | 3.65E-1 | 240 | 1.38E+17 |  |  |  |  |

| <b>S</b> 8   | 8.00E-2                                        | 6.28E-2     | 2.34E-1 | 1.45E-1 | 2.98E-2 | 2.98E-2 | 1.10E-1 | 2.34E-1 | 2.04E-1 | 185 | 2.17E+17 |  |  |  |  |

|              | <b>Overall</b> 1.16E-2 9.35E-2 3.98E-1 3.86E-1 |             |         |         |         |         |         |         |         |     | 2.73E+17 |  |  |  |  |

Table 5.7. 4-point probe measured SOI wafer resistivity and derived B doping.

Wafers *S1*, *S3*, *S6* and *S8* (with average thickness of 144 nm) were sent to Core Systems for the top-up B implant. Wafer *S5* was arbitrarily chosen as a test-wafer with which to continue processing experiments.

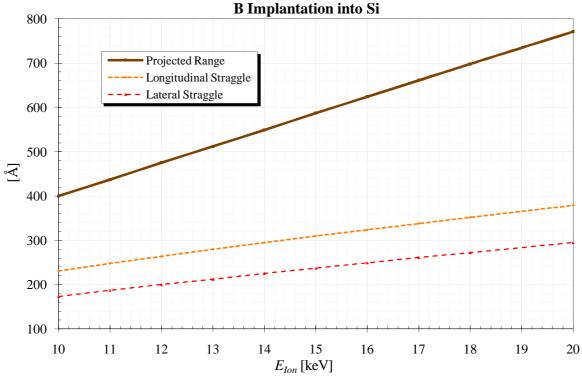

Figure 3.1 shows that the average B concentration in the silicon is approximately reduced by a factor 45 during all oxidations (reducing the finger thickness from 150 nm to about 30 nm). This means that a final average B concentration of  $10^{18}$  cm<sup>-3</sup> (when the fingers are oxidized down to about 30 nm) requires an initial doping concentration of about 4.5 $\cdot 10^{19}$  cm<sup>-3</sup> when the fingers are still 150 nm thick. From Table 5.7 the geometrical mean B doping concentration of *S1*, *S3*, *S6* and *S8* was about  $1.9 \cdot 10^{17}$  cm<sup>-3</sup>. This means that the required implant dose  $D = (4.5 \cdot 10^{19} \text{ cm}^{-3} - 1.9 \cdot 10^{17} \text{ cm}^{-3})(144 \text{ nm}) \approx 6.5 \cdot 10^{14} \text{ cm}^{-2}$ .

From Table 5.5 the implant energy is calculated for a range  $R_P$  equal to half the minimum Si thickness  $t_{Min}$ :  $R_P = t_{Min}/2 = 44.8 \text{ nm}/2 = 224 \text{ Å}$ .

Data provided by Core Systems in Figure 5.1 shows that B ions implanted at their lowest acceleration energy of 10 keV penetrate to a range of about 400 Å, which was sufficient.

Figure 5.1. B implantation into Si range and straggle.

During wafer shipment to Core Implantation Systems in California for B implantation, wafer *S6* unfortunately broke and had to be excluded from subsequent processing.

# 5.3. Si Island Definition

Table 5.8 below shows the processing steps taken to create the Si islands on the BOX.

| Step | Action                                                             | Equipment                        | Material                                                                                                               | Facility | Graphical representation                                  |

|------|--------------------------------------------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------|----------|-----------------------------------------------------------|

| 3a   | SiO <sub>2</sub> deposition<br>1 Min 20 s: 71 nm<br>(Addendum D.3) | Unaxis<br>PECVD                  | -                                                                                                                      |          | SiO2<br>p - Si<br>BOx<br>Si                               |

| 3b   | Surface Dehydration<br>(10 Min @ 120 °C)                           | Oven                             | -                                                                                                                      |          |                                                           |

| 3с   | PR application<br>(4 000 RPM: 1.2 μm)                              | Spin-coater                      | SC1813                                                                                                                 |          | $\begin{tabular}{ c c c c c c c c c c c c c c c c c c c$  |

| 3d   | Soft-bake PR<br>(1 Min @ 115 °C)                                   | Hot-plate                        | -                                                                                                                      | -        |                                                           |

| 3e   | Pattern transfer/ exposure<br>$(t_{Exposure} = 3.6 \text{ s})$     | Karl Süss<br>MA6<br>mask aligner | Si Island<br>Photo-mask                                                                                                |          | Resist<br>SiO <sub>2</sub><br>P<br>SiO <sub>2</sub><br>Si |

| 3f   | Develop PR<br>(1 Min)                                              | Fume hood                        | FM319                                                                                                                  | MiRC     | Resist<br>SiO <sub>2</sub><br>P                           |

| 3g   | Hard-bake PR<br>(110 °C, 30 Min)                                   | Hot-plate                        | -                                                                                                                      |          | BOx<br>Handle                                             |

| 3h   | SiO <sub>2</sub> etch<br>5 Min: 71 nm<br>(Appendix D.4.3.2)        | Vision                           | _                                                                                                                      |          | Resist       SiO2       P       BOx       Handle          |

| 3i   | Si etch<br>2 Min: 286 nm<br>(Addendum D.4.2.1)                     | RIE                              | _                                                                                                                      |          | BOx<br>Handle                                             |

| 3j   | PR strip                                                           |                                  | 10 Min                                                                                                                 |          |                                                           |

| 3k   | Wash wafers                                                        | Fume-hood                        | Piranha<br>4:1<br>98 % H <sub>2</sub> SO <sub>4</sub> : 30 % H <sub>2</sub> O <sub>2</sub><br>560 ml + 140 ml = 700 ml |          | BOx<br>Handle                                             |

Table 5.8. Si island definition processing steps.

Department of Electrical, Electronic and Computer Engineering University of Pretoria

Manufacture

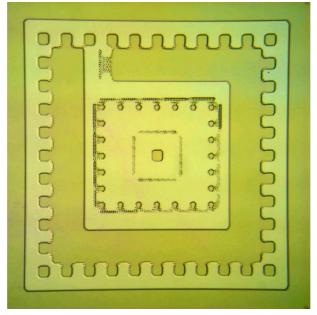

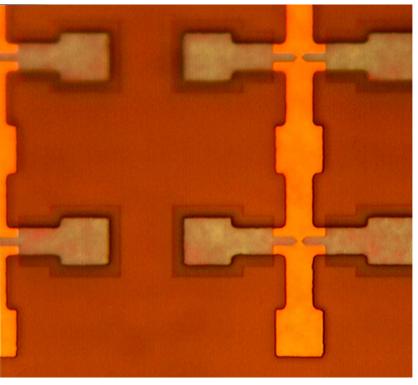

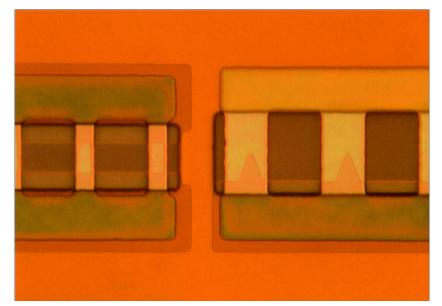

The first photolithographic Si island definition consumed three days due to problems with the Karl Süss MA6 TSA mask aligner. The initial photolithographic exposures were out of focus as shown in Figure 5.2.

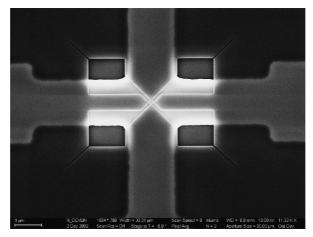

Figure 5.2. Bad Chip1 Si Island exposure (step 3f).

After investigating many possible causes (including wafer warp and PR adhesion), it was found that the mask aligner had a cut in its wafer holder vacuum seal and that its wafer-holding screws were too far turned out for the thinner than usual Siegert SOI wafers. After faultfinding and fixing the mask aligner, decent photolithographic exposures, as shown in Figure 5.3, were achieved and subsequent photolithography was successful.

Figure 5.3. Proper Chip2 Si Island exposure (step 3f).

## 5.4. As Implant

Table 5.9 lists the steps involved in implanting the As where  $n^+$  diffusions are intended.

| Step | Action                                                                | Equipment    | Material             | Facility | Graphical representation |

|------|-----------------------------------------------------------------------|--------------|----------------------|----------|--------------------------|

| 4a   | SiO <sub>2</sub> deposition<br>3 Min 32 s: ≈ 200 nm<br>(Addendum D.3) | Unaxis PECVD | Control wafer pieces |          | p<br>BOx<br>Si           |

| 4b   | Apply positive EBL resist<br>(1 Min 2000 RPM: 500 nm)                 | Spin-coater  | ZEP520A EBL resist   |          | EBL resist               |

| 4c   | Soft-bake EBL resist<br>(180 °C for 2 Min)                            | Hot-plate    | -                    |          | BOx<br>Si                |

| 4d   | EBL exposure<br>(200 µC/cm <sup>2</sup> )                             | JEOL EPG     | As (EBL) file        |          | BOx<br>Si                |

| 4e   | Develop EBL resist<br>(2 Min)                                         | Fume hood    | Amyl Acetate         | MiRC     | EBL resist               |

| 4f   | Wafer rinse<br>(30 sec IPA immersion)                                 |              | IPA                  |          | BOx<br>Si                |

| 4g   | SiO <sub>2</sub> etch<br>13 Min: 210 nm<br>(Addendum D.4.3.2)         | Vision RIE   | Control wafer pieces |          | P<br>BOx<br>Si           |

| 4h   | ZEP de-scumming                                                       |              | O <sub>2</sub>       |          | SiO                      |

| 4i   | Dehydration bake<br>(10 Min @ 120 °C)                                 | Oven         | -                    |          | BOx<br>Si                |

| 4j   | PR application<br>(4500 RPM: 1.1 um)                                  | Spin-coater  | SC1813               |          | BOx<br>Si                |

| 4k | Pattern transfer exposure<br>Mask EBL clusters with tape<br>4s  | Mask aligner     | As (Photo)<br>mask                                                        |                 | BOx<br>Si                                                                                                                                                                                                                             |

|----|-----------------------------------------------------------------|------------------|---------------------------------------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 41 | Develop & hard-bake PR                                          | Fume hood & oven | MF319 developer                                                           | MiRC            | BOx<br>Si                                                                                                                                                                                                                             |

| 4m | SiO <sub>2</sub> etch<br>(Si also etched!)<br>13 Min: 210 nm    | Vision RIE       | Control wafer pieces                                                      |                 | BOx<br>Si                                                                                                                                                                                                                             |

| 4n | PR removal<br>&<br>wafer clean                                  | Fume-hood        | Piranha<br>H <sub>2</sub> SO <sub>4</sub> & H <sub>2</sub> O <sub>2</sub> |                 | BOx<br>Si                                                                                                                                                                                                                             |

| 40 | As implant<br>(1.5·10 <sup>14</sup> cm <sup>-2</sup> @ 118 keV) | Ion implanter    | As                                                                        | Core<br>Systems | $ \begin{array}{c} \downarrow $ |

| 4p | Anneal<br>30 Min @ 950 °C                                       | AET RTP          | $N_2$                                                                     | MiRC            | SiO <sub>2</sub><br>n+ p<br>BOx<br>Handle                                                                                                                                                                                             |

| 4q | SiO <sub>2</sub> etch<br>(Addendum D.2)                         | Fume hood        | BOE                                                                       |                 | n+ p<br>BOX<br>Handle                                                                                                                                                                                                                 |

Before the wafers could be sent to Core Systems for As implantation, holes had to patterned and etched into a SiO<sub>2</sub> masking layer that should be thick enough to prevent As from penetrating through it and reach the Si underneath it. Since it was determined that on some wafers an average of about 18 nm of the SiO<sub>2</sub> mask was not completely etched away in the  $n^+$ implantation holes, it was decided to increase the As implantation acceleration energy to penetrate these thin SiO<sub>2</sub> layers.

Data supplied by Core Systems in Figure 5.4 shows that As implanted at  $E_{Ion} = 118$  keV penetrates to a range  $Rp_{As\_Si}$  of about 80 nm with lateral straggle  $\Delta R \perp_{As\_Si}$  of about 18 nm.

Figure 5.4. As implant range  $Rp_{As\_Si}$ , longitudinal  $\Delta Rp_{As\_Si}$  and transverse straggle  $\Delta R \perp_{As\_Si}$  in Si.

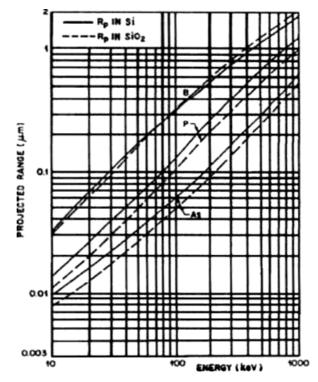

Figure 5.5 shows that As implanted into SiO<sub>2</sub> at 118 keV will have a range of about 58 nm.

Figure 5.5. Projected ion implantation range  $Rp_{As\_SiO2}$  in SiO<sub>2</sub> [91].

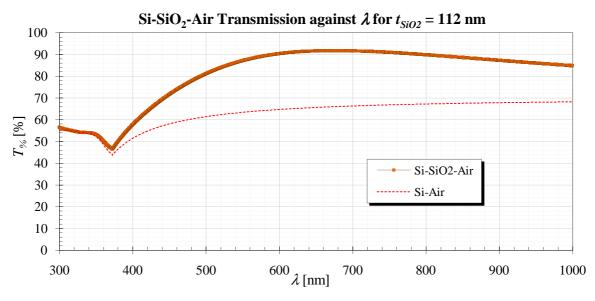

Since no straggle data was found for As implantation into SiO<sub>2</sub>, it is assumed that a SiO<sub>2</sub> mask thickness of twice the projected range  $Rp_{As\_SiO2}$  should be sufficient to block the As implant from reaching the underlying Si. Therefore  $t_{SiO2} > 2Rp_{As\_SiO2} = 116$  nm.

Figure 5.6 shows an *Opposite-injector* As mask pattern generated in the EBL resist during step 4f.

Figure 5.6. Arsenic EBL pattern in ZEP on oxide mask (step 4f).

Figure 5.7 shows the Arsenic mask spacing for the  $n^+pn^+$  punch-through finger junctions after SiO<sub>2</sub> removal in the Vision RIE in step 4g.

Figure 5.7. Arsenic EBL pattern after RIE (step 4g).

The 315 nm wide vertical stripe is the remaining  $SiO_2$  that masks the intermediate region of the punch-through devices from the As implant.

Figure 5.8 shows an optical microscope image of patterned holes in the  $SiO_2$  Arsenic masking layer at step 4h before Arsenic implant.

Figure 5.8. Arsenic EBL pattern before implant (step 4h).

Figure 5.9 shows the Arsenic implant holes etched into the  $SiO_2$  mask generated by the photolithographic process at step 4m.

Figure 5.9. After Arsenic Photo RIE (step 4m).

## 5.5. Finger Definition

Table 5.10 shows the physical manufacturing steps involved in defining and etching the finger spacing strips into the Si.

| Step | Action                                                                                                                                                                           | Equipment  | Material                   | Facility | Graphical representation                                                                                                         |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------|

| 5a   | EBL:<br>EBL steps 4b to 4h<br>600 nm ZEP<br>Align to <i>Si Island</i> EBL marker<br>( <i>w<sub>Finger</sub></i> = 2 <i>h<sub>Finger</sub></i> , <i>n<sub>Finger</sub></i> = 100) | JEOL EPG   | Finger Spacing<br>EBL file |          | Holes in EBL resist<br>EBL resist<br>+<br>p<br>p<br>t<br>t<br>t<br>t<br>t<br>t<br>t<br>t<br>t<br>t<br>t<br>t<br>t<br>t<br>t<br>t |

| 5b   | Si etch                                                                                                                                                                          | ICP        | -                          | MiRC     | n+ p                                                                                                                             |

| 5c   | EBL resist removal                                                                                                                                                               | Vision RIE | $O_2$                      |          |                                                                                                                                  |

| 5d   | Si finger width measurement                                                                                                                                                      | SEM        | -                          |          |                                                                                                                                  |

| 5e   | Wafer clean                                                                                                                                                                      | Wet-bench  | Piranha                    |          | n+ p<br>BOX                                                                                                                      |

| Table | 5 10  | Finger | definition | nrocess | flow |

|-------|-------|--------|------------|---------|------|

| Table | 5.10. | ringer | definition | process | now. |

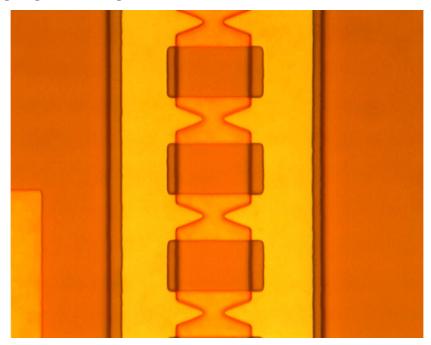

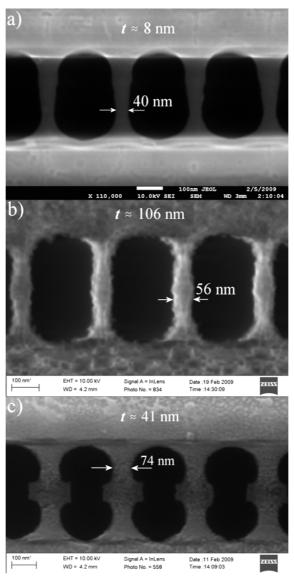

The SEM image in Figure 5.10 shows the finger spacing pattern in the ZEP EBL resist.

Figure 5.10. EBL finger spacing pattern (step 5a).

Figure 5.11 depicts a closer view of the EPG-written finger spacing pattern in the ZEP.

Figure 5.11. EBL finger spacing detail (step 5a).

Figure 5.12 shows the EBL-written ZEP holes that allow etching the superfluous Si away around the injector fingers.

Figure 5.12. EBL injector spacing definition (step 5a).

The importance of characterizing the processing equipment to determine limitations and adapt the process accordingly can be illustrated by comparing the etch profiles of two different RIE systems.

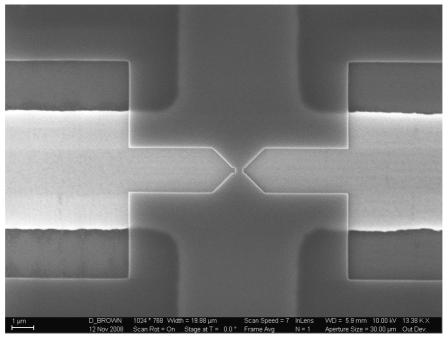

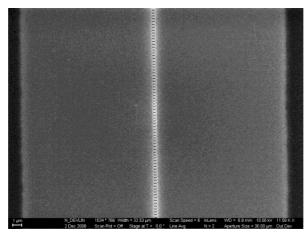

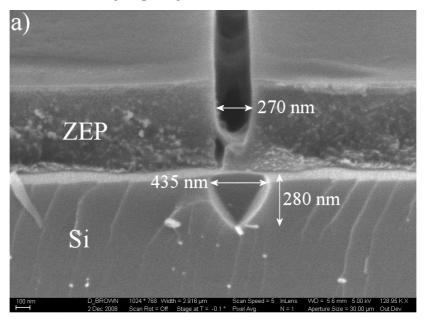

While most oxidation and deposition steps delivered expected results, reactive ion-beam etching (RIE) on the recommended Vision Oxide RIE machine caused some uniformity and small-feature geometry etching variation problems. It was found that RIE etch rates were dramatically influenced by narrow masks and that dedicated etch and SEM cross-sectioning trial runs were necessary. Since the test designs, material and scanning electron microscope (SEM) availability were highly limited, this work had to rely on etch tests performed on a test wafer piece previously EBL-written by Devin Brown, the EBL specialist at the MiRC. Figure 5.13 shows that while the Vision Oxide RIE has an excellent etch selectivity towards Si when the ZEP EBL resist was used as a mask, its excessive horizontal etch-spread made it unsuitable for etching the 100 nm wide finger spacing slits.

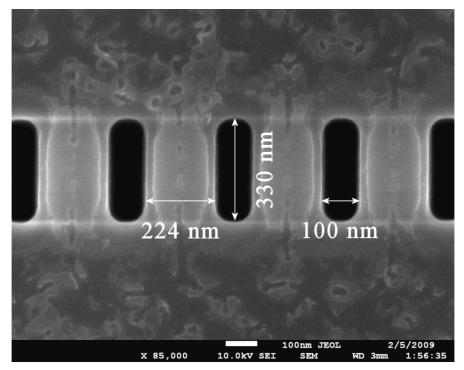

Figure 5.13. 100 nm Vision Oxide RIE Si groove etch test.

The Vision Oxide RIE is therefore not suitable for etching the 100 nm finger spacing slits into the Si since the resultant isotropic chemical etch width of up to 458 nm would completely remove the Si fingers. For this reason, the Plasmatherm ICP RIE, which was not included in the equipment training-program and was consequently not characterized extensively, had to be used.

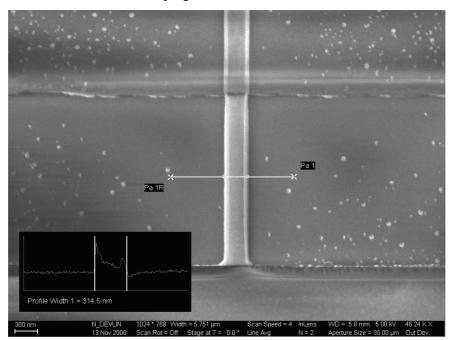

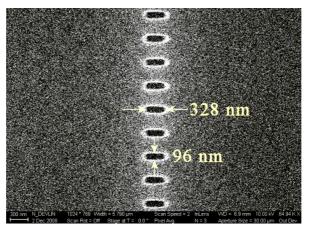

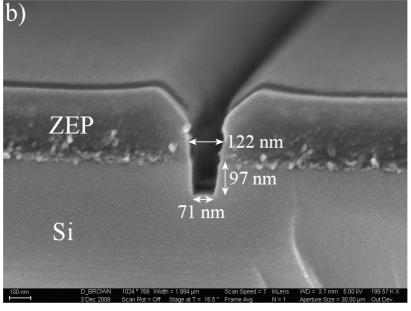

Figure 5.14 shows that the PlasmaTherm ICP, which was eventually used for the finger spacing etching, exhibited a very narrow etch profile, but suffered from a relatively poor etch selectivity of only about 0.3.

Figure 5.14. 100 nm ICP groove etch test.

The ICP could etch the 100 nm wide lines in the ZEP into about 71 nm wide and 97 nm deep grooves into the Si in 80 sec.

Figure 5.14 also shows the bad ICP etch selectivity of about 0.3. The etch selectivity is calculated as the etch rate ratio of desired material (in this case Si) to mask (in this case ZEP). The Plasmatherm ICP etched Si at an average rate of  $R_{Si} = 97$  nm/80 sec = 73 nm/Min while removing the ZEP at the surface and sidewalls with an average rate of  $R_{ZEP} = (600 \text{ nm} - 322 \text{ nm})/80 \text{ sec} = 209 \text{ nm/Min}$ . The ICP etch selectivity therefore is  $R_{Si}/R_{ZEP} \approx 0.3$ . Since the testmaterial used in above experiments had slightly different characteristics compared to the used wafers and the Plasmatherm ICP had a very low etch selectivity a best estimate etch time had to be compromised upon to etch sufficient silicon without completely removing the ZEP mask. It was decided that 2 Min 46 sec would only remove 582 nm of the 600 nm thick ZEP while still etching the thickest Si island thickness of 280 nm.

Due to Si island thickness variations, the finger definition ICP etch sufficiently formed all fingers but unfortunately the material around the injection devices was not completely removed before the ZEP EBL resist was also completely removed (see Figure 5.22).

Manufacture

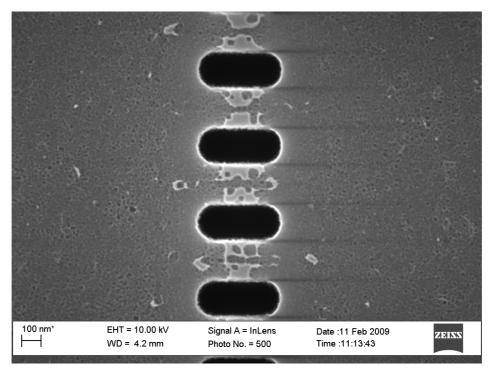

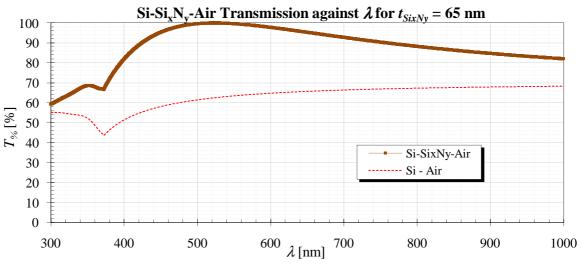

The SEM image in Figure 5.15 shows the finger spacing holes ICP-etched into the Si that remained once the ZEP EBL resist was de-scummed after the finger definition RIE (before thinning oxidation).

Figure 5.15. Finger spacing holes in the about 117 nm thick Si after RIE.

The device imaged above becomes a punch-through light source on wafer S3, cluster 1, Chip 2.

Although the EBL exposure and PlasmaTherm ICP etch resulted in rounded corners of the holes this is not critical to the junctions in the fingers.

## 5.6. Finger Thinning Oxidation

In the finger thinning oxidation processing steps in Table 5.11, the wafer was covered with a  $Si_xN_y$  masking layer. Oxidation windows were then etched into the  $Si_xN_y$  through which the Si fingers could be selectively oxidized thinner.

| Step | Action                                                                                                                  | Equipment           | Material                                                | Facility | Graphical representation                      |

|------|-------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------------------------------------------|----------|-----------------------------------------------|

| 6a   | EBL data preparation                                                                                                    | UNIX<br>workstation | GDS data file                                           |          |                                               |

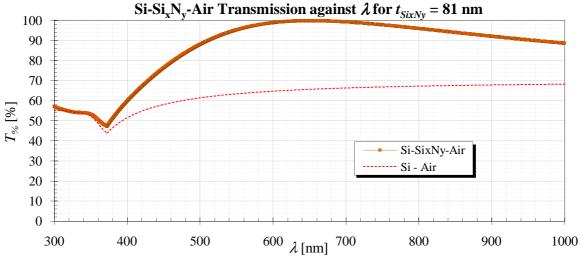

| бb   | Si <sub>x</sub> N <sub>y</sub> deposition<br>Prior SiO <sub>2</sub> for adhesion<br>81 nm: 9 Min 52 s<br>(Addendum D.3) | Unaxis<br>PECVD     | Chlorinated silane<br>NH <sub>3</sub><br>Control pieces |          | n+ p<br>Si <sub>X</sub> Ny                    |