# HIGH VOLTAGE BOOST DC-DC CONVERTER SUITABLE FOR VARIABLE VOLTAGE SOURCES AND HIGH POWER PHOTOVOLTAIC APPLICATION.

by

Fredrick Mukundi Mwaniki

Submitted in partial fulfilment of the requirements for the degree Master of Engineering (Electrical Engineering)

in the

Department of Electrical, Electronic and Computer Engineering Faculty of Engineering, Built Environment and Information Technology

UNIVERSITY OF PRETORIA

February 2013

## SUMMARY

## HIGH VOLTAGE BOOST DC-DC CONVERTER SUITABLE FOR VARIABLE VOLTAGE SOURCES AND HIGH POWER PHOTOVOLTAIC APPLICATION.

by

Fredrick Mukundi Mwaniki

| Supervisor: | Prof M.N. Gitau                                                          |

|-------------|--------------------------------------------------------------------------|

| Department: | Electrical, Electronic and Computer Engineering                          |

| University: | University of Pretoria                                                   |

| Degree:     | Master of Engineering (Electrical Engineering)                           |

| Keywords:   | Tapped-coupled-inductor, interleaving, high step-up DC-DC                |

|             | converter, coupling coefficient, photo-voltaic, digital control, voltage |

|             | regulation                                                               |

Important considerations of a photovoltaic (PV) source are achieving a high voltage and drawing currents with very little ripple component from it. Furthermore, the output from such a source is variable depending on irradiation and temperature. In this research, literature review of prior methods employed to boost the output voltage of a PV source is examined and their limitations identified. This research then proposes a multi-phase tapped-coupled inductor boost DC-DC converter that can achieve high voltage boost ratios, without adversely compromising performance, to be used as an interface to a PV source. The proposed converter achieves minimal current and voltage ripple both at the input and output. The suitability of the proposed converter topology for variable input voltage and variable power operation is demonstrated in this dissertation. The proposed converter is also shown to have good performance at high power levels, making it very suitable for high power applications.

Detailed analysis of the proposed converter is done. Advantages of the proposed converter are explained analytically and confirmed through simulations and experimentally. Regulation of the converter output voltage is also explained and implemented using a digital controller. The simulation and experimental results confirm that the proposed

converter is suitable for high power as well as variable power, variable voltage applications where high voltage boost ratios are required.

#### **OPSOMMING**

## HOOGSPANNING-AANJAER GS-GS OMSETTER GESKIK VIR VERANDERLIKE SPANNINGSBRONNE EN HOË-KRAG-FOTOVOLTAÏESE TOEPASSINGS.

deur

#### Fredrick Mukundi Mwaniki

| Studieleier:   | Prof M.N. Gitau                                                                                                                                              |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Departement:   | Elektriese, Elektroniese en Rekenaar ingenieurswese                                                                                                          |

| Universiteit:  | Universiteit van Pretoria                                                                                                                                    |

| Graad:         | Magister in Ingenieurswese (Elektriese Ingenieurswese)                                                                                                       |

| Sleutelwoorde: | Tapgekoppelde induktor, tussenlaag, hoë spanningsverhoging- GS-<br>GS-omsetter, koppel-koëffisiënt, foto-voltaïese, digitale beheer,<br>spanning regulering, |

|                | spuining regulating,                                                                                                                                         |

Die belangrikste oorwegings vir 'n fotovoltaïese (FV) bron is die bereiking van hoë spanning en die lewering van stroom met 'n baie klein rimpeling-komponent. Die uitset van so 'n bron is 'n veranderlike wat afhang van bestraling en temperatuur. In hierdie navorsing word literatuur oor metodes wat vantevore gebruik is om die uitsetspanning van 'n FV-bron te versterk, ondersoek en die beperkings geïdentifiseer. Hierdie navorsing stel dan 'n multi-fase tapgekoppelde induktor aanjaer GS-GS omsetter voor wat hoë spanning versterker verhoudings kan bereik, sonder om prestasie nadelig te raak, om gebruik te word as 'n koppelvlak na 'n FV-bron. Die voorgestelde omsetter handhaaf minimale stroom en spanning-rimpeling by sowel die inset as die uitset. Die geskiktheid van die voorgestelde omsetter topologie vir veranderlike inset-spanning en veranderlike krag-werking word in hierdie verhandeling gedemonstreer. Die voorgestelde omsetter het getoon dat dit baie geskik is vir hoë krag-toepassings.

Gedetailleerde analise van die voorgestelde omsetter is gedoen. Die voordele word analities verduidelik en deur middel van simulasies asook eksperimenteel bevestig. Regulering van die uitsetspanning word verduidelik en geïmplementeer met behulp van 'n digitale kontroleerder. Die simulasie en eksperimentele resultate bevestig dat hierdie

omsetter uiters geskik is sowel hoë as veranderlike krag, en veranderlike spanning toepassings waar hoë-spanningversterker verhoudings vereis word.

## LIST OF ABBREVIATIONS

| PV     | Photovoltaic                                      |

|--------|---------------------------------------------------|

| MPP    | Maximum Power Point                               |

| AC     | Alternating current                               |

| DC     | Direct current                                    |

| RMS    | Root mean squared                                 |

| EMI    | Electromagnetic interference                      |

| DSP    | Digital signal processor                          |

| PWM    | Pulse width modulation                            |

| RCD    | Resistor-capacitor-diode                          |

| MOSFET | Metal oxide semiconductor field effect transistor |

## AKNOWLEDGEMENTS

I would like to thank God for the time and privilege. I thank my study leader Prof. M.N. Gitau for his invaluable advice, motivation and guidance, my colleague Ahmed Sayyid for the help, my parents for the prayers and patience. I also give thanks to National Hub for Postgraduate Programme in Energy Efficiency and Demand Side Management for the financial support.

## TABLE OF CONTENTS

| СНАРТЕ | R 1 INTRODUCTION 1                                                                    |

|--------|---------------------------------------------------------------------------------------|

| 1.1 P  | ROBLEM STATEMENT 1                                                                    |

| 1.1.1  | Background and context 1                                                              |

| 1.1.2  | Research gap 2                                                                        |

| 1.2 R  | ESEARCH OBJECTIVE AND QUESTIONS                                                       |

| 1.3 H  | YPOTHESIS AND APPROACH 4                                                              |

| 1.4 R  | ESEARCH GOALS 5                                                                       |

| 1.5 R  | ESEARCH CONTRIBUTION 5                                                                |

| 1.6 O  | VERVIEW OF STUDY 5                                                                    |

| СНАРТЕ | R 2 LITERATURE STUDY7                                                                 |

|        | CHAPTER OBJECTIVE                                                                     |

| 2.2 B  | BOOSTING THE VOLTAGE OF THE PV ARRAY                                                  |

| 2.2.1  | The photovoltaic series string                                                        |

| 2.2.2  | PV array- inverter connection                                                         |

| 2.2.3  | Conventional boost DC-DC converter interface of PV array                              |

| 2.2.4  | Cascaded converters                                                                   |

| 2.2.5  | A DC-DC flyback converter                                                             |

| 2.2.6  | Step-up converters with coupled inductors 11                                          |

| 2.2.7  | Interleaved boost converters                                                          |

| 2.2.8  | Tapped-coupled boost converter15                                                      |

| 2.2.9  | Other proposed boost converters in the literature                                     |

| 2.3 SO | OLAR RESOURCE 17                                                                      |

| 2.3.1  | Solar array characteristics                                                           |

| 2.3.2  | Mismatch errors 19                                                                    |

| 2.3.3  | MPPT schemes 20                                                                       |

|        | ULTI-PHASE INTERLEAVED-TAPPED-COUPLED-INDUCTOR BOOST<br>ONVERTER WITH DIGITAL CONTROL |

| CHAPTER 3   | BOOST CONVERTER WITH TAPPED-COUPLED-INDUCTORS                                                           |

|-------------|---------------------------------------------------------------------------------------------------------|

| ••••••      |                                                                                                         |

| 3.1 OPERA   | ATION OF THE CONVERTER 24                                                                               |

| 3.3.1 Ideal | characteristics                                                                                         |

| 3.1.2 Non-  | -ideal characteristics                                                                                  |

| 3.1.3 Inpu  | t and capacitor current RMS ripple derivation                                                           |

|             | L-SIGNAL MODEL OF THE SINGLE-PHASE TAPPED-COUPLED-<br>CTOR BOOST CONVERTER                              |

| 3.3 CHAPT   | ER CONCLUSION                                                                                           |

|             | PROPOSED MULTI-PHASE BOOST CONVERTER WITH                                                               |

| TAPPED-COU  | PLED-INDUCTORS                                                                                          |

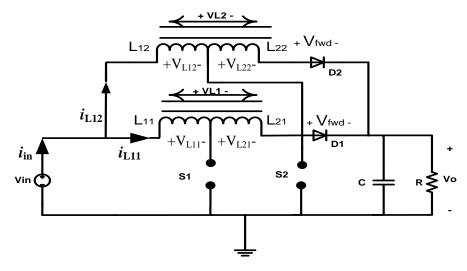

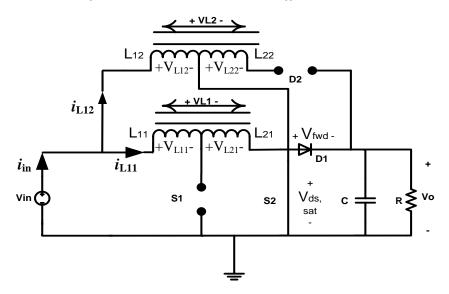

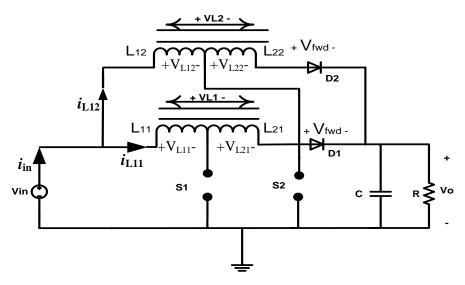

|             | OGY DERIVATION OF THE PROPOSED INTERLEAVED MULTI-<br>E BOOST CONVERTER WITH TAPPED-COUPLED INDUCTORS 44 |

|             | YSIS OF A TWO-PHASE INTERLEAVED TAPPED-COUPLED<br>CTOR BOOST CONVERTER 48                               |

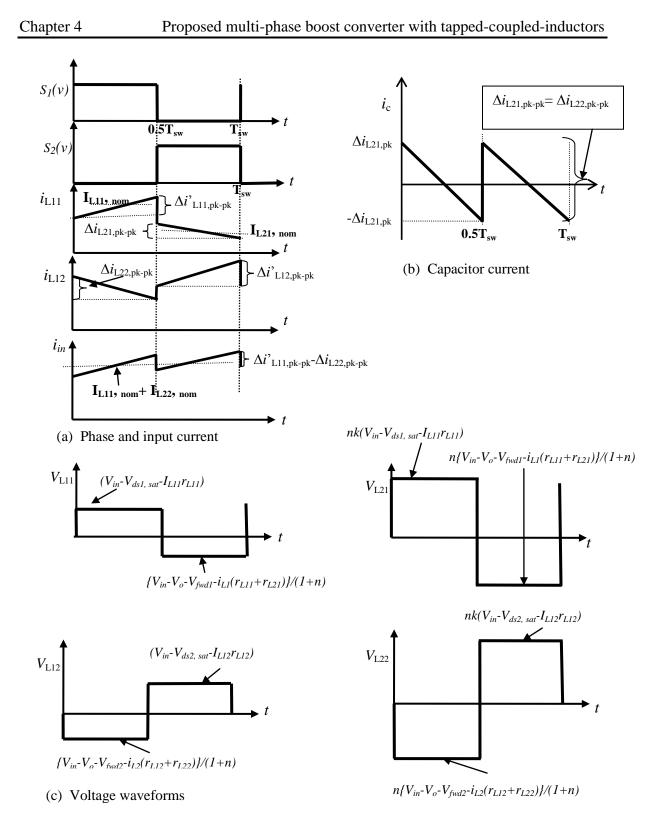

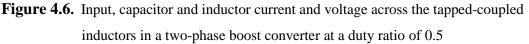

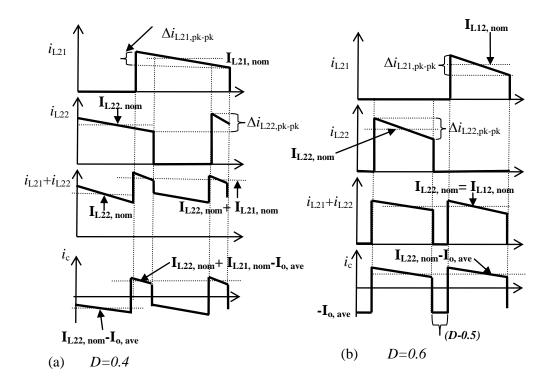

| 4.2.1 Oper  | ation Analysis 48                                                                                       |

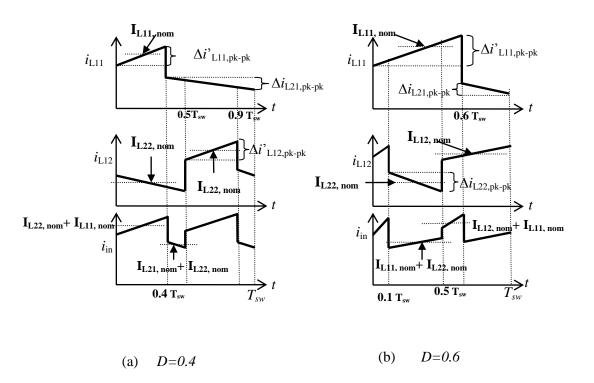

| 4.2.2 Deriv | vation of analytical expressions for average, RMS and ripple input current,                             |

| and         | output capacitor RMS current56                                                                          |

|             | LLING OF A TWO-PHASE INTERLEAVED TAPPED-COUPLED-<br>CTOR BOOST CONVERTER 60                             |

| 4.4 CHAPT   | TER CONCLUSION                                                                                          |

| CHAPTER 5   | SYSTEM DESIGN                                                                                           |

| 5.1 SYSTE   | EM SPECIFICATIONS 69                                                                                    |

| 5.2 COMP    | ONENT SELECTION                                                                                         |

| 5.2.1 Coup  | pled Inductors sizing and design71                                                                      |

| 5.2.2 Activ | ve switch77                                                                                             |

| 5.2.3 Outp  | out diode                                                                                               |

| 5.2.4 Outp  | ut Capacitor                                                                                            |

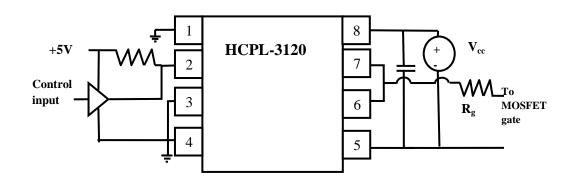

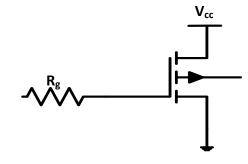

| 5.2.5 Swite | ch gate drive                                                                                           |

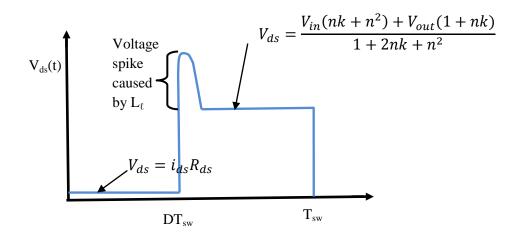

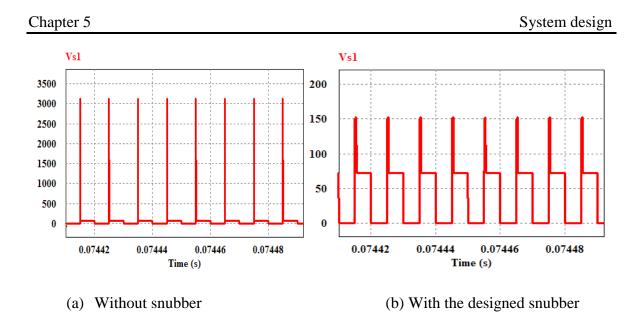

| 5.2.6 Volta | age clamp snubber                                                                                       |

| 5.3 CHAPT   | TER CONCLUSION                                                                                          |

| CHAPTER 6   | SYSTEM CONTROL                                                                                          |

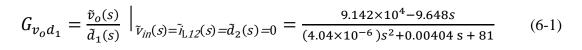

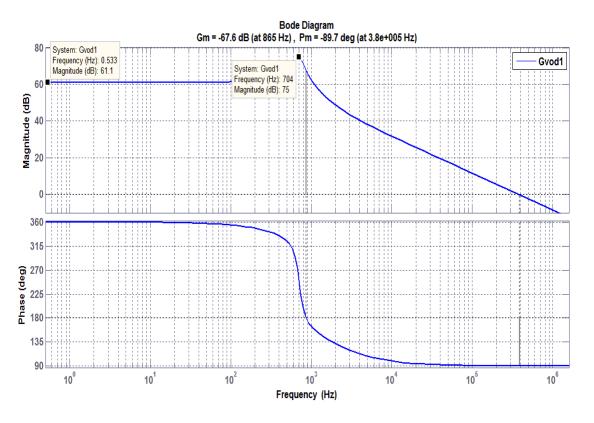

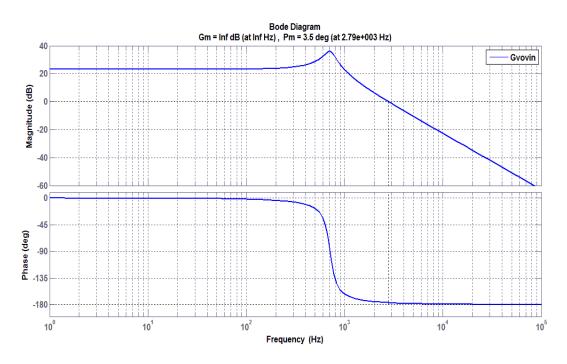

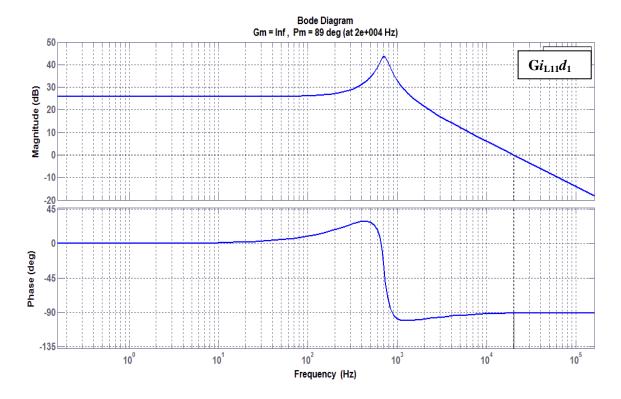

| 6.1 E  | 88 SODE PLOTS AND DISCUSSION 88                                                                    |

|--------|----------------------------------------------------------------------------------------------------|

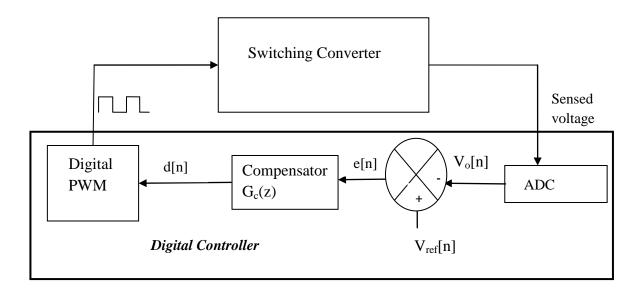

| 6.2 I  | 92 DIGITAL CONTROL                                                                                 |

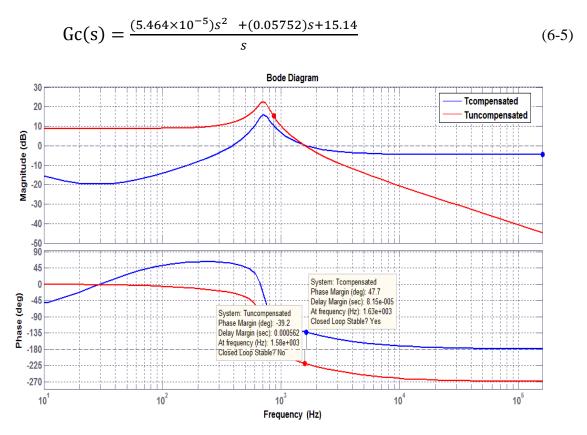

| 6.3 F  | PROPOSED CONVERTER DIGITAL CONTROL DESIGN                                                          |

| 6.3.1  | Analogue compensator design                                                                        |

| 6.3.2  | Discretization of the analogue compensator                                                         |

| 6.3.3  | Simulation results of the output voltage regulation of a two-phase tapped-                         |

|        | coupled inductor boost converter                                                                   |

| 6.3.4  | Compensator implementation using the TMS320F2812 DSP 102                                           |

| 6.3.5  | Tapped-coupled inductor converter interfacing with the DSP controller 104                          |

| 6.4 C  | CHAPTER CONCLUSION 105                                                                             |

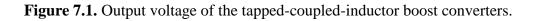

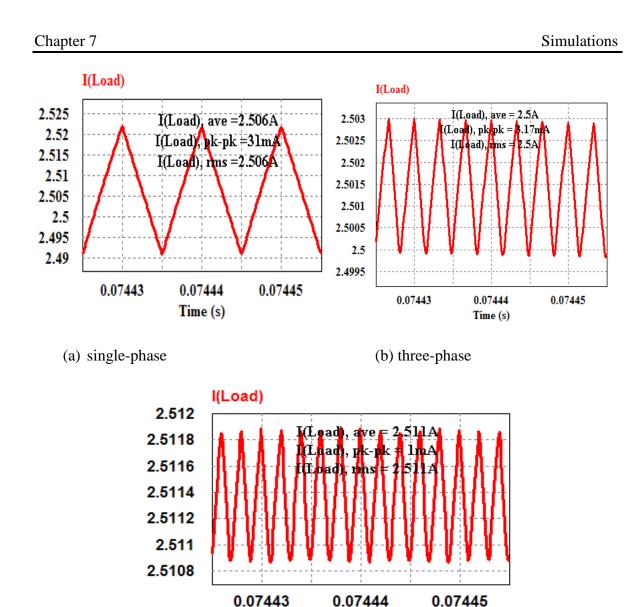

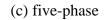

| СНАРТИ | ER 7 SIMULATIONS 106                                                                               |

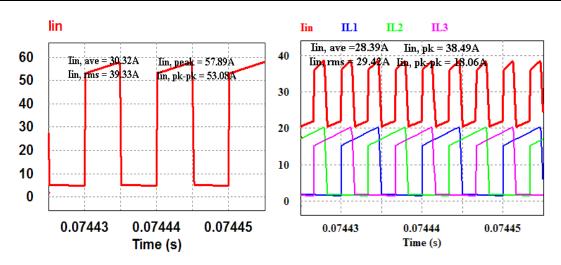

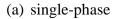

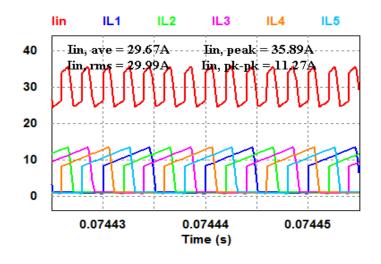

|        | VAVEFORMS OF MULTI-PHASE TAPPED-COUPLED-INDUCTOR BOOST                                             |

|        | CONVERTERS WITH ODD NUMBER OF PHASES 106                                                           |

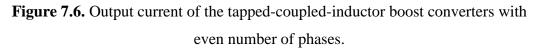

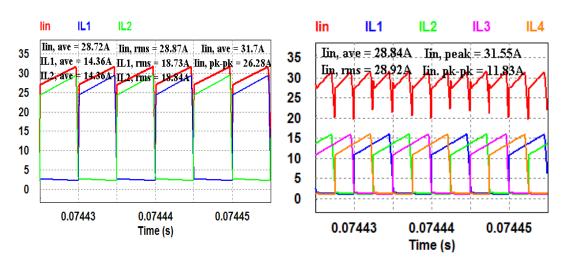

|        | VAVEFORMS OF MULTI-PHASE TAPPED-COUPLED-INDUCTOR BOOST<br>CONVERTERS WITH EVEN NUMBER OF PHASES111 |

|        | IMULATION DISCUSSION AND PERFORMANCE ANALYSIS OF THE                                               |

|        | SIX SIMULATED TAPPED-COUPLED-INDUCTOR BOOST CONVERTERS                                             |

|        |                                                                                                    |

| 7.3.1  | Boost ratio 116                                                                                    |

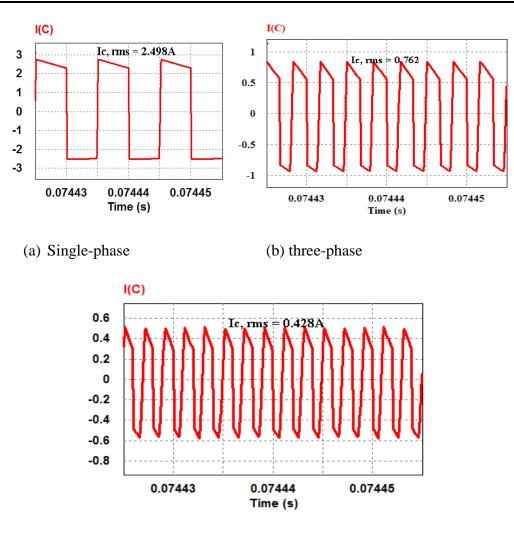

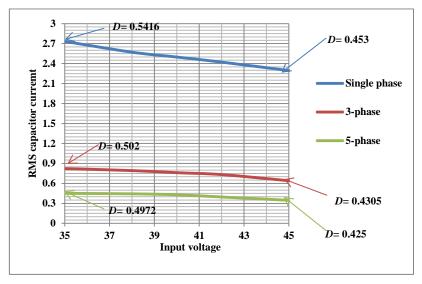

| 7.3.2  | Capacitor current                                                                                  |

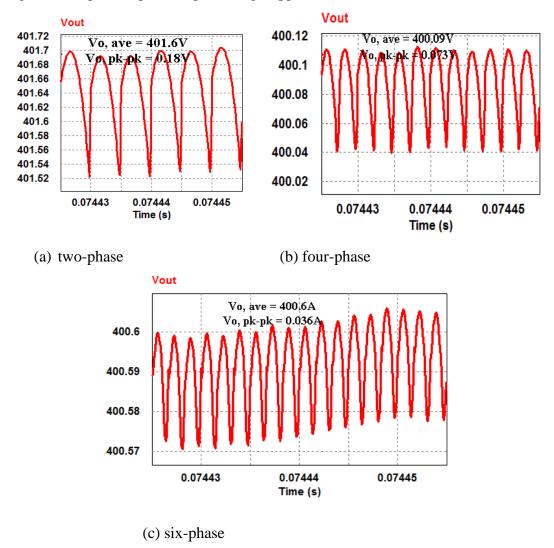

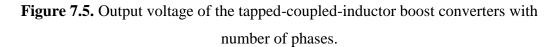

| 7.3.3  | Output current and voltage ripple                                                                  |

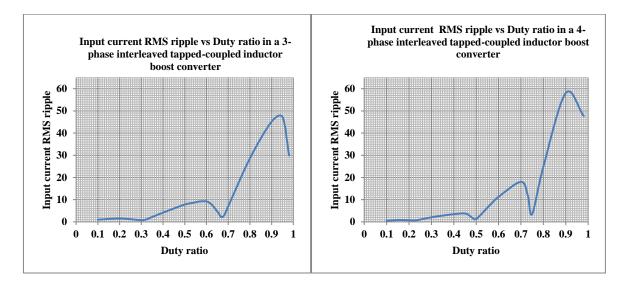

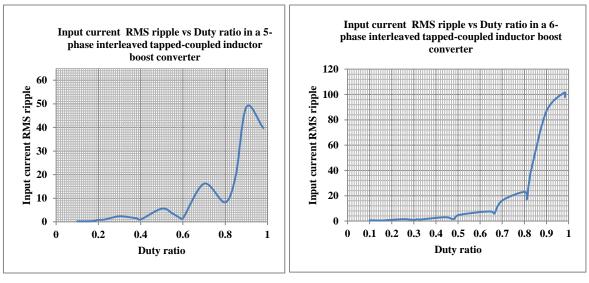

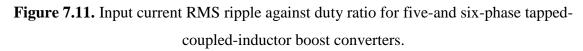

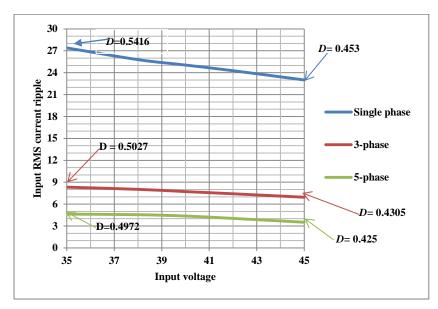

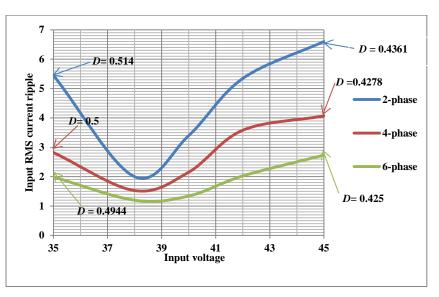

| 7.3.4  | Input current RMS ripple118                                                                        |

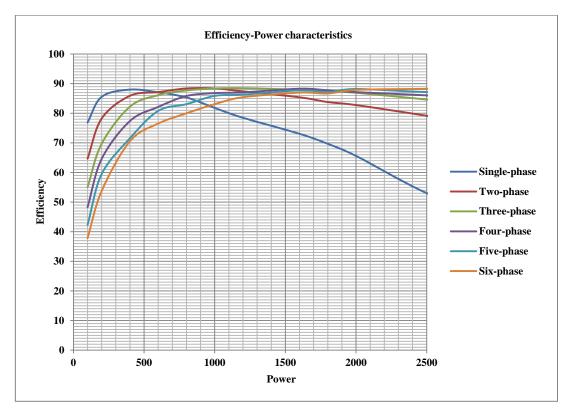

| 7.3.5  | Efficiency vs. Power 121                                                                           |

| 7.3.6  | Effects of input voltage variations123                                                             |

| СНАРТИ | ER 8 PRACTICAL RESULTS 127                                                                         |

| 8.1 S  | INGLE-PHASE TAPPED-COUPLED-INDUCTOR BOOST CONVERTER. 128                                           |

|        | WO-PHASE INTERLEAVED TAPPED-COUPLED-INDUCTOR BOOST                                                 |

|        | CONVERTER 129                                                                                      |

|        | DISCUSSION OF THE PRACTICAL RESULTS 132                                                            |

| 8.3.1  | Proposed converter loss and efficiency analysis                                                    |

| СНАРТІ | ER 9 CONCLUSION AND PROPOSAL FOR FUTURE WORK                                                       |

| 9.1 CONCLUSION                                             |

|------------------------------------------------------------|

| 9.2 FUTURE WORK 13                                         |

| APPENDIX A CONVERTER PROTOTYPE AND DIGITAL CONTROLLER      |

| CODE14                                                     |

| A.1 PROTOTYPE OF THE TWO-PHASE INTERLEAVED TAPPED-COUPLED- |

| INDUCTOR BOOST CONVERTER 14                                |

| A.2 DIGITAL CONTROLLER C-CODE                              |

## CHAPTER 1 INTRODUCTION

#### **1.1 PROBLEM STATEMENT**

#### 1.1.1 Background and context

Renewable energy has been thrust to the spotlight due to the rising oil prices, concern of environmental pollution around the world such as the greenhouse gas effect, acid rain and the eminent exhaustion of fossil-fuel reserves. Renewable energy sources such as solar, wind, tidal have become one of the most important renewable energy sources since they are clean, pollution free, and inexhaustible [1]

Solar cells convert sunlight directly into electricity through the photovoltaic effect of semiconductors. Solar photovoltaic (PV) can be used in a wide range of applications including power supplies for satellite communications or large solar power stations feeding electricity into the grid. A solar array consists of solar panels connected in series and/or shunt configurations. A solar panel consists of solar cells, also connected in series and/or parallel configurations.

The most important considerations on PV energy generators are to obtain a high voltage gain and sourcing of minimal reactive power by drawing currents with very little ripple component. Most currently available PV modules have low open-circuit and maximum power point (MPP) voltages [2]. Efficient power conversion is not achieved with a low voltage source. Some stand-alone applications operate at high power levels which require many PV modules to be connected in series to provide a high voltage. The utility grid voltage is also high including 220 or 110 V<sub>AC</sub>, hence a PV generator needs to produce a high DC voltage in case of PV solar-grid integration. A PV array output voltage and current also varies a lot depending on solar radiation and temperature.

Today's PV system cost mainly depends on the cost of the panels. One priority is to reduce the installation overhead by reducing the number of panels in series, while still maintaining a high power output by having parallel panel connections. Connection of large number of PV panels in series also lead to limitations like mismatch errors which cause low conversion efficiencies.

Mismatch errors are caused by circumstances in PV arrays such as load mismatching, mismatching of PV modules, shadows and obscurances [3].

DC-DC converters are being integrated to the PV sources to improve the conversion efficiencies. It is also possible to integrate a DC-DC converter with a maximum power point tracking (MPPT) algorithm that makes a PV array deliver its maximum available power. The buck, boost and buck-boost converters are commonly used with the MPPT [4].

Other than providing the MPPT, a boost DC-DC converter can be used to provide a high voltage amplification of the PV array output. PV panels also have very low current dynamics. It is hence always important to keep the current ripple very low. By controlling the DC-DC converter, a regulated converter output can be obtained despite the frequent fluctuations in the PV array output. Theoretically, conventional boost converters are able to achieve high step-up voltage gain at a high duty ratio. The voltage gain is however limited in practice due to losses in the inductor, filter capacitor, active switch and the output diode. With an high duty ratio, the output diode conducts for only a short time during each switching cycle, thus resulting in serious reverse-recovery problems and increase in the rating of devices[10]-[12].

## 1.1.2 Research gap

The problem addressed in this research lies in finding a way of efficiently stepping up the small intermittent output voltage of a PV array by at least ten times to a constant high voltage DC bus. Current from the PV array should also be drawn with minimal ripple. The

high output DC voltage can then be used for high power applications or integrated to the utility grid.

## **1.2 RESEARCH OBJECTIVE AND QUESTIONS**

The research questions to be addressed in this thesis include:

- 1. How can the output voltage of a small PV array be boosted to high values using a DC-DC converter without extreme duty ratios?

- 2. How can the input and output current and voltage ripple be reduced, hence a lower reactive power demand and an increase in the efficiency of a PV system?

- 3. Is it possible to obtain a converter topology suitable for variable input voltage and power operation to be used in an application such as solar PV?

- 4. What are the effects of the coupling coefficient on a boost converter with a tappedcoupled inductor?

- 5. How can a converter with an advantage of low output current ripple suitable for charging a battery from a PV source be obtained?

The main objectives of the research are to develop a novel DC-DC converter that is capable of ensuring:

- 1. A high voltage boost ratio of a PV source output or a similar type of source such as wind, for a high voltage and power application or integration to the grid. The high boost ratios should be achieved without adversely compromising performance.

- Minimal ripple in the input and output of the converter, hence an improvement of performance and efficiency. This will make the converter suitable for interface with a PV source where it is important to draw currents with very little ripple component.

- 3. Suitability for variable power and voltage operation.

- 4. A regulated output is obtained from the PV source at all times despite the changing environmental conditions.

## **1.3 HYPOTHESIS AND APPROACH**

The hypothesis as stated as;

A multi-phase interleaved tapped-coupled-inductor boost converter would:

- I. Be capable of achieving a high voltage boost ratio of a PV source without adversely compromising performance.

- II. Result to minimal ripple in the input and output of the converter which will hence lead to an improvement of performance and efficiency.

- III. Be suitable for variable power and voltage operation.

- IV. Be capable of ensuring that a regulated output is obtained from the PV source at all times despite the changing environmental conditions.

The approach to be used is given as follows;

- I. Literature review; a study of the existing PV array output boosting methods will be done. This will aid in choosing a suitable topology for a PV application that ensures a high voltage boost ratio, minimal ripple and a high efficiency. A suitable powerelectronics converter that has better performance characteristics is selected to be connected to the PV array output.

- II. Analysis and modelling of the selected boost converter is done which verifies the hypothesis and helps in the design.

- III. Design; The converter components will be designed and selected for optimal performance.

- IV. Control of the proposed converter is then done to regulate the output of the converter.

- V. Simulations of the proposed converter are done using PSIM software. With the simulations, the proposed converter's current and voltage waveforms are obtained which further verify the hypothesis.

- VI. Practical implementation; the designed converter will be implemented in hardware to validate simulation and analytical results.

Department of Electrical, Electronic and Computer Engineering University of Pretoria

5

## **1.4 RESEARCH GOALS**

- a) To formulate a new, efficient and low cost method of boosting the output voltage of a small PV array or a similar type of source.

- b) To design a simple, novel, highly efficient boost DC-DC converter that can be used as a sub-system in the integration of a renewable energy source to the grid or for high power applications.

- c) To design a converter that has minimal output current ripple hence suitable for an application such as battery charging.

- d) To design a DC-DC converter that is suitable for variable input voltage and power operation to be used in an application such as solar PV.

## 1.5 RESEARCH CONTRIBUTION

Output voltage of a solar array is low and it needs to be boosted to feed high power applications or integration to the grid. This however has to be done with high efficiency, while still ensuring maximum power is extracted from the PV array. Many techniques that try to boost the output voltage of a PV source have been identified, but these present limitations due to low efficiencies, complexity and cost. By use of the proposed DC-DC converter, high boost ratios can be attained at high efficiency and a low cost of the entire PV system. The proposed converter is also suitable for high and variable power applications.

#### **1.6 OVERVIEW OF STUDY**

This chapter introduces the background and context of the research problem. It identifies the research gap, briefly explains the research objectives, questions, and hypothesis and briefly describes the research approach.

In Chapter 2, the existing PV array voltage boost topologies are discussed and their advantages and limitations examined. Maximum power point tracking and PV array characteristics are also covered. A single-phase tapped-coupled inductor boost converter's operation is discussed and a detailed characterisation presented in Chapter 3. In Chapter 4,

6

the proposed interleaved tapped-coupled inductor boost converter is discussed. A twophase interleaved tapped-coupled-inductor boost converter is analysed and modelled.

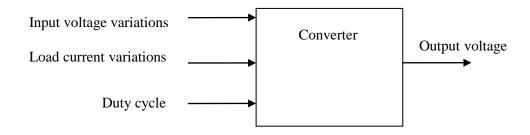

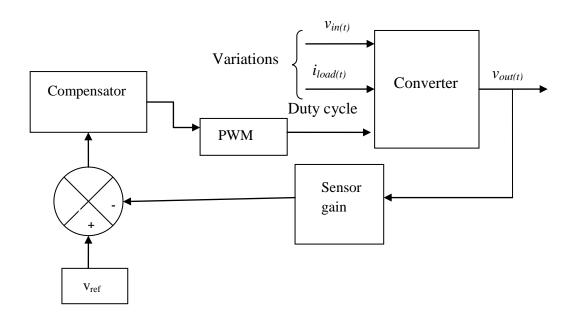

In Chapter 5, sizing of components constituting the proposed converter is done. The proposed converter circuit design is also discussed in this chapter. Control of the proposed converter is discussed in Chapter 6, where the design of a digital feedback control loop is explained. This control ensures that the output voltage is regulated despite the any input voltage and load variations.

In Chapter 7, the proposed multi-phase interleaved tapped-coupled-inductor boost converter up to six-phases is simulated. Comparison of the different multi-phase converters is done and discussed to show how converter performance is affected by the number of phases used. In Chapter 8 practical results from the built single-phase and two-phase tapped-coupled-inductor boost converters are presented and discussed. These are compared with the simulation results. Chapter 9 concludes and makes recommendations for further research.

Department of Electrical, Electronic and Computer Engineering University of Pretoria

# CHAPTER 2 LITERATURE STUDY

## **2.1 CHAPTER OBJECTIVE**

This chapter covers the literature survey. It examines the existing techniques that have been used in stepping up of a PV output voltage, minimising ripple in the current drawn from the PV and the different methods which have been used to ensure MPPT. A brief discussion of the proposed converter is also included at the end of this chapter.

## 2.2 BOOSTING THE VOLTAGE OF THE PV ARRAY

PV cells produce direct current (DC) power at only a fraction of a volt. Alternating current (AC) power with voltage greater than 100 V is used by the utility grid and most of the equipment in homes. To connect PV systems to the grid, an inverter is required to convert power from DC to AC. The input DC voltage to the inverter must be large, about 300V to 400V, for an efficient conversion to the AC-line voltage.

Some stand-alone applications also require high DC voltages which cannot be obtained directly from small PV arrays. To achieve these high voltages from the PV array, high voltage amplification is necessary. A number of ways to amplify the output of a PV system have been studied and are discussed below:

## 2.2.1 The photovoltaic series string

PV panels have previously been placed in series to obtain high output voltage, maintaining lower currents and higher efficiencies [7]. However, the long strings of panels have a lot of complications especially when the string is operating under non-uniform conditions of radiation.

Series connected PV panels are never exactly identical, though they are constrained to all conduct the same current. In case of shading of some of the panels, thus unequal radiation, then the following may occur:

I. The shaded cells or panels will try to drive the once not shaded into operating at a lower current level. As a result, the least efficient panel sets the string current. The system output power is limited by the current produced by the cell or panel generating the lowest output current. This means that the total efficiency of the array is limited to the efficiency of this cell.

Also, the PV panels in a string must be of the same size and orientation [7].

II. The cells or panels which are not shaded try to drive the shaded ones into operating at a higher current level. Current through a PV cell is directly proportional to irradiance, and the only way the cell can operate at a higher current than its short circuit current is by becoming reverse biased. The cell moves into the negative voltage region of the cell's I-V curve. This causes a phenomenon known has hotspot heating, as power generated by the unshaded cells is dissipated in the shaded cells, leading to possible cell damage [5]. During this time, however, the panel's backplane diode(s) become forward biased, limiting the reverse bias and the power dissipation in the shaded cell. The disadvantage of this is that now the shaded cells are bypassed, thus they have a zero power contribution to the PV array and a lower string voltage.

## 2.2.2 PV array- inverter connection

The use of a single stage inverter is also another method that has been used as an interface to the PV arrays. A single stage inverter feeding the utility grid from a PV array has the following functions:

- a) To invert the PV current in to an AC current.

- b) If the PV array voltage is lower than the grid voltage, the PV array voltage has to be boosted by an extra element such as a line frequency step-up transformer.

Protection and filtering components have to be included in such a system which increases complexity and cost [7]. Inclusion of a transformer also has a disadvantage of large size and weight and low efficiency [2].

## 2.2.3 Conventional boost DC-DC converter interface of PV array

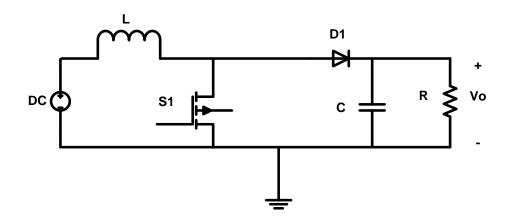

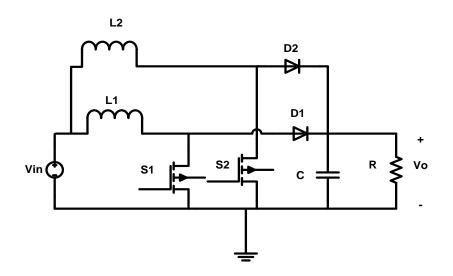

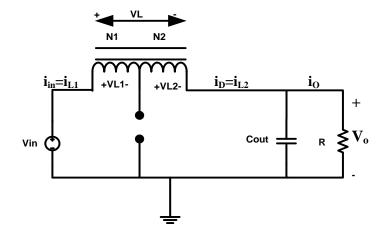

Due to the varying voltage levels of a PV array, a dc-dc converter can be connected to the array output for voltage regulation as well as boosting. The boost converter should have a high step-up voltage gain and a high efficiency. A conventional boost converter is shown in Figure 2.1.

Theoretically, conventional boost converters are able to achieve high step-up voltage gain in heavy duty load conditions. The voltage gain is however limited in practice due to losses

in the inductor, filter capacitor, active switch and the output diode. Due to these losses, the high voltage gain in a conventional boost converter can only be achieved with an extreme duty ratio. With an high duty ratio, the output diode conducts for only a short time during each switching cycle, thus resulting in serious reverse-recovery problems and increase in the rating of devices[10]-[12]. Under this condition, the EMI (electromagnetic interference) is severe. As a result of this, the conversion efficiency is degraded.

Furthermore a conventional boost converter has a low input voltage, hence large input currents result. High current and voltage rated switches, which have high parasitic resistance, are hence required. The draw backs of this include increased conduction loss, cost and size [6], [37]. Furthermore, this converter is not suitable for charging a battery from a PV source due to the discontinuous nature of its output current.

Figure 2.1. Conventional boost converter.

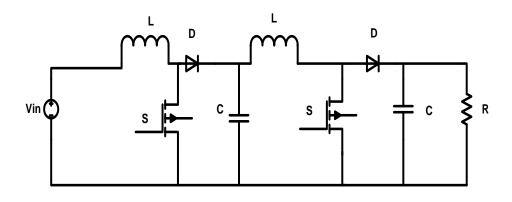

#### 2.2.4 Cascaded converters

Another way of increasing the voltage gain of a PV array output would be cascading DC-DC boost converters [7] as shown in Figure 2.2. As proposed in [7], every panel has its own DC-DC converter, and the panels with their associated converters are still placed in series to form a string. It was however concluded in [7] that the configuration is not capable of always delivering the full amount of output power from a mixture of shaded panels and those delivering full power. This is because if a PV panel is shaded, its current

falls and the current in the entire string must fall to the value of the lowest converter module input current. Another limitation of the cascaded converters is the complexity due to the higher number of switches and the magnetic components and the controllers which must be synchronized. Another concern of the cascaded converters is their stability. The output diode of the last boost stage converter has a severe reverse recovery problem due to the high levels of both output power and output voltage. This degrades efficiency and causes EMI noise [6].

Figure 2.2. Cascade boost converter.

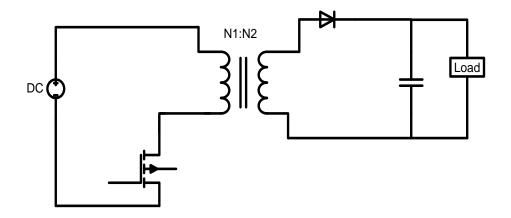

## 2.2.5 A DC-DC flyback converter

A DC-DC flyback converter in Figure 2.3 can be used to provide a high voltage boost. It has a transformer, used for voltage isolation as well as for better matching between the input and the output voltage and current requirements. Although the flyback converter has an advantage of a very simple structure, it suffers a high switch voltage stress due to the leakage inductance of the transformer. A snubber circuit is required to dissipate or recycle the energy stored in the leakage inductance of the primary winding when the switch is turned off. A flyback converter also does not offer a mechanism of ripple reduction in the input current [38].

Figure 2.3. Flyback converter

## 2.2.6 Step-up converters with coupled inductors

Coupled inductors, without tapping, can serve as a transformer to extend the voltage gain in DC-DC converters [2], [6], [9]-[11]. Voltage stress of the switch is reduced and the peak current of the power devices is minimized. This improves the circuit performance in high step-up DC-DC converters. Two coupled inductors include two windings wound on the same core. Coupled-inductor techniques involve simultaneous parallel energy transfer both electrically and magnetically.

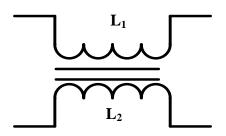

The current specifications for a coupled inductor differ depending on whether its windings are physically connected in series or in parallel. When the windings are connected in series as in Figure 2.4, the equivalent inductance is more than  $L_1+L_2$  due to the mutual inductance.

Figure 2.4. Two coupled inductors connected in series.

12

Figure 2.5. Two coupled inductors connected in parallel.

The mutual inductance, M of the two coils is related to the two coupled inductance and the coupling coefficient.

$$M = k\sqrt{L_1 L_2} \tag{2.1}$$

The coupling coefficient represents the flux linkage between the two windings. Coupling coefficient has values of 0 < k < 1 and is dependent on the portion of the total flux lines that cuts both the first and second coil. For a coupling coefficient of 1, then all the flux generated by the second winding cut the first winding and maximum energy would be transferred across the windings. The extreme duty cycle is avoided by the proper design of the turns ratio of the coupled inductor.

The leakage inductance of the coupled inductor can also be employed to control the diode turn-off current falling rate and hence alleviating the diode reverse-recovery problem [6], [9]. However, the leakage energy results in high voltage ripple across the switch due to a resonance phenomenon induced by the leakage currents and severe EMI problems which degrades efficiency [11]. This in turn requires the converter to employ a high voltage switch to sustain variations in order to protect the switch or a snubber circuit to deplete the leakage energy. A resistor-capacitor-diode (RCD) clamp circuit can reduce the voltage stress but at the cost of high power losses. In [6], a high step-up DC-DC utilising coupled inductors is described. The leakage energy in this converter is recycled by the use of a diode and a capacitor. A step-up converter with coupled-inductor described in [11] a passive regenerative snubber circuit is adopted to promote the voltage gain.

Another method of reducing the switch voltage stress due to the leakage inductance is by use of an active-clamp circuit [2], [8], [9], [10], and [39]. An active-clamp circuit recycles the leakage energy with minimal voltage stress across the switch, leading to a higher output voltage. However, limitations of the active-clamp circuit include topology complexity, increased cost and losses due to the clamp circuit. An overlap between the main and active-clamp switch gate-drive signals could lead to a failure of the circuit [6].

## 2.2.7 Interleaved boost converters

Multi-phase boost converters with interleaved switching have received considerable interest in PV applications [2], [12]-[14]. In interleaved converters, boost converters are paralleled to improve energy efficiency by reducing the amount of reactive power drawn from the source. The interleaved boost converters have the same duty ratio but with a  $2\pi/N$  phase shift, where N is the number of phases. Compared to conventional boost converters, the interleaved converters have the following advantages:

- a) Lower input- current ripple due to current sharing.

- b) Lower output-voltage ripple.

- c) A lower value of ripple amplitude and a high ripple frequency in the resulting input and output waveforms.

- d) Enhanced transient performance as a result of smaller filter components.

- e) More compact in size due to smaller filter components and heat-sink.

- f) Improved reliability due to structural redundancy.

- g) Reduced electromagnetic interference because of low ripple amplitude of the input current.

Interleaved converters however have limitations that include:

- a) They have a more complex control since the active switches are controlled by complementary signals.

- b) A higher number of components are required.

- c) A higher number of switches and gate drive circuits are required.

Figure 2.6. Two-phase interleaved boost converters

Although there is an increase in the number of components in the interleaved converter, the actual increase of cost may not be significant compared to the un-interleaved converter [40]. This is because of the current sharing in the inductors and the switching devices, leading to lower rated components in the interleaved converter.

A combination of interleaved and coupled inductors has been shown to produce high performance in the boost converters [2], [12]-[17], [40]. The coupling, which is a form of an integrated magnetic component, reduces the core number. This overcomes the shortcoming of interleaving, which increases the number of inductors compared to a conventional converter. The benefits of strongly coupled inductors in interleaved boost converters is presented in [15], where it is demonstrated that the topology has superior current sharing characteristics even in the presence of relatively large duty cycle mismatch and small input current ripple.

In [14], a two-cell interleaved boost converter with coupled inductors is used to match the photovoltaic system to the load and operate the solar cell array at a maximum point.

A ZVT interleaved boost converter, with a winding-coupled inductor structure is proposed in [12]. This converter offers a method to extend the voltage gain using the turns ratio

selection. The turn-off voltage of the main switch is clamped and leakage energy recycled by use of an active-clamp circuit. This ensured that the voltage spikes across the switch are suppressed and leakage energy recovered.

Analytical models describing the steady-state operation of multi-phase boost converters with interleaved switching for PV applications are derived in [18]. The analyzed topology in [18] included the non-ideal characteristics and a switching scheme based on ripple correlation control is deployed to maximise the power output of the photovoltaic source.

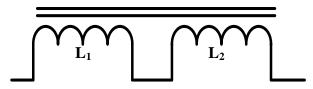

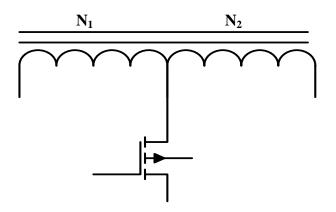

## 2.2.8 Tapped-coupled boost converter

Tapped inductors have been investigated to provide high step-up and step-down ratios with good efficiency with no requirement for isolation [24]-[34]. The two windings  $N_1$  and  $N_2$  of the tapped inductor are on the same core and therefore magnetically coupled as shown in Figure 2.7. A large step-up conversion can be achieved by selecting the turn-ratio of the tapped-inductor windings. Tapping the inductor has the benefits that the duty cycle of the converter can be optimized so as to achieve maximum efficiency. Tapping of the inductor also allows a different mix of voltage and current ratings for various components in the converter [24].

Figure 2.7. Tapped-coupled inductors.

In [24] and [25], a matrix of tapped inductor configurations is discussed which includes:

a) Switch-to-tap, where the switch is connected to the tapping point of the inductor,

rather than to one of the extremity of the inductor.

- b) Diode-to-tap, where the diode is connected to the tapping point of the inductor, rather than to one of the extremity of the inductor.

- c) Rail-to-tap, where the tap is connected to one of the power rails.

High-step-down converters using the tapped inductor have been investigated in [26] and [27]. Recent studies have also shown the tapped inductor application in high-step-up converters [28], [30] and [34]. In [28], it is shown that the boost converter with the tapped inductor has a higher transfer ratio than the classical boost converter for the same duty ratio. The converter in [28] also has lower voltage stress across the buffer capacitor, but a higher current stress on the input shunt capacitor. In [30], a tapped-inductor boost converter for high boost application is described and analysed, where it was also concluded that the converter is a good option for solving high boost requirements.

Application of tapped inductor converter on PV systems has been discussed in [31], [32] and [34]. In [31], a buck-boost converter with tapped inductor is studied, aiming at selecting the converter appropriate for an integrated PV inverter applied for residential use with connection to a single-phase grid. In this study, it was verified that the gain of the buck-boost with tapped-Inductor was higher than obtained with the classical buck-boost converter. It was also concluded in [31] that the application of the buck-boost with tapped inductor without ground is feasible in a small single-phase inverter within photovoltaic systems interconnected to the grid.

Study in [31] was extended in [32], where a tapped inductor buck-boost converter with a non-grounded output is discussed. In [32], it is concluded that connection of the PV to the grid for residential use could be done using a tapped inductor buck-boost converter operating in three modes: Continuous conduction mode, critical mode and the discontinuous mode.

A possibility of using tapped-inductor boost converter as a module integrated converter for PV sources has been discussed in [34].

A tapped-inductor boost converter with zero current switching (ZVS) is proposed. It is concluded that the proposed boost converter can allow voltage step-up of ten times its

input without an extreme duty ratio. Switching losses were also reduced and an increased efficiency achieved [34].

## 2.2.9 Other proposed boost converters in the literature.

Other high step-up converters include those utilising the switched-inductor technique [38], whereby two inductors with same level of inductance are charged in parallel during switch-on period and are discharged in series during switch-off period.

A basic cell with winding-cross-coupled inductors (WCCIs) and interleaved structure is proposed in [41]. A family of DC-DC converters is deduced from this basic cell which is suitable for high step-up conversions.

The wide-input-wide-output (WIWO) DC-DC converter [42] is formed by the integration of buck and boost converters via a tapped inductor. The WIWO converter achieves both high buck and boost features by application of proper control to the two active switches. The capacitor-diode voltage multiplier converter [43] has been proposed and can be used to drive voltage amplifiers. These types of converters however, are all complex and have a higher cost.

## **2.3 SOLAR RESOURCE**

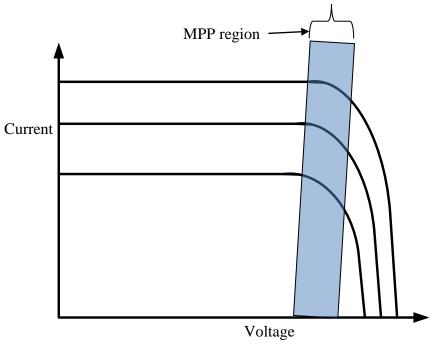

## 2.3.1 Solar array characteristics

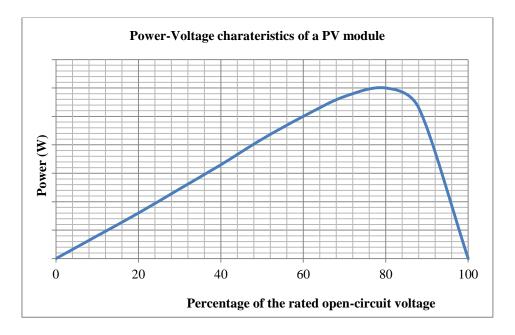

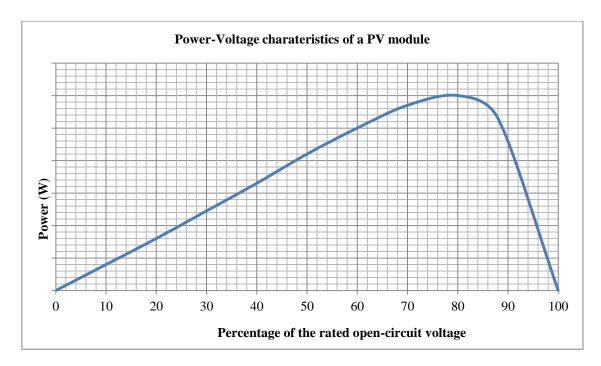

A PV array has non-linear voltage-current characteristics as shown in Figure 2.8. Its output depends on the load voltage and weather conditions, which are unpredictable. The characteristics are divided into two sections: (i) constant voltage section and (ii) constant-current section [15]. The current from the array is proportional to the radiation level and completely independent from temperature, while the voltage is completely independent from the radiation level and has negative coefficient with the temperature. Thus, an increase in solar irradiation and a decrease in array temperature results in an increase in maximum power output of the array. Due to the intermittent nature of the PV array, it is necessary to employ an efficient power electronic interface, with a maximum power point tracker (MPPT), between the array and the loads or the AC grid. The maximum power

point (MPP) region in Figure 2.8 shows a unique operating point where the array delivers maximum power. An MPPT ensures that the PV array operates at this maximum power point. This would ensure maximum utilisation of the PV source.

Figure 2.8. Voltage-Current characteristics of a PV- array

Figure 2.9. PV array power curve

Department of Electrical, Electronic and Computer Engineering University of Pretoria

## 2.3.2 Mismatch errors

Mismatch in a PV array occurs due to the interconnection of modules with different performance characteristics. This result in to detrimental effects like: power loss and reliability degradation. Mismatch losses in solar PV arrays can be due to a variety of reasons including:

- I. Differences in the working temperature of PV modules.

- II. Shadowing of some cells or PV modules.

- III. Different I-V characteristics of the cells during manufacture.

- IV. Aging of the PV modules.

- V. Inclination or orientation angles of the PV modules.

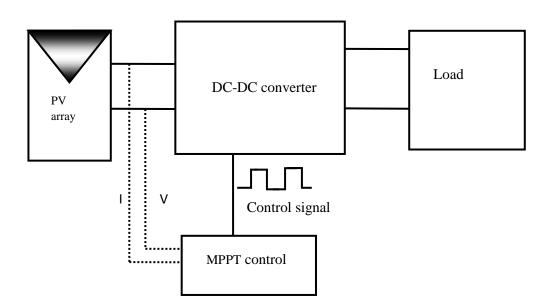

Due to mismatch loss, lower power than the array rating is delivered [5]. Incorporating a highly efficient DC-DC converter with MPPT function leads to a significant reduction of these power losses. Many MPPT solutions are developed to ensure the optimal utilization of PV modules [19], [22] and [23]. The implementations generally involve sensing the output current and voltage of PV modules, and the MPPT algorithms use the information to maximize power drawn from the PV modules. An example of this is shown in Figure 2.10.

Figure 2.10. Block diagram showing MPPT control in a PV array-Converter connection

## 2.3.3 MPPT schemes

An MPPT usually consists of a converter under the control of a maximum-power-pointseeking algorithm. Inserting an MPPT between the PV array and the load ensures that the array's operating point is controlled to deliver maximum power. Many MPPT methods have been developed and implemented [19]. Some of the MPPT schemes include:

- The Fixed Duty Cycle- It is the simplest of the methods. It does not require a feedback and the load impedance is adjusted only once for the maximum power point [35].

- 2) Fractional Open-Circuit Voltage or Constant voltage method-This method is based on the fact that there is a near linear relationship between  $V_{MPP}$  and  $V_{OC}$  of the PV array, under varying irradiance and temperature levels.  $V_{MPP}$  is around 0.7 to 0.8 of the  $V_{OC}$ . In this scheme,  $V_{OC}$  is measured periodically by momentarily shutting down the power converter. An advantage of this scheme is that only voltage needs to be measured. However, it has a disadvantage in that it incurs temporary loss of power each time  $V_{OC}$  has to be measured [19], [35].

- 3) Perturb and Observe- This is one of the most popular schemes. The output terminal voltage of the PV array is periodically incremented or decremented while comparing the power obtained in the current cycle with the power of the previous cycle. If there is an increase in power, the subsequent perturbation is kept the same to reach the MPP and if there is a decrease in power, the perturbation should be reversed [19]. This scheme is easy to implement and has a good performance. However, it has a disadvantage that it takes a long time before reaching MPP in case of an irradiation change [36]. A modified version of this scheme is obtained when the perturbation steps are changed according to the distance of the MPP, hence a higher efficiency [35]. DSP and microcontroller control is suitable for this scheme [19].

- 4) *Hill Climbing-* This scheme involves perturbation in the duty ratio of the power converter. Perturbing the duty ratio then perturbs the PV array current and consequently perturbs the PV array voltage.

5) *Incremental Conductance*- In this scheme, the derivative of power is calculated to get the correct direction for perturbing the array's reference variable. The slope of the PV array power curve on figure 2.8 is zero at the MPP, positive on the left of the MPP and negative on the right [19].

$\begin{cases} dP/dV = 0, & \text{at MPP} \\ dP/dV > 0, left of MPP \\ dP/dV < 0, right of MPP \end{cases}$

The Incremental Conductance scheme suffers from large sampling periods, though it does not suffer from fast transients in environmental conditions [35]. DSP and microcontroller control can be applied in this scheme; hence a track of previous values of voltage and currents can be kept [19].

- 6) Fuzzy Logic Control- This scheme consists of three stages: a) fuzzification, where numerical input variables are converted in to linguistic variables based on a membership function. b) Rule base table look up and c) defuzzification, where the fuzzy logic controller output is converted from a linguistic variable to a numerical variable, still using a membership function [19], [40]. The MPPT fuzzy logic controllers perform well under varying atmospheric conditions. However, this scheme is complex and needs additional hardware hence a limitation in low cost system design.

- 7) Neural Network- A PV array is tested over a period and the patterns between the inputs and outputs of the neural network are recorded, through a training process. PV arrays have different characteristics so a neural network has to be specifically trained for the PV array with which it will be used. The characteristic of a PV array also change with time, hence the neural network has to be periodically trained for an accurate MPPT [19].

- Other MPPT schemes include: Ripple correlation control, Current sweep, DC-Link Capacitor Droop Control, Load Voltage Maximization and the Beta method [19], [35], [36].

In the choice of the MPPT scheme to use, the following aspects should be put in to consideration: cost, complexity, required sensors, convergence speed, hardware requirement, and effectiveness.

## 2.4 MULTI-PHASE INTERLEAVED-TAPPED-COUPLED-INDUCTOR BOOST CONVERTER WITH DIGITAL CONTROL.

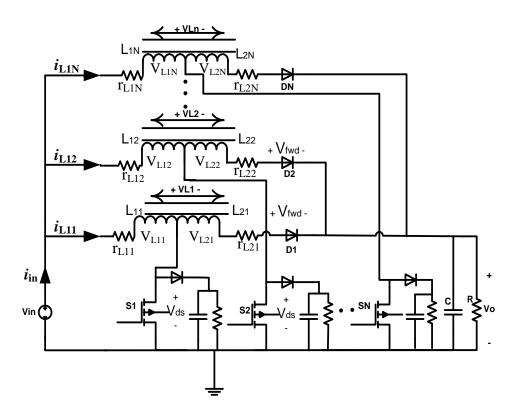

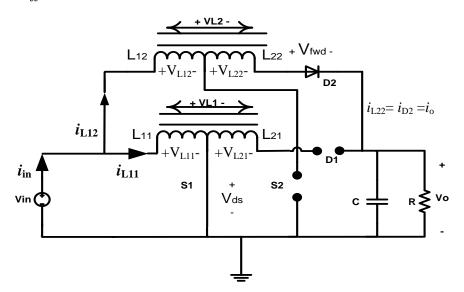

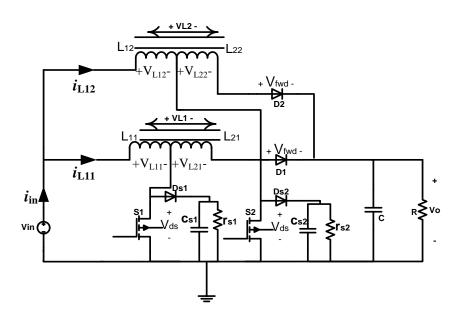

Most of the study done so far on high boost of a PV array voltage is either inefficient or is complex and expensive to implement. These drawbacks associated with existing boost converters and series connection of PV panels encourage a search for a high boost converter topology. There has been no study thus far on interleaving a tapped-coupled-inductor-boost converter, and also applying it to efficiently boost the PV array voltage. This thesis presents a novel step-up converter for boosting a low voltage of a PV array to a high DC-bus voltage which can be used to feed a grid connected inverter or can be applied on a standalone application. It combines the advantages of both interleaving and tapped-coupled inductors. With digital control, the multi-phase converter switching signals can be re-configured efficiently in case of changes in the PV array output, which may be due to an open circuit of a panel string due to shading.

Compared to the proposed converters in the literature, the proposed converter has the following merits:

- a) Circuit simplicity since a conventional interleaved boost converter comprising of two series coupled inductors with a switch tapping is used.

- b) High boost ratios are ensured by both the interleaving and the tapped-coupledinductor turns ratio.

- c) By use of a turns ratio, the duty ratio is kept within a reasonable range, hence avoiding an extreme duty ratio. This results to alleviation of severe reverserecovery and EMI problems which leads to a high conversion efficiency. An extreme duty ratio is also not desirable as it leaves no room for control which is needed to compensate changes in input and load.

- d) The proposed converter enjoys all the advantages of interleaving as mentioned in section 2.2.7. This increases the conversion efficiencies greatly.

- e) In the proposed converter the output current ripple is suppressed which makes it suitable for an application such as battery charging which demand current with low ripple.

- f) The required number of PV modules in series is reduced since high boosting is done by the proposed converter. This leads to a lower cost of the PV system and reduced mismatch errors on the PV array.

- g) By having high voltage boosting of the PV array voltage, the PV system power can be controlled in a wide range by just changing the number of parallel branches in the array. The proposed converter is also suitable for high and variable power operation.

- h) It is possible to integrate an MPPT control algorithm to the proposed converter which ensures that maximum power is extracted from the PV array despite the changing environmental conditions, hence maximizing PV conversion efficiency.

- i) The proposed converter is suitable for variable input voltage operation by making a trade-off between the choice of turns ratio and duty ratio.

Detailed characterisation of a single-phase tapped-coupled-inductor boost converter and a two-phase interleaved-tapped-coupled-inductor boost converter are also presented in this thesis. Simulations of a single-phase up to a six-phase tapped-coupled-inductor boost converter are also presented for comparison of performance and number of phases. This thesis also goes into detail on the design considerations of a two-phase interleaved-tapped-coupled-inductor boost converter. This includes modelling, simulations, hardware implementation, control algorithms and experimental testing.

# CHAPTER 3 BOOST CONVERTER WITH TAPPED-COUPLED-INDUCTORS

In this chapter, a single-phase boost converter with tapped-coupled inductors is described and analysed. Although this converter has previously been proposed, detailed analyses presented in this chapter is not available in the literature. Analysis is done for both ideal and non-ideal single-phase tapped-coupled-inductor boost converter operating in the continuous conduction mode (CCM). Expressions for the voltage boost ratio as well as factors affecting the boost ratio will be presented. Converter waveforms in CCM will be presented and analytical expressions for input average, RMS and ripple current as well as output capacitor RMS current will be derived.

#### **3.1 OPERATION OF THE CONVERTER**

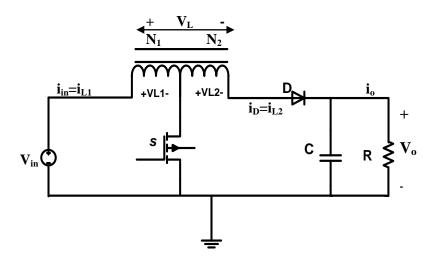

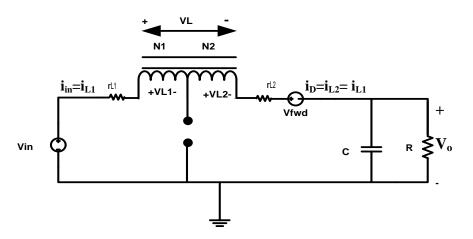

A tapped-coupled-inductor boost converter is shown in Figure 3.1. The circuit components include a MOSFET S, a diode D, tapped-coupled inductors,  $L_1$  and  $L_2$ , a filter capacitor C and a load resistance R. The MOSFET is turned on by a pulse-width modulator output through a gate drive circuit, at a duty ratio,  $=\frac{t_{on}}{t_{on}+t_{off}}$ , where  $t_{on}$  is the time when the MOSFET is conducting and  $t_{off}$  is the time when the MOSFET is not conducting.

Figure 3.1. Tapped-coupled-inductor boost converter

#### Boost Converter with tapped-coupled-inductors

The windings  $N_1$  and  $N_2$  are on the same core, hence magnetically coupled. When  $N_2 = 0$ , the configuration reduces to that of a conventional boost converter. The relationship between  $L_1$  and  $L_2$  is determined by the turns ratio of the magnetic element, that is:  $\frac{L_2}{L_1} = \left(\frac{N_2}{N_1}\right)^2 = n^2$  [30]. N<sub>1</sub> is the number of turns in the first inductor, L<sub>1</sub> and N<sub>2</sub> is the number of

turns in the second inductor,  $L_2$ . The converter operates with two states, when the switch is on and off in continuous conduction mode.

#### **3.3.1** Ideal characteristics

In this case, analysis is done with idealized components, thus neglecting the influence of parasitic components and power losses, and for the continuous mode in steady-state.

#### a) When the switch is conducting,0<t<DTs

When the switch is conducting, the diode D is reversed biased and the equivalent circuit is as shown in figure 3.2.

Figure 3.2. Tapped-coupled-inductor boost converter when the active switch is conducting.

With the diode not conducting, the voltage across  $N_1$  is equal to the input voltage  $V_{in}$  and energy is stored in the inductor  $L_1$ .

$$V_{in} = V_{L1} \tag{3-1}$$

25

$$V_{L1} = L_1 \frac{di_{L1}}{dt} = V_{in} \tag{3-2}$$

#### Boost Converter with tapped-coupled-inductors

Due to magnetic coupling, a voltage is induced in the second inductor,  $L_2$ , due to current  $i_{L1}$  flowing through the first inductor  $L_1$ , though no current flows through  $L_2$  during this interval.

$$V_{L2} = M \frac{di_{L1}}{dt} \tag{3-3}$$

Where mutual inductance,  $M = k \sqrt{L_1 L_2}$ , and k is the coupling coefficient.

$$\frac{L_2}{L_1} = \left(\frac{N_2}{N_1}\right)^2 = n^2 \Rightarrow L_2 = n^2 L_1$$

(3-4)

Where *n* is the turns ratio defined as  $\frac{N_2}{N_1}$ .

$$M = k\sqrt{n^2 L_1^2} \Rightarrow knL_1 \tag{3-5}$$

$$\therefore V_{L2} = M \frac{di_{L1}}{dt} = nkL_1 \frac{di_{L1}}{dt} = nkV_{L1} = nkV_{in}$$

(3-6)

$$V_L = V_{L1} + V_{L2} = (1 + nk)V_{L1}$$

(3-7)

$$\Rightarrow V_{L,on} = (1+nk) \times V_{in} \tag{3-8}$$

Where,  $V_{L,on}$  is tapped-coupled-inductor voltage when the switch is conducting.

Expression for current through the capacitor  $C_{out}$  in figure 3.2 is obtained as:

$$i_c = C \frac{dV_o}{dt} = -\frac{V_o}{R} \tag{3-9}$$

Input current during this interval is given as:

$$i_{in} = i_{L1} \tag{3-10}$$

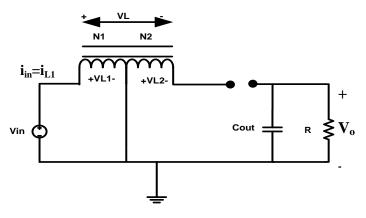

#### b) When the switch is off, $DT_s < t < T_s$

When the switch is off, the diode is forward biased. Energy stored in the inductors and from the input is supplied through the conducting diode to the output. Both windings N<sub>1</sub> and N<sub>2</sub> conduct the same current  $i_L$ . The voltage across both inductors is equal to  $(V_{in} - V_o) = V_1 + V_2$ , where  $V_1$  and  $V_2$  are shown in equations (3-11) and (3-12). As it can be seen

Chapter 3

Boost Converter with tapped-coupled-inductors

in these two equations, the voltage across each of the inductors has an induced voltage component.

$$V_1 = L_1 \frac{di_L}{dt} + M \frac{di_L}{dt} \Rightarrow (L_1 + M) \frac{di_L}{dt}$$

(3-11)

$$V_2 = L_2 \frac{di_L}{dt} + M \frac{di_L}{dt} \Rightarrow (L_2 + M) \frac{di_L}{dt}$$

(3-12)

Figure 3.3. Tapped-coupled-inductor boost converter with the output diode conducting.

This induced voltage across each of the inductors is due to the mutual inductance between the coupled inductors. The induced voltage leads to an increased voltage across both inductors, hence a higher boost ratio.

$$\frac{V_1}{L_1 + nkL_1} = \frac{V_2}{n^2 L_1 + nkL_1}$$

(3-13)

Since  $M = nkL_1$  and  $L_2 = n^2L_1$

$$V_2 = \left(\frac{n^2 + nk}{1 + nk}\right) \times V_1 \tag{3-14}$$

Referring to figure 3.3,

$$(V_{in} - V_o) = V_1 + V_2 \tag{3-15}$$

$$(V_{in} - V_o) = V_1 + \left\{ \left( \frac{n^2 + nk}{1 + nk} \right) \times V_1 \right\}$$

(3-16)

27

Department of Electrical, Electronic and Computer Engineering University of Pretoria

Boost Converter with tapped-coupled-inductors

$$\Rightarrow \{V_{in} - V_o\} = V_{L,off} = V_1 \times \left\{\frac{n^2 + 2nk + 1}{1 + nk}\right\}$$

(3-17)

Where,  $V_{L,off}$  is tapped-coupled-inductor voltage when the switch is not conducting.

An expression for the output capacitor current during this interval is given as:

$$i_c = C \frac{dV_o}{dt} = i_L - \frac{V_o}{R} \tag{3-18}$$

Input current during this interval is given as:

$$i_{in} = i_L \tag{3-19}$$

In steady-state, the average voltage across the two coupled inductors over a switching period should be equal to zero, hence

$$\langle V_L \rangle = 0 = D\{(1+nk) \times V_{in}\} + \{(1-D)(V_{in} - V_o)\}$$

(3-20)

$$0 = V_{in}(1 + nkD) - V_o(1 - D)$$

(3-21)

From equation (3-21) the voltage transfer ratio (the ratio of the output voltage,  $V_o$  to the

input voltage  $V_{in}$ ) is obtained as

$$\frac{V_o}{V_{in}} = \frac{1+nkD}{1-D} \tag{3-22}$$

For a k of 1,

$$\frac{V_0}{V_{in}} = \frac{1+nD}{1-D}$$

(3-23)

From equation (3-22), it can be seen that the voltage transfer ratio of the tapped-coupled boost converter depends on:

- $\circ$  Duty ratio, D

- $\circ$  Turns ratio, *n*

- $\circ$  Coupling coefficient, k

When *n* is equal to zero, the tapped-coupled boost converter is reduced to the conventional boost converter which has a voltage gain  $\frac{V_o}{V_{in}} = \frac{1}{1-D}$ .

Re-arranging equation (3-22) yields an expression for duty ratio as,

$$D = \frac{\binom{V_0}{V_{in}} - 1}{\binom{V_0}{V_{in}} + nk}$$

(3-24)

From equation (3-24), it is shown that as *n* increases, for a given voltage gain,  $(V_o/V_{in})$ , there will be a non-linear decrease in *D*.

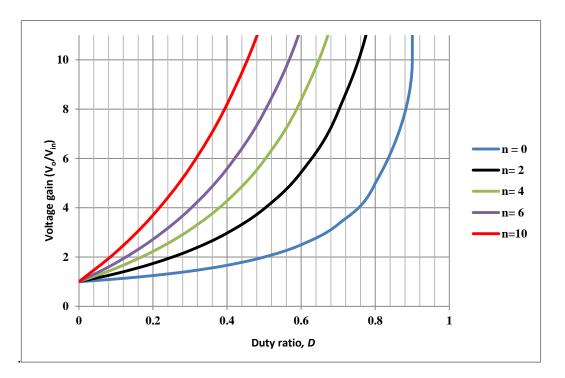

Figure 3.4 shows the relationship between voltage gain, duty ratio, D, and turns ratio, n, for a coupling coefficient, k, of 0.98.

Figure 3.4. Voltage gain against duty ratio D

It can be seen that the conventional boost converter with n = 0 requires an extremely high duty ratio to achieve a high voltage gain. With an extreme duty ratio, the output rectifier diode conducts for a very short period sustaining a short pulse width current with a high amplitude. This results in severe reverse-recovery problems and increased device stress. An extreme duty ratio leads to requirements of a high current and voltage rated switch, increasing conduction losses, switching losses and cost. As a result, the conversion efficiency is degraded, EMI problem is likely to be severe and the power level of the

#### Boost Converter with tapped-coupled-inductors

converter is limited. The switch also becomes under-utilised. Furthermore, an extreme duty ratio does not leave room for control to compensate changes in the input or the load [37].

However, the use of the tapped-coupled inductor boost converter with a higher turns ratio makes it possible to achieve high step-up ratios with a low duty ratio. As shown in Figure 3.4, a voltage gain of 10 is achieved with a duty ratio of 0.9 in the classical boost converter. However, with a duty ratio of just 0.56, the same voltage gain can be achieved by the tapped-coupled boost converter with a turns ratio of 6 and even a lower duty ratio of 0.46 with a turns ratio of 10. The selection of number of turns however, should be a trade off since with a very high turns ratio a high boost ratio is achieved but; (1) losses in winding  $N_2$  increase leading to a lower efficiency, (2) a small input variation leads to a large output variation which makes control difficult, (3) inductor  $L_2$  value would be large leading to reduced dynamic response (4) the input current peak-to-peak ripple increases.

The coupling coefficient, k, is a measure of the magnetic coupling between two coils and lies in the range  $0 \le k \le 1$ . When the two windings are tightly coupled so that all the flux linking the primary winding also links the secondary winding, there is no leakage inductance and k=1. This is an ideal situation because it is impossible to wind two coils so that they share precisely the same magnetic flux. High values of coupling coefficient of about 0.98 can however be obtained by tight coupling of the windings thus reducing the leakage inductances in the tapped-coupled inductors.

It can be seen that a high boost ratio is obtained with a high coupling coefficient in the tapped-coupled boost converter from equation (3-22). A low value of k also means high leakage inductance which results in high voltage spikes across the switch during turn-off. This results in efficiency degradation due to the increased switching losses.

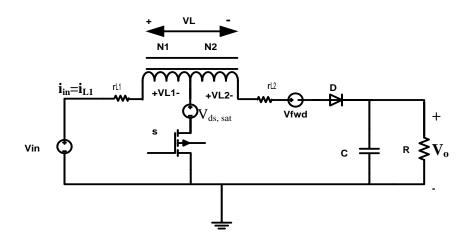

#### 3.1.2 Non-ideal characteristics

The model analysed in this section is shown in Figure 3.5 and accounts for winding resistances in the tapped-coupled inductors,  $r_{L1}$  and  $r_{L2}$ , voltage drop across the conducting active switch and the forward voltage drop across the output diode. Through analysis, the effects of these parasitic components and voltage drops are demonstrated.

Figure 3.5. A tapped-coupled-inductor boost converter with non-ideal components.

a) When the switch is conducting, 0 < t < DTs

Figure 3.6. A non-ideal tapped-coupled-inductor boost converter when the active switch is conducting.

During this interval, the output diode D is reverse biased while the active switch conducts as shown in Figure 3.6. The input voltage  $V_{in}$  is thus described as,

$$V_{in} = V_{L1} + i_{L1}r_{L1} + i_{L1}r_{ds,on} \tag{3-25}$$

$$\therefore V_{L1} = L_1 \frac{di_{L1}}{dt} = \left( V_{in} - i_{L1} r_{ds,on} - i_{L1} r_{L1} \right)$$

(3-26)

#### Boost Converter with tapped-coupled-inductors

No current flows through the second inductor during this interval, but due to coupling, a voltage  $V_{L2}$  appears across this inductor given as,

$$V_{L2} = M \frac{di_{L1}}{dt} = nkL_1 \frac{di_{L1}}{dt} = nkV_{L1} = nk(V_{in} - i_{L1}r_{ds,on} - i_{L1}r_{L1})$$

(3-27)

The total voltage across the two tapped-coupled inductors during this interval,  $V_L$  is thus given by

$$V_L = V_{L1} + V_{L2} = (1 + nk)V_{L1}$$

(3-28)

$$\Rightarrow V_{L,on} = (1+nk) \times \left( V_{in} - i_{L1} r_{ds,on} - i_{L1} r_{L1} \right)$$

(3-29)

Where,  $V_{L,on}$  is tapped-coupled-inductor voltage when the switch is conducting.

An expression for the output capacitor current in figure 3.6 is obtained as:

$$i_c = C \frac{dV_o}{dt} = -\frac{V_o}{R} \tag{3-30}$$

Input current during this interval is given as:

$$i_{in} = i_{L1} \tag{3-31}$$

Where,  $i_{L1}$  is the inductor current when both windings N<sub>1</sub> and N<sub>2</sub> are conducting.

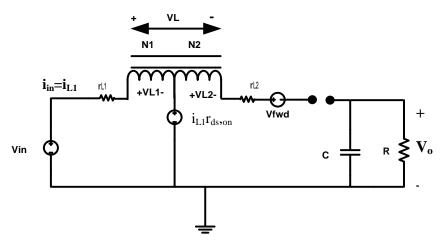

c) When the switch is off,  $DT_s < t < T_s$

During this interval, the same current,  $i_L$ , flows through both inductors. The voltage across the tapped-coupled inductors includes a voltage due to mutual inductance between the two inductors. Referring to Figure 3.7, the voltage across the coupled inductors is expressed as,

$$V_1 = L_1 \frac{di_L}{dt} + M \frac{di_L}{dt} \Rightarrow (L_1 + M) \frac{di_L}{dt}$$

(3-32)

$$V_2 = L_2 \frac{di_L}{dt} + M \frac{di_L}{dt} \Rightarrow (L_2 + M) \frac{di_L}{dt}$$

(3-33)

Department of Electrical, Electronic and Computer Engineering University of Pretoria

Chapter 3

Figure 3.7. Tapped-coupled-inductor boost converter with the output diode conducting.

Since the same current is flowing through both inductors during this interval its rate of change  $\frac{di_L}{dt}$  is also equal, thus,

$$\frac{V_1}{L_1 + nkL_1} = \frac{V_2}{n^2 L_1 + nkL_1} \tag{3-34}$$

Since  $M = nkL_1$  and  $L_2 = n^2L_1$

$$V_2 = \left(\frac{n^2 + nk}{1 + nk}\right) \times V_1 \tag{3-35}$$

Referring to Figure 3.7, the input and output voltage can be related to inductor voltage as,

$$(V_{in} - V_o) = V_1 + V_2 + i_L (r_{L1} + r_{L2}) + V_{fwd}$$

(3-36)

Then using equation (3-34), an expression for the tapped-coupled-inductor voltage when the switch is off is obtained as,

$$(V_{in} - V_o) = V_1 + \left\{ \left( \frac{n^2 + nk}{1 + nk} \right) \times V_1 \right\} + i_L \left( r_{L1} + r_{L2} \right) + V_{fwd}$$

(3-37)

$$V_{L,off} = \left\{ V_{in} - V_o - V_{fwd} - i_L \left( r_{L1} + r_{L2} \right) \right\} = V_1 \left\{ \frac{n^2 + 2nk + 1}{1 + nk} \right\}$$

(3-38a)

Boost Converter with tapped-coupled-inductors

Chapter 3

Referring to Figure 3.7

$$V_{L1} = \left(\frac{N_1}{N_1 + N_2}\right) \times V_{L,off} = \left(\frac{1}{1+n}\right) \times \left\{V_{in} - V_o - V_{fwd} - i_L \left(r_{L1} + r_{L2}\right)\right\}$$

(3-38b)

$$V_{L2} = \left(\frac{N_2}{N_1 + N_2}\right) \times V_{L,off} = \left(\frac{n}{1+n}\right) \times \left\{V_{in} - V_o - V_{fwd} - i_L \left(r_{L1} + r_{L2}\right)\right\}$$

(3-38c)

An expression for current through the output capacitor during this interval is given as:

$$i_c = C \frac{dV_o}{dt} = i_L - \frac{V_o}{R}$$

(3-39)

Input current during this interval is given as:

$$i_{in} = i_L = i_{L1}$$

(3-40)

Equations (3-28) and (3-37) are averaged for the two time intervals using duty ratio as a weight to obtain one voltage equation applicable over one switching period:

$$V_{L} = L \frac{di_{L}}{dt} = \left[ D \times \left\{ (1 + nk) \times \left( V_{in} - i_{L1} r_{ds,on} - i_{L1} r_{L1} \right) \right\} \right] \\ + \left[ (1 - D) \times \left\{ V_{in} - V_{o} - V_{fwd} - i_{L} \left( r_{L1} + r_{L2} \right) \right\} \right]$$

(3-41)

The equation for the output voltage is obtained as:

$$V_{o} = \frac{1}{(1-D)} \{ V_{in}(1+nkD) + V_{fwd}(D-1) - Di_{L1}r_{ds,on}(1+nk) - Dni_{L}r_{L1}(1+k(1+n)) - i_{L}(r_{L1}+r_{L2}) \}$$

(3-42)

The ripple current through the capacitor over one switching period is:

$$i_c = C \frac{dv_c}{dt} = \left[ D \times \left( -\frac{V_o}{R} \right) \right] + \left[ (1-D) \times \left( i_L - \frac{V_o}{R} \right) \right]$$

(3-43)

The average input current over one switching period is given as:

$$I_{in,ave} = I_L(nkD + 1) \tag{3-44}$$

34

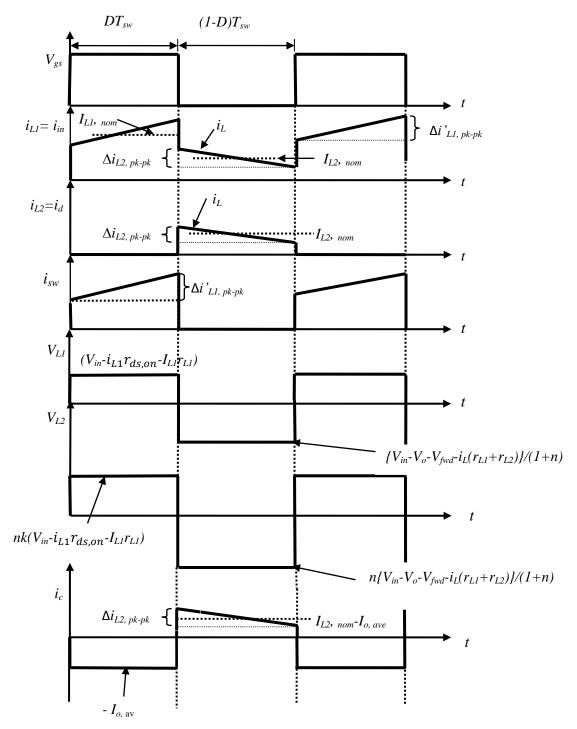

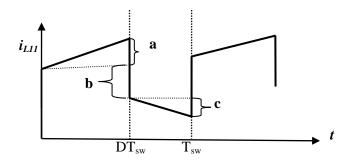

The key waveforms of a single phase tapped-coupled inductor boost converter are shown in Figure 3.8.

Figure 3.8. Key waveforms for the single-phase tapped-coupled inductor boost converter.

Department of Electrical, Electronic and Computer Engineering University of Pretoria

#### Boost Converter with tapped-coupled-inductors

Due to the tapped-coupled inductor, the shape of the current through the inductor is quite different from that for a conventional boost converter. When the active switch is conducting, the current through the first inductor winding  $N_1$  ramps up linearly from an initial value until when the switch goes off. At this interval, no current flows through the second winding  $N_2$  since the diode is reverse biased.

During the switching transitions, the flux through the core cannot change instantaneously, therefore the current through  $N_1$  steps down immediately when the switch is turning off. When the active switch stops conducting, the diode becomes forward biased and the same current flows through both sections  $N_1$  and  $N_2$  of the tapped inductor.

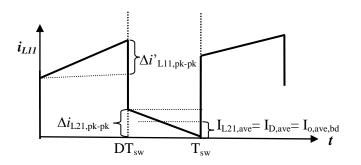

#### 3.1.3 Input and capacitor current RMS ripple derivation

In this section, expressions for the input current peak-to-peak ripple, RMS current, RMS ripple and the output capacitor RMS current are obtained. With reference to Figure 3.8, the following expressions are obtained,

$$I_{L2,ave} = I_{o,ave} = I_{L2,nom}(1-D)$$

(3-45)

$$I_{L2,nom} = \frac{I_{o,ave}}{(1-D)} \tag{3-46}$$

If operating conditions are ideal,

$$P_{in} = P_o \Rightarrow V_{in,ave} I_{in,ave} = V_{o,ave} I_{o,ave}$$

(3-47)

But from equation (3-22),

$$V_{o,ave} = V_{in,ave} \frac{1+nkD}{1-D}$$

(3-48)

$$V_{in,ave} \frac{1+nkD}{1-D} I_{o,ave} = V_{in,ave} I_{in,ave}$$

(3-49)

$$I_{in,ave} = \frac{1 + nkD}{1 - D} I_{o,ave} = I_{L1,ave}$$

(3-50)

$$I_{in,ave} = I_{L1,ave} = I_{L1,nom}D + I_{L2,nom}(1-D) = \frac{1+nkD}{1-D}I_{o,ave}$$

(3-51)

Boost Converter with tapped-coupled-inductors

Substituting equation (3-46) into (3-51) yields,

$$I_{L1,nom}D + \frac{I_{o,ave}}{(1-D)}(1-D) = \frac{1+nkD}{1-D}I_{o,ave}$$

(3-52)

$$I_{L1,nom}D = \left(\frac{1+nkD}{1-D} - 1\right)I_{o,ave} = \left(\frac{D+nkD}{1-D}\right)I_{o,ave}$$

(3-53)

Expressions for  $I_{L1, nom}$  and  $I_{in, ave}$  are obtained in terms of  $I_{L2, nom}$  as,

$$I_{L1,nom} = \left(\frac{1+nk}{1-D}\right) I_{o,ave} = (1+nk)I_{L2,nom}$$

(3-54)

$$I_{in,ave} = I_{L1,ave} = (1 + nk)I_{L2,nom}D + I_{L2,nom}(1 - D) = (nkD + 1)I_{L2,nom} (3-55)$$

From equations (3-26) and (3-38),

$$\Delta i'_{L1,pk-pk} = \frac{(V_{in} - i_{L1}r_{ds,on} - i_{L1}r_{L1})DT_{sw}}{L_1}$$

(3-56)

$$\Delta i_{L2,pk-pk} = \frac{n \left( V_{in} - V_o - V_{fwd} - i_L \left( r_{L1} + r_{L2} \right) \right) (1 - D) T_{sw}}{(n+1)L_2}$$

(3-57)

An expression for the input RMS current in a single-phase tapped-coupled-inductor boost converter is then obtained as,

$$I_{L1,rms} = \sqrt{\left\{ \left( I_{L1,nom} \right)^2 D \left[ 1 + \frac{1}{3} \left( \frac{\Delta i'_{L1,pk-pk}}{2I_{L1,nom}} \right)^2 \right] + \left( I_{L2,nom} \right)^2 (1-D) \left[ 1 + \frac{1}{3} \left( \frac{\Delta i_{L2,pk-pk}}{2I_{L2,nom}} \right)^2 \right] \right\}$$

(3-58a)

Substituting equations (3-46) and (3-54) in to (3-58a), the expression for the input RMS current is obtained as,

$$I_{L1,rms} = I_{in,rms} = \sqrt{\left\{ \left( \left(\frac{1+nk}{1-D}\right) I_{o,ave} \right)^2 D \left[ 1 + \frac{1}{3} \left( \frac{\Delta i_{L1,pk-pk}}{2\left(\frac{1+nk}{1-D}\right) I_{o,ave}} \right)^2 \right] + \left( \frac{I_{o,ave}}{(1-D)} \right)^2 (1-D) \left[ 1 + \frac{1}{3} \left( \frac{\Delta i_{L2,pk-pk}}{2\left(\frac{I_{o,ave}}{(1-D)}\right)} \right)^2 \right] \right\}$$

(3-58b)

37

Chapter 3

From equation (3-58b), it is seen that input RMS current is dependent on turns ratio, coupling coefficient and duty ratio and tends to infinity as duty ratio approaches to unity. For a given duty ratio, a high value of turns ratio and coupling coefficient results to a high value of input RMS current.

The input RMS current ripple can then be obtained with reference to figure. 3.8 and equations (3-51) and (3-58b) as.

$$I_{in,ripple,rms} = I_{o,ave} \sqrt{\left\{ D\left(\frac{1+nk}{1-D}\right)^2 \left[ 1 + \frac{1}{3} \left(\frac{\Delta i'_{L1,pk-pk}}{2\left(\frac{1+nk}{1-D}\right)I_{o,ave}}\right)^2 \right] + \frac{1}{(1-D)} \left[ 1 + \frac{1}{3} \left(\frac{\Delta i_{L2,pk-pk}}{2\left(\frac{lo,ave}{(1-D)}\right)}\right)^2 \right] - \left(\frac{1+nkD}{1-D}\right)^2 \right\}}$$

(3-59)

It is seen from equation (3-59) that the input RMS current ripple expression tends to infinity as the duty ratio approaches unity. The input ripple also is seen to depend on turns ratio, coupling coefficient, duty ratio and load current. A high value of duty ratio, turns ratio, coupling coefficient and load current result to a high input ripple current.

The input current peak-to-peak ripple can be expressed as,

$$i_{in,pk-pk} = \left[ I_{L1,nom} + \frac{1}{2} \left( \Delta i'_{L1,pk-pk} \right) \right] - \left[ I_{L2,nom} + \frac{1}{2} \left( \Delta i_{L2,pk-pk} \right) \right]$$

(3-60)

Substituting equations (3-46), (3-54), (3-56) and (3-57) into (3-60), the peak-to-peak ripple is obtained as,

$$i_{in,pk-pk} = \left[ \left(\frac{nk}{1-D}\right) I_{o,ave} + \left(\frac{(V_{in} - i_{L1}r_{ds,on} - i_{L1}r_{L1})DT_{sw}}{2L_1} \right) \right] + \left(\frac{n(V_{in} - V_o - V_{fwd} - i_L(r_{L1} + r_{L2}))(1-D)T_{sw}}{2(n+1)L_2} \right)$$

(3-61)

The input peak-to-peak current in expression (3-61) is seen to increase with increase in turns ratio, coupling coefficient, inductor value, duty ratio and load current. This expression tends to infinity as duty ratio approaches unity.

Referring to the capacitor current waveform in Figure 3.8 and equation (3-46), an expression for capacitor RMS current is obtained as,

$$I_{c,rms} = \sqrt{\left\{ \left( I_{o,ave} \right)^2 D + \left( I_{L2,nom} - I_{o,ave} \right)^2 (1 - D) \left[ 1 + \frac{1}{3} \left( \frac{\Delta i_{L2,pk-pk}}{2(I_{L2,nom} - I_{o,ave})} \right)^2 \right] \right\}}$$

(3-62a)

$$I_{c,rms} = \sqrt{\left\{ \left( I_{o,ave} \right)^2 D + \left( \frac{DI_{o,ave}}{(1-D)} \right)^2 (1-D) \left[ 1 + \frac{1}{3} \left( \frac{\Delta i_{L2,pk-pk}}{2\left( \frac{DI_{o,ave}}{(1-D)} \right)} \right)^2 \right] \right\}}$$

(3-62b)

It is seen from equation (36) that capacitor RMS current is almost independent of turns ratio and coupling coefficient for a fixed load current except for the term  $\Delta i_{L2, pk-pk}$ .

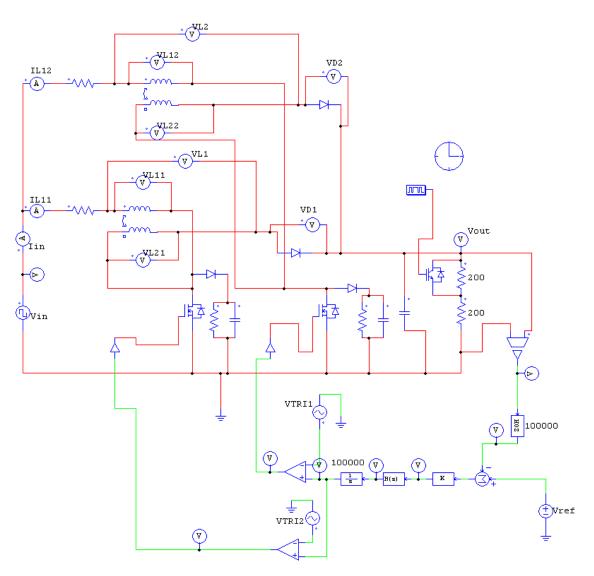

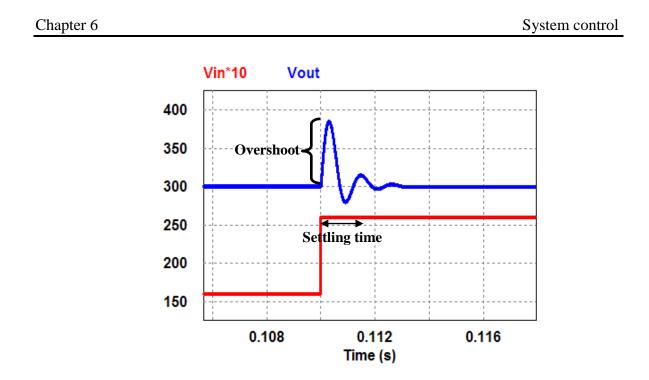

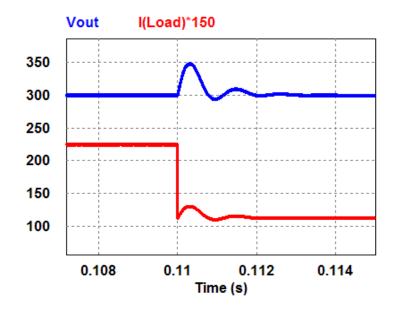

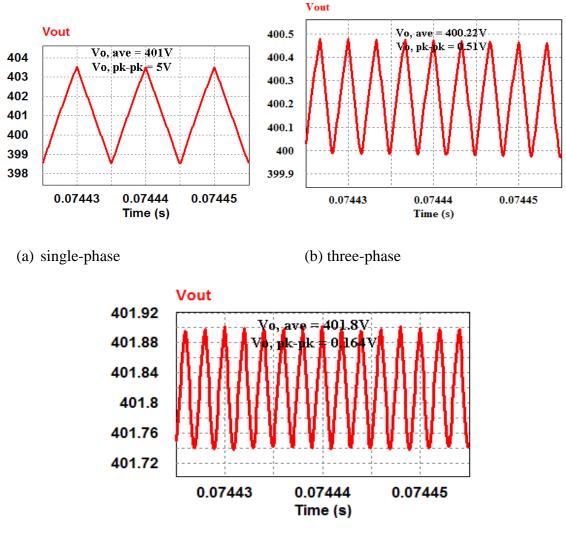

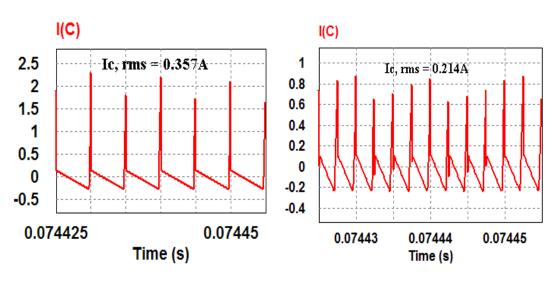

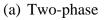

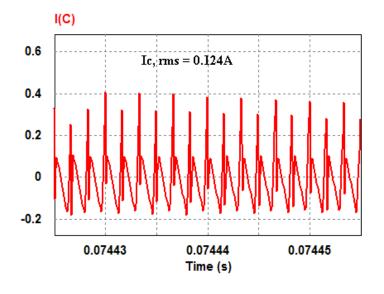

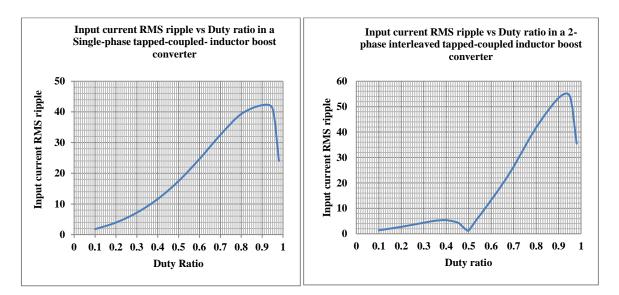

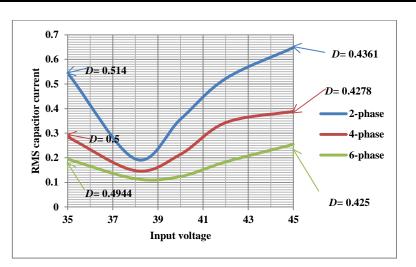

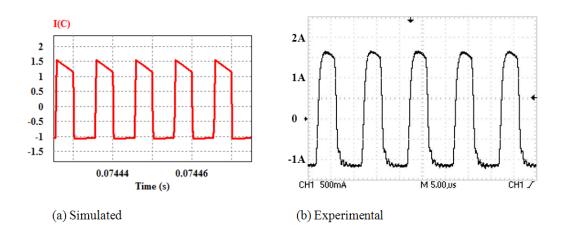

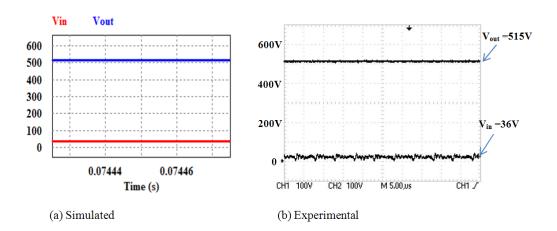

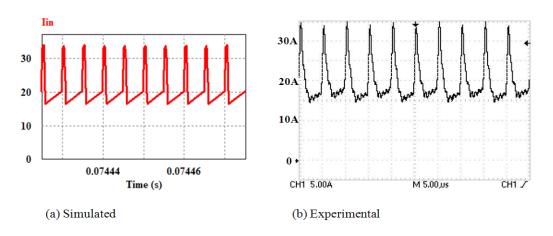

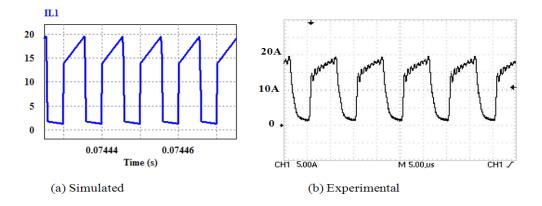

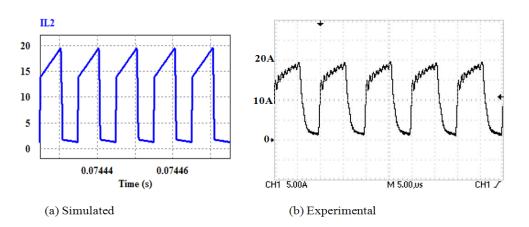

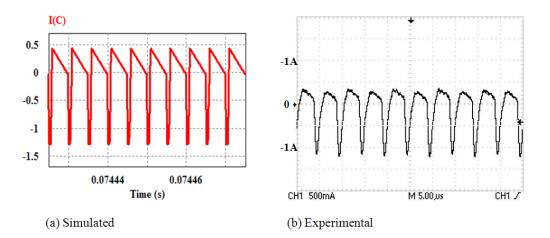

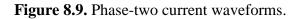

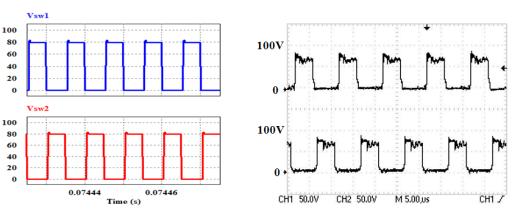

#### 3.2 SMALL-SIGNAL MODEL OF THE SINGLE-PHASE TAPPED-COUPLED-INDUCTOR BOOST CONVERTER.