## **CHAPTER 3**

# **EXPERIMENTAL TECHNIQUES**

#### 3.1 Introduction

In this chapter, the apparatus and techniques used will be described. Section 3.2 presents sample preparation, i.e. cleaning process, ohmic and Schottky contact fabrication. In section 3.3 Schottky diode characterization techniques (i.e. current-voltage (I-V), capacitance-voltage (C-V), and temperature dependent I-V and C-V are discussed. Deep level transient spectroscopy (DLTS), a defect characterization technique is outlined in section 3.4. Section 3.5 deals with the Rutherford backscattering spectrometry, utilised to study the in-diffusion of thin film metals on germanium. Scanning electron microscope system is presented in section 3.6. This chapter ends with a discussion of annealing apparatus in section 3.7.

## 3.2 Sample preparations

Prior to metallization, the germanium samples were cut into  $(0.5 \times 0.3)$  cm<sup>2</sup> followed by a chemical cleaning process. Cleanliness is essential to achieving high yields and reproducible process in the production of any microelectronic devices [1]. Before metallization the semiconductor should be atomically as clean as possible and stoichiometrically perfect [2], in order to obtain high quality Schottky barrier diodes with a low leakage current when reverse biased.

## 3.2.1 Germanium cleaning process

Before metallization the following cleaning procedure was followed:

- i) Degreasing the samples in trichloroethylene (TCE), acetone and then methanol, each for five minutes in an ultrasonic bath at room temperature. The degreasing process is followed by rinsing the sample in de-ionized water of resistivity < 18 M $\Omega$ cm.

- ii) Etching in a solution of 30% H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O (1:5) for one minute for the removal of the remaining oxide layer and insoluble organic contaminants and then followed by rinsing in de-ionized water.

- iii) The samples are blown-dry in a stream of filtered, dry, nitrogen gas, and ready for metallization.

#### 3.2.2 Ohmic and Schottky contact fabrication

The ohmic contacts were fabricated by resistively evaporating a 100 nm thick layer of Au-Sb (0.6% Sb) on the back surface of the germanium samples. The deposition follows the evacuating of the deposition chamber to pressure below 10<sup>-6</sup> Torr. The samples were then annealed for ten minutes at 350°C in Ar, to optimize the ohmic contact by lowering the barrier height, hence reducing its resistivity [3]. The annealing process results in the infusion of Sb into the backside of the germanium resulting in the increase of doping concentration. This leads to a very thin depletion region, known as a tunnel junction [4], through which field emission can take place. The use of Ar gas reduces oxidation of the metal during the annealing process, while it can also reduce interfacial oxide between the semiconductor and the metal.

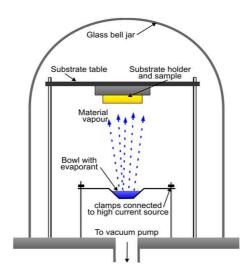

A schematic of the vacuum resistive deposition system is shown in Fig. 3.1. A current flows through the crucible containing the metal to be evaporated. The molten metal evaporates and deposits onto the sample mounted above the crucible. Only metals with melting points less than 1 600°C are evaporated from this system.

Before Schottky contact deposition, the samples were again chemically cleaned as described in section 3.2.1. The Schottky contacts 0.6 mm in diameter, 30 nm thick were either fabricated by resistive deposition or electron beam deposition.

Fig. 3.1 A Schematic representation of the vacuum resistive deposition system

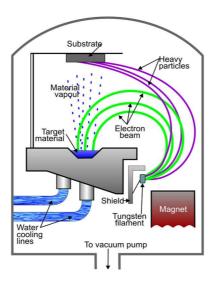

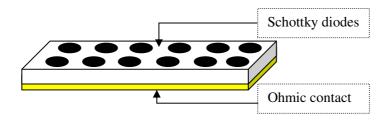

The electron beam deposition (EBD) system is depicted in Fig. 3.2. In the electron beam deposition system, a hot filament emits a beam of electrons, focused onto the crucible containing the metal by magnetic and electric fields, resulting in the melting and evaporation of the metal which deposits onto the sample. Fig. 3.3 shows the sample after the metallization process.

**Fig. 3.2** A schematic representation of the electron beam deposition system

Fig. 3.3 A sample showing Schottky contacts and ohmic layer.

## 3.3 Current-Voltage and Capacitance-Voltage measurements

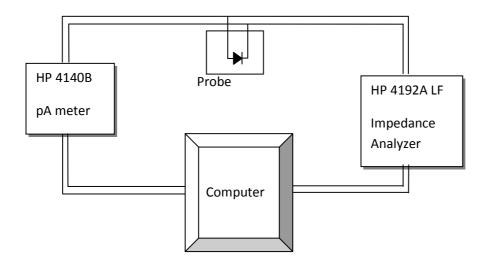

After contact fabrication, electrical characterization through current-voltage (I-V) and capacitance-voltage (C-V) measurements were carried out at room temperature. The (I-V) measurements were made by an HP 4140 B pA meter/ DC voltage source, capable of measuring current limit of  $10^{-14}$  A. The (C-V) characteristics were measured by an HP 4192A LF Impedance Analyzer. The samples were measured in the dark and screened from electrical noise by enclosing them in a light-tight metal box. The most important diode parameters obtained from the (I-V) and (C-V) measurements are series resistance  $R_s$ , the barrier height  $\phi_{B(I-V)}$ , the ideality factor n, reverse current  $I_r$  measured at a reverse bias of 1 V and free carrier density  $N_D$ . Fig. 3.4 depicts a schematic diagram of the (I-V), (C-V) station used during the electrical characterization of the samples. Isochronal annealing of the samples was performed in the temperature range 25°C to 700°C in steps of 25°C for 30 minutes in Ar atmosphere. I-V and C-V measurements followed each annealing cycle.

**Fig. 3.4** *Block diagram of (I-V) and (C-V) station for determining the diode characteristics.*

Temperature dependent (*I-V*) measurements, in the 20-300 K temperature range were performed in a He cryostat using an automated Labview program. From the measurements, ideality factor (n), series resistance (R<sub>s</sub>), reverse saturation current (I<sub>r</sub>), and barrier height ( $\Phi_{B(I-V)}$ ) as function of temperature, were extracted. Temperature dependent (*C-V*) measurements were recorded at a frequency of 1 MHz for voltage ranging from 0 V to –1 V and temperature range of 20-300 K via a Labview program. The barrier height ( $\Phi_{B(I-V)}$ ) and the carrier concentration ( $N_D$ ) were obtained from the plot of  $1/C^2 vs V$ .

# 3.4 Deep level transient spectroscopy (DLTS) and Laplace-DLTS system

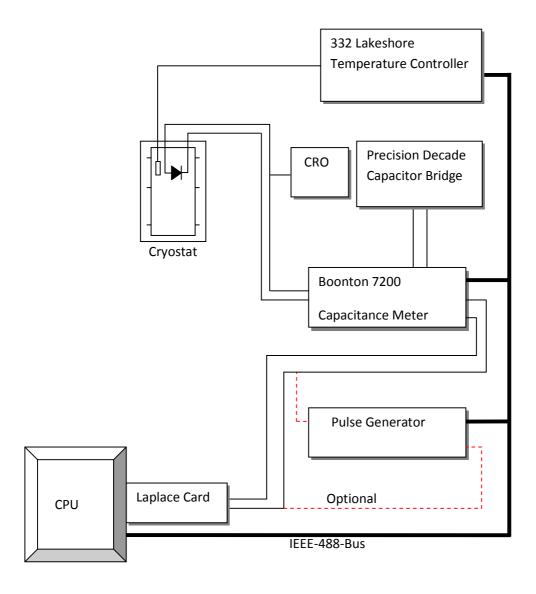

The layout of the DLTS and LDLTS system used in this study is illustrated in Fig. 3.5. The system consists of:

- i) A cryostat, in which the sample is mounted. The cryostat temperature is controlled by a Lakeshore 340 temperature controller in the range 16-380 K.

- ii) Boonton 7200 capacitance meter, with 100 mV, 1 MHz AC ripple voltage, and it monitors thermal emission after excitation by a pulse generator.

- iii) A Laplace card, which has an internal pulse generator for generating the appropriate quiescent bias and pulses. This card is also the data collection and processing system which analyses and averages the transients prior to displaying the spectra for either the conventional DLTS or L-DLTS.

- iv) HP 33120 15 MHz Function waveform external generator, for providing the desired quiescent bias and filling pulse to the diode which are not provided by the Laplace card.

The Laplace card sets the sample excitation parameters, capacitance transient acquisition conditions, and then initiates the measurement, acquiring the transient and converts it into either a DLTS or LDLTS spectrum depending on the measurements. For conventional DLTS the capacitance transients after excitation are measured by the capacitance meter. These transients are then processed by the Laplace card. As the temperature is ramped a DLTS spectrum is displayed on a computer for a particular rate window. L-DLTS gives an intensity output as a function of emission rate. The measurement is carried out at a fixed temperature, and several capacitance transients are captured and averaged. In the isothermal DLTS method, the sample temperature is held constant while the sampling time is varied. This technique also uses the equation

$$C(t) = C_0 \left[ 1 - \left( \frac{n_T(0)}{2N_D} \right) \exp\left( -\frac{t}{\tau_e} \right) \right]$$

(3.1)

From Eq. (3.1) the function tdC(t)/dt plotted against t has a maximum value  $n_T(0)C_0/2N_D(1/e)$  at  $t=\tau_e$ . From a series of tdC(t)/dt against t plots at various constant temperatures permits an Arrhenius plot of  $\ln(\tau_e T^2)$  against 1/T, similar to a conventional DLTS plot. The main difference is the constancy of the temperature during measurement. In the conventional DLTS C(t) measurements have to be made over a wide time range, requiring high frequency capacitance meters.

Fig. 3.5 Block diagram of the DLTS and LDLTS

## 3.5 Rutherford backscattering spectrometry

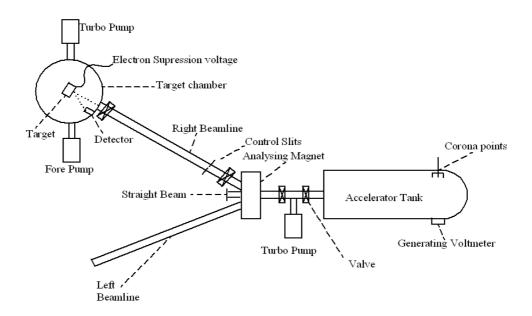

Rutherford backscattering spectrometry (RBS) is a technique based on the analysis of the energy of the backscattered charged particles such as He<sup>+</sup> used in this study. In this study, RBS technique was used to investigate the in-diffusion of metals deposited on Ge at different annealing temperatures. The schematic diagram of the RBS system attached to a Van de Graaff 2.5 MeV at the University of Pretoria is depicted in Fig. 3.6. The charged particles are generated from a gas introduced into the ion source, and accelerated to high energies up to 1.8 MeV by applying a large potential difference across the accelerator tube. The energy of 1.6 MeV was used in this study. The acceleration voltage is generated from a moving insulating belt that carries charge that is sprayed on at base plate, and this charge is removed as a column current flowing through a set of resistors [5].

The dipole magnet in front of the Van de Graaff accelerator acts as an energy and mass separator. It deflects the beam into either the left beam line or right beam line. The Left Beam line is designed to operate below room temperature while the right beam line operates at room temperature. For this study, the right beam line was used. The beam of positively-charged ions (He<sup>+</sup>) passes through slits that stabilise the accelerating voltage, and they are collimated into a specific size before they reach the target. Secondary electrons are suppressed by a negative voltage of 200 V connected to a ring electrode in front of the target holder.

The backscattered alpha particles are detected by a Si surface barrier detector operating with a reverse bias of 40 V, and connected to a pre-amplifier where it is integrated into a voltage signal that is proportional to backscattered energy. This voltage signal is amplified before it is converted to a digital signal by an analogue to digital converter (ADC) inside the multi-channel analyzer (MCA). The MCA output is a spectrum of the yield (counts) *versus* channel number. The yield is the number of backscattered particles at 165°, while the channel number is proportional to the backscattered energy.

**Fig. 3.6** Block diagram of the Rutherford backscattering spectrometry attached to Van de Graaf accelerator at the University of Pretoria.

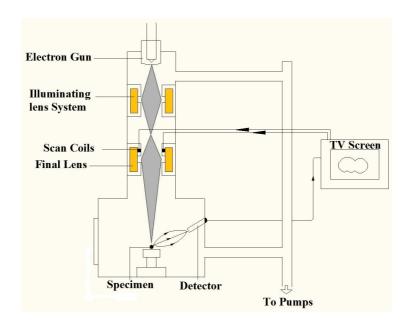

## 3.6 Scanning electron microscopy

A scanning electron microscope (SEM), shown in Fig 3.7 is a high resolution microscope that uses electrons rather than light for imaging on conducting materials. A highly focused electron beam is created in the electron gun by the heated filament. The electron gun provides a stable electron beam of adjustable energy. The electron beam is guided into the aperture by lenses. When focused on the surface, the electron beam stimulates the emission of different electrons such as back scattered electrons and secondary electrons, and the signal produced is detected and amplified to increase the brightness of the Cathode Ray Tube (CRT) display. The energy of the electrons is directly related to the desired image. The ZEISS ULTRA PLUS and the JEOL JSM-5800LV SEM systems were operated at a pressure below 10<sup>-6</sup> Torr and at voltages of 1 kV and 5 KV, respectively.

Fig. 3.7 Scanning electron microscope system.

## 3.7 Annealing apparatus

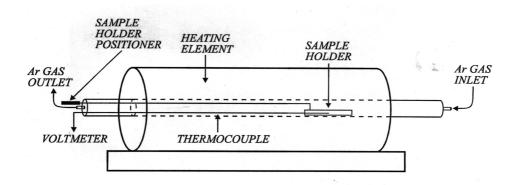

All the annealing experiments were carried out in a Lindberg "heavy duty" furnace (200-1200°C), in argon atmosphere at an approximate flow rate of 2 litres/min. The annealing temperature was monitored by a thermocouple placed inside the sample holder just under the sample. The annealing furnace used in this study is shown schematically in Fig 3.8.

Fig. 3.8 Lindberg "Heavy duty" annealing furnace

# References

- [3] F.D. Auret, P.J. Janse van Rensburg, M. Hayes, J.M. Nel, S. Coelho, W.E. Meyer,

S. Decoster, V. Matias, A. Vantomme, D. Smeets, Nucl. Instr. And Meth. B 257 (2007)

169.

- [4] R.R. Lieten, S. Degroote, M. Kuijk, and G. Borghs, Appl. Phys. Lett. **92** (2006) 022106.

- [5] R.J. van de Graaf, Phys Rev. **38** (1931) 1919.

<sup>[1]</sup> R.E. Williams: Gallium Arsenide Processing Techniques (Artech House) (1984) 85.

<sup>[2]</sup> F.D. Auret, W.O. Barnard, G. Myburg and L.J. Bredell: S. Afr. J. Sci. 87 (1991) 127.

## **CHAPTER 4: RESULTS**

# Thermal annealing behaviour of metal Schottky contacts on n-Ge (100)

## 4.1 Introduction

So far, several studies have been done concerning the reactions of Ge with platinum (Pt) [1,2,3,4,5,6], nickel (Ni) [2,3,7,8,9,10,11,12,13], titanium (Ti) [3,14], cobalt (Co) [3,15,16,17], palladium (Pd) [3,15,18,19,20], iridium (Ir) [21,22,23,24,25,26] and ruthenium (Ru) [3], using electrical and structural characterization techniques. Yao et al. [2] studied the current-voltage (I-V) characteristics of Pt/n-Ge (001) and Ni/ n-Ge (001) after subjecting the Schottky contacts to rapid thermal anneal (RTA) in N<sub>2</sub> ambient at 250-700°C for 20 s. Łsazcz et al. [5] studied the mechanisms of the Pt germanide formation by RTA process in Ge/Pt/Ge/SiO<sub>2</sub> structure at 200-600°C range. Their results depict that, during annealing of the Ge/Pt/Ge/SiO<sub>2</sub> structure at 200°C, the whole Pt layer had reacted with a part of the Ge layer and after 300°C anneal the whole Ge reacted with Pt. Thanailakis et. al [7] established a relationship between as-deposited Ni/n-Ge (111) and Pd/n-Ge (111) Schottky contacts barrier height values, the metal work functions and the density of surface states germanium substrate. Their results show a linear correlation of the as-deposited Schottky barrier height (SBH) values and work functions for the metals Pd and Ni, confirming the Effective Work Function model. Peng et al [9] reported the Ni/n-Ge (100) Schottky diodes I-V characteristics and the nickel germanide induced strain after subjecting the Schottky contacts to RTA in the temperature range 300-600°C. Their results show that the orthorhombic structure of NiGe induces epitaxial tensile strain on Ge substrate due to the difference in lattice constants. They also suggested that the increase of barrier height with annealing temperature may be due to the conduction band edge shift by the strain after germanidation process. An et al. [10] have investigated the impact of ion implantation on nickel germanides formation with pure-Ge substrate and electrical dependence of NiGe/Ge Schottky diodes on contact size. Their results reveal that ion implantation of BF<sub>2</sub> before germanidation is favourable for the formation of low-resistivity monogermanide phase (NiGe). They also showed that the Schottky barrier

height of Ni/Ge (100) Schottky diodes formed on pure-Ge substrate decreased with deceasing contact size, while the ideality factor increased remarkably, which may provide the guideline for the application to Schottky source/drain germanium transistors [10]. Peng et al. [11] have carried out micro-Raman studies on nickel germanides formed on (110) crystalline Ge. From XRD analysis they found that Ni<sub>5</sub>Ge<sub>3</sub>, NiGe and Ni<sub>2</sub>Ge phases are formed sequentially with increasing annealing temperatures from 300°C to 600°C on n-Ge (110) substrate. Their results depicted a strong tensile stress in the underlying Ge (110) substrate, which was attributed to the lattice mismatch between nickel germanides and germanium substrate. An et al. [12] have also successfully demonstrated the modulation of Schottky barrier height of Ni/n-Ge (111) by a germanidation-induced dopant segregation technique. Their results showed that the change of the Schottky barrier height was not attributed to the phase change of nickel germanides but to dopant segregation at the interface of germanides/germanium which causes conduction energy band bending. Perrin et al. [13] have studied both systems (Ni-Si and Ni-Ge) in order to compare their phase formation and growth kinetics. Ni thin films and armorphous semiconductor layers (a-Si and a-Ge) had been deposited on undoped (100) Si wafers. They have showed that Ni-Si system has three major phases (Ni<sub>2</sub>Si, NiSi and NiSi<sub>2</sub>) that grow sequentially while Ni-Ge system showed only two phases (Ni<sub>5</sub>Ge and NiGe) that grow simultaneously. Dedong et al. [14] studied changes in the electrical properties of Ti and Ni germanide Schottky contacts on n-Ge (100) substrate in the temperature range 300-500°C. Habanyama et al. [26] have used ion beam analysis employing micro-Rutherford backscattering spectrometry to investigate the interaction between iridium and germanium in lateral diffusion couple. Gaudet et al. [3] have investigated the phase formation sequence of Ru thin films on germanium using the x-ray diffraction technique.

Studies on germanides formation up to date have been carried out. The majority of them have reported the use of in-situ annealing by slowly-ramping annealing temperature or RTA in the temperature range 200-700°C. In this study we investigated the change in the electrical properties of Pt/-, Ni/-, Ti/-, Co/-, Pd/-, Ir/- and Ru/n-Ge (100) Schottky contacts at different furnace annealing temperatures in the temperature range 25-600°C. Results presented here are based on the effects of thermal annealing on the current-voltage characteristics of the metal Schottky contacts at different annealing temperatures, which may be attributed to combined effects of interfacial reaction and phase transformation [27], during the annealing process.

## 4.2 Experimental procedures

To study the thermal annealing behaviour of the Schottky contacts, we used bulk-grown (100) oriented, n-type Ge, doped with antimony (Sb) to a density of (1.5-3)  $\times 10^{15}$  cm<sup>-3</sup> supplied by Umicore. Before metallization, the samples were first degreased and subsequently etched in a mixture of H<sub>2</sub>O<sub>2</sub> (30%):H<sub>2</sub>O (1:5) for 1 min. Immediately after cleaning they were inserted into a vacuum chamber where 100 nm of AuSb (0.6%), was deposited by resistive evaporation on their back surfaces as ohmic contacts. The samples were then annealed at 350°C in Ar ambient for ten minutes to minimize the ohmic contact resistivity [28]. Before Schottky contact deposition, the samples were again chemically cleaned as described above. Pt, Ti, Ir or Ru Schottky contacts 0.6 mm in diameter, 300 nm thick were deposited by electron beam deposition under vacuum below 10<sup>-6</sup> Torr through a metal contact mask, while Ni, Co-, or Pd Schottky contacts were resistively deposited. The metal layer thickness and deposition rates were monitored in situ using a quartz crystal thickness monitor. Eight of each Pt/-, Ni/-, Ti/- Co/- Pd/-, Ir/- and Ru/n-Ge (100) Schottky barrier diodes (SBDs) were fabricated. After contact fabrication, current-voltage (I-V) and capacitance-voltage (C-V) measurements were used to extract the free carrier concentration and to determine the quality of the diodes. Isochronal annealing of the samples was performed in the temperature range 25-600°C in steps of 25°C for 30 min. I-V measurements followed each annealing cycle.

#### 4.3 Results

The barrier heights of the contacts were calculated from *I-V* characteristics, which were analyzed by the thermionic emission model given by the following equation [29,30]:

$$I(V) = I_0 \exp\left(\frac{qV}{nkT}\right) \left[1 - \exp\left(-\frac{qV}{kT}\right)\right]$$

(4.1)

where

$$I_0 = AA^*T^2 \exp\left(-\frac{q\phi_B}{kT}\right) \tag{4.2}$$

is the saturation current obtained as the intercept from the straight line of  $\ln I$  versus V,  $A^*$  is the effective Richardson constant, A is the diode area, T the measurement temperature in Kelvin, k is the Boltzmann constant,  $\phi_B$  is the zero bias effective Schottky barrier height (SBH), q is the electronic charge and n is the ideality factor which can be determined accurately from the slope of the linear part of a  $\ln I$  versus V plot. Assuming pure thermionic emission, n can be obtained from Eq. (4.1) as

$$n = \frac{q}{kT} \frac{dV}{d(\ln(I))} \tag{4.3}$$

which is equal to unity for an ideal diode and usually has a value greater than unity. The values of effective SBH were determined from the intercepts of the straight lines of the semilog-forward bias I-V characteristics with the help of Eq. (4.2). The effective SBHs and ideality factors vary from diode to diode; therefore it is common practice to take averages.

#### 4.3.1 Pt/n-Ge (100) Schottky diodes

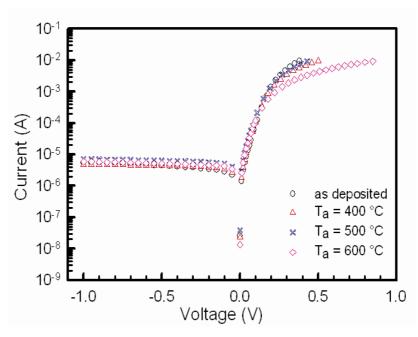

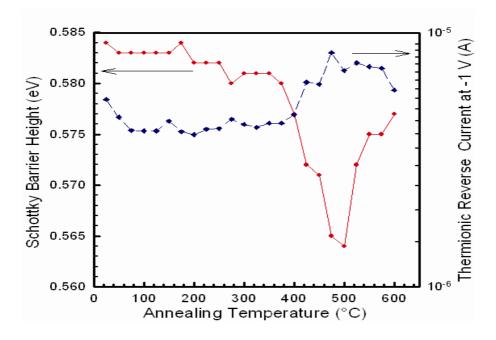

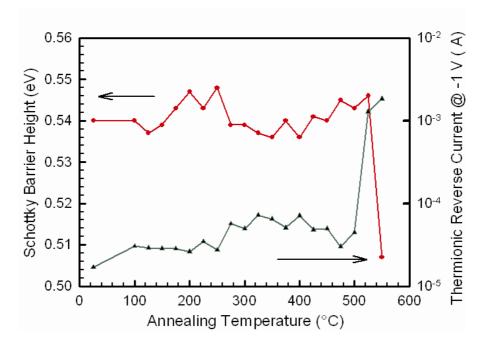

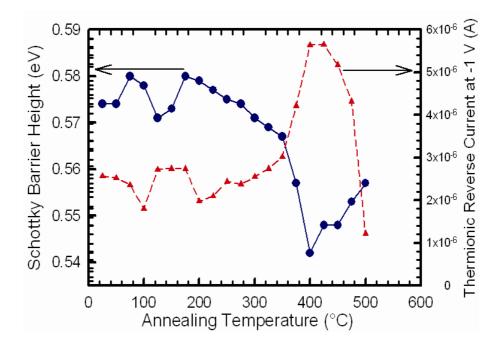

Fig. 4.1 presents the forward and reverse bias I-V characteristics of the Pt/n-Ge (100) SBDs annealed in the 25-600°C temperature range. Fig. 4.2 shows the variation of the Schottky barrier height and reverse current at -1 V with annealing temperature for Pt Schottky contacts. The SBH and reverse current at a bias voltage of -1 V for as-deposited Pt Schottky contacts were found to be  $(0.584 \pm 0.005)$  eV and  $(5.46 \pm 0.02)$   $\mu$ A, respectively.

**Fig.4.1** Experimental forward and reverse I-V characteristics of one of the Pt/n-Ge (100) Schottky barrier diodes after isochronal thermal treatment for 30 min at different annealing temperatures: as-deposited, 400°C, 500°C and 600°C.

**Fig. 4.2** Plot of the Schottky barrier height and reverse current at -1 V as a function of annealing temperature for Pt Schottky contacts on n-Ge (100).

The barrier height (BH) was approximately a constant within experimental error up to an annealing temperature of 350°C. The BH then drops to  $(0.564 \pm 0.005)$  eV after annealing at 500°C. It is evident that the BH decreases significantly above 350°C annealing. We can say

that there is a significant reaction between Pt and the Ge substrate. The change coincides with the initial phase formation of a germanide  $Ge_3Pt_2$ , which has been reported to form at  $400^{\circ}C$  [1,2]. After annealing at  $600^{\circ}C$ , the barrier height (BH) increased to  $(0.577\pm0.005)$  eV. The change in BH after the  $500^{\circ}C$  anneal coincides with the temperature range of formation of platinum germanide  $Ge_2Pt$  as reported by [1,2]. Throughout the annealing process, the reverse current at -1 V remains in the same order of magnitude  $(10^{-5} \text{ to } 10^{-6})$  A.

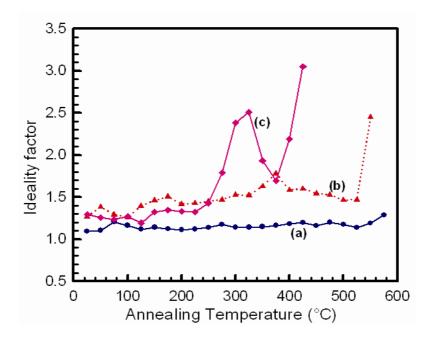

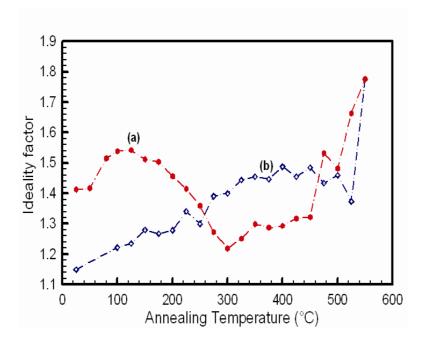

Fig. 4.3 (a) shows the variation of ideality factor of Pt/n-Ge(100) Schottky contacts with annealing temperature. The ideality factor was found to be between 1.09 and 1.30. The ideality factor is almost a constant, 1.09 up to a temperature of 575°C. It then increases to 1.30 after annealing at 600°C.

**Fig. 4.3** Plot of ideality factor as a function of annealing temperature for: (a) Pt Schottky contacts on n-Ge (100); (b) Ni Schottky contacts on n-Ge (100) and (c) Ti Schottky contacts on n-Ge (100).

## 4.3.2 Ni/n-Ge (100) Schottky diodes

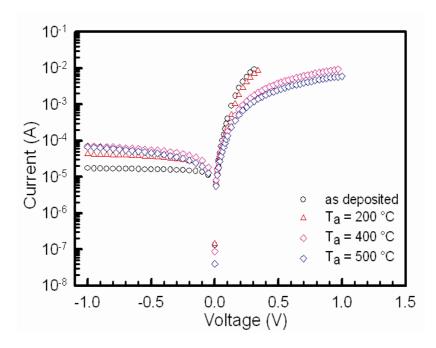

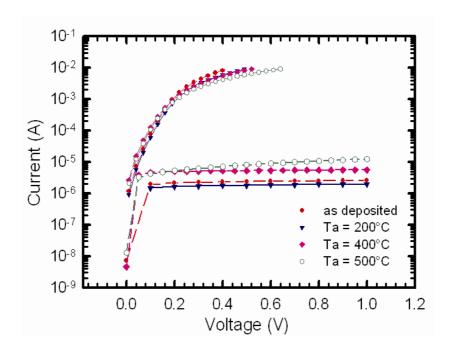

Fig. 4.4 depicts the semilog forward and reverse bias I-V characteristics of Ni/n-Ge (100) Schottky diodes annealed in the 25-550°C temperature range, together with those of as-deposited diodes. Fig. 4.5 shows the variation of the Schottky barrier height and reverse current at -1 V with annealing temperature for Ni/n-Ge (100) Schottky contacts.

**Fig. 4.4** Experimental forward and reverse I-V characteristics of one of the Ni/n-Ge (100) Schottky barrier diodes after isochronal thermal treatment for 30 min at different annealing temperatures: as-deposited, 200°C, 400°C and 500°C.

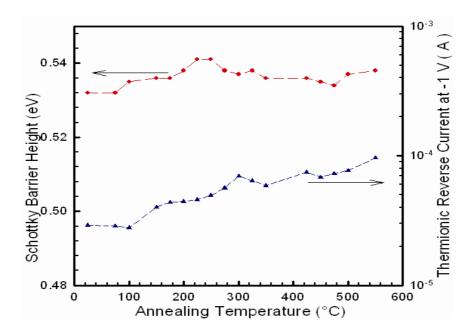

The as-deposited SBH and reverse current at -1 V for Ni/n-Ge (100) were found to be  $(0.532 \pm 0.005)$  eV and  $(29.20 \pm 0.02)$   $\mu$  A, respectively. The barrier height remains almost constant within experimental error in the temperature range  $100\text{-}550^{\circ}\text{C}$ . The near constant barrier height with annealing temperature in Ni/n-Ge (100) Schottky contacts may be attributed to the strong Fermi level pining effect between Ni-germanide/n-Ge (100) substrates [14]. Studies by Gaudet et al. [3], Peng et al. [9] and An et al. [10] revealed the existence of only one germanide phase, NiGe for Ni in this temperature range. Fig. 4.3 (b) shows the variation of ideality factor with annealing temperature for the Ni/n-Ge (100) Schottky diodes. The ideality factors were on the average between 1.27 and 1.47 at annealing temperatures between 25°C and 550°C.

**Fig. 4.5** Plot of the Schottky barrier height and reverse current at -1 V as a function of annealing temperature for Ni/n-Ge (100) Schottky contacts.

## 4.3.3 Ti/n-Ge (100) Schottky diodes

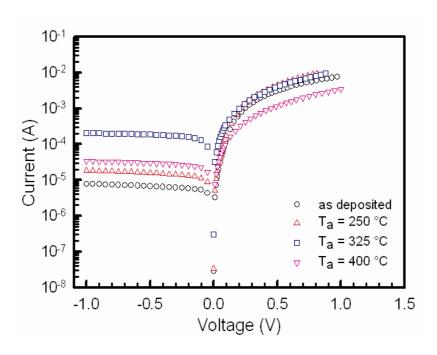

The semilog forward and reverse bias I-V characteristics of Ti/n-Ge (100) Schottky barrier diodes annealed in 25-425°C temperature range, together with those of as-deposited diodes are presented in Fig. 4.6.

The as-deposited Schottky barrier height and reverse current at -1~V for Ti/n-Ge (100) Schottky contacts were found to be (0.566  $\pm$  0.005) eV and (7.76  $\pm$  0.02)  $\mu$  A, respectively. Variation of barrier height and reverse current at a bias voltage of -1~V with annealing temperature for Ti/n-Ge (100) contacts is shown in Fig 4.7. The barrier height was approximately constant within experimental error up to an annealing temperature of 225°C. After further annealing at higher temperatures the barrier height decreased, reaching a minimum value of (0.497  $\pm$  0.005) eV at 300°C. This change in barrier height could be associated with the phase formation of a germanide  $Ti_6Ge_5$ , which has been reported to form at 300°C [14]. The subsequent increase in barrier height after annealing at temperatures higher than 300°C coincides with the temperature range for the formation of germanide  $Ti_5Ge_3$  [14].

**Fig. 4.6** Experimental forward and reverse I-V characteristics of one of the Ti/n-Ge (100) Schottky barrier diodes after isochronal thermal treatment for 30 min at different annealing temperatures: as-deposited, 250°C, 325°C and 400°C.

**Fig 4.7** Plot of the Schottky barrier height and reverse current at -1 V as a function of annealing temperature for Ti/n-Ge (100) Schottky contacts.

After a 425°C anneal, I-V characteristics of the Ti/n-Ge (100) severely deteriorated, and the contacts became near-ohmic. Even after subjecting these contacts to a temperature of 20 K, I-V measurements revealed no improvement in their rectifying behaviour.

The variation of ideality factor with annealing temperature for Ti/n-Ge (100) Schottky diodes is shown in Fig. 4.3 (c). The ideality factors were between 1.29 and 3.05 at annealing temperatures between 25°C and 425°C.

#### 4.3.4 Co/n-Ge (100) Schottky diodes

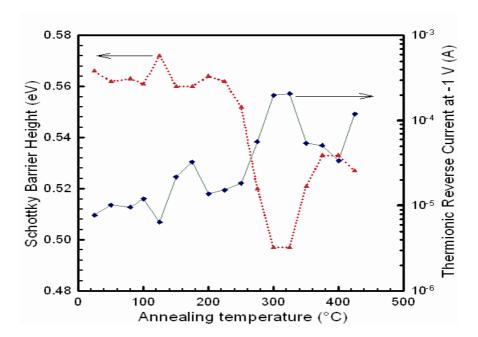

The variation in the electrical parameters, SBH and reverse current at –1 V for Co/n-Ge (100) Schottky contacts (Fig. 4.8) coincides with the temperature ranges of Co germanide phases formed by annealing as reported by Hsieh et al. [16] and Sun et al. [31], with CoGe forming between 100-300°C, Co<sub>5</sub>Ge<sub>7</sub> forming around 300°C and CoGe<sub>2</sub> forming at temperatures above 425°C. Fig 4.9 (a) depicts the variation of Co/n-Ge (100) ideality factors with annealing temperatures in the 25-550°C temperature range.

**Fig. 4.8** Plot of the Schottky barrier height and reverse current at -1 V as a function of annealing temperature for Co/n-Ge (100) Schottky diodes.

**Fig. 4.9** Plot of the ideality factor as a function of annealing temperature for (a) Co/n-Ge (100) and (b) Pd/n-Ge (100) Schottky diodes.

## 4.3.5 Pd/n-Ge (100) Schottky diodes

Fig. 4.10 shows the variation of the SBH and reverse current at -1 V with annealing temperature for Pd Schottky contacts on n-Ge (100). The SBH and reverse current at a bias voltage of -1 V for as-deposited Pd/n-Ge (100) Schottky diodes were found to be (0.540  $\pm$  0.005) eV and (17.00  $\pm$  0.02)  $\mu$  A, respectively. The variation of Pd/n-Ge (100) Schottky contacts barrier height between 100-500°C is approximately constant within experimental error. According to Gaudet et al. [3], only one germanide phase, PdGe exists for Pd on n-Ge (100) in this temperature range. This germanide is stable over a wide range of temperature. The variation of Pd/n-Ge (100) Schottky contacts ideality factors with annealing temperature is shown in Fig. 4.9 (b).

**Fig. 4.10** Plot of the Schottky barrier height and reverse current at -1 V as a function of annealing temperature for Pd/n-Ge (100) Schottky diodes.

## 4.3.6 Ir/n-Ge (100) Schottky diodes

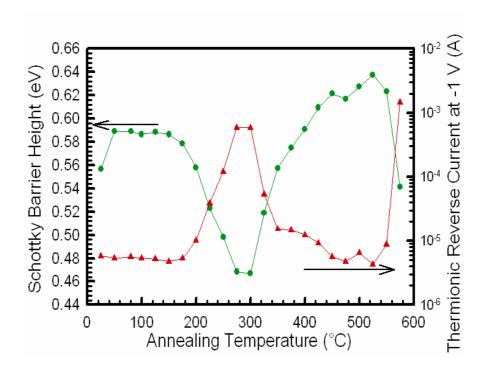

Fig. 4.11 shows the semilog forward and reverse bias I-V characteristics of Ir/n-Ge (100) Schottky diodes annealed in the temperature range 25-500°C, together with those of asdeposited samples. Fig. 4.12 represents the variation of the Schottky barrier height and reverse current at -1 V with annealing temperature for the Ir Schottky diodes on n-Ge (100). The SBH and reverse current at a bias voltage of -1 V for as-deposited Ir/n-Ge (100) Schottky diodes were found to be  $(0.574 \pm 0.005)$  eV and  $(2.57 \pm 0.02)$   $\mu$ A, respectively. After annealing at temperatures higher than  $200^{\circ}$ C, the barrier height drops significantly, reaching  $(0.542 \pm 0.05)$  eV after a  $400^{\circ}$ C anneal, suggesting that a significant reaction occurred between Ir and Ge. The change coincides with the initial phase formation of the IrGe and Ir<sub>4</sub>Ge<sub>5</sub> germanides, which have been reported by Habanyama et al. [26] to coexist and form at annealing temperatures around 350°C. Bhan and Scubert [32] also reported the phases IrGe and Ir<sub>4</sub>Ge<sub>5</sub> to coexist in bulk diffusion couples. The change in the barrier height after the  $400^{\circ}$ C anneal also coincides with the temperature of formation of germanide Ir<sub>3</sub>Ge<sub>7</sub> reported by Habanyama et al. [26]. Fig. 4.12 also depicts that, throughout the annealing process the reverse current at -1 V remains in the same order of magnitude, i.e.  $10^{-6}$  A. After

a 525°C anneal, the electrical characteristics of the Ir Schottky contacts severely deteriorated, the contacts became near ohmic and further evaluation was impossible.

**Fig 4.11** Experimental forward and reverse I-V characteristics of one of the Ir/n-Ge (100) Schottky barrier diodes after isochronal thermal treatment at different annealing temperatures: as-deposited, 200°C, 400°C and 500°C.

**Fig. 4.12** Plot of the Schottky barrier height and reverse current at -1 V as a function of annealing temperature for Ir Schottky contacts on n-Ge (100).

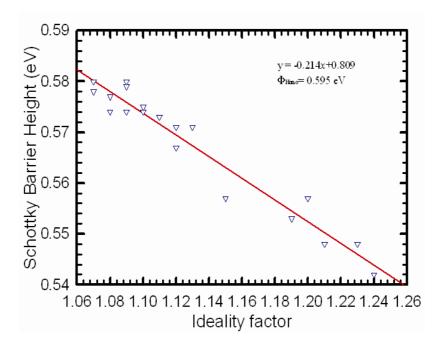

Fig. 4.13 shows a plot of barrier heights as a function of their respective ideality factors, obtained during the annealing process in the temperature range 25-500°C. The straight line in Fig. 4.13 is the least squares fit to experimental data. Since the results show a linear correlation between barrier heights and ideality factors, we then extrapolated the plot to ideality factor, n = 1.0 and obtained a laterally homogeneous barrier height of  $(0.595 \pm 0.005)$  eV for Ir/n-Ge (100) structures. The homogeneous barrier heights rather than effective BHs of contacts or their mean values should be used to discuss theories on the physical mechanisms that determine the BHs of metal-semiconductor contacts [33,34].

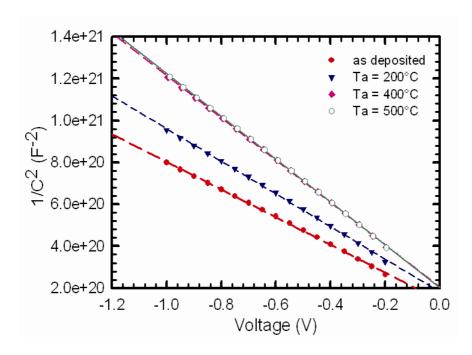

Fig 4.14 shows the plots of the reverse bias  $C^2$  versus V characteristics at 1.0 MHz of Ir/n-Ge (100) Schottky diodes at different annealing temperatures. The plots of  $C^2$  as a function of reverse bias voltage are linear, indicating the formation of Schottky diodes [35] and a constant donor concentration. In Schottky diodes, the depletion layer capacitance (C), can be expressed as [29,36]

$$\frac{1}{C^2} = \frac{2(V_0 - V)}{q\varepsilon_s A^2 N_D} \tag{4.4}$$

where A is the area of the diode,  $\varepsilon_s$  is the permittivity of the semiconductor,  $N_D$  is the carrier doping density, V is the magnitude of the reverse bias and  $V_0$  is the diffusion

**Fig 4.13** The plot of barrier heights as a function of their respective ideality factors of the *Ir/n-Ge* (100) Schottky barrier diodes at various annealing temperatures.

potential at zero bias. From Eq. (4.4), the values of  $V_0$  and  $N_D$  can be determined from the intercept and slope of the  $C^{-2}$ -V plot respectively.

**Fig. 4.14**  $C^2$ -V characteristics of one of the Ir/n-Ge (100) Schottky diodes at frequency of 1.0 MHz after isochronal treatment for 30 min at different annealing temperatures: as-deposited, 200°C, 400°C and 500°C measured at room temperature.

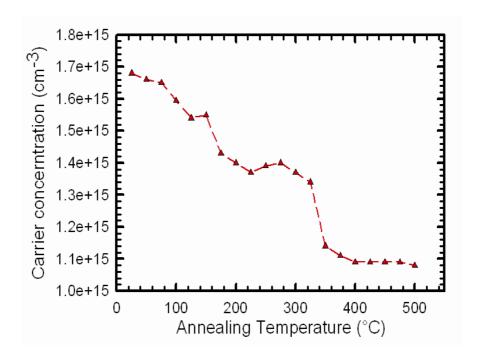

Fig. 4.15 The variation of the carrier concentration with annealing temperature.

Fig 4.15 depicts the variation of carrier doping concentration with annealing temperature. The carrier concentration decreases with increasing annealing temperature. Similar results have been reported by Serin [37], Nuhoglu et. al [38] and Opsomer et al. [39]. This may be due to either the presence of high density of compensating deep acceptor levels [37], possibly related to in-diffused Ir or the decrease in the dangling bonds due to annealing [38] and formation of Iridium germanide [26].

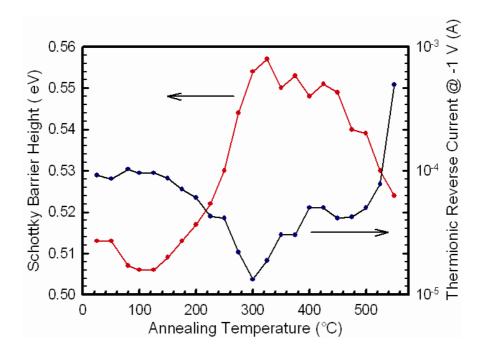

## 4.3.7 Ru/n-Ge (100) Schottky diodes

The variation of Schottky barrier height and reverse current at -1 V with annealing temperature for the Ru/n-Ge (100) Schottky diodes is depicted in Fig. 4.16. The values of SBH and reverse current at a bias of -1 V for as-deposited samples were determined to be  $(0.557 \pm 0.005)$  eV and  $(5.79 \pm 0.02)$   $\mu$ A, respectively. The results (Fig. 4.16) indicate nearly a constant Schottky barrier height in the temperature range 50-150°C. After annealing at temperatures higher than 150°C the barrier height decreases with annealing temperature and a low Schottky barrier of  $(0.467 \pm 0.005)$  eV is achieved after a 280°C anneal, suggesting a significant reaction between Ru and the Ge substrate forming a germanide.

**Fig. 4.16** Plot of the Schottky barrier height and reverse current at -1 V as a function of annealing temperature for Ru/n-Ge (100) Schottky diodes.

Although Gaudet et al. [3] have reported the first phase of Ru germanide, Ru+Ru<sub>2</sub>Ge<sub>3</sub> forming at 450°C after ramp anneal, we propose that after subjecting the Schottky contacts to isochronal annealing, the first phase of Ru germanide is formed in the temperature range 150-300°C, as the SBH decreases significantly above 150°C annealing. The subsequent increase in barrier height after annealing at temperatures higher than 300°C depicts the formation of the Ru germanide Ru<sub>2</sub>Ge<sub>3</sub>, in the temperature range 325-525°C. After a 550°C anneal the contacts became near-ohmic and further evaluation was impossible.

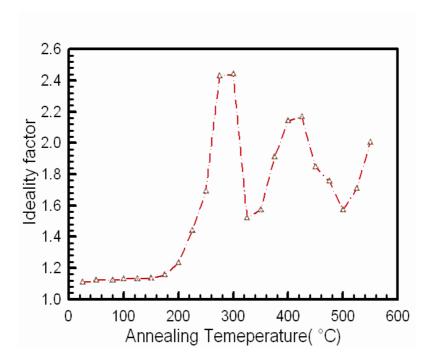

Fig. 4.17 shows the variation of ideality factor (n) with annealing temperature for the Ru/n-Ge (100) Schottky contacts. The value of n for as-deposited samples was determined to be 1.08. This ideality factor is almost a constant within experimental error up to an annealing temperature of 175°C. After annealing at temperatures higher than 175°C the ideality factors were greater than 1.1.

**Fig. 4.17** Plot of ideality factor as a function of annealing temperature for Ru/n-Ge (100) Schottky contacts.

## 4.4 Discussion

The fundamental mechanisms that determine the barrier height are still not fully understood [36,40,41,42]. The barrier height is likely to be a function of the interface atomic structure and atomic inhomogeneities at the metal-semiconductor interface which are caused by grain

boundaries, multiple phases, facets, defects, a mixture of different phases, etc [43,44]. It is well known that the chemical reactions between metals and semiconductors at interfaces can play an important role in the electrical properties of devices. Boyarbay et al. [45] suggested that the recent motivation for studying Schottky barrier formation is due to the recognition that both electronic and chemical equilibrium have to be considered together across a reactive interface between metal and semiconductor as surface states and metal-induced gap states failed to take into consideration the chemical equilibrium at the interface. During the annealing process, metals may react with semiconductors. The chemical equilibrium after heat treatment results in interfacial atomic rearrangement, interdiffusion and compound formation, which should have a profound effect on the electronic equilibrium producing the Schottky barrier [46]. Hence, the change in the Schottky barrier heights may be attributed to combined effects of interfacial reactions and phase transformation [27]. The Schottky barrier height is also temperature dependent, due to the fact that the measured current across a Schottky junction is a combination of thermionic emission and recombination currents [47]. Furthermore, the barrier height change in Schottky contacts can be explained according to the effective work function (EWF) model [48], where the barrier height value is determined by the work function of microclusters of one or more phases resulting from either oxygen contamination or metal-semiconductor reactions which occur during metallization and annealing, and each phase having its own effective work function [49].

For ideal Schottky contacts the ideality factor is 1.0. The ideality factors for Schottky contacts found to be greater than 1.1, indicates that the transport properties are not well modelled by thermionic emission alone although these contacts remain rectifying [50]. The deviation from ideality has been attributed mostly to the states associated with the defects near surface of the semiconductor [47]. These interface states, inter-diffusion, chemical reaction, compound formation, defects generation, etc. can all be derived from thermodynamics due to thermal annealing [51,52,53]. These may lead to recombination centres [50] and SBH inhomogeneities [54], which cause a flow of excess current leading to a deviation from the ideal thermionic emission behaviour.

# 4.5 Summary and conclusion

Pt/-, Ti/-, Ir/- and Ru/n-Ge (100) Schottky contacts were fabricated by electron beam deposition. Ni/-, Co/- and Pd/n-Ge (100) Schottky diodes were fabricated by resistive deposition. The Schottky contacts behaviour was investigated under various annealing conditions. The variation of Schottky barrier heights and ideality factors with annealing temperature may be attributed to interfacial reactions of metals (Pt, Ni, Ti, Co, Pd, Ir, Ru) with germanium and the phase transformation of the metal-germanides during annealing. The electrical properties of the metal Schottky contacts reveal that Pt/n-Ge (100) and Ir/n-Ge (100) Schottky contacts are of high quality with low reverse currents at –1 V of the order (10<sup>-5</sup> to 10<sup>-6</sup>) A and as-deposited ideality factors as low as 1.09. The as-deposited barrier heights of nearly equal in magnitude to the bandgap of Ge in the Pt/-, Ni/-, Ti/- and Ir/n-Ge (100) Schottky contacts imply good Schottky source/drain contact materials in p-channel Ge-MOSFETS, for the hole injection from source into inverted p-channel [2]. The results also show that Pt/n-Ge (100) and Ru/n-Ge (100) Schottky contacts are highly thermally stable over a wide range of temperatures compared to Ni/-, Ti/-, Co/-,Pd/- and Ir/n-Ge (100) Schottky contacts.

#### References

- [1] M. G. Grimaldi, L. Weilunski, M.-A. Nicolet, Thin Solid Films **81** (1981) 207.

- [2] H.B. Yao, C.C. Tan, S.L. Liew, C.T. Chua, C.K. Chua, R. Li, R.T.P. Lee, S.J. Lee, D.Z. Chi, International Workshop on Junction Technology Processing, (2006) 164.

- [3] S. Gaudet, C. Detavernier, A.J. Kellock, P. Desjardins, C. Lavoie, J. Vac. Sci. Technol. A **24** (3) (2006) 474.

- [4] R. Gumeniuk, W. Schnelle, H. Rosner, M. Nicklas, A. Leithe-Jasper, Yu Grin, Phys. Rev. Lett. **100** (2008) 0170021.

- [5] A. Łaszcz, J. Ratajczak, A. Czerwinski, J. Kątcki, V. Srot, F. Philipp, P.A. van Aken,N. Breil, G. Larrieu, E. Dubois, Mater. Sci. Eng. B 154-155 (2008) 175.

- [6] F. Ohtsu, H. Fukuoka, S. Yamanaka, J. Alloys Compd. **487** (2009) 712.

- [7] A. Thanaillakis, D.C. Northrop, Solid State Electron. **16** (1973) 249.

- [8] F. Nemouchi, D. Mangelinck, J.L. Lábár, M. Putero, C. Bergman, P. Gas, Microelectron. Eng. **83** (2006) 2101.

- [9] C.-Y. Peng, Y.-H. Yang, C.-M. Lin, Y.-J. Yang, C.-F. Huang, C.W. Liu, International Conference on Solid-State and Integrated Circuits Technology Proceeding (ICSICT), art. No. 4734645 (2008) 681

- [10] X. An. C. Fan. R. Huang, X. Zhang, Proceedings- Electrochemical Society, PV 1 (2008) 408.

- [11] C.-Y. Peng, C.-F. Huang, Y.-J. Yang, C.W. Liu, ECS Trans. **16** (2008) 249.

- [12] X. An, C. Fan, R. Huang, X. Zhang, Chin. Phys. Lett. **26** (2009) 0873041.

- [13] C. Perrin, D. Mangelinck, F. Nemouchi, J. Labar, C. Lavoie, C. Bergman, P. Gas,Mater. Sci. Eng. B 154-155 (2008) 163

- [14] H. Dedong, W. Xin, W.Yi, Wang, T. Dayu, W. Wei, L. Xiaoyan, K. Jinfeng,H. Ruqi, Microelectron. Eng. 82 (2005) 93

- [15] M. Wittmer, M.A. Nicolet, and J.W. Mayer, Thin Solid Films 42 (1977) 51.

- [16] Y.F. Hsieh, L.J. Chen, L.J. Marshall, and S.S. Lau, Appl. Phys. Lett. **51** (1987)1588.

- [17] S.P. Ashburn, M.C. Öztürk, G. Harris, and D.M. Maher, J. Appl. Phys. 74 (1993) 4455.

- [18] E.D. Marshall, C.S. Wu, C.S. Pai, D.M. Scott, and S.S. Lau, Thin Solid Films:Material Research Society (MRS) Symposia Proceedings, Pittsburg, PA, (1985) 161.

- [19] G. Ottaviani, C. Canali, G. Ferrari, G. Majni, M. Prudenziati, and S.S. Lau, Thin Solid Films 47 (1977) 187.

- [20] Y.F. Hsieh and L.J. Chen, Thin Solid Films **162** (1988) 295)

- [21] P.S. Salamakha, O.I. Bodak, V.K. Percharskii, V.K. Bel'skii, Russian Metallurgy, Metally **1** (1989) 210.

- [22] B. Pene, M. Hofmann, J. Leciejewicz, M. Ślaski, A. Szytuła, J. Alloys Compd. **287** (1999) 18.

- [23] U.C. Rodewald, R. Pöttgen, Solid State Sci. 5 (2005) 487.

- [24] D.X. Li, S. Nimori, Y. Homma, Y. Shiokawa, J. Appl. Phys. 97 (2005) 073903-1.

- [25] K. Katoh, T. Tsutsumi, K. Yamada, G. Terui, Y. Niide, A. Ochiai, Physica B **373** (2006).

- [26] A. Habanyama, C.M. Comrie, Thin Solid Films **516** (2008) 5137.

- [27] Y. Sun, X.M. Shen, J. Wang, D.G. Zhao, G. Feng, Y. Fu, S.M. Zhang, Z.H. Zhang,Z.H. Feng, Y.X. Bai, H. Yang, J. Phys. D.: Appl. Phys. 35 (2002) 2648.

- [28] F.D. Auret, P.J. Janse van Rensburg, M. Hayes, J.M. Nel, S. Coelho, W.E. Meyer,

S. Decoster, V. Matias, A. Vantomme, D. Smeets, Nucl. Instrum. Methds B 257

(2007) 169.

- [29] S.M. Sze, Physics of Semiconductor Devices, New York, 1981, p. 245.

- [30] B. Li, S. Chua, Y. Nikolai, L. Wang, E. Sia, Solid State Electron. 47 (2003) 602.

- [31] H.P. Sun, Y.B Chen, X.Q. Pan, D.Z. Chi, R. Nath, and Y.L. Foo, Appl. Phys. Lett. **86** (2005) 071904.

- [32] S. Bhan, K. Schubert, Z. Metallkunde. **51** (1960) 327.

- [33] R.F. Schmitsdorf, T.U. Kampen, W. Mönch, J. Vac. Sci. Technol. B. **15** (1997) 1221.

- [34] H. Çetin, B. Şahin, E. Ayyilidiz, A. Turut, Semicon. Sci. Technol. 19 (2004) 1113

- [35] V. Saxen, R. Prakash, Polym. Bull. **45** (2000) 267.

- [36] E.H. Rhoderick, R.H. Williams, Metal-Semiconductor Contacts, Clarendon Press Oxford, 1988.

- [37] T. Serin, Tr. J. Phys. **22** (1998) 423.

- [38] C. Nuhoglu, Y. Gulen, Vacuum **84** (2010) 812.

- [39] K. Opsomer, E. Simoen, C. Clayes, K. Maex, C. Detavernier, R.L. Van Meirhaeghe,S. Forment, P. Clauws, Mater. Sci. Semicond. Processing 9 (2006) 554.

- [40] E. Hökelek, G.Y. Robinson, Solid State Electron. 99 (1981) 24.

- [41] K. Bourenane, A. Keffous, G. Nezzal, Vacuum **81** (2007) 663.

- [42] S. Chand, S. Bala, Physica B **390** (2007) 179.

- [43] J.P. Sullivan, R.T. Tung, M.R. Pinto, W.R. Graham, J. Appl. Phys. **70** (1991) 7403.

- [44] R.T. Tung, Mater. Sci. Eng. R **35** (2001) 1.

- [45] B. Boyarby, H. Çetin, M. Kaya, E. Ayyildiz, Microelectron. Eng. 85 (2008) 721

- [46] R.D. Thomson, K.N. Tu, J. Appl. Phys. **53** (1982) 4285.

- [47] A.R. Saha, S. Chattopadhyay, C.K. Maiti, Mater. Sci. Eng. B 114-115 (2004) 218.

- [48] J.L. Freeouf, J.M. Woodall, Appl. Phys. Lett. **29** (1976) 263.

- [49] E. Ayyildiz, A. Türüt, Solid State Electron. **43** (1999) 521.

- [50] H. Dogan, N. Yildirim, A. Turut, Microelectron. Eng. 85 (2008) 655.

- [51] T. Sands, Appl. Phys. Lett. **52** (1988) 197.

- [52] S.K. Cheung, N.W. Cheung, Appl. Phys. Lett. **49** (1986) 85.

- [53] J.L. Everaet, R.L. Van Meirhaeghe, W.H. Laflěre, F. Cardon, Semicond. Sci. Technol. **5** (1990) 60.

- [54] R.T. Tung, J.P. Sullivan, F. Schrey, Mater. Sci. Eng. B **14** (1992) 266.

# List of publications

- 1. A. Chawanda, C. Nyamhere, F.D. Auret, W. Mtangi, T.T. Hlatshwayo, M. Diale, J.M. Nel, Physica B **404** (2009) 4482.

- 2. A. Chawanda, C. Nyamhere, F.D. Auret, W. Mtangi, M. Diale, J.M. Nel, J. Alloys Compd. **492** (2010) 649.

- 3. A. Chawanda, C. Nyamhere, F.D. Auret, W. Mtangi, M. Diale, and J.M. Nel, Phys. Status Solidi, 7 (2010) 248.